## 2N5060 THRU 2N5064

## SILICON CONTROLLED RECTIFIERS 0.8 AMP, 30 THRU 200 VOLT

www.centralsemi.com

The CENTRAL SEMICONDUCTOR 2N5060 series devices are epoxy molded SCRs designed for control systems and sensing circuit applications.

MAXIMUM RATINGS: (T<sub>A</sub>=25°C unless otherwise noted)

| MAXIMOM NATINGO: (1A-23 O diliciss other                | ,                     | ONEGGO | 0115064 | 0115000   | 0115000 | 0115004 | LINUTO |

|---------------------------------------------------------|-----------------------|--------|---------|-----------|---------|---------|--------|

| Dools Donotition Off Chata Vallage                      |                       | 2N5060 | 2N5061  | 2N5062    | 2N5063  |         |        |

| Peak Repetitive Off-State Voltage                       | $V_{DRM}$ , $V_{RRM}$ | 30     | 60      | 100       | 150     | 200     | V      |

| RMS On-State Current (Note 1; T <sub>C</sub> =80°C)     | <sup>I</sup> T(RMS)   |        |         | 8.0       |         |         | Α      |

| Average On-State Current (Note 1; T <sub>C</sub> =67°C) | $I_{T(AV)}$           |        |         | 0.51      |         |         | Α      |

| Average On-State Current (Note 1; T <sub>C</sub> =102°C | ) I <sub>T(AV)</sub>  |        |         | 0.255     |         |         | Α      |

| Peak One Cycle Surge Current (60Hz)                     | lTSM                  |        |         | 10        |         |         | Α      |

| I <sup>2</sup> t Value for Fusing (t=8.3ms)             | I <sup>2</sup> t      |        |         | 0.4       |         |         | $A^2s$ |

| Peak Forward Gate Power (tp≤1.0µs)                      | $P_{GM}$              |        |         | 0.1       |         |         | W      |

| Average Forward Gate Power (t=8.3ms)                    | $P_{G(AV)}$           |        |         | 0.01      |         |         | W      |

| Peak Forward Gate Current (tp≤1.0µs)                    | l <sub>GM</sub> ′     |        |         | 1.0       |         |         | Α      |

| Peak Reverse Gate Voltage (tp≤1.0µs)                    | $V_{RGM}$             |        |         | 5.0       |         |         | V      |

| Operating Junction Temperature                          | $T_J$                 |        | -       | 40 to +12 | 5       |         | °C     |

| Storage Temperature                                     | T <sub>stg</sub>      |        | -       | 40 to +15 | 0       |         | °C     |

| Thermal Resistance (Note 2)                             | ΘJC                   |        |         | 75        |         |         | °C/W   |

| Thermal Resistance                                      | $\Theta_{\sf JA}$     |        |         | 200       |         |         | °C/W   |

Notes: 1) 180° Conduction Angles

2) Measured with the "flat side down" on a heatsink and held in position by a metal clamp over the curved surface.

| ELECTRICAL CHARACTERISTICS: (T <sub>C</sub> =25°C unless otherwise noted) |                                                                   |     |     |     |       |

|---------------------------------------------------------------------------|-------------------------------------------------------------------|-----|-----|-----|-------|

| SYMBOL                                                                    | TEST CONDITIONS                                                   | MIN | TYP | MAX | UNITS |

| I <sub>DRM</sub> , I <sub>RRM</sub>                                       | $V_D$ =Rated $V_{DRM}$ , $R_{GK}$ =1.0k $\Omega$                  |     |     | 10  | μΑ    |

| I <sub>DRM</sub> , I <sub>RRM</sub>                                       | $V_D$ =Rated $V_{DRM}$ , $R_{GK}$ =1.0k $\Omega$ , $T_C$ =110°C   |     |     | 50  | μΑ    |

| lgt                                                                       | $V_D = 7.0V, R_L = 100\Omega$                                     |     |     | 200 | μΑ    |

| l <sub>GT</sub>                                                           | $V_D$ =7.0V, $R_L$ =100 $\Omega$ , $T_C$ =-40°C                   |     |     | 350 | μΑ    |

| lΗ                                                                        | Initiating Current, I <sub>T</sub> =20mA, $R_{GK}$ =1.0k $\Omega$ |     |     | 5.0 | mA    |

| lΗ                                                                        | Initiating Current, IT=20mA, RGK=1.0k $\Omega$ , TC=-40°C         |     |     | 10  | mA    |

| $V_{GT}$                                                                  | $V_D = 7.0V, R_L = 100\Omega$                                     |     |     | 0.8 | V     |

| $V_{GT}$                                                                  | $V_D$ =7.0V, $R_L$ =100 $\Omega$ , $T_C$ =-40°C                   |     |     | 1.2 | V     |

| $V_{GD}$                                                                  | $V_D$ =Rated $V_{DRM}$ , $R_L$ =100 $\Omega$ , $T_C$ =110°C       | 0.1 |     |     | V     |

| $V_{TM}$                                                                  | I <sub>TM</sub> =1.2A, T <sub>A</sub> =25°C                       |     |     | 1.7 | V     |

| dv/dt                                                                     | $V_D$ =Rated $V_{DRM}$ , $R_{GK}$ =1.0k $\Omega$                  |     | 30  |     | V/µs  |

R5 (7-May 2015)

## 2N5060 THRU 2N5064

# SILICON CONTROLLED RECTIFIERS 0.8 AMP, 30 THRU 200 VOLT

**ELECTRICAL CHARACTERISTICS - Continued:** (T<sub>C</sub>=25°C unless otherwise noted) **2N5062**

| SYMBOL                           | TEST CONDITIONS                                                                                           | 2N5060<br>2N5061<br>TYP | 2N5062<br>2N5063<br><u>2N5064</u><br>TYP | UNITS    |

|----------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------|------------------------------------------|----------|

| t <sub>d</sub><br>t <sub>r</sub> | [V <sub>D</sub> =Rated V <sub>DRM</sub> , I <sub>GT</sub> =1.0mA,<br>Forward Current=1.0A, di/dt=6.0A/µs] | 3.0<br>0.2              | 3.0<br>0.2                               | μs<br>μs |

| tq                               | Forward Current=1.0A, tp=50μs,<br>0.1% Duty Cycle, di/dt=6.0A/μs,<br>dv/dt=20V/μs, I <sub>GT</sub> =1.0mA | 10                      | 30                                       | μs       |

R1

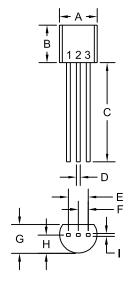

## **TO-92 CASE - MECHANICAL OUTLINE**

| DIMENSIONS |        |       |             |      |  |  |

|------------|--------|-------|-------------|------|--|--|

|            | INCHES |       | MILLIMETERS |      |  |  |

| SYMBOL     | MIN    | MAX   | MIN         | MAX  |  |  |

| A (DIA)    | 0.175  | 0.205 | 4.45        | 5.21 |  |  |

| В          | 0.170  | 0.210 | 4.32        | 5.33 |  |  |

| С          | 0.500  |       | 12.70       | -    |  |  |

| D          | 0.016  | 0.022 | 0.41        | 0.56 |  |  |

| Е          | 0.100  |       | 2.54        |      |  |  |

| F          | 0.050  |       | 1.27        |      |  |  |

| G          | 0.125  | 0.165 | 3.18        | 4.19 |  |  |

| Н          | 0.080  | 0.105 | 2.03        | 2.67 |  |  |

|            | 0.015  |       | 0.38        |      |  |  |

TO-92 (REV: R1)

## LEAD CODE:

- 1) Cathode

- 2) Gate

- 3) Anode

# MARKING:

**FULL PART NUMBER**

#### 2N5060 THRU 2N5064

#### **SERVICES**

- · Bonded Inventory

- · Custom Electrical Screening

- Custom Electrical Characteristic Curves

- SPICE Models

- Custom Packaging

- Package Base Options

- Custom Device Development/Multi Discrete Modules (MDM™)

- · Bare Die Available for Hybrid Applications

**LIMITATIONS AND DAMAGES DISCLAIMER:** In no event shall Central be liable for any collateral, indirect, punitive, incidental, consequential, or exemplary damages in connection with or arising out of a purchase order or contract or the use of products provided hereunder, regardless of whether Central has been advised of the possibility of such damages. Excluded damages shall include, but not be restricted to: cost of removal or reinstallation, rework, ancillary costs to the procurement of substitute products, loss of profits, loss of savings, loss of use, loss of data, or business interruption. No claim, suit, or action shall be brought against Central more than two (2) years after the related cause of action has occurred.

In no event shall Central's aggregate liability from any warranty, indemnity, or other obligation arising out of or in connection with a purchase order or contract, or any use of any Central product provided hereunder, exceed the total amount paid to Central for the specific products sold under a purchase order or contract with respect to which losses or damages are claimed. The existence of more than one (1) claim against the specific products sold to Buyer under a purchase order or contract shall not enlarge or extend this limit.

Buyer understands and agrees that the foregoing liability limitations are essential elements of a purchase order or contract and that in the absence of such limitations, the material and economic terms of the purchase order or contract would be substantially different.

R5 (7-May 2015)