**Data Sheet (Non-confidential)**

### **DESCRIPTION**

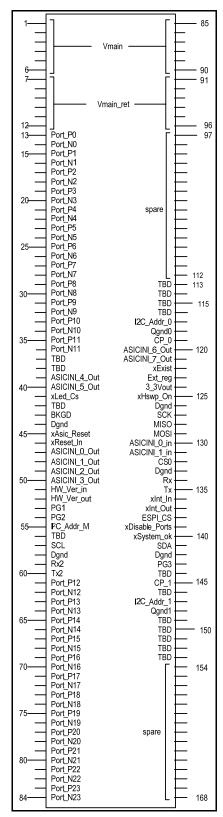

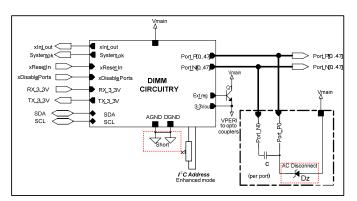

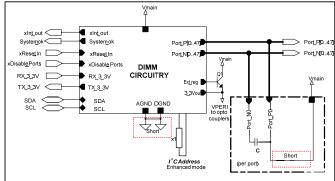

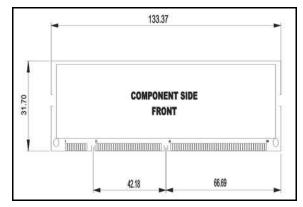

Microsemi's™ new and unique family of Power over Ethernet (PoE) modules enable next-generation network devices to share data and power over the same cable. The PD671xxx PoE PSE modules are fit / form compatible with the standard plug-in memory modules used in personal computers (Dual Inline Memory Modules - DIMMs) (see Figure 1 and Figure 12). Thus, the use of these modules permit network devices to be designed for up to 96 ports, with fewer ports actually installed. Additional modules can be inserted in the field at any time.

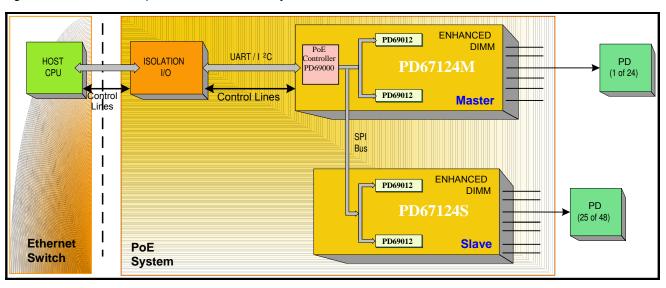

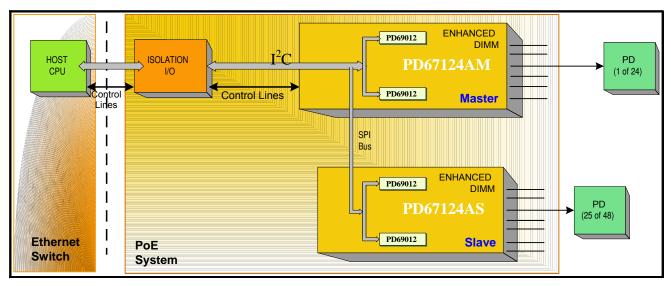

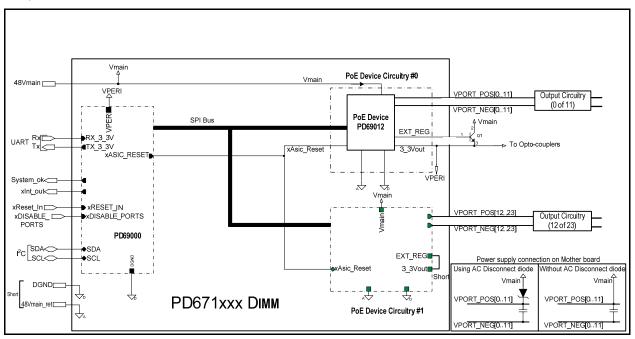

The PD671xxx (8, 12 or 24 ports DIMM) includes a wide range of functions. Some of these modules include the PD69000 micro-controller unit (PoE controller) for Enhanced features and a flexible work environment in a DIMM master or DIMM slave configuration (refer to Ordering Information, page 2).

Microsemi's PoE PD671xxx DIMMs implement real time mechanisms including detection, classification, port real-time protection and system level functions (power management and MIB support).

Microsemi's PD69012 IC, 12-channel PoE Manager IC is at the heart of these modules. PD671xxx DIMMs enable the detection of IEEE802.3at-2009 Type 1 (low power) or Type 2 (high power) Powered Devices (PDs), ensuring safe power feeding and removal over Ethernet ports. The PD69012-based DIMMs detect and disable disconnected ports, using DC or AC disconnection methods. The DIMMs are embedded in multiport and highly populated Ethernet switches, requiring a minimum of external components.

The PD671xxx DIMM is fully backwards compatible with the PD670xx DIMM and can be dropped into existing designs.

Figure 1: PoE PD67124 DIMM

IMPORTANT: For the most current data, consult Microsemi's website: <a href="http://www.microsemi.com">http://www.microsemi.com</a>

#### **KEY FEATURES**

- IEEE 802.3AT-2009 and IEEE802.3AF-2003 compliant

- Up to 30 W per port power PoE solution

- RoHS compliant

- Supports IETF PoE MIB (RFC 3621)

- Up to 24 power ports per single DIMM

- Up to 96 ports in a system, using master and slave configuration

- Thermal protection per port

- Thermal monitoring capabilities

- Pre-standard detection methods (Cisco Inline Power and Power over LAN Legacy)

- Non-standard terminals supported

- DC disconnect with DC modulation

- AC disconnect function utilizing external diodes

- PD 2-events classification function

- Operates using a single input (44 to 57 VDC)

- I<sup>2</sup>C or UART host interface

- Host communication is backward compatible with PD67024M communication, or Marvell® ISSR

- Programmable over current protection per port

- Built-in power management algorithm

- Internal power-on reset mechanism

- Fast port shutdown on power supply failure

- Supports Backplane Power Management

- Automatic on/off sequencer for 96 ports

- Disable/enable power per port

- Continuous port current monitoring

- Serial interface for LED indicator support

- Backwards compatible with PD670xx

- Fit/form compliant with168-pin DIMM JEDEC MO-161F, 3.3 V

- Space efficient compact design

- Factory pre-tested, for plug-and-play integration

- Safety standard compliant: UL / cUL per UL60950-1 (mounted on Microsemi evaluation board)

| Ordering Information           |       |                           |                      |                                      |  |  |

|--------------------------------|-------|---------------------------|----------------------|--------------------------------------|--|--|

| Part Number                    | Ports | Port Disconnect<br>Method | DIMM<br>Master/Slave | Mode<br>Enhanced/Auto <sup>[3]</sup> |  |  |

| PD67124MDC-gggg <sup>[1]</sup> | 24    | DC                        | Master               | Enhanced                             |  |  |

| PD67124S                       | 24    | AC/DC [4]                 | Slave [2]            | Enhanced                             |  |  |

| PD67112MDC-gggg                | 12    | DC                        | Master               | Enhanced                             |  |  |

| PD67108MDC-gggg                | 8     | DC                        | Master               | Enhanced                             |  |  |

| PD67124MAC-gggg                | 24    | AC                        | Master               | Enhanced                             |  |  |

| PD67112MAC-gggg                | 12    | AC                        | Master               | Enhanced                             |  |  |

| PD67108MAC-gggg                | 8     | AC                        | Master               | Enhanced                             |  |  |

| PD67124AM                      | 24    | AC/DC [5]                 | Master               | Auto                                 |  |  |

| PD67124AS                      | 24    | AC/DC [5]                 | Slave [2]            | Auto                                 |  |  |

| PD67112AM                      | 12    | AC/DC [5]                 | Master               | Auto                                 |  |  |

| PD67108AM                      | 8     | AC/DC [5]                 | Master               | Auto                                 |  |  |

| Matai                          |       |                           |                      |                                      |  |  |

#### Note:

- [1] gggg: MCU software version.

- [2] DIMM Slave should be used in conjunction with DIMM Master (for systems require more than 24 ports).

- [3] Enhanced and Auto mode of operation stand for the PoE system features. The Enhanced mode system includes the PD69000 PoE controller.

- [4] DIMM Slave port disconnection method is determined by the DIMM Master which controllers it.

- [5] DIMM functioning at the Auto Mode Configuration can be configured to AC or DC port disconnection method by the system host. Further details can be found in the Auto Mode User Guide, Catalogue Number 06-1200-056.

## **APPLICABLE DOCUMENTS**

- IEEE 802.3at-2009 standard, DTE Power via MDI

- PD69012 Data Sheet, Catalogue Number 06-0069-058

- PD69000 Data Sheet, Catalogue Number 06-0070-058

- Serial Communication Protocol User Guide 06-0032-056

- Auto Mode User Guide, Catalogue Number 06-1200-056

- Layout Design Guidelines for DIMM-based PoE Systems, AN-132 Catalogue Number 06-0010-080

- Designing a DIMM-based PoE System, AN-133 Catalogue Number 06-0011-080

-0.3 to 80 VDC (1)

-0.3 to 0.3 VDC  $^{(2)}$

-0.3 to 80 VDC  $^{(1)}$

-0.3 to (3\_3Vout + 0.3 VDC)

-0.3 to (3\_3Vout + 0.3 VDC)

3.8 VDC -0.3 to 6 VDC

± 2 kV <sup>(3)</sup> -40° to +125° C

## ABSOLUTE MAXIMUM RATINGS

Vmain

DGND, AGND, QGND

VPORT\_POSx, VPORT\_NEGx

3\_3Vout

EXT\_REG

I<sup>2</sup>C\_Addr\_M.

MISO, MOSI, SCK, CS, SCL, SDA, SSn, Led\_Cs, Asic\_Reset

ESD (Human Body Model) Storage temperature

**Notes:** "x" defines port numbers, 0 to 11, inclusive.

(1) 80 VDC is the transient voltage that can be applied for up to one minute.

(2) Maximum voltage value between grounds.

(3) ESD Human Body Model is: (CZap = 100 pF, RZap = 1500  $\Omega$ ).

Stresses beyond those listed above can cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods could affect device reliability.

| CALCULATED MTBF DATA [1] |                   |                         |             |  |  |

|--------------------------|-------------------|-------------------------|-------------|--|--|

|                          | Operation mode    | Failures per 10^6 Hours | MTBF(Hours) |  |  |

| PD67124M @ 25°C Ambient  | IEEE 802.3AT-2009 | 0.5181                  | 1930000     |  |  |

| PD67124M @ 25°C Ambient  | IEEE802.3AF-2003  | 0.5128                  | 1950000     |  |  |

#### Notes:

[1] - MTBF calculation made for the worst case PoE DIMM populated with 24 fully loaded ports

| OPERATING CONDITIONS                                                 |          |          |          |      |  |  |  |

|----------------------------------------------------------------------|----------|----------|----------|------|--|--|--|

| PARAMETER                                                            | MIN.     | NOM.     | MAX.     | UNIT |  |  |  |

| Operating ambient temperature                                        | -10      |          | +70      | °C   |  |  |  |

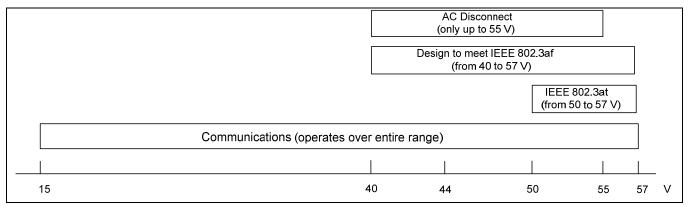

| Operating voltage (see Figure 2)                                     | 40 to 44 | 44 to 55 | 55 to 57 | VDC  |  |  |  |

| Operating humidity (non-condensing, Per IEC 68-2-56)                 |          |          | 95       | %    |  |  |  |

| Notes:                                                               |          |          |          |      |  |  |  |

| Operating functions depend on the input voltage.                     |          |          |          |      |  |  |  |

| Operating voltage range for IEEE802.3AF is 44 to 57 VDC              |          |          |          |      |  |  |  |

| Operating voltage range for IEEE802.3AT (High Power) is 50 to 57 VDC |          |          |          |      |  |  |  |

Figure 2: Operational voltage Ranges

### **Airflow**

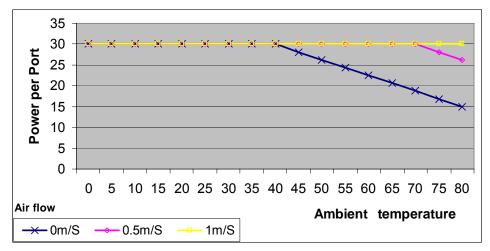

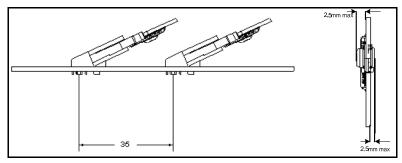

To prevent overheating, the application designer should supply a minimal airflow to the PD671xxx DIMMs. Figure 3 shows the power handling capability versus air velocities in meter/second, as measured at all points of the DIMM envelope, prior to insertion into the connector(s). As shown in Figure 12, the connectors are spaced by 35 mm; 1 m/s = 197 LFM (linear feet per minute). Maximum allowed temperature is +85° C for the MCU (PD69000) and +125° C for the PD69012.

Figure 3: Power per Port for two DIMMs (48 ports)

## **Electrical Characteristics**

The following sections detail the DC and analog characteristics.

## **DC Characteristics for Digital Inputs and Outputs**

| PARAMETER                 | SYMBOL                      | MIN.                                                                  | MAX.         | UNIT       | REMARKS                 |  |  |

|---------------------------|-----------------------------|-----------------------------------------------------------------------|--------------|------------|-------------------------|--|--|

| Pin Name                  | SCL, xDisabl                | SCL, xDisable_Ports, Rx (without internal pull-up/pull-down resistor) |              |            |                         |  |  |

| Туре                      | Schmitt Trigg               | ger CMOS in                                                           | put, TTL lev | ⁄el        |                         |  |  |

| High level input voltage  | $V_{IH}$                    | 2.0                                                                   |              | V          |                         |  |  |

| Low level input voltage   | $V_{IL}$                    |                                                                       | 0.8          | V          |                         |  |  |

| Input voltage hysteresis  |                             | 0.3                                                                   |              | V          |                         |  |  |

| Input high current        | I <sub>IH</sub>             | -1                                                                    | +1           | μΑ         |                         |  |  |

| Input low current         | I <sub>IL</sub>             | -1                                                                    | +1           | μA         |                         |  |  |

| Pin Name                  |                             |                                                                       |              | l pull-up  | /down resistor)         |  |  |

|                           | SCK (with int               |                                                                       | or)          |            |                         |  |  |

| Туре                      | CMOS I/O, TT                |                                                                       |              | 1          |                         |  |  |

| High level input voltage  | V <sub>IH</sub>             | 2.0                                                                   |              | V          |                         |  |  |

| Low level input voltage   | $V_{IL}$                    |                                                                       | 0.8          | V          |                         |  |  |

| Input voltage hysteresis  |                             | 0.3                                                                   |              | V          |                         |  |  |

| Input high current        | I <sub>IH</sub>             | -1                                                                    | +1           | μA         |                         |  |  |

| Input low current         | I <sub>IL</sub>             | -1                                                                    | +1           | μA         |                         |  |  |

| High level output voltage |                             | V <sub>PERI</sub> -0.4V                                               |              | V          | I <sub>out</sub> = 3 mA |  |  |

| Low level output voltage  |                             |                                                                       | 0.4          | V          | I <sub>out</sub> = 3 mA |  |  |

| Tri state output current  |                             | -1                                                                    | +1           | μA         |                         |  |  |

| Pin Name                  | xAsic_Reset<br>SDA (without | t internal res                                                        | istor)       |            |                         |  |  |

| Туре                      | CMOS open of                | drain output w                                                        | ith Schmitt  | Trigger in | nput, TTL level         |  |  |

| High level input voltage  | V <sub>IH</sub>             | 2.0                                                                   |              | V          |                         |  |  |

| Low level output voltage  | V <sub>OH</sub>             |                                                                       | 0.4          | V          | I <sub>out</sub> = 3mA  |  |  |

| Low level input voltage   | $V_{IL}$                    |                                                                       | 0.8          | V          |                         |  |  |

| Input voltage hysteresis  |                             | 0.3                                                                   |              | V          |                         |  |  |

| OFF state output current  |                             | -1                                                                    | +1           | μA         |                         |  |  |

## **Electrical Characteristics for Analog I/O Pads**

| PARAMETER                             | MIN   | MAX    | UNIT | REMARKS                                                                    |

|---------------------------------------|-------|--------|------|----------------------------------------------------------------------------|

| Pin Name                              | VPOR' | T_POSx |      |                                                                            |

| Operating voltage                     | 44    | 62     | V    |                                                                            |

| Pin current consumption               | -5    | +10    | μΑ   | Port driver, Vport measurement and AC generator are off                    |

| Pin Name                              | VPOR' | T_NEGx | ,    |                                                                            |

| Operating voltage                     | 0     | Vmain  | V    | Port driver, V <sub>port</sub> measurement and AC generator are off        |

| Pin current consumption               | -5    | +10    | μΑ   | ·                                                                          |

| Pin Name                              | Vmain |        |      |                                                                            |

| Operating voltage – AF mode           | 40    | 57     | V    | Recommended Range 48v to 55v                                               |

| Operating voltage – AT mode           | 50    | 57     | V    | Recommended Range 51v to 55v                                               |

| V <sub>main</sub> current consumption |       | 40     | mΑ   | Total on V <sub>main</sub>                                                 |

| Pin Name                              | 3_3Vo | ut     |      |                                                                            |

| Voltage                               | 3.13  | 3.46   | V    |                                                                            |

| Output current                        |       | 6      | mΑ   | Without external NPN (see Q1 in Figure 8)                                  |

|                                       |       | 30     | mΑ   | When using external NPN for V <sub>PERI</sub> (see Q1 in <b>Figure 8</b> ) |

Copyright © 2009 *Microsemi* Page Rev. 1.0 / 17-March-10 Analog Mixed Signal Group

## Dynamic Characteristics

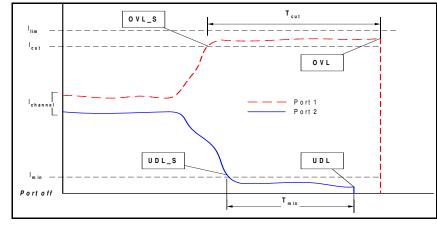

The PD671xxx DIMMs utilize three programmable current level thresholds ( $I_{min}$ ,  $I_{cut}$ ,  $I_{lim}$ ) and two timers ( $T_{min}$ ,  $T_{cut}$ ), to operate as shown in Figure 4. Loads that consume more than  $I_{cut}$  for longer than  $T_{cut}$  (OVL\_S to OVL) are categorized as 'overloads' and are automatically shutdown. Automatic recovery from overload and no-load conditions is attempted every  $T_{OVLREC}$  and  $T_{UDLREC}$  periods (typically 5 and 1 seconds, respectively). Output current is limited to  $I_{lim}$ , which is the maximum peak current allowed at each port.

## **DC Disconnect**

Output current consumption below  $I_{min}$  for more than  $T_{PMDO}$  (UDL\_S to UDL) is categorized as 'no-load' and is shutdown.

## **AC Disconnect**

A port maintains power if Zac < 27 K $\Omega$

A port shutdowns power if Zac > 1980 K $\Omega$  for a time period greater than TPMDO.

| PARAMETER                               | CONDITIONS         |                                                                                            | MIN. | TYP. | MAX. | UNIT |

|-----------------------------------------|--------------------|--------------------------------------------------------------------------------------------|------|------|------|------|

| Automatic recovery from                 | (can be            | c value, measured from port shutdown e modified via control port)                          |      | 5    |      | s    |

| Automatic recovery from no-             |                    | can be modified via control port)                                                          |      | 1    |      | s    |

| Inrush current                          | I <sub>Inrsh</sub> | For t = 50 ms, C <sub>load</sub> =180 uF max.                                              |      |      | 750  | mA   |

| Output current operating range          | I <sub>port</sub>  | Continuous operation after startup period                                                  | 10   |      | 700  | mA   |

| Output power available, operating range | P <sub>port</sub>  | Continuous operation after startup period, at port output (@ Vport = 57 VDC)               | 0.57 |      | 30   | W    |

| DC disconnect                           | I <sub>min1</sub>  | Must disconnect for t greater than T <sub>UVL</sub>                                        | 0    |      | 5    | mA   |

| OFF mode                                | I <sub>min2</sub>  | May or may not disconnect for t greater than T <sub>UVL</sub>                              | 5    | 7.5  | 10   | mA   |

| AC Disconnect                           | Zac1               | Does not remove power                                                                      |      |      | 27   | KΩ   |

| OFF mode                                | Zac2               | Remove power                                                                               | 1980 |      |      | KΩ   |

| PD power maintenance                    | $T_{PMD}$          | Buffer period to handle transitions                                                        | 300  |      | 400  | ms   |

| Over load current detection range       | I <sub>cut</sub>   | Time limited to T <sub>OVL</sub>                                                           | 660  | 680  | 700  | mA   |

| Over load time limit                    | T <sub>OVL</sub>   | Typical timer accuracy is 2 ms                                                             | 50   |      | 75   | ms   |

| Turn on rise time                       | T <sub>rise</sub>  | From 10% to 90% of V <sub>port</sub> (specified for PD load consisting of 100 uF capacitor | 15   |      |      | us   |

| Port turn off time                      | Toff               | From V <sub>port</sub> to 5 Vdc                                                            |      |      | 500  | ms   |

Figure 4: Power Limits

## Data Sheet (Non-confidential)

## Pin Designations \_\_\_\_

The PD671xxx DIMMs have a fit/form based on a JEDEC MO-161f outline.

## Conventions used in the design are as follows:

- Power and ground connections are reproduced a number of times to carry heavy currents.

- Signals are categorized as analog (input or output) or digital (input, output and I/O).

- All lines which are identified with an "x" prefix are active when logical is low.

Refer to Figure 5.

Figure 5: Pinout

## **Pin Description**

Signals are categorized as 'analog' (input or output) or 'digital' (input, output and I/O).

| Channel 11 negative output   Channel 12 positive output   Channel 12 positive output   Channel 12 positive output   Channel 12 positive output   Channel 12 negative output   Chanle output   Channel 12 negative output   Chanle output   Channel 12 negative output   Channel 12 negative output   Chanle output   C   | Pin      | Pin Name    | Pin Type       | Pin Description                        | Pin | Pin       | Pin Type      | Pin Description                  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------|----------------|----------------------------------------|-----|-----------|---------------|----------------------------------|--|--|

| Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1        |             |                |                                        | 05  | Name      |               |                                  |  |  |

| Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <u> </u> |             |                |                                        |     |           |               |                                  |  |  |

| Power input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2        |             |                |                                        | 86  |           |               |                                  |  |  |

| Power input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3        | Vmain       |                | Main V+ input                          | 87  | Vmain     |               | Main V+ input                    |  |  |

| Fig.   Power input   Power input   Fig.   Power input   Power i   |          |             |                |                                        |     |           |               |                                  |  |  |

| Vmain_ret                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |             | Dower input    |                                        |     | =         | Dower input   |                                  |  |  |

| Nain V return   Section    |          |             | Power input    |                                        |     |           | rowei iliput  |                                  |  |  |

| Main V return                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |             |                |                                        |     |           |               |                                  |  |  |

| 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ^        |             |                |                                        |     |           |               |                                  |  |  |

| 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          | Vmain_ret   |                | Main V return                          |     | Vmain_ret |               | Main V return                    |  |  |

| 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |             |                |                                        |     |           |               |                                  |  |  |

| Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 12       |             |                |                                        | 96  |           |               |                                  |  |  |

| Fig.   Port, P1   Port P2   Port, P3   Port, P3   Port, P4   Port, P4   Port, P4   Port, P5   Port, P6   Port, P7   Port, P8   Port, P8   Port, P9   Port, P8   Port, P9   Por   |          | _           |                |                                        |     |           |               |                                  |  |  |

| Channel 2 negative output   100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |             |                |                                        |     |           |               |                                  |  |  |

| The   Port   P   |          | _           |                |                                        |     |           |               |                                  |  |  |

| Record   Port N2   Port N3   Port N3   Port N4   Port N4   Port N5   Port N4   Port N5   Port N5   Port N6   Port    |          |             |                |                                        |     |           |               |                                  |  |  |

| Port P3   Port P4   Port P4   Port P4   Port P4   Port P5   Port P6   Port P6   Port N4   Port P6   Port N6   Port N7   Port N6   Port N6   Port N6   Port N7   Port N6   Port N6   Port N6   Port N6   Port N7   Port N6   Port N6   Port N7   Port N6   Port N6   Port N7   Port N6   Port N7   Port N6   Port N7   Port N6   Port N7   Port N6   Port N6   Port N7   Port N6   Port N6   Port N7   Port N6   Port N6   Port N6   Port N7   Port N6   Port N6   Port N7   Port N6   Port   |          |             |                |                                        |     |           |               |                                  |  |  |

| Port_P4   Port_N5   Port_P5   Port_P6   Port_P6   Port_P6   Port_P7   Port_P7   Port_P7   Port_P8   Port_P9   Port_P8   Port_P9   Port_P10   Port_P9   Port_P9   Port_P10   P   |          | Port_P3     |                |                                        |     |           |               |                                  |  |  |

| Port_P4   Port_N4   Port_N5   Port_P6   Port_P6   Port_P6   Port_P6   Port_P6   Port_P7   Port_P7   Port_P7   Port_P8   Port_P9   Port_P10   Port_P9   Port_P10   Port_P9   Port_P10   Po   |          |             |                |                                        |     | Spare     |               |                                  |  |  |

| Channel 6 positive output   107   108   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   109   100   109   109   109   100   109   109   100   109   109   100   100   100   109   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100   100      |          |             |                |                                        |     |           |               |                                  |  |  |

| Port_N6    Port_N7    Port_N8    30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |             |                |                                        |     |           |               |                                  |  |  |

| Analog output   Channel 7 positive output   109   Channel 8 positive output   111   Channel 8 positive output   112   Channel 8 positive output   112   Channel 8 positive output   112   Channel 8 positive output   113   TBD      |          |             |                |                                        |     |           |               |                                  |  |  |

| Channel 7 negative output   100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |             | Analog output  |                                        |     |           |               |                                  |  |  |

| Channel 8 negative output   112     Channel 9 positive output   113   TBD      |          |             |                |                                        | 100 |           |               |                                  |  |  |

| Channel 9 positive output   113   TBD      |          |             |                |                                        |     |           |               |                                  |  |  |

| Channel 9 negative output   114   TBD      |          |             |                |                                        |     | TDD       |               | Tee                              |  |  |

| Channel 10 positive output   115   TBD     |          |             |                |                                        |     |           |               |                                  |  |  |

| Channel 10 negative output   116   TBD   TBD   Auto mode; sets I2C at 2   Auto mode; sets I2C at 3     |          |             |                |                                        |     |           |               |                                  |  |  |

| Channel 11 positive output   Channel 11 positive output   Channel 11 negative output   Channel 11 negative output   Channel 12 positive output   Channel 12 negative output   Channel 12 neg   |          |             |                |                                        |     |           |               |                                  |  |  |

| Channel 12 positive output   Channel 12 positive output   Channel 12 negative output   Channel 12 neg   |          |             |                | Channel 11 positive output             | 117 | I2C_Addr_ | Digital input |                                  |  |  |

| Channel 12 negative output   120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          | _           |                |                                        |     |           |               |                                  |  |  |

| TBD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          | _           |                |                                        |     |           |               | ut NC (not in use)               |  |  |

| TBD    | 36       | Ροπ_Ν11     |                | Channel 12 negative output             | 120 |           | _             | CCDI address                     |  |  |

| TBD  TBD  TBD  TBD  TBD  TBD  TBD  TBD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.7      | TBD         |                | TBD                                    | 101 |           | — Analog outp | ut Lor raddress                  |  |  |

| ASICINI_4_Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 37       |             |                |                                        | 121 |           | -             |                                  |  |  |

| Analog output Out ASICINI_5_Out Analog output Asicini_5_Out Analog output Asicini_5_Out Analog output Determine DIMM 1 manager Analog output Analog output Determine DIMM 1 managers Analog  | 38       | TBD         |                | TBD                                    | 122 | xExist    | Digital outpo |                                  |  |  |

| Analog output  Analog |          | ACICINII 4  |                | Determine DIMM 2 managers              |     | Ext rog   | Analog outn   | P                                |  |  |

| Analog output Out Analog output Out | 39       |             |                |                                        | 123 | EXI_leg   | Arialog outp  | ut External regulation for 3.3 v |  |  |

| Out    A   Couplers    | 40       |             | Analog output  |                                        | 104 | 3_3Vout   | Analog outp   | ut 3.3 V output to support opto  |  |  |

| TBD    | 40       | Out         |                |                                        |     |           |               | couplers (5 V tolerant)          |  |  |

| BKGD   Digital input   Factory use only   127   SCK   Digital I/O   SPI clock - PD69012   comm   128   MISO   Digital I/O   SPI I/O - PD69012 in comm   128   MISO   Digital I/O   SPI I/O - PD69012 in comm   128   MISO   Digital I/O   SPI I/O - PD69012 in comm   129   MOSI   Digital I/O   SPI I/O - PD69012 in comm   129   MOSI   Digital I/O   SPI I/O - PD69012 in comm   130   ASICINI_0   Analog input   Determine DIMM material in   Asicinity   Analog output   Determine DIMM 1 manager   131   Asicinity   Analog input   Determine DIMM material in   SPI address   132   CSO   Digital I/O   CS for ESPI   133   CSO   Digital I/O   CS for ESPI   134   CSO   Digital I/O   CS for ESPI   135   CSO   Digital I/O   CS for ESPI   136   CSO   Digital I/O   CS for ESPI   137   CSO   Digital I/O   CS for ESPI   137   CSO   Digital I/O   CS for ESPI   138   CSO   Digital I/O   CS for ESPI   139   CSO   Digital I/O   CS for ESPI   130   CSO   |          |             | Digital output |                                        |     |           |               |                                  |  |  |

| 44 DGND Ground Digital ground  45 XAsic_Reset Digital I/O Internal reset to PD69012  46 XReset_In Digital input A reset signal driven by the Host CPU to PoE DIMM  47 ASICINI_0_ Out Analog output Determine DIMM 1 manager SPI address  48 ASICINI_1 Analog output Determine DIMM 1 managers  49 Analog output Determine DIMM 1 managers SPI address  40 Digital I/O SPI I/O - PD69012 in comm  41 ASICINI_0 Analog input Determine DIMM manager SPI address  41 Analog output Determine DIMM 1 managers SPI address  42 CS0 Digital I/O CS for ESPI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |             | Digital issue  |                                        |     |           |               | ŭ ŭ                              |  |  |

| 44 DGND Ground Digital ground  128 MISO Digital I/O SPI I/O – PD69012 in comm  45 XAsic_Reset Digital I/O Internal reset to PD69012  46 XReset_In Digital input A reset signal driven by the Host CPU to PoE DIMM  47 ASICINI_0_ Out Analog output ESPI address  48 ASICINI_1_ Analog output Determine DIMM 1 managers  48 ASICINI_1_ Analog output Determine DIMM 1 managers  49 Analog output Determine DIMM 1 managers  40 Digital I/O SPI I/O – PD69012 in comm  410 ASICINI_0_ Analog input Determine DIMM managers  411 ASICINI_1_ Analog input Determine DIMM managers  412 Analog output Determine DIMM 1 managers  413 CS0 Digital I/O CS for ESPI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 43       | DVGD        | וטוgıtaı input | ractory use only                       | 127 | SUK       | Digital I/O   |                                  |  |  |

| 45 XAsic_Reset Digital I/O Internal reset to PD69012 129 MOSI Digital I/O SPI I/O – PD69012 in comm  46 XReset_In Digital input A reset signal driven by the Host CPU to PoE DIMM 130 ASICINI_0 Analog input ESPI address  47 ASICINI_0 Analog output Determine DIMM 1 manager ESPI address  48 ASICINI_1 Analog output Determine DIMM 1 managers 132 CS0 Digital I/O CS for ESPI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 44       | DGND        | Ground         | Digital ground                         | 128 | MISO      | Digital I/O   | SPI I/O – PD69012 internal       |  |  |