# 2 GHz to 6 GHz, 45 dBm Power Amplifier

Data Sheet HMC7885

#### **FEATURES**

2 GHz to 6 GHz

21 dB typical small signal gain

45 dBm typical saturated RF output power (Pout)

18-lead, hermetically sealed module

-30°C to +60°C operating temperature

#### **APPLICATIONS**

Test and measurement equipment

Communications

Electronic warfare (EW)

Military

Traveling wave tube (TWT) replacements

SATCOM

Commercial and military radars

#### **GENERAL DESCRIPTION**

The HMC7885 is a 32 W gallium nitride (GaN), monolithic microwave integrated circuit (MMIC) power amplifier (PA) module that operates between 2 GHz and 6 GHz, and is provided in an 18-lead hermetically sealed module. The amplifier typically provides 21 dB of small signal gain and 45 dBm of saturated radio frequency (RF) output power. The amplifier draws 2200 mA of quiescent current ( $\rm I_{\rm DD}$ ) from a 28 V dc supply. The RF input and output are dc blocked and matched to 50  $\Omega$  for ease of use.

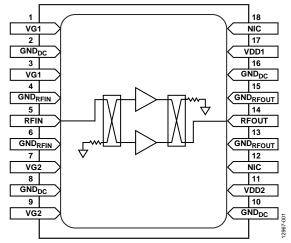

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

## **TABLE OF CONTENTS**

| Features                 | l |

|--------------------------|---|

| Applications             | 1 |

| General Description      | 1 |

| Functional Block Diagram | 1 |

| Revision History         |   |

| Specifications           |   |

| Absolute Maximum Ratings |   |

| ESD Caution              |   |

| riii Connguration and runction Descriptions |      |

|---------------------------------------------|------|

| C I                                         |      |

| Typical Performance Characteristics         | (    |

| Applications Information                    |      |

| Evaluation Board Assembly                   | . 10 |

| Bill of Materials                           | . 10 |

| Outline Dimensions                          | . 1  |

| Ordering Guide                              | . 1  |

#### **REVISION HISTORY**

1/2017—Revision 0: Initial Version

### **SPECIFICATIONS**

VDD = VDD1 = VDD2 = 28 V dc, VGG = VG1 = VG2,  $T_A = 25^{\circ}$ C, unless otherwise noted. Adjust VGG between -5 V to 0 V to achieve a total  $I_{DD} = 2200 \text{ mA}$  typical (1100 mA per side).

Table 1.

| Parameter                                  | Min | Тур | Max | Unit | Test Conditions/Comments                         |

|--------------------------------------------|-----|-----|-----|------|--------------------------------------------------|

| FREQUENCY RANGE                            | 2   |     | 6   | GHz  |                                                  |

| GAIN                                       |     |     |     |      |                                                  |

| Small Signal Gain                          |     | 21  |     | dB   |                                                  |

| Power Gain                                 |     | 17  |     | dB   |                                                  |

| Gain Flatness                              |     | ±2  |     | dB   |                                                  |

| VOLTAGE STANDING WAVE RATIO (VSWR)         |     |     |     |      |                                                  |

| Input                                      |     | 2:1 |     |      |                                                  |

| Output                                     |     | 2:1 |     |      |                                                  |

| RF OUTPUT                                  |     |     |     |      |                                                  |

| Saturated Output Power (P <sub>SAT</sub> ) |     | 45  |     | dBm  | 5 dB compression with continuous wave (CW) input |

| Output Power for 1 dB Compression (P1dB)   |     | 39  |     | dBm  |                                                  |

| Output Third-Order Intercept (IP3)         |     | 53  |     | dBm  |                                                  |

| Linear Power Output                        |     | 34  |     | dBm  |                                                  |

| POWER ADDED EFFICIENCY (PAE)               |     | 25  |     | %    | At P <sub>SAT</sub>                              |

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 2.

| Parameter                              | Rating            |

|----------------------------------------|-------------------|

| Drain Bias Voltage (VDD1, VDD2)        | 32 V              |

| Gate Bias Voltage (VG1, VG2)           | –8 V dc to 0 V dc |

| RF Input (RFIN) Power                  | 36 dBm            |

| Operating Temperature <sup>1</sup>     | −30°C to +60°C    |

| Junction Temperature (T <sub>J</sub> ) | 225°C             |

| Storage Temperature <sup>2</sup>       | −65°C to +150°C   |

<sup>&</sup>lt;sup>1</sup> For operation with a continuous wave input.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

<sup>&</sup>lt;sup>2</sup>This device is not surface mountable and is not intended nor suitable for use in a solder reflow process. This device must not be exposed to ambient temperatures above 150°C.

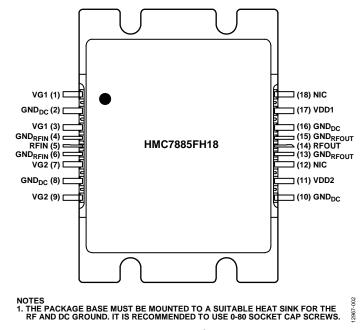

### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pin Configuration

**Table 3. Pin Function Descriptions**

| Pin No.      | Mnemonic             | Description                                                                                                                         |  |  |  |

|--------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1            | VG1                  | Supply Voltage for MMIC 1 Gates. This pin is typically –1.3 V dc. Pin 1 is connected internally to Pin 3                            |  |  |  |

| 2            | $GND_DC$             | Power Supply Ground.                                                                                                                |  |  |  |

| 3            | VG1                  | upply Voltage for MMIC 1 Gates. This pin is typically –1.3 V dc. Pin 3 is connected internally to Pin 1.                            |  |  |  |

| 4            | GND <sub>RFIN</sub>  | Finput Ground.                                                                                                                      |  |  |  |

| 5            | RFIN                 | RF Input. This pin is dc-coupled and matched to 50 $\Omega$ .                                                                       |  |  |  |

| 6            | GND <sub>RFIN</sub>  | RF Input Ground.                                                                                                                    |  |  |  |

| 7            | VG2                  | Supply Voltage for MMIC 2 Gates. This pin is typically –1.3 V dc. Pin 7 is connected internally to Pin 9.                           |  |  |  |

| 8            | $GND_DC$             | Power Supply Ground.                                                                                                                |  |  |  |

| 9            | VG2                  | Supply Voltage for MMIC 2 Gates. This pin is typically –1.3 V dc. Pin 9 is connected internally to Pin 7.                           |  |  |  |

| 10           | $GND_DC$             | Power Supply Ground.                                                                                                                |  |  |  |

| 11           | VDD2                 | Supply Voltage for MMIC 2 Drains.                                                                                                   |  |  |  |

| 12           | NIC                  | Not Internally Connected. However, this pin can be connected externally to the RF and/or dc ground.                                 |  |  |  |

| 13           | GND <sub>RFOUT</sub> | RF Output Ground.                                                                                                                   |  |  |  |

| 14           | RFOUT                | RF Output. This pin is ac-coupled and matched to 50 $\Omega$ .                                                                      |  |  |  |

| 15           | GND <sub>RFOUT</sub> | RF Output Ground.                                                                                                                   |  |  |  |

| 16           | $GND_DC$             | Power Supply Ground.                                                                                                                |  |  |  |

| 17           | VDD1                 | Supply Voltage for MMIC 1 Drains.                                                                                                   |  |  |  |

| 18           | NIC                  | Not Internally Connected. However, this pin can be connected externally to the RF and/or dc ground.                                 |  |  |  |

| Package Base | GND                  | The package base must be mounted to a suitable heat sink for the RF and dc ground. It is recommended to use 0-80 socket cap screws. |  |  |  |

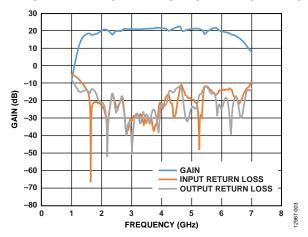

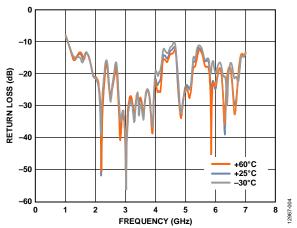

### TYPICAL PERFORMANCE CHARACTERISTICS

Figure 3. Gain and Input/Output Return Loss vs. Frequency

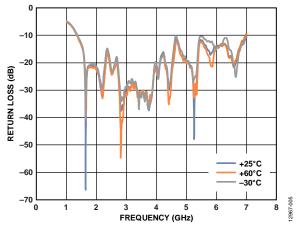

Figure 4. Output Return Loss vs. Frequency at Various Temperatures

Figure 5. Input Return Loss vs. Frequency at Various Temperatures

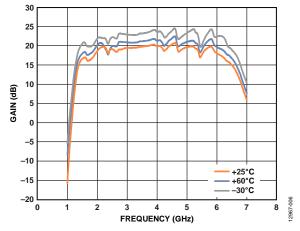

Figure 6. Gain vs. Frequency at Various Temperatures

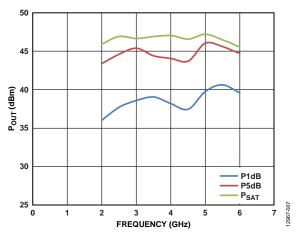

Figure 7.  $P_{OUT}$  vs. Frequency for P1dB, Output Power for 5 dB Compression (P5dB), and  $P_{SAT}$

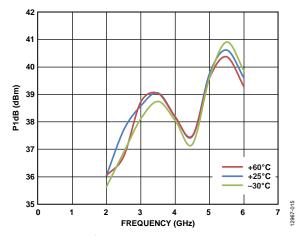

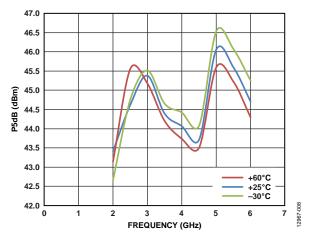

Figure 8. P1dB vs. Frequency at Various Temperatures

Figure 9. P5dB vs. Frequency at Various Temperatures

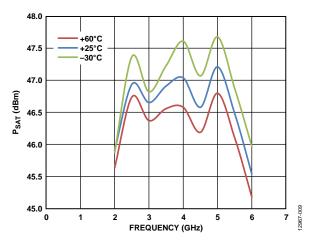

Figure 10. P<sub>SAT</sub> vs. Frequency at Various Temperatures

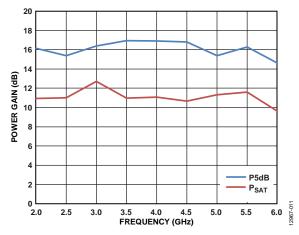

Figure 11. Power Gain vs. Frequency for P5dB and PSAT

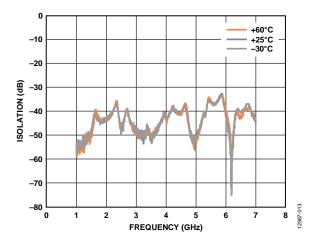

Figure 12. Reverse Isolation vs. Frequency at Various Temperatures

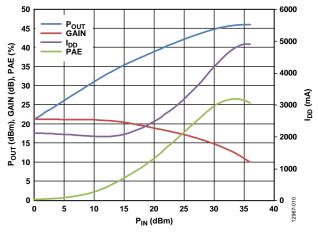

Figure 13. Power Compression at 2 GHz

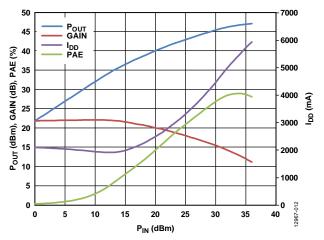

Figure 14. Power Compression at 4 GHz

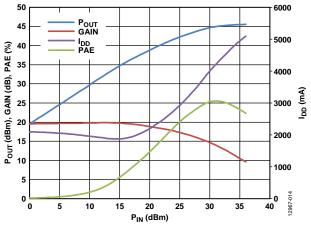

Figure 15. Power Compression at 6 GHz

### **APPLICATIONS INFORMATION**

To turn on the amplifier, complete the following steps:

- 1. Set VG1 and VG2 to −5 V.

- 2. Set VDD1 and VDD2 to +28 V.

- 3. Ramp the gate voltage until the quiescent current ( $I_{DD}$ ) = 1100 mA per side (2200 mA total).

- 4. Apply the RF input power.

To turn off the amplifier, complete the following steps:

- 1. Remove the RF input power.

- 2. Set VG1 and VG2 to −5 V.

- 3. Set VDD1 and VDD2 to 0 V.

- 4. Set VG1 and VG2 to 0 V.

### **EVALUATION BOARD ASSEMBLY**

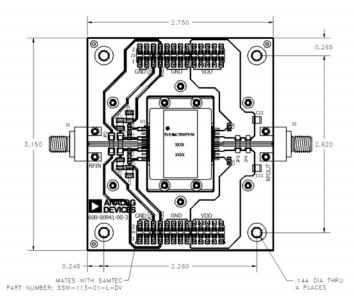

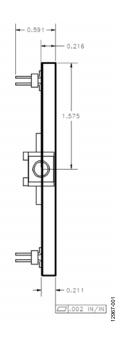

Figure 16. Evaluation Fixture

#### **BILL OF MATERIALS**

Use RF circuit design techniques for the circuit board used in the application. Provide 50  $\Omega$  impedance for the signal lines, and connect the package ground leads and package base directly to the ground plane. DC bias voltages can be applied through either J3 or J4. The evaluation board shown is available from Analog Devices, Inc., upon request.

Table 4. Bill of Materials for Evaluation Board Assembly EV1HMC7885FH18

| ltem       | Description                                                                               |

|------------|-------------------------------------------------------------------------------------------|

| J1, J2     | SMA jack                                                                                  |

| J3, J4     | DC, 0.1" terminal strip                                                                   |

| JP1 to JP4 | 6.9 mm, SMT jumper                                                                        |

| C1 to C6   | 1 μF capacitors, 0603 package                                                             |

| C7 to C10  | 10 μF capacitor, 1210 package                                                             |

| U1         | HMC7885FH18                                                                               |

| PCB        | 600-00941-00 evaluation printed circuit board (PCB); circuit board material: Rogers 4350B |

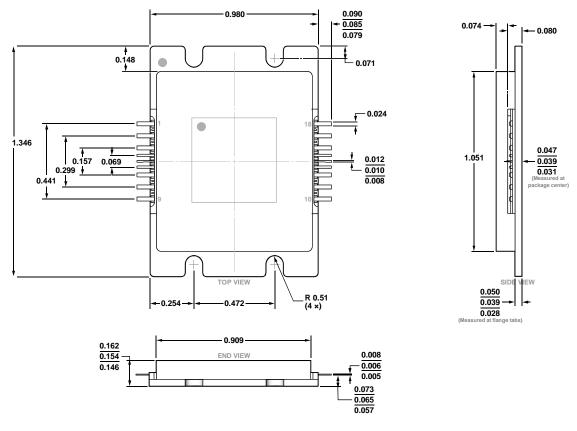

## **OUTLINE DIMENSIONS**

Figure 17. 18-Lead Multichip Module Hermetic Ceramic/Metal Package [CM] (MC-18-1) Dimensions shown in inches

#### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                                          | Package Option |

|--------------------|-------------------|--------------------------------------------------------------|----------------|

| HMC7885FH18        | −30°C to +60°C    | 18-Lead Multichip Module Hermetic Ceramic/Metal Package [CM] | MC-18-1        |

| EV1HMC7885FH18     |                   | Evaluation Board                                             |                |

<sup>&</sup>lt;sup>1</sup> The HMC7885FH18 is an RoHS-compliant part.