### Single-channel Voltage/Current Monitors and Voltage Marginers

### **FEATURES & APPLICATIONS**

- Capable of margining supplies with trim inputs using • either positive or negative trim pin control

- Wide Margin range of 0.3V to VDD with internal . reference

- Differential Voltage Sensing of the DC-DC converter . output voltage

- Supply-side current monitoring (10-bit ADC) •

- 10-bit ADC readout of supply voltage over I<sup>2</sup>C bus

- Margining Controlled Via: •

- I<sup>2</sup>C Command

- Input Pins (MUP, MDN)

- Two programmable general purpose sensor inputs ٠ (COMP1/2) – UV/OV with FAULT Output

- Programmable glitch filters (COMP1/2)

- Programmable internal COMP1/2 VREF: 0.5V or 1.25V •

- Operates from 2.7V to 5.5V supply .

- Current sensing from 4.0V to 15V supply .

- Programmable, general purpose I/Os (SMM152) ٠

- General Purpose 256-Byte EEPROM with Write Protect

- I<sup>2</sup>C 2-wire serial bus for programming configuration and monitoring status

- 28-lead 5x5 QFN

#### Applications

•

- In-system test and control of Point-of-Load (POL)

- Power Supplies for Multi-voltage Processors, DSPs and ASICs

- Routers, Servers, Storage Area Networks

TYPICAL APPLICATION

#### 4.0V-15V $R_s$ 2.7V-5.5V> VDĎ CAPC COMP1 cs--Ŷ V1 CS+ Margin COMP2 Commands Š VREF VIN FAULT# D-Status VOUT+ -**SMM151** READY 🗅 Outputs SEN-SDA 🗗 (SMM152) TRIM TRIM 1<sup>2</sup>C SCL T-VOUT-Interface A0-A2 -CAPM+ SEN--D-WP D-**DC-DC Converter** (GPIO0) -(GPIO1) 🗅

#### Figure 1 – Application with the SMM151/152 used to Monitor and Margin a DC/DC Converter.

(GPIO2) 🗆

(GPIO3) 🗆

Notes: Rs must be Kelvin sensed for maximum current sensing accuracy. This is an applications example only. Some components and values are not shown.

VM+

₩.

INTRODUCTION

SMM151/152 are highly accurate power The supply voltage/current supervisors and monitors with provisions for voltage margining of the monitored supply. The parts include an internal voltage reference to accurately monitor and margin the supply to within ±1%. The SMM151/152 have the capability to margin over a wide range from 0.3V to VDD using the internal reference and can read the differential voltage of the supply and voltage drop of the current sense resistor over the I<sup>2</sup>C bus using an on-chip 10-bit ADC. The margin levels are set using the I<sup>2</sup>C serial bus. The devices initiate margining via the I<sup>2</sup>C bus or by using the MUP or MDN inputs. Once the preprogrammed margin target voltage is reached, the SMM151/152 hold the converter at this voltage until receiving an I<sup>2</sup>C command or de-asserting the margin input pin. When the SMM151/152 are not margining, the TRIM output pin is held in a high impedance state allowing the converter to operate at its nominal set point.

Two general purpose input pins are provided for sensing under or over-voltage conditions. A programmable glitch filter associated with these inputs allows the user to ignore spurious noise signals. A FAULT# pin is asserted once either input set point is exceeded. The SMM152 also provides four programmable general-purpose inputs/outputs.

Using the I<sup>2</sup>C interface, a host system can communicate with the SMM151/152 status register and utilize 256-bytes of nonvolatile memory.

### **GENERAL DESCRIPTION**

The SMM151 and SMM152 are capable of margining the DC output voltage of LDOs or DC/DC converters that use a trim/adjust pin. The Margin function is programmable over a standard 2-wire I<sup>2</sup>C serial data interface and is used to set the margin low/high DC output voltages. The devices are also capable of monitoring the differential output voltage and the input current of DC/DC converters, thereby providing real-time power information to the system.

In margining mode the user communicates with the SMM151/152 via the I<sup>2</sup>C serial data bus to select the desired values for margining. This allows the part to margin the supplies up or down to these set values either through asserting the MUP and MDN pins or by writing to the margin register directly. The margin high and margin low voltage settings can range from 0.3V to VDD around the converter's nominal output voltage setting depending on the specified margin range of the DC-DC converter and/or system components, usually ±10%. The SMM151/152 also feature a margin nominal command and set-point. This can be used to set the converter's nominal output voltage to a more accurate value than is attainable without margining due to inaccuracy of the standalone converter and its voltage setting components.

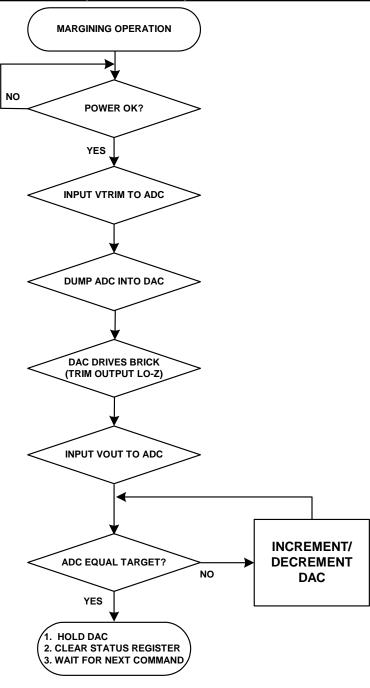

When the SMM151/152 receive the command to margin, the TRIM output will begin adjusting the supply to the selected margin voltage. This is accomplished by incrementing (or decrementing) an internal counter based on the digital comparison between the voltage margin target value and that read by the ADC from the VM+ - VM- differential input. This operation is repeated until the 2 values are equal, after which the SMM151/152 hold the TRIM output pin at the voltage required to maintain the margin setting. An I<sup>2</sup>C command or de-assertion of the MUP/MDN pin will return the TRIM output pin to a high impedance state thus allowing the converter to return to its nominal operating voltage.

The SMM151 and SMM152 sense converter input current using a Kelvin connected sense resistor in series with the converter supply whose terminals are connected to the CS+ and CS- pins. The internal ADC, also used for measuring the converter's output voltage, is used to measure the converter's input current using the voltage dropped across the current sense resistor  $R_s$  (see Figure 1).

The SMM151/152 have two additional input pins and one additional output pin. The input pins, COMP1 and COMP2, are high impedance inputs, each connected to a comparator and compared against the internal reference (VREF: 0.5V or 1.25V). Each comparator can be independently programmed to monitor for UV or OV. When either of the COMP1 or COMP2 inputs are in fault the open-drain FAULT# output will be pulled low. A configuration option exists to disable the FAULT# output during margining.

The SMM152 also provides four programmable generalpurpose inputs/outputs. The power-on state of these I/Os is determined via non-volatile (NV) memory. Volatile programming allows the user to select the logic level (HIGH or LOW) of each I/O, which can also be read via a status register.

Programming of the SMM151/152 is performed over the industry standard  $I^2C$  2-wire serial data interface. A status register is available to read the state of the part and a Write Protect (WP) pin is available to prevent writing to the configuration registers and EE memory.

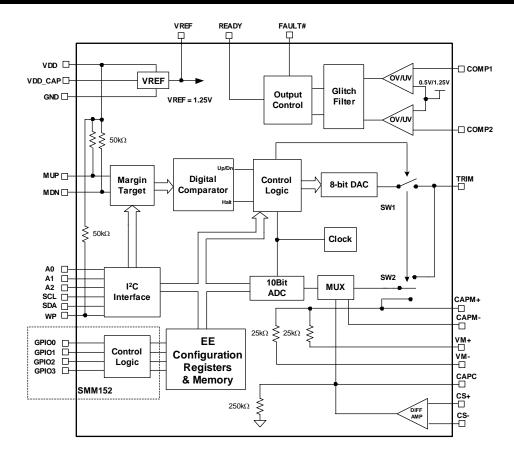

## **INTERNAL BLOCK DIAGRAM**

Figure 2 – SMM151 and SMM152 Controller Internal Block Diagram.

## PIN DESCRIPTIONS

| Pin         Pin           Number         Type   Pin Name Pin Description |      |             | Pin Description                                                                                                                                                                                                          |  |

|--------------------------------------------------------------------------|------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                          | Туре |             |                                                                                                                                                                                                                          |  |

| 28                                                                       | I/O  | SDA         | I <sup>2</sup> C Bi-directional data line                                                                                                                                                                                |  |

| 1                                                                        | Ι    | SCL         | I <sup>2</sup> C clock input.                                                                                                                                                                                            |  |

| 2                                                                        | I    | A2          | The address pins are biased either to VDD, GND or left floating. This allows                                                                                                                                             |  |

| 4                                                                        |      | A1          | for a total of 21 distinct device addresses. When communicating with the SMM151/2 over the 2-wire bus these pins provide a mechanism for                                                                                 |  |

| 6                                                                        | Ι    | A0          | assigning a unique bus address.                                                                                                                                                                                          |  |

| 0 0 00 07                                                                | I/O  | GPIO0,1,2,3 | SMM152: General purpose inputs/outputs.                                                                                                                                                                                  |  |

| 3, 9, 22, 27                                                             | NC   | NC          | SMM151: No Connect.                                                                                                                                                                                                      |  |

| 8                                                                        | I    | WP          | Programmable Write Protect active high/low input. When asserted, writes to the configuration registers and general purpose EE are not allowed. The WP input is internally tied to VDD with a $50K\Omega$ resistor.       |  |

| 10, 13                                                                   | CAP  | CAPM+, -    | External capacitor inputs used to filter the VM+/VM- inputs, $0.22\mu$ F.                                                                                                                                                |  |

| 20                                                                       | 0    | TRIM        | Output voltage used to control and/or margin converter voltages. Connect to the converter trim input.                                                                                                                    |  |

| 14                                                                       | Ι    | VM+         | Voltage monitor input. Connect to the DC-DC converter positive sense line or its +Vout pin.                                                                                                                              |  |

| 15                                                                       | Ι    | VM-         | Voltage monitor input. Connect to the DC-DC converter negative sense line or its -Vout pin.                                                                                                                              |  |

| 18                                                                       | Ι    | CS+         | Current monitor input + side. Kelvin connect to the input supply side of the current sense resistor.                                                                                                                     |  |

| 17                                                                       | Ι    | CS-         | Current monitor input - side. Kelvin connect to the load side of the current sense resistor.                                                                                                                             |  |

| 26                                                                       | PWR  | VREF        | Internal reference voltage of 1.25V. Connect to GND through a 0.1uF capacitor to improve noise immunity.                                                                                                                 |  |

| 16                                                                       | 0    | CAPC        | External capacitor input used to filter the CS+/CS- input. Typical value: 1uF.                                                                                                                                           |  |

| 21                                                                       | PWR  | VDD         | Power supply of the part.                                                                                                                                                                                                |  |

| 23                                                                       | PWR  | VDD_CAP     | External capacitor input used to filter the internal VDD supply rail.                                                                                                                                                    |  |

| 7                                                                        | GND  | GND         | Ground of the part. The SMM151/2 ground pin should be connected to the ground of the device under control or to a star point ground. PCB layout should take into consideration ground drops.                             |  |

| 24                                                                       | Ι    | MUP         | Margin up command input. Asserted high. The MUP input is internally tied to VDD with a $50K\Omega$ resistor.                                                                                                             |  |

| 25                                                                       | Ι    | MDN         | Margin down command input. Asserted high. The MDN input is internally tied to VDD with a $50K\Omega$ resistor.                                                                                                           |  |

| 19                                                                       | Ι    | COMP1       | COMP1 and COMP2 are high impedance inputs, each connected internally<br>to a comparator and compared against the internally programmable VREF<br>voltage. Each comparator can be independently programmed to monitor for |  |

| 12                                                                       | Ι    | COMP2       | UV or OV. The monitor level is set externally with a resistive voltage divider.                                                                                                                                          |  |

| 11                                                                       | 0    | FAULT#      | When either of the COMP1 or COMP2 inputs are in fault the open-drain FAULT# output will be pulled low. A configuration option exists to disable the FAULT# output while the device is margining.                         |  |

| PIN DESCRIPTIONS (CONTINUED) |     |       |                                                                                                                                                                                                                                                        |  |  |  |

|------------------------------|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 5                            | I/O | READY | Programmable active high/low open drain output indicates that VM+ - VM-<br>is at its set point. When programmed as an active high output, READY can<br>also be used as an input. When pulled low, it will latch the state of the<br>comparator inputs. |  |  |  |

| 29                           | GND | GND   | GND. The bottom side metal plate (Pad 29) should be connected on the PCB to GND for optimized noise performance.                                                                                                                                       |  |  |  |

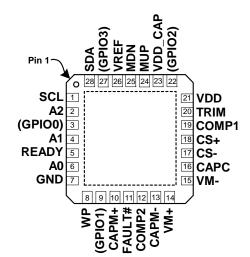

## **PIN CONFIGURATION**

28-Pad 5x5 QFN Top View

() applies on SMM152

## ABSOLUTE MAXIMUM RATINGS

| Temperature Under Bias              | 55°C to 125°C      |

|-------------------------------------|--------------------|

| Storage Temperature QFN             | 65°C to 150°C      |

| Terminal Voltage with Respect to 0  | GND:               |

| VDD Supply Voltage                  | 0.3V to 6.0V       |

| All Others                          | 0.3V to VDD + 0.7V |

| FAULT#                              | GND to 15.0V       |

| CS+, CS                             | 0.3V to 16.0V      |

| Output Short Circuit Current        | 100mA              |

| Reflow Solder Temperature (10 secs) | 240°C              |

| Junction Temperature                | 150°C              |

| Human Body ESD Rating per JEDEC     | 2000V              |

| Machine Model ESD Rating per JEDEC  | 200V               |

| Latch-Up testing per JEDEC          | ±100mA             |

|                                     |                    |

### **RECOMMENDED OPERATING CONDITIONS**

| Temperature Range (Industrial)–40°C to +85°C<br>(Commercial)0°C to +70°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS+, CS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Package Thermal Resistance ( $\theta_{JA}$ )<br>28-Pad QFN (Thermal pad connected to PCB)37.2°C/W<br>28-Pad QFN (Thermal pad not connected to PCB)66.5°C/W                                                                                                                                                                                                                                                                                                                                                                                                        |

| Moisture Classification Level 3 (MSL 3) per J-STD- 020                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| RELIABILITY CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Data Retention20 Years                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Endurance100,000 Cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Note - The device is not guaranteed to function outside its operating rating.<br>Stresses listed under Absolute Maximum Ratings may cause permanent damage<br>to the device. These are stress ratings only and functional operation of the<br>device at these or any other conditions outside those listed in the operational<br>sections of the specification is not implied. Exposure to any absolute maximum<br>rating for extended periods may affect device performance and reliability.<br>Devices are ESD sensitive. Handling precautions are recommended. |

## **DC OPERATING CHARACTERISTICS**

$T_A$ = 0°C to +70°C, VDD = 2.7V to 5.5V, VCS = 4.0V to 15V, unless otherwise noted. All voltages are relative to GND. Note 6.

| Symbol                                 | Parameter                                  | Notes                                       | Min.    | Тур. | Max     | Unit |  |

|----------------------------------------|--------------------------------------------|---------------------------------------------|---------|------|---------|------|--|

| VDD                                    | Supply Voltage                             |                                             | 2.7     | 3.3  | 5.5     | V    |  |

| \/N.4                                  | Sense Voltage Common                       | VM+ pin voltage range, Note 5               | -0.3    |      | VDD     | V    |  |

| VM <sub>Range</sub>                    | Mode Range                                 | VM- pin voltage range, Note 5               | -0.3    |      | +0.5    | V    |  |

| CS <sub>Range</sub>                    | Current Sense Common Mode<br>Voltage Range | CS+, CS- pin voltage range                  | 4.0     |      | 15      | V    |  |

| I <sub>DD</sub>                        | Supply Current from VDD                    | TRIM pin floating                           |         | 3    |         | mA   |  |

| I                                      | Max. TRIM output current                   | TRIM Sourcing Current, Note 5               |         | 1.5  |         | mA   |  |

| I <sub>TRIM</sub> through 100Ω to 1.0V |                                            | TRIM Sinking Current, Note 5                |         | -1.5 |         | mA   |  |

| V <sub>TRIM</sub>                      | TRIM output voltage range                  | I <sub>TRIM</sub> ±1.5mA, Note 5            | GND     |      | 2.5     | V    |  |

| V <sub>ADOC</sub>                      | Margin Range                               | Depends on Converter Trim range             | 0.3     |      | VDD     | V    |  |

| M                                      | Input High Voltage                         | VDD = 2.7V                                  | 0.9xVDD |      | VDD     | v    |  |

| VIH                                    | SĎA, SČL, WP, MUP, MDN                     | VDD = 5.0V                                  | 0.7xVDD |      | VDD     | V    |  |

| M                                      | Input Low Voltage                          | VDD = 2.7V                                  |         |      | 0.1xVDD | V    |  |

| VIL                                    | SDA, SCL, WP, MUP, MDN                     | VDD = 5.0V                                  |         |      | 0.3xVDD | V    |  |

| V <sub>OL</sub>                        | Open Drain Output FAULT#,<br>GPIOx, READY  | ISINK = 1mA                                 |         | 0.2  |         | V    |  |

| M                                      | Address Input High Voltage,                | VDD = 2.7V, $R_{pullup} \leq 300 k\Omega$   | 0.9xVDD |      | VDD     | V    |  |

| V <sub>AIH</sub>                       | A2, A1, A0                                 | VDD = 5.0V, $R_{pullup} \leq 300 k\Omega$   | 0.7xVDD |      | VDD     | V    |  |

| M                                      | Address Input Low Voltage,                 | VDD = 2.7V, $R_{pulldown} \leq 300 k\Omega$ |         |      | 0.1xVDD | v    |  |

| V <sub>AIL</sub>                       | A2, A1, A0                                 | VDD = 5.0V, R <sub>pulldown</sub> ≤300kΩ    |         |      | 0.3xVDD | v    |  |

## DC OPERATING CHARACTERISTICS (CONTINUED)

#### T<sub>A</sub>= 0°C to +70°C, VDD = 2.7V to 5.5V, VCS = 4.0V to 15V, unless otherwise noted. All voltages are relative to GND.

| Symbol               | Parameter                                          | Notes                                                                  | Min.  | Тур.  | Max   | Unit |

|----------------------|----------------------------------------------------|------------------------------------------------------------------------|-------|-------|-------|------|

| I <sub>AIT</sub>     | Address Input Tristate<br>Maximum Leakage – High Z |                                                                        | -3.0  |       | +3.0  | μΑ   |

| OV/UV                | Monitor Voltage Range                              | COMP1 and COMP2 pins                                                   | 0     |       | VDD   | V    |

| V <sub>HYST</sub>    | COMP1/2 DC Hysteresis                              | COMP1 and COMP2 pins,<br>V <sub>TH</sub> -V <sub>TL</sub> (see Note 1) |       | 10    |       | mV   |

| R <sub>Pull-Up</sub> | Input Pull-Up Resistors                            | See Pin Descriptions, Note 5                                           |       | 50    |       | kΩ   |

| VREF                 | Internal COMP4/2 Deference                         | VREF=1.25V                                                             | 1.24  | 1.25  | 1.26  | V    |

| VREF                 | Internal COMP1/2 Reference                         | VREF=0.5V                                                              | 0.495 | 0.500 | 0.505 | V    |

| MADO                 | Margin Accuracy                                    | VM+ - VM- = 1.2V, Note 4                                               | -1.0  | ±0.75 | +1.0  | %    |

| MARGacc              |                                                    | VM+ - VM- = 2.5V, Note 4                                               | -1.0  | ±0.75 | +1.0  | %    |

| VM <sub>ADC</sub>    | Voltage Monitor ADC<br>Measure Range               | VM+ - VM-                                                              | 0     |       | VDD   | V    |

| R <sub>VM</sub>      | VM+, VM- Input Resistance                          | Note 5                                                                 |       | 50    |       | kΩ   |

| CMRR <sub>VM</sub>   | Voltage Sense Common<br>Mode Rejection Ratio       | $V_{CM}$ (VM+, VM-) = 0.5V – VDD, Note 5                               |       | 62    |       | dB   |

| <u></u>              | Current Monitor ADC<br>Measure Range               | Minimum CS+ - CS- voltage                                              |       | 0     |       | m\/  |

|                      |                                                    | Maximum CS+ - CS- voltage                                              |       | 100   |       | mV   |

| CS <sub>ACC</sub>    |                                                    | $CS_{ADC} \ge 50mV$ , Note 2                                           | -2    |       | +2    | %    |

|                      | Current Sense Accuracy                             | CS <sub>ADC</sub> < 50mV, Note 2                                       | -1    |       | +1    | mV   |

| CMDD                 | Current Sense Common                               | V <sub>CM</sub> (CS+, CS-) = 5.0V, Note 5                              |       | 100   |       | ٩D   |

|                      | Mode Rejection Ratio                               | V <sub>CM</sub> (CS+, CS-) = 12V, Note 5                               |       | 80    |       | dB   |

Note 1:  $V_{HYST}$  is measured with a 1.25V external voltage and is determined by subtracting Threshold Low from Threshold High,  $V_{TH}-V_{TL}$  while monitoring the FAULT# pin state. Actual DC Hysteresis is derived from the equation:  $(V_{IN(COMP1/2)}/V_{REF})(V_{HYST})$ . For example, if  $V_{IN(COMP1/2)}/=2.5V$  and  $V_{REF}=1.25V$  then Actual DC Hysteresis= (2.5V/1.25V)(0.003V)=6mV.

Note 2: Current sense accuracy depends on the current sense resistor tolerance. Kelvin sensing of the voltage drop across this resistor must be used to guarantee accuracy. Accuracy at the low range of the current monitor ADC will be adversely impacted by offset errors.

Note 3: It is recommended that ADC reads occur with a frequency of not more than 250Hz.

Note 4: Voltage accuracy is only guaranteed for factory-programmed settings. Changing voltage from the value reflected in the customer specific CSIR code may result in inaccuracies exceeding those specified above.

Note 5: Not 100% Production tested. Guaranteed by Design and/or Characterization.

Note 6: All electrical parameters are guaranteed to function over the stated VDD, VCS and temperature range. Electrical parameters not specified as "guaranteed by design" are tested with a VDD voltage required of the specific application. For example, if the device is to be operated at 3.3V and VCS supply of 12V, it is tested with a VDD supply of 3.3V, +-10% and a VCS supply of 12V, +-10%.

## **AC OPERATING CHARACTERISTICS**

#### $T_A$ = 0°C to +70°C, VDD = 2.7V to 5.5V unless otherwise noted. All voltages are relative to GND.

| Symbol                   | Parameter                                         | Notes                                                                                                                               | Min. | Тур. | Max | Unit |

|--------------------------|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------|------|-----|------|

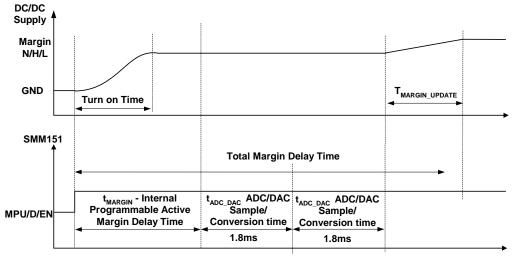

| t <sub>ADC_DAC</sub>     | Monitor sampling/conversion period                | Update period for ADC conversion and DAC update                                                                                     |      | 1.8  |     | ms   |

| t <sub>MARG_I</sub> /D   | Margin single bit increment or decrement time     | $\begin{array}{ll} T_{MARG\_UPDATE} &=& (X)(1.8ms)\\ where: & \\ X=step number of possible 256\\ steps and 1 step=10mV \end{array}$ |      | 1.8  |     | ms   |

| t <sub>GLITCH_MU/D</sub> | Margin Up/Down glitch filter                      |                                                                                                                                     | 70   | 100  | 130 | μS   |

|                          |                                                   |                                                                                                                                     |      | 0    |     | ms   |

|                          | Programmable COMP1 & COMP2<br>glitch filter times |                                                                                                                                     |      | 10   |     | ms   |

|                          |                                                   |                                                                                                                                     |      | 20   |     | ms   |

|                          |                                                   |                                                                                                                                     |      | 40   |     | ms   |

| t <sub>GLITCH_COMP</sub> |                                                   |                                                                                                                                     |      | 80   |     | ms   |

|                          |                                                   |                                                                                                                                     |      | 100  |     | ms   |

|                          |                                                   |                                                                                                                                     |      | 120  |     | ms   |

|                          |                                                   |                                                                                                                                     |      | 140  |     | ms   |

|                          |                                                   |                                                                                                                                     |      | 2.5  |     | ms   |

|                          | Due guerre en ble Maurie Delas - Timore           |                                                                                                                                     |      | 5    |     | ms   |

| t <sub>MARGIN</sub>      | Programmable Margin Delay Times                   | See Figure 4                                                                                                                        |      | 10   |     | ms   |

|                          |                                                   |                                                                                                                                     |      | 17.5 |     | ms   |

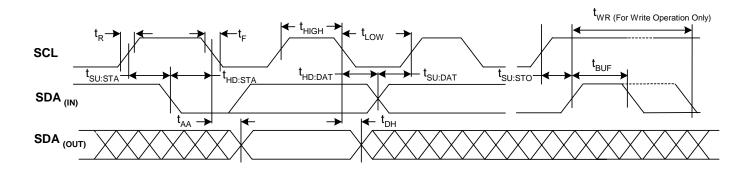

## I<sup>2</sup>C 2-WIRE SERIAL INTERFACE AC OPERATING CHARACTERISTICS – 100kHz

$T_A$ = 0°C to +70°C, VDD = 2.7V to 5.5V unless otherwise noted. All voltages are relative to GND. See Figure 3 Timing Diagram. Note 6.

| Symbol              | Description Conditions     |                                   | Min | Тур | Max  | Units |  |

|---------------------|----------------------------|-----------------------------------|-----|-----|------|-------|--|

| f <sub>SCL</sub>    | SCL Clock Frequency        |                                   | 0   |     | 100  | KHz   |  |

| t <sub>LOW</sub>    | Clock Low Period           |                                   | 4.7 |     |      | μs    |  |

| t <sub>HIGH</sub>   | Clock High Period          |                                   | 4.0 |     |      | μs    |  |

| t <sub>BUF</sub>    | Bus Free Time              | Before New Transmission, Note 5   | 4.7 |     |      | μs    |  |

| t <sub>SU:STA</sub> | Start Condition Setup Time |                                   | 4.7 |     |      | μs    |  |

| t <sub>HD:STA</sub> | Start Condition Hold Time  |                                   | 4.0 |     |      | μs    |  |

| t <sub>SU:STO</sub> | Stop Condition Setup Time  |                                   | 4.7 |     |      | μs    |  |

| t <sub>AA</sub>     | Clock Edge to Data Valid   | SCL low to valid SDA (cycle n)    | 0.2 |     | 3.5  | μs    |  |

| t <sub>DH</sub>     | Data Output Hold Time      | SCL low (cycle n+1) to SDA change | 0.2 |     |      | μS    |  |

| t <sub>R</sub>      | SCL and SDA Rise Time      | Note 5                            |     |     | 1000 | ns    |  |

| t <sub>F</sub>      | SCL and SDA Fall Time      | Note 5                            |     |     | 300  | ns    |  |

| t <sub>SU:DAT</sub> | Data In Setup Time         |                                   | 250 |     |      | ns    |  |

| t <sub>HD:DAT</sub> | Data In Hold Time          |                                   | 0   |     |      | ns    |  |

| TI                  | Noise Filter SCL and SDA   | Noise suppression                 |     | 100 |      | ns    |  |

| t <sub>WR</sub>     | Write Cycle Time           |                                   |     |     | 5    | ms    |  |

Note 5: Not 100% Production tested. Guaranteed by Design and/or Characterization.

Note 6: All electrical parameters are guaranteed to function over the stated VDD, VCS and temperature range. Electrical parameters not specified as "guaranteed by design" are tested with a VDD voltage required of the specific application. For example, if the device is to be operated at 3.3V and VCS supply of 12V, it is tested with a VDD supply of 3.3V, +-10% and a VCS supply of 12V, +-10%.

### TIMING DIAGRAMS

## **APPLICATIONS INFORMATION**

#### **DEVICE OPERATION**

#### POWER SUPPLY

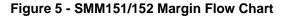

The SMM151 and SMM152 can be powered by a 2.7V to 5.5V input to the VDD pin (Figure 1). See Figure 6 as an example.

#### **VOLTAGE REFERENCE**

The SMM151/152 use an internal voltage reference, VREF with a level of 1.25V. Total accuracy of VREF is  $\pm 1.0\%$  over temperature and supply variations.

#### MODES OF OPERATION

The SMM151/152 have four basic modes of operation: under-voltage (UV) and over-voltage (OV) monitoring mode, differential output voltage sensing mode, input current monitoring mode and supply margining mode. A detailed description of each mode and feature follows and can also be found in Application Note 68. A flow diagram is shown in Figure 5.

#### MARGIN MODE

The SMM151/152 can control margining of a DC/DC converter that has a trim pin or any regulator having access to its feedback node. The TRIM pin on the SMM151 is connected to the trim input pin on the power supply converter. Sense lines from the converter's point-of-load connects to the VM+ and VM-inputs. The margin function begins upon an  $I^2C$  command or assertion of the MUP/MDN pins. The TRIM pin is driven by a DAC whose input is incremented or decremented every 200µs based on the digital comparison of the margin target value and

the actual converter output voltage. The voltage on the TRIM output will continue increasing or decreasing until the converter's output voltage equals the target margin voltage. This voltage adjustment allows the SMM151 and SMM152 to control the margined output voltage of the power supply converter to within  $\pm 1.0\%$  in an open-loop manner.

The converter is held at the margin voltage until the SMM151 receives an I<sup>2</sup>C command or the respective MUP/MDN pin is de-asserted. When not margining, the TRIM pin on the SMM151/152 is in a high impedance state. The voltage on the TRIM pin is buffered and applied to the ADC at the beginning of a margin cycle to ensure the converter is margined from its nominal setpoint. This allows a smooth transition from the converter's nominal voltage to the SMM151/152 controlling that margin voltage to the margin target setting. After margining high, low or nominal, issuing a margin Off command will cause the trim pin to go high impedance. The part margin time from Off to High or Off to Low is specified as a typical according to the equation:

$T_{MARG_UPDATE} = (X)(1.8ms)$  where:

X=number of possible steps (256) and 1 step = 10mV

The Active Margin Command Delay Time using the MUP and MDN pins is shown in Figure 4.

Figure 4 – Margin Delay Time

## **APPLICATIONS INFORMATION (CONTINUED)**

When measuring the margin delay time external to the device, ADC sample time and Update Trim time ( $\cong$  3.6 ms) must be added to the internally programmed delay time as shown:

| Spec    | Actual measurement |

|---------|--------------------|

| 2.5 ms  | 6.1 ms             |

| 5 ms    | 8.6 ms             |

| 10 ms   | 13.6 ms            |

| 17.5 ms | 21.1 ms            |

#### MONITOR

The SMM151/152 monitor the COMP1 and COMP2 pins. COMP1 and COMP2 are high impedance inputs, each connected internally to a comparator and compared against the programmable internal reference voltage. Each comparator can be independently programmed to monitor for either an UV or an OV event. The monitor level may be set externally with a resistive voltage divider. The COMPx pins can be connected to Vin. Vout or any voltage that needs to be monitored. The internal comparators COMP1/2 are compared to VREF, so the voltage dividers are set above or below the programmed VREF level depending on whether monitoring UV or OV. As an example, with VREF set to 1.25V, to monitor an OV of 1.7V on COMP1 and a UV of 1.3V on COMP2, the voltage divider resistors are:

For OV, RUpper = 1.37k, 1% RLower = 3.83k, 1%. For UV, RUpper = 1.02k, 1% RLower = 25.5k, 1%.

The parts can be programmed to trigger the FAULT# pin when either COMPx comparator has exceeded the UV or OV setting. The READY and FAULT# outputs of the SMM151/152 are active as long as the triggering limit remains in a fault condition. The READY pin is a programmable active high/low open drain output indicates that VM+ - VM- is at its' set point.

When programmed as an active high output, READY can also be used as an input. When pulled low, it will latch the state of the comparator inputs. When either of the COMP1 or COMP2 inputs are in fault, the opendrain FAULT# output will be pulled low. A configuration option exists to disable the FAULT# output while the device is in margining mode.

#### **GENERAL-PURPOSE INPUTS/OUTPUTS**

The GPIOs are open drain type outputs. The pins should be pulled up externally to voltages ranging from 2.0V to 12V. Each I/O has non-volatile (NV) memory setting associated with it that determines the power-on state of the pin. The status (High/Low) is read

from bit 0 of registers 34h, 35h, 36h or 37h with 0=Low and 1=High. Additionally, the I/Os have a command bit that when written overrides the NV setting and sets the pin either high or low. The I/Os also have status bits to read the state of the pin as high or low. The command/status register for each I/O is addressed separately alleviating the need for the host controller to remember the state of the other I/Os when writing commands. More information can be found in Application Note 69.

#### STATUS REGISTER

A status register exists for I<sup>2</sup>C polling of the status of the COMP1 and COMP2 inputs. Two bits in this status register reflect the current state of the inputs (1 = fault, 0 = no fault). Two additional bits show the state of the inputs latched by one of two events programmed in the configuration. More information can also be found in Application Note 69. The first event option is the FAULT# output going active. The second event option is the READY pin going low. The READY pin is an I/O. As an output, the READY output pin goes active when the DC controlled voltages are at their set point. As an input programmed to active high, it can be pulled low externally and latch the state of the COMP inputs. This second event option allows the state of the COMP inputs on multiple devices to be latched at the same time while a host monitors their FAULT# outputs.

#### MARGINING

The SMM151/152 have three additional control voltage settings: margin high, margin nominal, and margin low. The margin high and margin low settings can be as much as  $\pm 15\%$  of the nominal setting depending on the converter manufacturer. The margin high and margin low voltage settings can range from 0.3V to VDD around the converters' nominal output voltage setting depending on the specified margin range of the DC-DC converter. These settings are stored in the configuration registers and are loaded as control voltage settings by margin commands issued via the  $l^2C$  bus.

The margin command registers contain two bits that decode the commands to margin high or margin low. Once the SMM151/152 receive the command to margin the supply voltage, it begins adjusting the supply voltage to move toward the desired setting. When this voltage setting is reached, a bit is set in the margin status registers and the READY signal becomes active.

Note: Configuration writes or reads of registers  $00_{HEX}$  to  $03_{HEX}$  should not be performed while the SMM151 or SMM152 is margining.

#### FAULTS

When either of the COMP1 or COMP2 inputs are in fault, the open-drain FAULT# output will be pulled low. A configuration option exists to disable the FAULT# output while the device is margining. If "Fault Output Disabled while Margining" is selected, Faults are disabled for all margining except when margining to the 'Off' and 'Nominal' states. Also, the programmable feature 'Fault Holds Off and Shutdown Control' is enabled only for the Nominal margin state.

Please note that if "Fault Output Disabled" is selected and the device has margined to LOW and HIGH and then returns to the OFF state without going through NOMINAL, the Status Register will read a fault (if there is one) but the FAULT Output Pin will be disabled until such time that the NOMINAL setting is activated. To avoid this condition it is recommended that the device always return to OFF from the NOMINAL state.

#### Fault Latched by a Fault Condition:

The "Fault Latched by a Fault Condition" programmable option is triggered only on the leading edge of a Fault. That is, a latched fault can be cleared while the Fault yet exists.

#### Fault Latched by Ready I/O Pin:

Fault Latched by Ready I/O pin functions on the margin transitions from Off to Hi/Low/Nominal or from Nominal to Hi/Low or Hi/Low to Nominal but not from Hi/Low/Nominal to Off.

#### WRITE PROTECTION

Write protection for the SMM151/152 is located in a volatile register where the power-on state is defaulted to write protect. There are separate write protect modes for the configuration registers and memory. In order to remove write protection, the code  $55_{HEX}$  is written to the write protection register.Other codes will enable write protection.

For example, writing  $59_{HEX}$  will allow writes to the configuration register but not to the memory, while writing  $35_{HEX}$  will allow writes to the memory but not to the configuration registers. The SMM151/152 also feature a Write Protect pin (WP input) which, when asserted, prevents writing to the configuration registers and EE memory. In addition to these two forms of write protection there is a configuration register lock bit which, once programmed, does not allow the configuration registers to be changed.

#### A2, A1, A0

The address bits A[2:0] can be hard wired High or Low or may be left open (High-Z) to allow for a total of 21 distinct device addresses. When floating, the inputs can tolerate the amount of leakage as described by the specification  $I_{AIT}$ . An external 100k pull-up or pull down resistor is sufficient to set a High or Low logic level.

#### CS+, CS-

Select a resistor value that will drop no more than 100mV (full scale) when full load is drawn by the converter or circuit being sensed by the resistor  $R_s$  (Figure 1). To obtain highest accuracy current-sensing, provide a Kelvin connection from the resistor to the CS+ and CS- pins. Do not allow the main current path circuit traces to inadvertently become a part of the current sense resistor. Kelvin connect directly at the resistor and follow the manufacturer's instructions for exact positioning of the traces for Kelvin sensing.

### **APPLICATIONS INFORMATION (CONTINUED)**

Figure 6 – Typical application schematic shows the SMM151 controlling a 12V in/1.5V out DC/DC converter. This example, using the 1.25V VREF, also shows the COMP1/2 pins monitoring the DC/DC converter VOUT set to an OV of 1.7V on COMP1 and a UV of 1.3V on COMP2, the voltage divider resistors are: For OV, R1 = 1.37k, 1% R3 = 3.83k, 1%, For UV, R2 = 1.02k, 1% R4 = 25.5k, 1%. The Programming Supply jumper can be used to supply the SMM151 VDD voltage from the SMX3202 programmer when the device is programmed with board power off and the controlled supply unloaded.

#### **Maximizing Accuracy**

Maximum margining accuracy is obtained by placing a resistor between the SMM151/152 TRIM output and the TRIM input of the converter. From the manufacturer's data sheet obtain the value of the internal voltage reference and equivalent TRIM input series resistance.

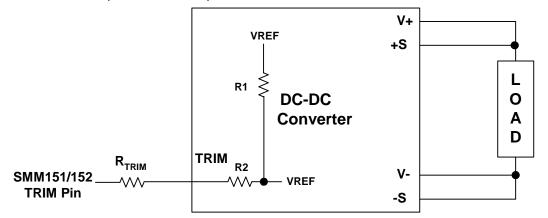

Figure 7 below displays the internal trimming circuit for a typical isolated DC-DC converter. In this example, the converter uses positive trimming, i.e., an increase in voltage at the TRIM pin causes an increase in output voltage.

#### Figure 7 - Simplified TRIM circuit of an isolated DC-DC converter connects to SMM151/152 TRIM output

For this example R<sub>TRIM</sub> is found:

$$R_{TRIM} = \frac{R2 \times \left[\frac{(VREF \times k) - 0.3}{(VREF - 0.3)}\right]}{1 - \frac{(k \times VREF - 0.3)}{(VREF - 0.3)}}$$

Where:

$$\mathbf{k} = \frac{V_{Low}}{V_{Nom}}$$

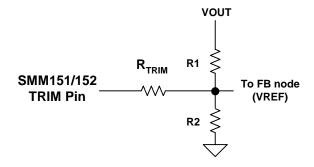

0.3 = SMM151/152 TRIM output saturation voltage VLow = Margin Low target voltage VNom = Nominal (non-trimmed output voltage) VREF = Converter internal reference voltage The next example applies to most non-isolated DC-DC converters, LDO's and in-system designed converters using monolithic PWM controllers. Figure 8 is a simplified schematic showing the resistor divider network used to close the loop from the output to the circuit's feedback node. These type circuits employ negative trimming, meaning any decrease in voltage into the feedback node cause an increase in output voltage.

$$R_{TRIM} = \frac{R1 \times (VREF - 0.3)}{VNom \times (k-1)}$$

$$k = \frac{V High}{V_{Nom}}$$

0.3 = SMM151/152 TRIM output saturation voltage VHIGH = Margin Low target voltage VNom = Nominal (non-trimmed output voltage) VREF = Converter internal reference voltage

Figure 8 - Simplified TRIM circuit of a non-isolated DC-DC converter connects to SMM151/152 TRIM output

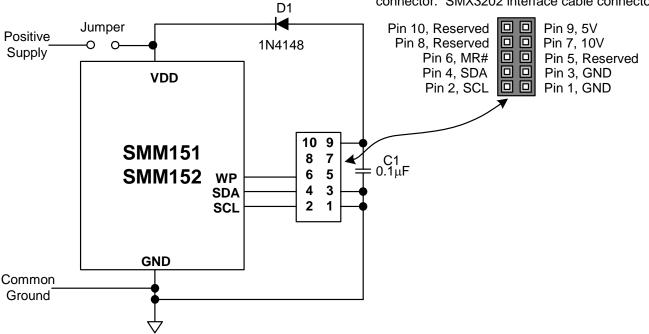

The end user can obtain the Summit SMX3202 programming system for device prototype development. The SMX3202 system consists of a programming Dongle, cable and Windows<sup>TM</sup> GUI software. It can be ordered on the website or from a local representative. The latest revisions of all software and an application brief describing the SMX3202 is available from the website (www.summitmicro.com).

The SMX3202 programming Dongle/cable interfaces directly between a PC's USB port and the target application. The device is then configured on-screen via an intuitive graphical user interface employing drop-down menus.

The Windows GUI software will generate the data and send it in  $l^2C$  serial bus format so that it can be directly downloaded to the SMM151/152 via the programming Dongle and cable. An example of the connection interface is shown in Figure 9.

When design prototyping is complete, the software can generate a HEX data file that should be transmitted to Summit for approval. Summit will then assign a unique customer ID to the HEX code and program production devices before the final electrical test operations. This will ensure proper device operation in the end application.

Top view of straight 0.1" x 0.1 closed-side connector. SMX3202 interface cable connector.

Figure 9– SMX3202 Programmer  $I^2C$  serial bus connections to program the SMM151/152. The SMM151/152 have a Write Protect pin (WP input) which, when asserted, prevents writing to the configuration registers and EE memory. In addition, there is a configuration register lock bit, which, once programmed, does not allow the configuration registers to be changed.

## I<sup>2</sup>C PROGRAMMING INFORMATION

#### SERIAL INTERFACE

Access to the configuration registers, general-purpose memory and command and status registers is carried out over an industry standard 2-wire serial interface (I<sup>2</sup>C). SDA is a bi-directional data line and SCL is a clock input. Data is clocked in on the rising edge of SCL and clocked out on the falling edge of SCL. All data transfers begin with the most significant bit (MSB). During data transfers SDA must remain stable while SCL is high. Data is transferred in 8-bit packets with an intervening clock period in which an Acknowledge is provided by the device receiving data (SMM151). The SCL high period (t<sub>HIGH</sub>) is used for generating Start and Stop conditions that precede and end most transactions on the serial bus. A high-to-low transition of SDA while SCL is high is considered a Start condition while a low-to-high transition of SDA while SCL is high is considered a Stop condition.

The interface protocol allows operation of multiple devices and types of devices on a single bus through unique device addressing. The address byte is comprised of a 4-bit device type identifier (slave address) and a unique (three-state) 3-bit bus address. The remaining bit indicates either a read or a write operation. Refer to Table 1 for a description of the address bytes used by the SMM151/152. Refer to Table 2 for an example of the unique address handling of the SMM151/152.

The device type identifier for the memory array, the configuration registers and the command and status registers are accessible with the same slave address. It can be set using the address pins as described in Table 2.

The bus address bits A[2:0] are hard wired only through address pins 2, 4 and 6 (A2, A1 and A0 respectively) or may be left open (Z) to allow for a total of 21 distinct device addresses. The bus address accessed in the address byte of the serial data stream must match the setting on the SMM151 address pins.

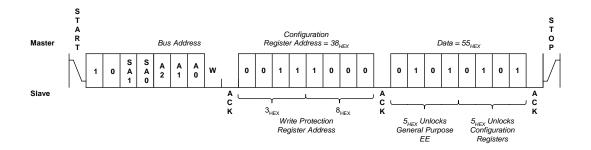

#### WRITE

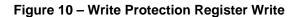

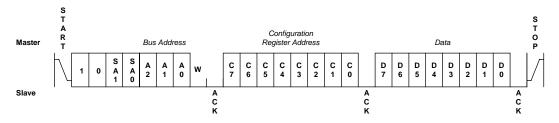

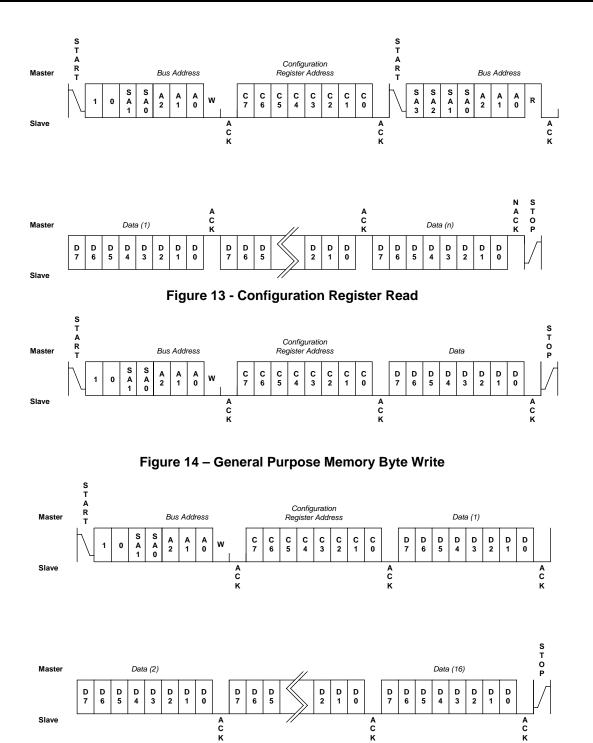

Writing to the memory or configuration registers is illustrated in Figures 10, 11, 12, 14, 15 and 17. A Start condition followed by the address byte is provided by the host I<sup>2</sup>C controller; the SMM151 responds with an Acknowledge; the host then responds by sending the memory address pointer or configuration register address pointer; the SMM151/152 respond with an acknowledge; the host then clocks in one byte of data. For memory and configuration register writes, up to 15 additional bytes of data can be clocked in by the host to write to consecutive addresses within the same page. After the last byte is clocked in and the host receives an Acknowledge, a Stop condition must be issued to initiate the nonvolatile write operation.

#### READ

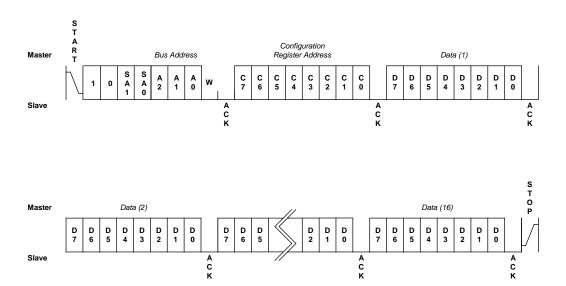

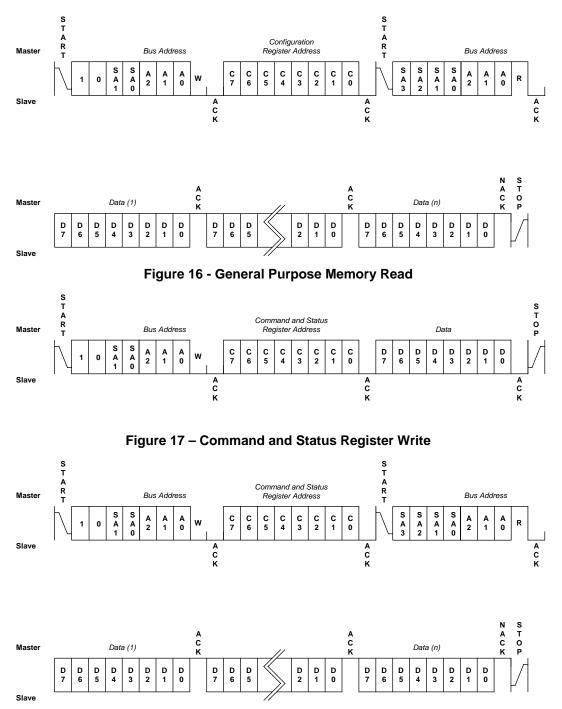

The address pointer for the configuration registers, memory, command and status registers and ADC registers must be set before data can be read from the SMM151. This is accomplished by issuing a dummy write command, which is simply a write command that is not followed by a Stop condition. The dummy write command sets the address from which data is read. After the dummy write command is issued, a Start command followed by the address byte is sent from the host. The host then waits for an Acknowledge and then begins clocking data out of the slave device (SMM151/2). The first byte read is data from the address pointer set during the dummy write command. Additional bytes can be clocked out of consecutive addresses with the host providing an Acknowledge after each byte. After the data is read from the desired registers, the read operation is terminated by the host holding SDA high during the Acknowledge clock cycle and then issuing a Stop condition. Refer to Figures 13, 16 and 18 for an illustration of the read sequence.

#### WRITE PROTECTION

The SMM151/152 power up into a write protected mode. Writing a code to the volatile write protection register (write only) can disable the write protection. The write protection register is located at address  $38_{\text{HEX}}$ . Writing to the write protection register is shown in Figure 10.

Writing  $0101_{\text{BIN}}$  to bits [7:4] of the write protection register allows writes to the general-purpose memory while writing  $0101_{\text{BIN}}$  to bits [3:0] allow writes to the configuration registers. Write protection isre-enabled by writing other codes (not  $0101_{\text{BIN}}$ ) to the write protection register.

## I<sup>2</sup>C PROGRAMMING INFORMATION (CONTINUED)

#### **CONFIGURATION REGISTERS**

The majority of the configuration registers are grouped with the general-purpose memory. Writing and reading the configuration registers is shown in Figures 11, 12 and 13.

Note: Configuration writes or reads of registers 00 to  $03_{HEX}$  must not be performed while the SMM151/152 is margining.

#### **GENERAL-PURPOSE MEMORY**

The 256-byte general-purpose memory is located at any slave address. The bus address bits are hard wired by the address pins A2, A1 and A0. They can be tied low, high or left floating, (Hi-Z). Memory writes and reads are shown in Figures 14, 15 and 16.

#### COMMAND AND STATUS REGISTERS

Writes and reads of the command and status registers are shown in Figures 17 and 18.

#### **GRAPHICAL USER INTERFACE (GUI)**

Device configuration utilizing the Windows based SMM151/152 graphical user interface (GUI) is strongly recommended. The software is available from the Summit website (www.summitmicro.com). Using the GUI in conjunction with this datasheet simplifies the process of device prototyping and the interaction of the various functional blocks. A programming Dongle (SMX3202) is available from Summit to communicate with the SMM151/152. See Figure 9 and the SMX3202 Data Sheet (www.summitmicro.com).

|               | 101         |                                                                                                                      |

|---------------|-------------|----------------------------------------------------------------------------------------------------------------------|

| Slave Address | Bus Address | Register Type                                                                                                        |

| 10XX          | A2 A1 A0    | Configuration Registers are located in 00 $_{\rm HEX}$ thru 05 $_{\rm HEX}$ and 30 $_{\rm HEX}$ thru 3E $_{\rm HEX}$ |

| IUXX          |             | General-Purpose Memory is located in 40 $_{\rm HEX}$ thru FF $_{\rm HEX}$                                            |

#### Table 1 - Address bytes used by the SMB151/152.

Slave Address programmed as 10XX (Z = Hi-Z state)

| Pins A[2:0] |    | D] |               |             |

|-------------|----|----|---------------|-------------|

| A2          | A1 | A0 | Slave Address | Bus Address |

| 0           | 0  | 0  | 1000          | 000         |

| 0           | 0  | 1  | 1000          | 001         |

| 0           | 0  | Z  | 1000          | 010         |

| 0           | 1  | 0  | 1000          | 100         |

| 0           | 1  | 1  | 1000          | 101         |

| 0           | 1  | Z  | 1000          | 110         |

| 0           | Z  | Х  | 1000          | 011         |

| 1           | 0  | 0  | 1001          | 000         |

| 1           | 0  | 1  | 1001          | 001         |

| 1           | 0  | Z  | 1001          | 010         |

| 1           | 1  | 0  | 1001          | 100         |

| 1           | 1  | 1  | 1001          | 101         |

| 1           | 1  | Z  | 1001          | 110         |

| 1           | Z  | Х  | 1001          | 011         |

| Z           | 0  | 0  | 1010          | 000         |

| Z           | 0  | 1  | 1010          | 001         |

| Z           | 0  | Z  | 1010          | 010         |

| Z           | 1  | 0  | 1010          | 100         |

| Z           | 1  | 1  | 1010          | 101         |

| Z           | 1  | Z  | 1010          | 110         |

| Z           | Z  | Х  | 1010          | 011         |

Table 2 – Example device addresses allowed by the SMM151.

## I<sup>2</sup>C PROGRAMMING INFORMATION (CONTINUED)

Figure 12 – Configuration Register Page Write

## I<sup>2</sup>C PROGRAMMING INFORMATION (CONTINUED)

## I<sup>2</sup>C PROGRAMMING INFORMATION (CONTINUED)

Figure 18 - Command and Status Register Read

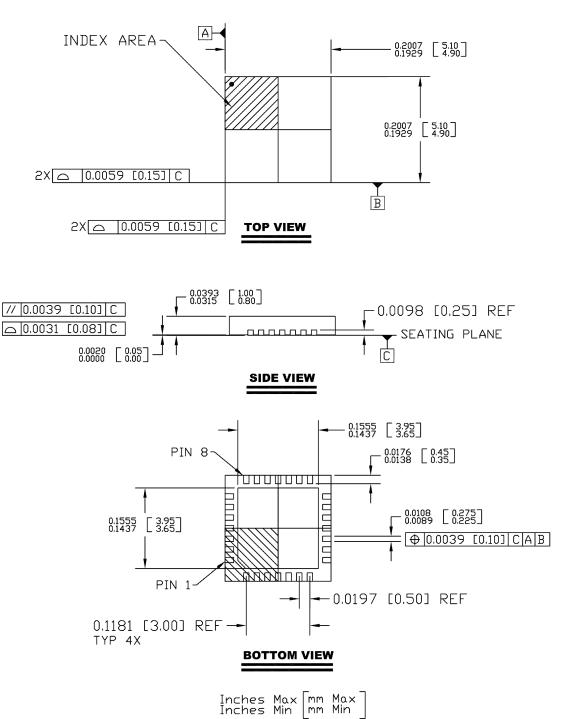

## PACKAGE OUTLINES

## SMM151/152

### 28-Pad QFN

REFERENCE JEDEC MD-220

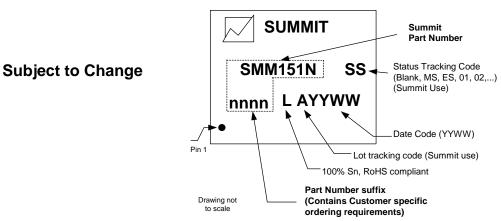

### PART MARKING

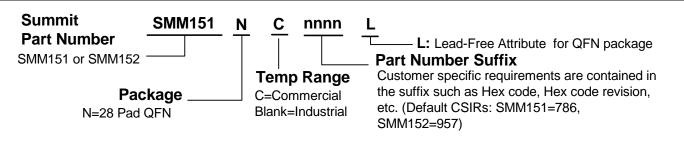

### **ORDERING INFORMATION**

#### NOTICE

NOTE 1 - This is a final data sheet that describes a Summit product currently in production.

SUMMIT Microelectronics, Inc. reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability. SUMMIT Microelectronics, Inc. assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contained herein reflect representative operating parameters, and may vary depending upon a user's specific application. While the information in this publication has been carefully checked, SUMMIT Microelectronics, Inc. shall not be liable for any damages arising as a result of any error or omission.

SUMMIT Microelectronics, Inc. does not recommend the use of any of its products in life support or aviation applications where the failure or malfunction of the product can reasonably be expected to cause any failure of either system or to significantly affect their safety or effectiveness. Products are not authorized for use in such applications unless SUMMIT Microelectronics, Inc. receives written assurances, to its satisfaction, that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; and (c) potential liability of SUMMIT Microelectronics, Inc. is adequately protected under the circumstances.

Revision 3.0 - This document supersedes all previous versions. Please check the Summit Microelectronics Inc. web site at <u>www.summitmicro.com</u> for data sheet updates.

© Copyright 2008 SUMMIT MICROELECTRONICS, Inc. PROGRAMMABLE POWER FOR A GREEN PLANET™

I<sup>2</sup>C is a trademark of Philips Corporation