# TLV4946K, TLV4946-2K

Value Optimized Hall Effect Latches for Industrial and Consumer Applications

## Datasheet

Rev1.1, 2010-08-02

Sense and Control

#### Edition 2010-08-02

Published by Infineon Technologies AG 81726 Munich, Germany © 2010 Infineon Technologies AG All Rights Reserved.

#### **Legal Disclaimer**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

#### Value Optimized Hall Effect Latches for Industrial and Consumer Applications

Revision History: 2010-08-02, Rev1.1

**Previous Revisions: 1.0**

| Page | Subjects (major changes since last revision) |

|------|----------------------------------------------|

| all  | TLV4946-2L removed                           |

|      |                                              |

|      |                                              |

|      |                                              |

|      |                                              |

|      |                                              |

#### **We Listen to Your Comments**

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

sensors@infineon.com

#### **Table of Contents**

## **Table of Contents**

|                                        | Table of Contents                                                                                                                            | 4                    |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|                                        | List of Figures                                                                                                                              | 5                    |

|                                        | List of Tables                                                                                                                               | 6                    |

| <b>1</b><br>1.1<br>1.2<br>1.3          | Product Description Overview Features Target Applications                                                                                    | 7<br>7               |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6 | Functional Description  General  Pin Configuration  Pin Description  Block Diagram  Operating Modes and States  Functional Block Description | 8<br>9<br>9<br>10    |

| 3<br>3.1<br>3.2<br>3.3<br>3.4          | Specification Application circuit Absolute Maximum Ratings Operating Range Electrical Characteristics                                        | . 11<br>. 11<br>. 12 |

| <b>4</b><br>4.1                        | Package Information                                                                                                                          |                      |

|                                        |                                                                                                                                              |                      |

## TLV4946K, TLV4946-2K

## List of Figures

## **List of Figures**

| Figure 1 | Pin Configuration and sensitive area (Top view, figure not to scale)              | . 8 |

|----------|-----------------------------------------------------------------------------------|-----|

| Figure 2 | TLV4946K, TLV4946-2K Block Diagram                                                | . 9 |

| Figure 3 | Definition of the Magnetic Field direction                                        |     |

| Figure 4 | Output Signal                                                                     | 10  |

| Figure 5 | Application circuit                                                               | 11  |

| Figure 6 | Timing Diagram                                                                    | 13  |

| Figure 7 | Marking of the TLV4946K and TLV4946-2K and distance of the chip to the upper side | 14  |

| Figure 8 | PG-SC59-3-5 Package Outline                                                       | 14  |

| Figure 9 | Footprint PG-SC59-3-5 (SOT23 compatible)                                          | 15  |

|          |                                                                                   |     |

## TLV4946K, TLV4946-2K

#### **List of Tables**

## **List of Tables**

| Table 1 | PIN Definitions for the PG-SC59-3-5 package | 9 |

|---------|---------------------------------------------|---|

| Table 2 | Absolute Maximum Ratings                    | 1 |

| Table 3 | Operating Range 1                           | 2 |

|         | Electrical Characteristics                  |   |

| Table 5 | Magnetic Characteristics                    | 3 |

#### **High Precision Hall Effect Latch**

#### TLV4946K, TLV4946-2K

### 1 Product Description

#### 1.1 Overview

The TLV4946K and TLV4946-2K are high precision Hall Effect Latches with highly accurate switching thresholds for ambient operating temperatures up to 85°C.

The TLV4946K and the TLV4946-2K are available in a lead-free and halogen-free SMD package PG-SC59-3-5 package to meet current and future requirements.

#### 1.2 Features

- 2.7 V to 18 V supply voltage operation.

- · Operation from unregulated power supply.

- High sensitivity and high stability of the magnetic switching points.

- High resistance to mechanical stress by active error compensation.

- Reverse battery protection (-18 V).

- Superior temperature stability.

- Low jitter (typically 1 μs).

- High ESD performance (± 4 kV HBM).

- Digital output signal (open-drain).

- · Lead-free and halogen free SMD package

- Not suitable for automotive applications

#### 1.3 Target Applications

The TLV4946-2K is ideally suited to detect the rotor position in Brushless DC (BLDC) Motors used in industrial and consumer applications, such as: air conditioning systems, pumps, washing machines, DVD players, rolling shutter, etc. The TLV4946K can be used in index counting applications with a magnetized pole wheel mounted on the axle of a motor.

| Product Name | Product Type      | Order Code  | Package     |  |

|--------------|-------------------|-------------|-------------|--|

| TLV4946K     | Hall Effect Latch | SP000604402 | PG-SC59-3-5 |  |

| TLV4946-2K   | Hall Effect latch | SP000604332 | PG-SC59-3-5 |  |

Datasheet 7 Rev1.1, 2010-08-02

**Functional Description**

## 2 Functional Description

#### 2.1 General

Precise magnetic switching thresholds and high temperature stability are achieved by active compensation circuits and chopper techniques on chip. Offset voltages generated by temperature-induced stress or overmolding are canceled so that high accuracy is achieved. The IC has an open collector output stage with 20 mA current sink capability. A wide operating voltage range from 2.7 V to 18 V with reverse polarity protection down to -18 V makes the TLV4946K and TLV4946-2K suitable for a wide range of applications. A magnetic south pole with a field strength above  $B_{op}$  turns the output on. A magnetic north pole exceeding  $B_{rp}$  turns it off.

#### 2.2 Pin Configuration

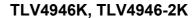

Figure 1 Pin Configuration and sensitive area (Top view, figure not to scale)

**Functional Description**

## 2.3 Pin Description

Table 1 PIN Definitions for the PG-SC59-3-5 package

| PIN No. | Name           | Function       |

|---------|----------------|----------------|

| 1       | V <sub>s</sub> | Supply Voltage |

| 2       | Q              | Output         |

| 3       | GND            | Ground         |

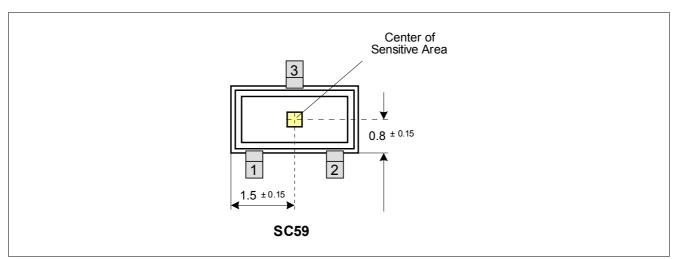

### 2.4 Block Diagram

Figure 2 TLV4946K, TLV4946-2K Block Diagram

**Functional Description**

### 2.5 Operating Modes and States

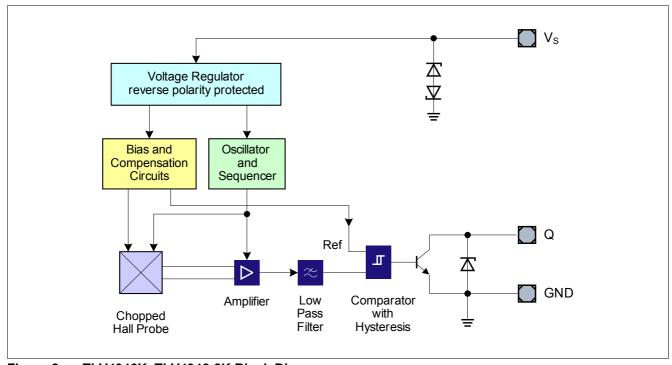

#### **Field Direction and Definition**

Positive magnetic fields correspond to the south pole of the magnet targeting the branded side of the package.

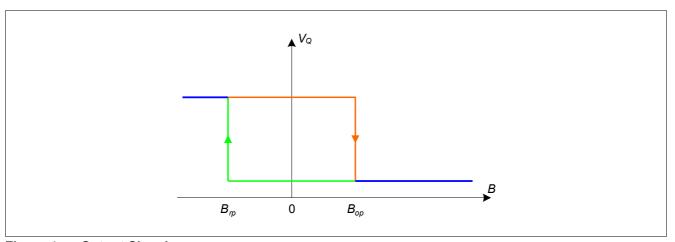

Figure 3 Definition of the Magnetic Field direction

Figure 4 Output Signal

#### 2.6 Functional Block Description

The chopped Hall Effect Latch comprises a Hall probe, a bias generator, compensation circuits, an oscillator and an output transistor. The bias generator provides currents to the Hall probe and the active circuits. Compensation circuits stabilize response of the IC over temperature and reduce the impact of process variations.

The Active Error Compensation rejects offsets in the signal path and reduces the impact of mechanical stress in the package caused by molding, soldering and thermal effects.

The chopper technique together with the threshold generator and the comparator ensure high accurate magnetic switching points.

**Specification**

## 3 Specification

#### 3.1 Application circuit

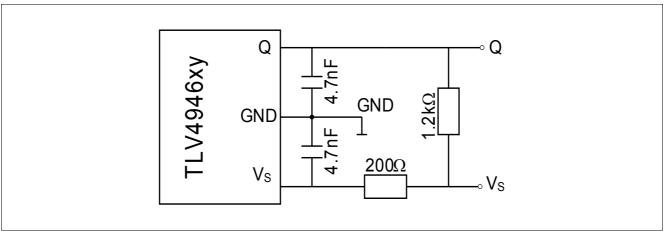

Figure 5 Application circuit

It is recommended to use a resistor of 200  $\Omega$  in the supply line for current limitation in the case of an overvoltage pulse. Two capacitors of 4.7 nF enhance the EMC performance. The pull-up of 1.2 k $\Omega$  limits the current through the output transistor.

#### 3.2 Absolute Maximum Ratings

Stress above the maximum values listed in this section may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect the reliability of the device. Exceeding only one of these values may cause irreversible damage to the device.

Table 2 Absolute Maximum Ratings

| Parameter                                   | Symbol                  | Values |      |           | Unit | Note / Test Condition |

|---------------------------------------------|-------------------------|--------|------|-----------|------|-----------------------|

|                                             |                         | Min.   | Тур. | Max.      |      |                       |

| Maximum Ambient Temperature                 | $T_{A}$                 | - 40   | _    | 125       | °C   |                       |

| Maximum Junction Temperature                | $T_{J}$                 | - 40   | _    | 150       | °C   |                       |

| Supply Voltage                              | $V_{S}$                 | - 18   | _    | 18        | V    |                       |

| Supply current through protection device    | $I_{S}$                 | -50    | _    | 50        | mA   |                       |

| Output Voltage                              | $V_{OUT}$               | - 0.7  | _    | 18        | V    |                       |

| Storage Temperature                         | $T_{S}$                 | - 40   | _    | 150       | °C   |                       |

| Magnetic flux density                       | В                       | _      | _    | unlimited | mT   |                       |

| ESD Robustness HBM: 1.5 k $\Omega$ , 100 pF | $V_{\rm ESD,HBM}^{-1)}$ | _      | _    | 4         | kV   |                       |

|                                             | 1                       |        |      |           |      |                       |

<sup>1)</sup> According to EIA/JESD22-A114-E

Specification

### 3.3 Operating Range

The following operating conditions must not be exceeded in order to ensure correct operation of the device. All parameters specified in the following sections refer to these operating conditions unless otherwise mentioned.

Table 3 Operating Range

| Parameter                   | Symbol  | Values |      |      | Unit | Note / Test Condition |

|-----------------------------|---------|--------|------|------|------|-----------------------|

|                             |         | Min.   | Тур. | Max. |      |                       |

| Supply Voltage              | $V_{S}$ | 2.7    | _    | 18   | V    |                       |

| Output Voltage              | $V_{Q}$ | -0.7   | _    | 18   | V    |                       |

| Output Current              | $I_{Q}$ | 0      | _    | 20   | mA   |                       |

| Maximum Ambient Temperature | $T_{A}$ | -40    | _    | 85   | °C   |                       |

#### 3.4 Electrical Characteristics

Product characteristics include the spread of values guaranteed within the specified voltage and ambient temperature range. typical characteristics are the median of the production (at  $V_s$ =12V and  $T_A$ =25°C).

Table 4 Electrical Characteristics

| Parameter                                            | Symbol            | Values |      |                  | Unit              | Note / Test Condition                        |  |

|------------------------------------------------------|-------------------|--------|------|------------------|-------------------|----------------------------------------------|--|

|                                                      |                   | Min.   | Тур. | Max.             |                   |                                              |  |

| Supply Current                                       | $I_{\mathbb{S}}$  | 2      | 4    | 6                | mA                | V <sub>S</sub> =2.7 V18 V                    |  |

| Reverse Current                                      | $I_{SR}$          | 0      | 0.2  | 1                | mA                | V <sub>S</sub> =-18 V                        |  |

| Output Saturation Voltage                            | $V_{QSAT}$        | _      | 0.3  | 0.6              | V                 | I <sub>Q</sub> =20 mA                        |  |

| Output leakage current                               | $I_{QLEAK}$       | _      | 0.05 | 10               | μΑ                | V <sub>Q</sub> =18 V                         |  |

| Output fall time <sup>1)</sup>                       | $t_{f}$           | _      | 0.02 | 1                | μs                | $R_L$ =1.2k $\Omega$ , $C_L$ =50 pF          |  |

| Output rise time <sup>1)</sup>                       | $t_{r}$           | _      | 0.4  | 1                | μs                |                                              |  |

| Chopper frequency                                    | $f_{ m OSC}$      | _      | 320  | _                | kHz               |                                              |  |

| Switching frequency                                  | $f_{\sf SW}$      | 0      | _    | 15 <sup>2)</sup> | kHz               |                                              |  |

| Delay time <sup>3)</sup>                             | $t_{d}$           | _      | 13   | _                | μs                |                                              |  |

| Output jitter <sup>4)</sup>                          | $t_{\mathrm{QJ}}$ | -      | 1    | _                | μs <sub>RMS</sub> | Typical value for a 1 kHz square wave signal |  |

| Power-on Time <sup>5)</sup>                          | $t_{PON}$         | _      | 13   | _                | μs                | V <sub>S</sub> > 2.7 V                       |  |

| Thermal Resistance junction to ambient <sup>6)</sup> | $R_{\rm thja}$    | -      | 100  | _                | K/W               |                                              |  |

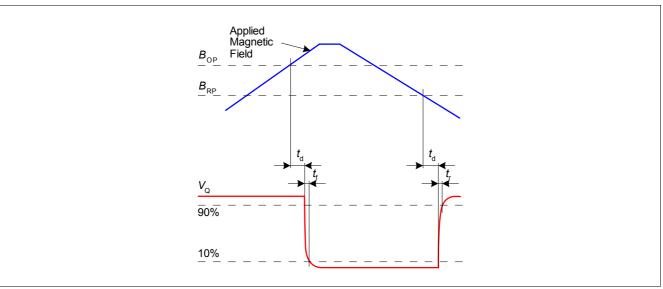

<sup>1)</sup> See Figure 6

Datasheet 12 Rev1.1, 2010-08-02

<sup>2)</sup> To operate the sensor at maximum switching frequency, the value of the magnetic signal amplitude must be 1.4 times higher than the static fields. This is due to the -3 dB corner frequency of the low pass filter in the signal path.

<sup>3)</sup> Systematic delay between magnetic threshold reached and output.

<sup>4)</sup> Jitter is the unpredictable deviation of the output switching delay.

<sup>5)</sup> Time from applying  $V_S$ . > 2.7 V to the sensor until the output state is valid.

<sup>6)</sup> Relationship between junction and ambient temperature:  $T_J = T_{amb} + R_{thia}$ . ( $V_S \cdot I_S + V_{QS} \cdot I_Q$ ).

**Specification**

Figure 6 Timing Diagram

Table 5 Magnetic Characteristics<sup>1)</sup>

| Parameter                                          | Symbol    | Values |       |      | Unit          | Note / Test Condition                            |

|----------------------------------------------------|-----------|--------|-------|------|---------------|--------------------------------------------------|

|                                                    |           | Min.   | Тур.  | Max. |               |                                                  |

| Operate point                                      | $B_{OP}$  | 6.1    | 14.0  | 19.2 | mT            | TLV4946K                                         |

|                                                    |           | 0.5    | 2.0   | 3.5  | mT            | TLV4946-2K                                       |

| Release point                                      | $B_{RP}$  | -19.2  | -14.0 | -6.1 | mT            | TLV4946K                                         |

|                                                    |           | -3.5   | -2.0  | -0.5 | mT            | TLV4946-2K                                       |

| Hysteresis                                         | $B_{HYS}$ | 22.0   | 28.0  | 34.0 | mT            | TLV4946K <sup>2)</sup>                           |

|                                                    |           | 1.0    | 4.0   | 6.0  | mT            | TLV4946-2K                                       |

| Magnetic offset <sup>3)</sup>                      | $B_{OFF}$ | -3.0   | _     | 3.0  | mT            | TLV4946K <sup>2)</sup>                           |

|                                                    |           | -1.5   | 0     | 1.5  | mT            | TLV4946-2K                                       |

| Temperature compensation of                        | TC        | _      | -2000 | _    | ppm/°C        | TLV4946K                                         |

| magnetic thresholds                                |           | _      | -350  | _    | ppm/°C        | TLV4946-2K                                       |

| Repeatability of magnetic thresholds <sup>4)</sup> | $B_{REP}$ | -      | 20    | _    | $\mu T_{RMS}$ | typical value for $\Delta B/\Delta t > 12 mT/ms$ |

<sup>1)</sup> Over all operating conditions

<sup>2)</sup> at 25°C.

<sup>3)</sup>  $B_{OFF} = (B_{OP} + B_{RP}) / 2$ .

<sup>4)</sup>  $B_{REP}$  is equivalent to the noise constant.

**Package Information**

## 4 Package Information

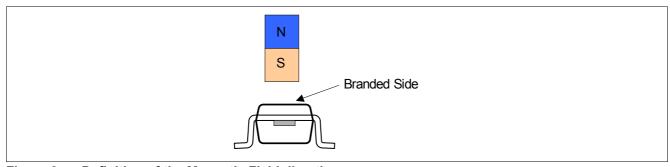

#### 4.1 TLV4946K and TLV4946-2K Package Outline

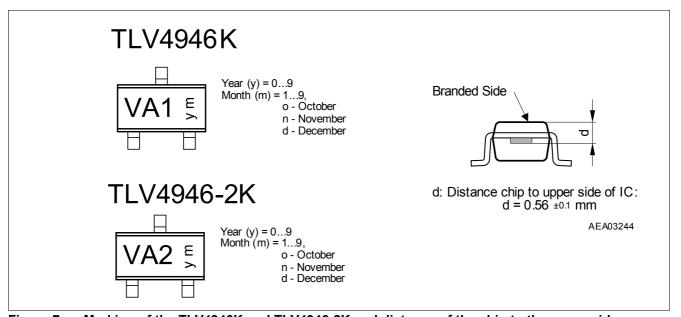

Figure 7 Marking of the TLV4946K and TLV4946-2K and distance of the chip to the upper side

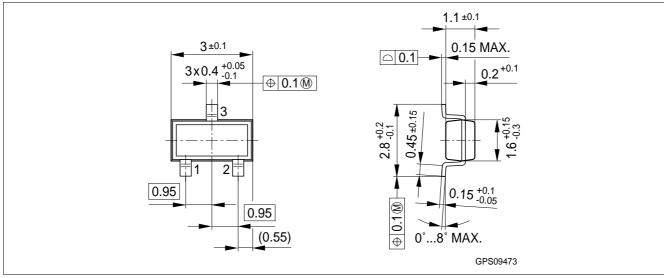

Figure 8 PG-SC59-3-5 Package Outline

Datasheet 14 Rev1.1, 2010-08-02

**Package Information**

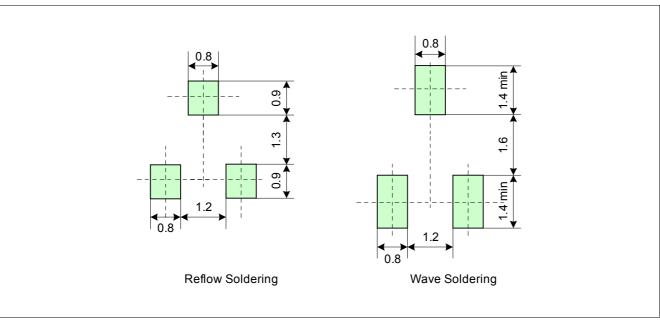

Figure 9 Footprint PG-SC59-3-5 (SOT23 compatible)

www.infineon.com Published by Infineon Technologies AG