Engine Management IC for Small Engines

TLE8080EM TLE8080-2EM

# Data Sheet

Rev. 1.1, 2012-10-19

# Automotive Power

### **Table of Contents**

### **Table of Contents**

| 1                                               | Overview                                                                                                                                                                                                                                           | 3                    |

|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 2                                               | Block Diagram                                                                                                                                                                                                                                      | 4                    |

| <b>3</b><br>3.1<br>3.2                          | Pin Configuration         Pin Assignment         Pin Definitions and Functions                                                                                                                                                                     | 5                    |

| 4                                               | General Product Characteristics                                                                                                                                                                                                                    | 7                    |

| <b>5</b><br>5.1<br>5.2<br>5.3<br>5.4            | 5V Supply, Reset and Supervision         5V Supply         Power On Reset and Reset Output         Watchdog Operation         Electrical Characteristics 5V Supply, Reset and Supervision                                                          | 9<br>9<br>10         |

| <b>6</b><br>6.1<br>6.2                          | Power Stages                                                                                                                                                                                                                                       | 14                   |

| <b>7</b><br>7.1                                 | Variable Reluctance Sensor (VRS) Interface         2           Electrical Characteristics VR Sensor Interface         2                                                                                                                            |                      |

| <b>8</b><br>8.1<br>8.2<br>8.2.1<br>8.2.2<br>8.3 | Serial Peripheral Interface (SPI)       2         SPI Signal Description       2         SPI Protocol       2         SPI Register       2         Set and Reset of Diagnosis Register Bits       2         Electrical Characteristics SPI       2 | 24<br>24<br>26<br>28 |

| <b>9</b><br>9.1<br>9.2                          | K-Line                                                                                                                                                                                                                                             | 33                   |

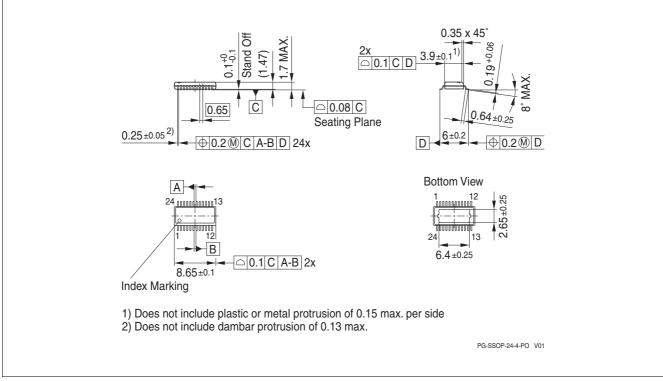

| 10                                              | Package Outlines                                                                                                                                                                                                                                   | 36                   |

| 11                                              | Revision History                                                                                                                                                                                                                                   | 37                   |

### **Engine Management IC for Small Engines**

### TLE8080EM

#### Features

- Supply 5V (+/-2%), 250mA

- K-line transceiver (ISO 9141)

- Serial Peripheral Interface (SPI)

- 4 low side driver for inductive loads with overtemperature and overcurrent protection and open load/short to GND in off diagnosis:

- 2 low side switches with maximum operation of 2.6A

- 2 low side switches with maximum operation of 350mA

- 1 low side driver for resistive loads with maximum operation current of 3A including overtemperature and overcurrent protection

- · Configurable variable reluctance sensor interface

- Reset output and 5V undervoltage detection

- Watchdog

- Green product (RoHS compliant)

- AEC qualified

#### Description

The TLE8080EM is an engine management IC based on Infineon Smart Power Technology (SPT). It is protected by embedded protection functions and integrates a power supply, K-line, SPI, variable reluctance sensor interface and power stages to drive different loads in an engine management system. It provides a compact and cost optimized solution for engine management systems. It is very suitable for one cylinder motorcycle engine management systems.

#### TLE8080-2EM

This version differs from the main version in the parameters "V5DD Reset Threshold for TLE8080-2EM" and "Power On Reset Delay Time" in Chapter 5.4.

For ordering conditions please contact the nearest Infineon Technologies office.

| Туре        | Package   | Marking     |

|-------------|-----------|-------------|

| TLE8080EM   | PG-SSOP24 | TLE8080EM   |

| TLE8080-2EM | PG-SSOP24 | TLE8080-2EM |

PG-SSOP24

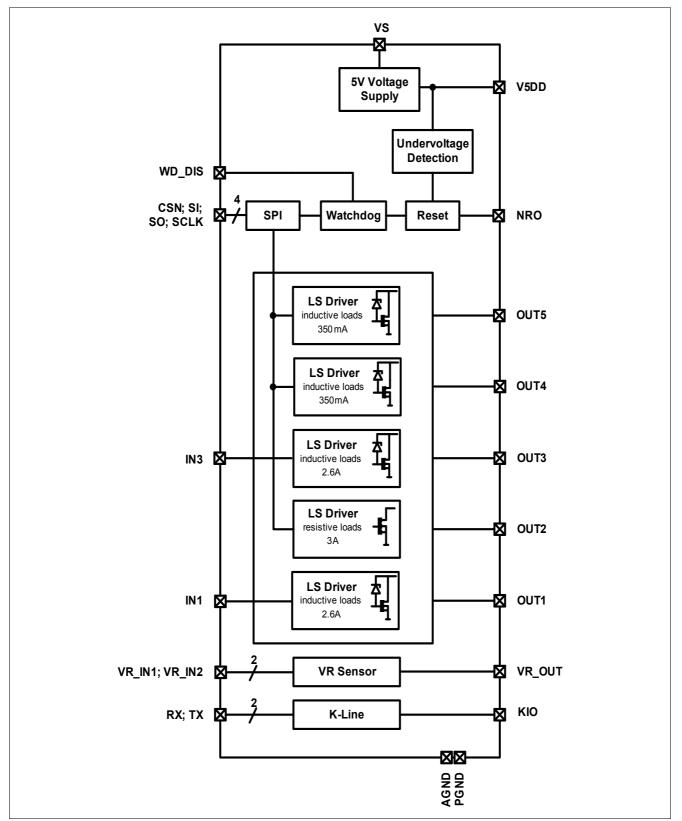

**Block Diagram**

### 2 Block Diagram

Figure 1 Block Diagram

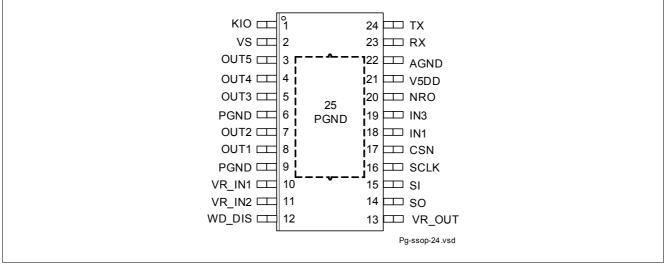

**Pin Configuration**

### 3 Pin Configuration

### 3.1 Pin Assignment

Figure 2 Pin Configuration

### 3.2 Pin Definitions and Functions

| Pin | Symbol | Function                                                                                   |

|-----|--------|--------------------------------------------------------------------------------------------|

| 1   | KIO    | K-Line Bus Connection                                                                      |

| 2   | VS     | <b>Battery Voltage:</b> Block to AGND directly at the IC with min. 100nF ceramic capacitor |

| 3   | OUT5   | Output Channel 5                                                                           |

| 4   | OUT4   | Output Channel 4                                                                           |

| 5   | OUT3   | Output Channel 3                                                                           |

| 6   | PGND   | Power Ground: internally connected to pin 9, connect externally to pin 9                   |

| 7   | OUT2   | Output Channel 2                                                                           |

| 8   | OUT1   | Output Channel 1                                                                           |

| 9   | PGND   | Power Ground: internally connected to pin 6, connect externally to pin 6                   |

| 10  | VR_IN1 | VR Sensor Interface Input 1                                                                |

| 11  | VR_IN2 | VR Sensor Interface Input 2                                                                |

| 12  | WD_DIS | Watchdog Disable: high active; internal pull down                                          |

| 13  | VR_OUT | VR Sensor Output                                                                           |

| 14  | SO     | SPI Slave Output: high impedance                                                           |

| 15  | SI     | SPI Slave Input: internal pull down                                                        |

| 16  | SCLK   | SPI Clock Input: internal pull down                                                        |

| 17  | CSN    | SPI Chip Select Input: low active; internal pull up                                        |

### **Pin Configuration**

| Pin | Symbol      | Function                                                                                                           |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------|

| 18  | IN1         | Control Input Channel 1: internal pull down                                                                        |

| 19  | IN3         | Control Input Channel 3: internal pull down                                                                        |

| 20  | NRO         | Reset Output: low active, open drain                                                                               |

| 21  | V5DD        | 5V Supply Output: connected to external blocking capacitor                                                         |

| 22  | AGND        | Analog Ground: connected to system logic ground                                                                    |

| 23  | RX          | K-Line Receive Output: logic output of data received from the K-Line bus KIO                                       |

| 24  | ТХ          | <b>K-Line Transmit Input:</b> logic level input for data to be transmitted on the K-Line bus KIO; internal pull up |

| 25  | Exposed Pad | Substrate Connection: must be connected to PGND externally on PCB                                                  |

### **General Product Characteristics**

### 4 General Product Characteristics

### Table 1 Absolute Maximum Ratings <sup>1)</sup>

$T_j$ = -40°C to +150°C: All voltages with respect to ground unless otherwise specified. Positive current flowing into pin (unless otherwise specified)

| Parameter                                              | Symbol                     | Values |      |               | Unit | Note /                                                         | Number |

|--------------------------------------------------------|----------------------------|--------|------|---------------|------|----------------------------------------------------------------|--------|

|                                                        |                            | Min.   | Тур. | Max.          |      | <b>Test Condition</b>                                          |        |

| Voltages                                               |                            |        |      |               |      |                                                                |        |

| Supply Voltage VS                                      | V <sub>VS</sub>            | -0.3   | -    | 40            | V    | -                                                              | 4.1.1  |

| Supply Voltage V5DD                                    | V <sub>V5DD</sub>          | -0.3   | -    | 5.5           | V    | -                                                              | 4.1.2  |

| Input Voltage on Pins IN1,<br>IN3, SCLK, SI, WD_DIS    | V <sub>x</sub>             | -0.3   | -    | 5.5           | V    | -                                                              | 4.1.3  |

| Input Voltage on Pins CSN,<br>TX                       | V <sub>x</sub>             | -0.3   | -    | V5DD<br>+0.3V | V    | -                                                              | 4.1.3  |

| Input Voltage VR_IN1,<br>VR_IN2                        | V <sub>VR_IN1/2</sub>      | -0.3   | -    | 5.5           | V    | see also 4.2.1<br>and 4.2.2                                    | 4.1.4  |

| DC Voltage on Pins OUT1-5,<br>KIO                      | V <sub>x</sub>             | -0.3   | -    | 30            | V    | respect to PGND<br>all channels and<br>KIO are switched<br>off | 4.1.5  |

| DC Voltage on Pins<br>VR_OUT, SO, RX, NRO              | V <sub>x</sub>             | -0.3   | -    | 5.5           | V    | l <sub>x</sub> <1mA                                            | 4.1.6  |

| DC Voltage AGND to PGND                                | V <sub>x</sub>             | -0.3   | -    | 0.3           | V    |                                                                | 4.1.7  |

| DC Voltage on Pin KIO                                  | V <sub>KIO</sub>           | -0.3   | -    | 35            | V    | respect to PGND<br>KIO is switched off                         | 4.1.8  |

| Currents                                               |                            |        |      |               | ·    |                                                                |        |

| Input Current between<br>VR_IN1 and VR_IN2             | I <sub>VR_IN1,VR_IN2</sub> |        | -    | 50            | mA   | -                                                              | 4.2.1  |

| Input Current VR_IN1,<br>VR_IN2 to GND                 | I <sub>VR_IN1/2,GND</sub>  |        | -    | 10            | mA   | -                                                              | 4.2.2  |

| Temperatures                                           |                            |        |      |               |      |                                                                |        |

| Junction Temperature                                   | T                          | -40    | -    | 150           | °C   | -                                                              | 4.3.1  |

| Storage Temperature                                    | T <sub>stg</sub>           | -55    | -    | 150           | °C   | -                                                              | 4.3.2  |

| ESD Susceptibility                                     |                            |        |      |               |      |                                                                |        |

| ESD Resistivity all Pins to GND                        | V <sub>ESD</sub>           | -2     | -    | 2             | kV   | HBM <sup>2)</sup>                                              | 4.4.1  |

| ESD Resistivity all Pins to GND                        | V <sub>ESD</sub>           | -500   | -    | 500           | V    | CDM <sup>3)</sup>                                              | 4.4.2  |

| ESD Resistivity Pin 1, 12, 13, 24 (corner pins) to GND | V <sub>ESD1,19,20,36</sub> | -750   | -    | 750           | V    | CDM <sup>3)</sup>                                              | 4.4.3  |

1) Not subject to production test, specified by design.

2) ESD susceptibility, HBM according to EIA/JESD 22-A114B

3) ESD susceptibility, Charged Device Model "CDM" EIA/JESD22-C101 or ESDA STM5.3.1

### **General Product Characteristics**

### Notes

- 1. Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

### Table 2 Functional Range

| Parameter            | Symbol | Values |      | 3    | Unit | Note /         | Number |

|----------------------|--------|--------|------|------|------|----------------|--------|

|                      |        | Min.   | Тур. | Max. |      | Test Condition |        |

| Supply Voltage       | Vs     | 6      | -    | 18   | V    | -              | 4.5.1  |

| Junction Temperature | Tj     | -40    | -    | 150  | °C   | -              | 4.5.2  |

Note: Within the functional range the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the related electrical characteristics table.

### Table 3 Thermal Resistance

| Parameter           | Symbol            |      | Values |      |     | Note /         | Number |

|---------------------|-------------------|------|--------|------|-----|----------------|--------|

|                     |                   | Min. | Тур.   | Max. |     | Test Condition |        |

| Junction to Case    | R <sub>thJC</sub> | -    | 7      | -    | K/W | 1)             | 4.6.1  |

| Junction to Ambient | R <sub>thJA</sub> | -    | 29     | -    | K/W | 1) 2)          | 4.6.2  |

1) Not subject to production test, specified by design

Specified R<sub>thJA</sub> value is according to Jedec JESD51-2,-5,-7 at natural convection on FR4 2s2p board; The Product (Chip+Package) was simulated on a 76.2 x 114.3 x 1.5 mm board with 2 inner copper layers (2 x 70µm Cu, 2 x 35µm Cu). Where applicable a thermal via array under the exposed pad contacted the first inner copper layer.

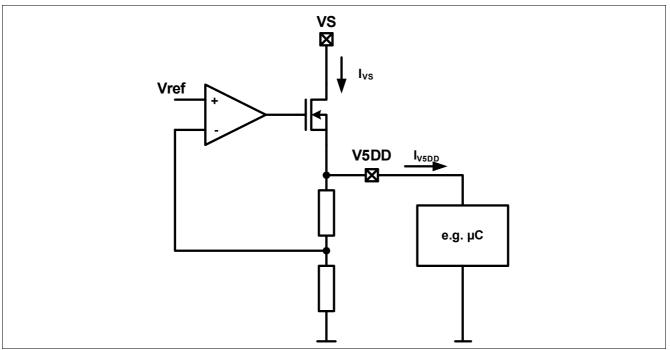

### 5 5V Supply, Reset and Supervision

### 5.1 5V Supply

The TLE8080EM integrates a voltage regulator for load currents up to 250mA. The input voltage at VS is regulated to 5V on V5DD with a precision of  $\pm 2\%$ . The design allows to achieve stable operation even with ceramic output capacitors down to 470 nF. It is protected against overload, short circuit, and over temperature conditions. For low drop operation, a charge pump is implemented.

Figure 3 5V Supply

### 5.2 Power On Reset and Reset Output

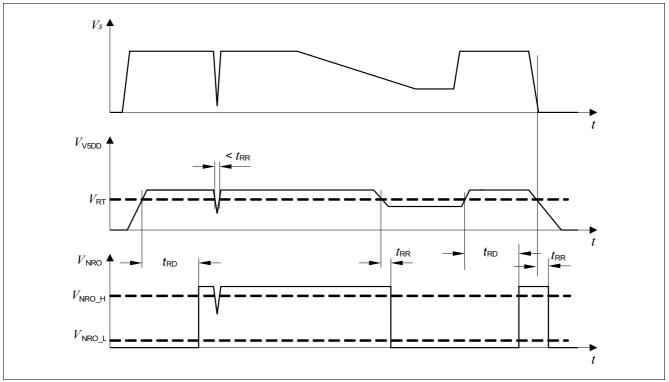

The reset output NRO is an open drain output. When the level of  $V_{V5DD}$  reaches the reset threshold ( $V_{RT}$ ) (increasing voltage  $V_{V5DD}$ ) the signal at NRO remains low for the power-up reset delay time ( $t_{RD}$ ). The reset function and timing is illustrated in **Figure 4**. The reset reaction time ( $t_{RR}$ ) avoids wrong triggering caused by short "glitches" on the V5DD-line. In case of V5DD power down (decreasing voltage;  $V_{V5DD} < V_{RT}$  for  $t > t_{RR}$ ) a logic low signal is generated at the pin NRO to reset an external micro controller. The level of the reset threshold for increasing  $V_{V5DD}$  is for the hysteresis ( $V_{RH}$ ) higher than the level for decreasing  $V_{V5DD}$ .

With an active reset all power stages and the K-Line output are disabled and SPI commands are ignored.

5V Supply, Reset and Supervision

Figure 4 Reset Timing Diagram

### 5.3 Watchdog Operation

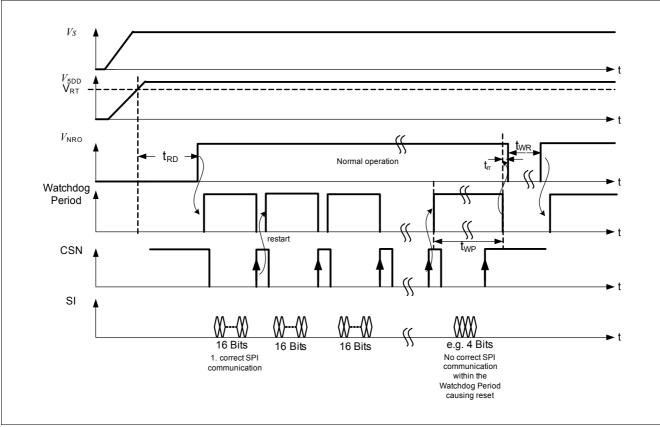

The TLE8088EE integrates a watchdog function which monitors the correct SPI communication with the micro controller. A watchdog disable pin (WD\_DIS) with an internal pull down current source is implemented. With a high level the watchdog function is disabled.

For enabled watchdog function after power-up reset delay time ( $t_{RD}$ ), valid SPI communication from the micro controller must occur within the watchdog period ( $t_{WP}$ ) specified in the electrical characteristics. A restart of the watchdog period is done with a low to high transition of the CSN pin of a valid transmission of a 16 bit message.

A reset is generated (NRO goes LOW) for the time ( $t_{WR}$ ) if there is no restart during the watchdog period as shown in **Figure 5**.

Status after watchdog overflow:

- all outputs are switched off

- · SPI registers are not influenced

- · Watchdog Time Out bit in SPI status register is set

- first answer to SPI communication is the content of the status register

Switching of Outputs and reset of Watchdog Time Out Bit after watchdog overflow:

- Outputs 1 and 3 will be switched on with an positive edge at IN1 respectively IN3

- Outputs 2, 4 and 5 will be switched on with a write command to CMD register

- the watchdog time out bit will be reset with the rising edge of CSN of the first read command of the status register

# infineon

### TLE8080EM

5V Supply, Reset and Supervision

Figure 5 Watchdog Timing Diagram

### 5V Supply, Reset and Supervision

### 5.4 Electrical Characteristics 5V Supply, Reset and Supervision

### Table 4 Electrical Characteristics: 5V Supply, Reset and Supervision

$V_s$ =13.5V,  $T_j$ = -40°C to +150°C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                               | Symbol                    | Values |      |      | Unit     | Note /                                                                       | Number |

|-----------------------------------------|---------------------------|--------|------|------|----------|------------------------------------------------------------------------------|--------|

|                                         |                           | Min.   | Тур. | Max. |          | <b>Test Condition</b>                                                        |        |

| 5V Supply                               |                           |        |      |      | <b>!</b> | -                                                                            |        |

| Output Voltage                          | V <sub>V5DD</sub>         | 4.9    | 5    | 5.1  | V        | 0 mA < $I_{V5DD}$ < 250mA<br>6V < $V_{S}$ < 18V                              | 5.1.1  |

| Output Current Limitation               | I <sub>V5DD</sub>         | 250    | -    | 650  | mA       | $V_{\rm V5DD}$ = 0V                                                          | 5.1.2  |

| Load Regulation                         | $\Delta V_{ m V5DD,\ Lo}$ | -      | -    | 50   | mV       | 1 mA < I <sub>V5DD</sub> < 250mA                                             | 5.1.3  |

| Line Regulation                         | $\Delta V_{ m V5DD,\ Li}$ | -      | -    | 10   | mV       | $I_{V5DD}$ = 1mA<br>10V < $V_{S}$ < 18V                                      | 5.1.4  |

| Power Supply Rejection                  | PSRR                      | -      | 60   | -    | dB       | f = 100Hz<br>$V_{\text{S, ripple}}$ = 0.5<br>Vpp <sup>1</sup> )              | 5.1.5  |

| Output Capacitor                        | $C_{\rm V5DD}$            | 470    | -    | -    | nF       | 1)                                                                           | 5.1.6  |

| Output Capacitor ESR                    | $ESR(C_{V5DD})$           | -      | -    | 10   | Ω        | 1)                                                                           | 5.1.7  |

| Current Consumption                     | I <sub>VS</sub>           | -      | 5.5  | 8    | mA       | $I_{\rm V5DD}$ = 0mA, all channels and K-Line off                            | 5.1.8  |

| Low Drop Voltage                        | V <sub>V5DD</sub>         | 4.8    | -    | 5    | V        | $I_{\rm V5DD}$ = 1mA<br>$V_{\rm S}$ =5V                                      | 5.1.9  |

|                                         |                           | 4.15   | -    | 5    | V        | $I_{V5DD}$ = 250mA<br>$V_{S}$ =5V;<br>after device<br>ramp-up ( $V_{S}$ >9V) | 5.1.10 |

| <b>Over Temperature Protectio</b>       | n                         |        |      |      | <b>I</b> |                                                                              |        |

| Over Temperature Threshold              | T <sub>OT</sub>           | 150    | -    | 200  | °C       | 1)                                                                           | 5.2.1  |

| Over Temperature Hysteresis             | $T_{\rm OT,Hys}$          | -      | 20   | -    | °C       | 1)                                                                           | 5.2.2  |

| Under Voltage Detection                 | , .                       | •      |      |      | - 1      | +                                                                            | •      |

| V5DD Reset Threshold                    | V <sub>RT</sub>           | 4.00   | 4.25 | 4.50 | V        | $V_{\rm V5DD}$ decreasing only at version TLE8080EM                          | 5.3.1  |

| Reset Hysteresis                        | V <sub>RH</sub>           | 10     | -    | 150  | mV       |                                                                              | 5.3.2  |

| V5DD Reset Threshold for<br>TLE8080-2EM | V <sub>RT</sub>           | 3.4    | 3.65 | 3.9  | V        | $V_{\rm V5DD}$ decreasing only at version TLE8080-2EM                        | 5.3.3  |

### 5V Supply, Reset and Supervision

### Table 4 Electrical Characteristics: 5V Supply, Reset and Supervision (cont'd)

$V_s$ =13.5V,  $T_j$ = -40°C to +150°C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                  | Symbol                  | Values |      |      | Unit | Note /                         | Number |

|----------------------------|-------------------------|--------|------|------|------|--------------------------------|--------|

|                            |                         | Min.   | Тур. | Max. |      | <b>Test Condition</b>          |        |

| Power On Reset             | 1                       |        |      |      |      |                                |        |

| Power On Reset Delay Time  | t <sub>RD</sub>         | 10     | 15   | 20   | ms   | only at version<br>TLE8080EM   | 5.4.1  |

|                            |                         | 30     | 40   | 50   | ms   | only at version<br>TLE8080-2EM | 5.4.2  |

| Reset Reaction Time        | t <sub>RR</sub>         | 10     | 15   | 20   | μs   |                                | 5.4.3  |

| Reset Output NRO           |                         |        |      |      | #    | -                              |        |

| Low Level Output Voltage   | $V_{\rm NRO,L}$         | -      | -    | 1.1  | V    | $I_{\rm NRO}$ = 1mA            | 5.5.1  |

| Watchdog                   |                         |        |      |      |      |                                |        |

| Watchdog Period            | t <sub>WP</sub>         | 50     | 60   | 70   | ms   |                                | 5.6.1  |

| Watchdog Reset Time        | t <sub>WR</sub>         | 120    | 240  | 360  | μs   |                                | 5.6.2  |

| Input Characteristics WD_D | IS                      |        |      |      |      |                                |        |

| Low Level Input Voltage    | $V_{\rm WD\_DIS,L}$     | -      | -    | 1    | V    |                                | 5.7.1  |

| High Level Input Voltage   | V <sub>WD_DIS,H</sub>   | 2      | -    | -    | V    |                                | 5.7.2  |

| Pull Down Current          | I <sub>WD_DIS,pd</sub>  | 20     | 50   | 100  | μA   | at V <sub>IN</sub> = 5V        | 5.7.3  |

| Pull Down Current          | I <sub>WD_DIS,pd</sub>  | 2.4    | -    | -    | μA   | at V <sub>IN</sub> = 0.6V      | 5.7.4  |

| Hysteresis                 | V <sub>WD_DIS,Hys</sub> | 30     |      | 250  | mV   |                                | 5.7.5  |

1) Not subject to production test, specified by design

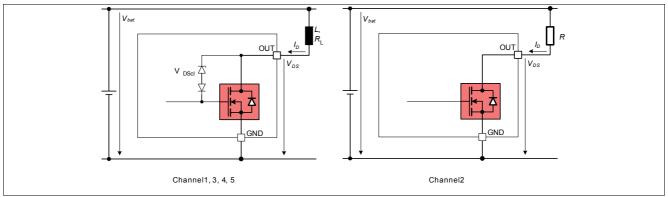

### 6.1 Low Side Switches

The power stages are built by N-channel power MOSFET transistors. The channels are universal multi channel switches, but are mostly suitable to be used in engine management systems. Within an engine management system, the best fit of the channels to the typical loads is:

- Channel 1 and 3 for injector valves or similar sized solenoids with a maximum operation current requirement of 2.6A

- · Channel 2 for malfunction indication lamps or other resistive loads with a maximum current requirement of 3A

- · Channel 4 and 5 for relays or other inductive loads with a maximum current requirement of 350mA

The channels are switched off while reset is active (pin NRO is low). After an power on reset the channels will be switched on with a positive edge at IN1 respectively IN3 or with a switch on command over SPI.

### Figure 6 Low Side Switches

In Table 5 the control concept, typical loads, the implemented protection and monitor functions are illustrated.

| Channel | Control                   | Recommended<br>Load | Over<br>Temperature                                            | Over Current                                         | Open<br>Load/Short<br>to GND |

|---------|---------------------------|---------------------|----------------------------------------------------------------|------------------------------------------------------|------------------------------|

| 1       | Pin IN1                   | Injector Valve      | x                                                              | Latch <sup>1)</sup>                                  | x                            |

| 2       | SPI CMD Register<br>Bit 0 | MIL (max. 3W)       | x                                                              | repetitive switching;<br>off time $t_{oc,off}^{(1)}$ | -                            |

| 3       | Pin IN3                   | Valve               | x                                                              | Latch <sup>1)</sup>                                  | x                            |

| 4       | SPI CMD Register<br>Bit 1 | Relay               | one<br>temperature<br>sensor for<br>channel 4 and<br>channel 5 | Latch <sup>1)</sup>                                  | x                            |

| 5       | SPI CMD Register<br>Bit 2 | Relay               | one<br>temperature<br>sensor for<br>channel 4 and<br>channel 5 | Latch <sup>1)</sup>                                  | x                            |

### Table 5 Overview Diagnosis Function

1)Reset behavior of the diagnosis bits see Chapter 8.2

#### **Power Stages**

In overcurrent condition the affected channel will be switched off. There are two different implementations for switching on again after an over current event.

For channels 1, 3, 4 and 5 the switch off state is latched. The input pins IN1, IN3 must be set to low to reset the latch before the channel can be switched on again.

For channels 4 and 5 the over current status is reset with a write command to the CMD register. The switching state is according to the status of bit 1 and 2.

Channel 2 will be switched off and after  $t_{oc_off}$  = 5ms typically the channel will be switched on again automatically. The result is repetitive switching with a fixed off time of  $t_{oc,off}$ . The overcurrent status of channel 2 is internally latched. For releasing the over current diagnosis bit after over current condition, channel 2 must stay switched on for at least  $t_{oc,St}$ .

The bits 0 to 4 in the Stat register reflect the actual switching status of the channels.

For detailed description see Chapter 8.2.2.

All the channels are protected from over temperature. In an overtemperature situation the affected channel will be switched off. The channel will restart operation if the junction temperature decreases by thermal shutdown hysteresis  $T_{\text{OT,Hys}}$ . Channels 4 and 5 are using a common temperature sensor. Therefore, the two channels are switched together during over temperature.

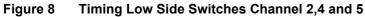

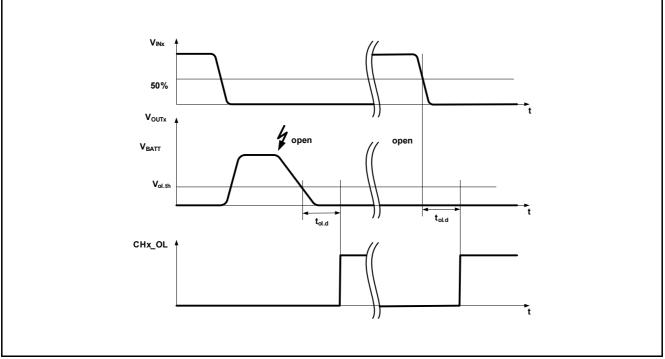

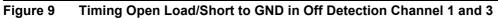

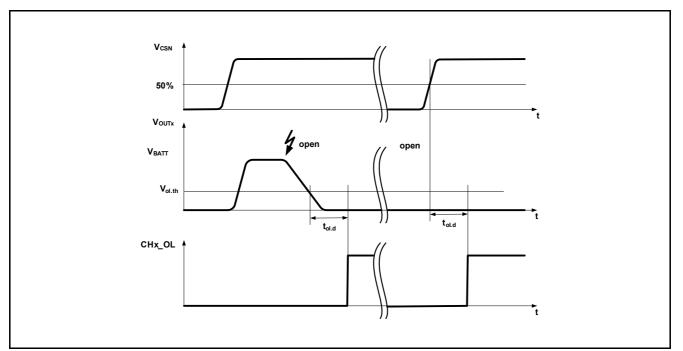

For channels 1, 3, 4 and 5 an open load/short to GND in off detection with a pull down current source (active in off) and a comparator is implemented. In case of switch off and the output voltage is below the open load detection threshold ( $V_{outx} < V_{ol,th}$ ), the open load in off timer is started. After the open load in off delay time  $t_{ol,d}$ , the open load is detected (timing see **Figure 9** and **Figure 10**).

The diagnosis status of the channels is monitored in the SPI Diagnosis Register DIAG (see Chapter 8.2).

### 6.2 Electrical Characteristics Low Side Switches

### Table 6 Electrical Characteristics: Power Stage

$V_s$ =13.5V,  $T_j$ = -40°C to +150°C: All voltages with respect to ground. Positive current flowing into pin (unless otherwise specified).

| Parameter                                       | Symbol               |      | Value | Values |    | Note /                                                                   | Number |

|-------------------------------------------------|----------------------|------|-------|--------|----|--------------------------------------------------------------------------|--------|

|                                                 |                      | Min. | Тур.  | Max.   |    | <b>Test Condition</b>                                                    |        |

| Output Channel 1 and 3                          |                      |      | -     |        |    | -                                                                        | •      |

| On Resistance                                   | R <sub>OUTx_on</sub> | -    | 0.6   | 0.7    | Ω  | $I_{OUTx_{nom}} = 1.3A;$<br>$T_{j} = 150^{\circ}C$                       | 6.1.1  |

| Output Clamping Voltage                         | $V_{\rm OUTx\_cl}$   | 30   | 35    | 40     | V  | <i>I</i> <sub>OUTx</sub> = 0.02A                                         | 6.1.2  |

| Over-current Switch Off<br>Threshold            | I <sub>OUTx_oc</sub> | 2.6  | -     | 5      | A  |                                                                          | 6.1.3  |

| Over-current Switch Off Filter<br>Time          | t <sub>oc,f</sub>    | 0.5  | -     | 3      | μS |                                                                          | 6.1.4  |

| Over Temperature Switch Off                     | T <sub>OT</sub>      | 150  | _     | 200    | °C |                                                                          | 6.1.5  |

| Over Temperature Hysteresis                     | $T_{\rm OT,Hys}$     | _    | 20    | -      | °C |                                                                          | 6.1.6  |

| Open Load in Off Detection<br>Threshold         | V <sub>ol,th</sub>   | 2    | 2.8   | 3.2    | V  |                                                                          | 6.1.7  |

| Open Load in Off Pull Down<br>Diagnosis Current | I <sub>ol</sub>      | 50   | 100   | 150    | μA | V <sub>OUTx</sub> = 13.5V                                                | 6.1.8  |

| Open Load in Off Diagnosis<br>Delay Time        | t <sub>ol,d</sub>    | 100  | -     | 200    | μS |                                                                          | 6.1.9  |

| Turn On Delay Time                              | t <sub>d,ON</sub>    | -    | 0.25  | 1      | μS | $V_{OUTx}$ = 13.5V<br>$I_{OUTx}$ = 1.3A,<br>resistive load <sup>1)</sup> | 6.1.10 |

| Turn Off Delay Time                             | t <sub>d,OFF</sub>   | -    | 0.9   | 1.5    | μS | $V_{OUTx}$ = 13.5V<br>$I_{OUTx}$ = 1.3A,<br>resistive load <sup>1)</sup> | 6.1.11 |

| Turn On Time                                    | t <sub>s,ON</sub>    | -    | 0.6   | 1.2    | μs | $V_{OUTx}$ = 13.5V<br>$I_{OUTx}$ = 1.3A,<br>resistive load <sup>1)</sup> | 6.1.12 |

| Turn Off Time                                   | t <sub>s,OFF</sub>   | -    | 0.6   | 1.2    | μS | $V_{OUTx}$ = 13.5V<br>$I_{OUTx}$ = 1.3A,<br>resistive load <sup>1)</sup> | 6.1.13 |

| Output Leakage Current in<br>Off Mode           | $I_{\rm OUTx\_off}$  | -    | -     | 3      | μA | $V_{OUTx} = 13.5V$<br>$T_{j} = 150^{\circ}C^{2)}$                        | 6.1.14 |

| Output Channel 2                                | I                    | J    | 1     | 1      | 1  |                                                                          | 1      |

| On Resistance                                   | R <sub>OUTx_on</sub> | -    | 1.1   | 1.2    | Ω  | $I_{OUTx\_nom} = 0.3A;$<br>$T_j = 150^{\circ}C$                          | 6.2.1  |

| Over-current Switch Off<br>Threshold            | $I_{\rm OUTx\_oc}$   | 3    | -     | 6.5    | A  |                                                                          | 6.2.2  |

| Over-current Switch Off Filter<br>Time          | t <sub>oc,f</sub>    | 0.5  | -     | 3      | μS |                                                                          | 6.2.3  |

| Over-current Switch Off Time                    | t <sub>oc,off</sub>  | 3    | _     | 8      | ms |                                                                          | 6.2.4  |

### Table 6 Electrical Characteristics: Power Stage (cont'd)

$V_s$ =13.5V,  $T_j$ = -40°C to +150°C: All voltages with respect to ground. Positive current flowing into pin (unless otherwise specified).

| Parameter                                       | Symbol               |      | Value | 5    | Unit     | Note /                                                                   | Number |

|-------------------------------------------------|----------------------|------|-------|------|----------|--------------------------------------------------------------------------|--------|

|                                                 |                      | Min. | Тур.  | Max. |          | <b>Test Condition</b>                                                    |        |

| Over-current Status Time                        | t <sub>oc,St</sub>   | 1    | -     | 12   | ms       |                                                                          | 6.2.5  |

| Over Temperature Switch Off                     | T <sub>OT</sub>      | 150  | -     | 200  | °C       |                                                                          | 6.2.6  |

| Over Temperature Hysteresis                     | $T_{\rm OT,Hys}$     | -    | 20    | -    | °C       |                                                                          | 6.2.7  |

| Turn On Delay Time                              | t <sub>d,ON</sub>    | -    | 0.6   | 1.2  | μs       | $V_{OUTx}$ = 13.5V<br>$I_{OUTx}$ = 1.3A,<br>resistive load <sup>1)</sup> | 6.2.8  |

| Turn Off Delay Time                             | t <sub>d,OFF</sub>   | -    | 0.7   | 1.5  | μs       | $V_{OUTx}$ = 13.5V<br>$I_{OUTx}$ = 1.3A,<br>resistive load <sup>1)</sup> | 6.2.9  |

| Turn On Time                                    | t <sub>s,ON</sub>    | -    | 0.4   | 1    | μS       | $V_{OUTx}$ = 13.5V<br>$I_{OUTx}$ = 1.3A,<br>resistive load <sup>1)</sup> | 6.2.10 |

| Turn Off Time                                   | t <sub>s,OFF</sub>   | -    | 0.4   | 1    | μS       | $V_{OUTx}$ = 13.5V<br>$I_{OUTx}$ = 1.3A,<br>resistive load <sup>1)</sup> | 6.2.11 |

| Output Leakage Current in<br>Off Mode           | $I_{\rm OUTx\_off}$  | -    | -     | 3    | μA       | $V_{OUTx} = 13.5V$<br>$T_{j} = 150^{\circ}C$                             | 6.2.12 |

| Output Channel 4 and 5                          |                      | I    |       |      | <b>I</b> |                                                                          |        |

| On Resistance                                   | R <sub>OUTx_on</sub> | -    | 3.3   | 3.6  | Ω        | $I_{OUTx_nom} = 0.3A;$<br>$T_i = 150^{\circ}C$                           | 6.3.1  |

| Output Clamping Voltage                         | $V_{\rm OUTx\_cl}$   | 30   | 35    | 40   | V        | <i>I</i> <sub>OUTx</sub> = 0.02A                                         | 6.3.2  |

| Over-current Switch Off<br>Threshold            | I <sub>OUTx_oc</sub> | 350  | -     | 600  | mA       |                                                                          | 6.3.3  |

| Over-current Switch Off Filter<br>Time          | t <sub>oc,f</sub>    | 0.8  | -     | 2.4  | μS       |                                                                          | 6.3.4  |

| Over Temperature Switch Off                     | T <sub>OT</sub>      | 150  | _     | 200  | °C       |                                                                          | 6.3.5  |

| Over Temperature Hysteresis                     | T <sub>OT,Hys</sub>  | -    | 20    | -    | °C       |                                                                          | 6.3.6  |

| Open Load in Off Detection<br>Threshold         | V <sub>ol,th</sub>   | 2    | 2.8   | 3.2  | V        |                                                                          | 6.3.7  |

| Open Load in Off Pull Down<br>Diagnosis Current | I <sub>ol</sub>      | 50   | 100   | 150  | μA       | V <sub>OUTx</sub> = 13.5V                                                | 6.3.8  |

| Open Load in Off Diagnosis<br>Delay Time        | t <sub>ol,d</sub>    | 100  | -     | 200  | μs       |                                                                          | 6.3.9  |

| Turn On Delay Time                              | t <sub>d,ON</sub>    | -    | 0.5   | 1.2  | μS       | $V_{OUTx}$ = 13.5V<br>$I_{OUTx}$ = 0.3A,<br>resistive load <sup>1)</sup> | 6.3.10 |

| Turn Off Delay Time                             | t <sub>d,OFF</sub>   | -    | 0.7   | 1.5  | μS       | $V_{OUTx}$ = 13.5V<br>$I_{OUTx}$ = 0.3A,<br>resistive load <sup>1)</sup> | 6.3.11 |

### Table 6 Electrical Characteristics: Power Stage (cont'd)

$V_s$ =13.5V,  $T_j$ = -40°C to +150°C: All voltages with respect to ground. Positive current flowing into pin (unless otherwise specified).

| Parameter                             | Symbol                |          | Value    | s    | Unit | Note /                                                                   | Number |

|---------------------------------------|-----------------------|----------|----------|------|------|--------------------------------------------------------------------------|--------|

|                                       |                       | Min.     | Тур.     | Max. |      | Test Condition                                                           |        |

| Turn On Time                          | t <sub>s,ON</sub>     | -        | 0.1      | 0.8  | μS   | $V_{OUTx}$ = 13.5V<br>$I_{OUTx}$ = 0.3A,<br>resistive load <sup>1)</sup> | 6.3.12 |

| Turn Off Time                         | t <sub>s,OFF</sub>    | -        | 0.1      | 0.8  | μS   | $V_{OUTx}$ = 13.5V<br>$I_{OUTx}$ = 0.3A,<br>resistive load <sup>1)</sup> | 6.3.13 |

| Output Leakage Current in<br>Off Mode | I <sub>OUTx_off</sub> | -        | -        | 2    | μA   | $V_{OUTx} = 13.5V$<br>$T_{j} = 150^{\circ}C^{2)}$                        | 6.3.14 |

| Input Characteristic IN1 an           | d IN3                 | <u>!</u> | <b>i</b> |      |      | +                                                                        |        |

| Low Level Input Voltage               | $V_{\rm IN,L}$        | -        | -        | 1    | V    |                                                                          | 6.4.1  |

| High Level Input Voltage              | $V_{\rm IN,H}$        | 2        | _        | -    | V    |                                                                          | 6.4.2  |

| Input Voltage Hysteresis              | $V_{\rm IN,Hys}$      | 50       | 110      | 250  | mV   |                                                                          | 6.4.3  |

| Pull Down Current                     | $I_{\rm IN,PD}$       | 20       | 50       | 100  | μA   | $V_{\rm IN} = 5V$                                                        | 6.4.4  |

| Pull Down Current                     | $I_{\rm IN,PD}$       | 2.4      | _        | -    | μA   | V <sub>IN</sub> = 0.6V                                                   | 6.4.5  |

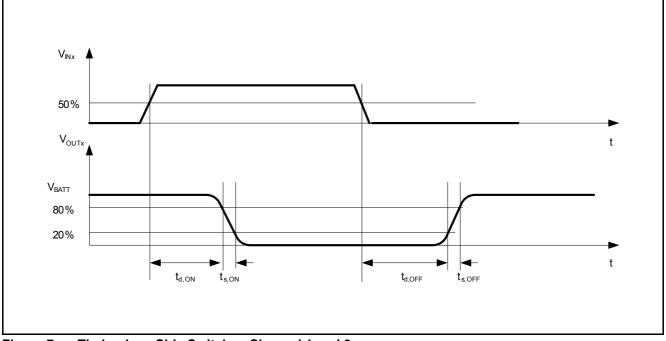

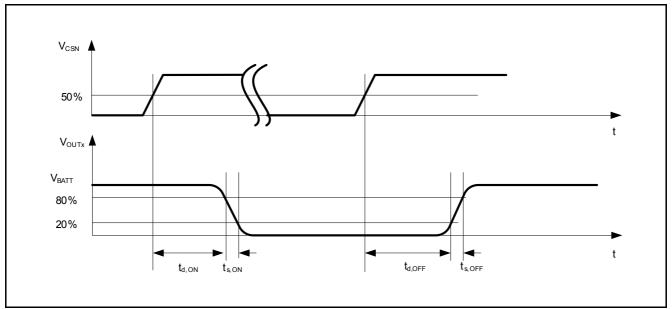

1)definition of timing see Figure 7 or Figure 8

2) in OFF mode open load diagnosis pull down current active

Figure 7 Timing Low Side Switches Channel 1 and 3

#### **Power Stages**

**Power Stages**

Figure 10 Timing Open Load/Short to GND in Off Detection Channel 2,4 and 5

Variable Reluctance Sensor (VRS) Interface

### 7 Variable Reluctance Sensor (VRS) Interface

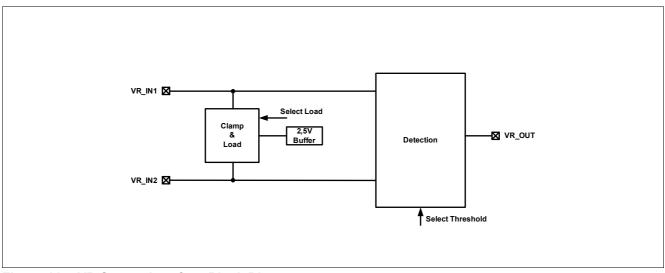

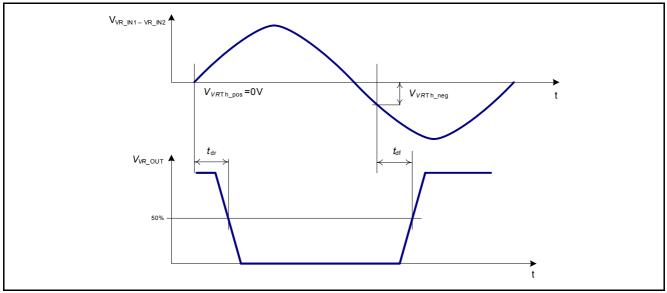

The variable reluctance (VR) sensor interface converts an output signal of a VR sensor into a logic level signal suited for  $\mu$ C 5V input ports. The voltage difference between the two input pins, VR\_IN1 and VR\_IN2, which are connected to the two output pins of the VR sensor, is detected and the output pin VR\_OUT is switched depending on the sign of the voltage difference ( see Figure 12 )The amplitude of the VR sensor signal is limited by an internal clamping circuit to avoid damage of the device due to over voltage caused by the VR sensor signal.

Figure 11 VR Sensor Interface Block Diagram

### Variable Reluctance Sensor (VRS) Interface

### 7.1 Electrical Characteristics VR Sensor Interface

### Table 7 Electrical Characteristics: VR Sensor Interface

$V_s$ =13.5V,  $T_j$ = -40°C to +150°C: All voltages with respect to ground. Positive current flowing into pin (unless otherwise specified)

| Parameter                                           | Symbol                |              | Value | 5    | Unit | Note /                                                               | Number |  |

|-----------------------------------------------------|-----------------------|--------------|-------|------|------|----------------------------------------------------------------------|--------|--|

|                                                     |                       | Min.         | Тур.  | Max. |      | Test Condition                                                       |        |  |

| Input Characteristics:                              | -                     |              | -     |      |      | •                                                                    |        |  |

| positive VR Sensor Interface<br>Detection Threshold | $V_{\rm VR,th\_pos}$  | -30          | 0     | 30   | mV   |                                                                      | 7.1.1  |  |

| negative VR Sensor Interface<br>Detection Threshold | $V_{\rm VR,th\_neg}$  | -80          | -50   | -20  | mV   | CMD Register:<br>VR_T[1:0] = "00"<br>Reset State                     | 7.1.2  |  |

|                                                     |                       | -130         | -100  | -70  | mV   | CMD Register:<br>VR_T[1:0] = "01"                                    | 7.1.3  |  |

|                                                     |                       | -550         | -500  | -450 | mV   | CMD Register:<br>VR_T[1:0] = "10"                                    | 7.1.4  |  |

|                                                     |                       | -1.1         | -1    | -0.9 | V    | CMD Register:<br>VR_T[1:0] = "11"                                    | 7.1.5  |  |

| VR Sensor Interface Load<br>Selection               | R <sub>VR,Load</sub>  | 30           | 75    | 120  | kΩ   | $T_j$ = 25°C;<br>CMD Register:<br>VR_L[1:0] = "00"<br>Reset State    | 7.1.6  |  |

|                                                     |                       |              | 90    |      | kΩ   | $T_j$ = -40°C;<br>CMD Register:<br>VR_L[1:0] = "00"<br>Reset State   |        |  |

|                                                     |                       |              | 60    |      | kΩ   | $T_{j}$ = 150°C;<br>CMD Register:<br>VR_L[1:0] = "00"<br>Reset State |        |  |

|                                                     |                       | 3            | 4.5   | 8    | kΩ   | CMD Register:<br>VR_L[1:0] = "01"                                    | 7.1.7  |  |

|                                                     |                       | 1.5          | 2.2   | 3.3  | kΩ   | CMD Register:<br>VR_L[1:0] = "10"                                    | 7.1.8  |  |

|                                                     |                       | 0.7          | 1.2   | 1.9  | kΩ   | CMD Register:<br>VR_L[1:0] = "11"                                    | 7.1.9  |  |

| VR Sensor Interface Input<br>Clamping Current       | I <sub>VR,clamp</sub> | -            | -     | ±50  | mA   |                                                                      | 7.1.10 |  |

| VR Sensor Interface Input<br>Clamping Voltage       | $V_{\rm VR, clamp}$   | ±2.5         | ±3    | ±3.5 | V    | I <sub>VR,clamp</sub> = ±50mA                                        | 7.1.11 |  |

| Output Characteristics:                             |                       |              |       |      |      |                                                                      |        |  |

| Low Level Output Voltage                            | $V_{\rm VR\_OUT,L}$   | -            | -     | 0.3  | V    | <i>I</i> <sub>VR_OUT-</sub> = 100μA                                  | 7.2.1  |  |

| High Level Output Voltage                           | V <sub>VR_OUT,H</sub> | V5DD-<br>0.3 | -     | -    | V    | $I_{\text{VR}_{\text{OUT}}}$ = -100µA                                | 7.2.2  |  |

### Variable Reluctance Sensor (VRS) Interface

### Table 7 Electrical Characteristics: VR Sensor Interface (cont'd)

$V_s$ =13.5V,  $T_j$ = -40°C to +150°C: All voltages with respect to ground. Positive current flowing into pin (unless otherwise specified)

| Parameter                               | Symbol          |      | Value     | s   | Unit | Note /                | Number |  |

|-----------------------------------------|-----------------|------|-----------|-----|------|-----------------------|--------|--|

|                                         |                 | Min. | Typ. Max. |     |      | <b>Test Condition</b> |        |  |

| Transfer Characteristics:               |                 |      |           |     |      |                       |        |  |

| Delay Time Input to VR_OUT falling edge | t <sub>dr</sub> | 1    | 1.5       | 2.5 | μS   |                       | 7.3.1  |  |

| Delay Time Input to VR_OUT rising edge  | t <sub>df</sub> | 1    | 1.5       | 2.5 | μS   |                       | 7.3.2  |  |

Figure 12 Timing Characteristics of the VR Sensor Interface

### 8 Serial Peripheral Interface (SPI)

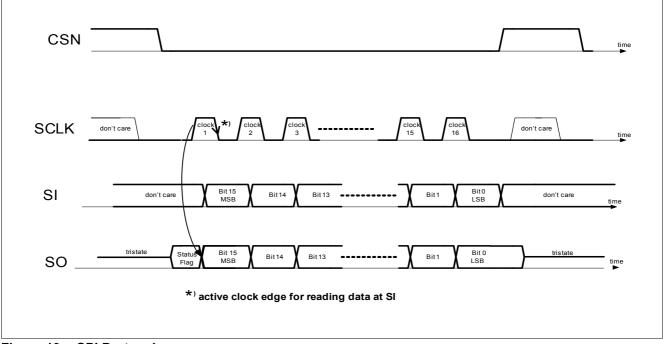

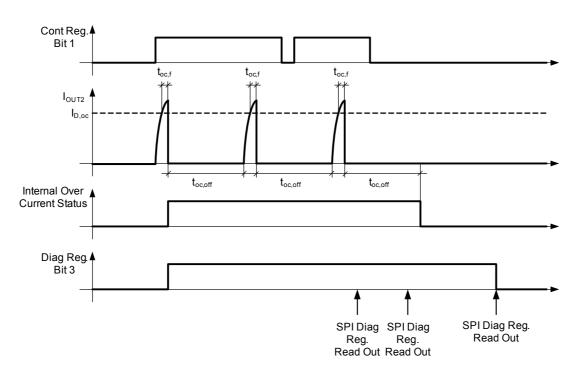

The diagnosis and control interface is based on a serial peripheral interface (SPI). The SPI is a 16 bit full duplex synchronous serial slave interface, which uses four lines: **SI**, **SO**, **SCLK** and **CSN**.

### 8.1 SPI Signal Description

### **CSN - Chip Select:**

The system micro controller selects the IC by means of the CSN pin. Whenever the pin is in low state, data transfer can take place. As long as CSN is in high state, all signals at the SCLK and SI pins are ignored and SO is forced to high impedance.

### CSN - High to Low Transition:

SO changes from high impedance to high or low state depending on the Status Flag (see Chapter 8.2).

### CSN - Low to High Transition:

End of transmission, the validation check of the communication is done (number of bits and valid command) and valid commands are executed.

### SCLK - Serial Clock:

This input pin clocks the internal shift register. The serial input (SI) transfers data into the shift register on the falling edge of SCLK while the serial output (SO) shifts information out on the rising edge of the serial clock. It is essential that the SCLK pin is in low state whenever chip select CSN makes any transition.

### SI - Serial Input:

Serial input data bits are shifted in at this pin, the most significant bit (MSB) first. SI information is read on the falling edge of SCLK. Please refer to **Section 8.2** for further information.

### SO - Serial Output:

Data is shifted out serially at this pin, the MSB first. SO is in high impedance until the CSN pin goes to low. The output level before the first rising edge of SCLK depends on the status flag. New data will appear at the SO pin following the rising edge of SCLK. Please refer to **Section 8.2** for further information.

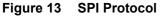

### 8.2 SPI Protocol

The principle of the SPI communication is shown in **Figure 13**. The message from the micro controller must be sent MSB first. The data from the **SO** pin is sent MSB first. The TLE8080EM samples data from the SI pin on the falling edge of SCLK and shifts data out of the SO pin on the rising edge of SCLK. Each access must be terminated by a rising edge of CSN.

All SPI messages must be exactly 16-bits long, otherwise the SPI message is discarded.

There is a one message delay in the response to each message (i.e. the response for message N will be returned during message N+1).

during message N+1).

The SPI protocol of the TLE8080EM provides three registers. The control register, the diagnosis, and the status register. The control register contains the set up bits for the VR sensor interface and the control bits of channels 2, 4 and 5. The diagnosis register contains the diagnosis bits of the five low side switches. The status register contains the status bits of the five low side switches, the watchdog status bit, and the watchdog time out bit. After power-on reset, all register bits are set to reset state (see Chapter 8.2.1).

There are four ways of valid access:

- Write access to the command register: the answer is 1 for the R/W bit, 00 for the address and the content of the register

- Read access to the command register: the answer is 0 for the R/W bit, 00 for the address and the content of the register

- Read access to the diagnosis register: the answer is 0 for the R/W bit, 01 for the address and the content of the register

- Read access to the status register: the answer is 0 for the R/W bit, 10 for the address and the content of the register

Any other access is recognized as an invalid message.

<u>Status Flag Indication</u>: after the falling edge of **CSN** and before the first rising edge of **SCLK**, the level of the **SO** indicates the status of the diagnosis register:

- **SO** = "0": no error condition detected; all diagnosis register bits are "0"

- SO = "1": one or more error conditions are detected; one or more diagnosis register bits are "1"

With this feature during every SPI communication a check of the diagnosis status can be done without additional read access of the diagnosis register.

### SPI Answers:

- during power on reset: SPI commands are ignored, SO is always low

- after power on reset: the content of the command register is transmitted with the next SPI transmission

- during watchdog reset: SPI commands are ignored, SO has the value of the status flag

- <u>after watchdog overflow:</u> the content of the status register is transmitted with the first SPI transmission after the low to high transition of NRO

- <u>after a read or write command</u>: the content of the selected register is transmitted with the next SPI transmission

- <u>after an invalid communication</u>: the content of the diagnosis register is transmitted with the next SPI transmission

### 8.2.1 SPI Register

### Overview

| 15  | 14  | 13  | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-----|-----|-----|----|----|----|---|---|---|---|---|---|---|---|---|---|--|

| R/W | AD1 | AD0 |    |    |    |   |   |   |   |   |   |   |   |   |   |  |

| Field    | Bits    | Туре | Description                                                                                                                |

|----------|---------|------|----------------------------------------------------------------------------------------------------------------------------|

| AD1:AD0] | [14:13] | W    | Address Bits:<br>00 <sub>B</sub> Control Register<br>01 <sub>B</sub> Diagnosis Register<br>10 <sub>B</sub> Status Register |

| R/W      | 15      | w    | Read - Write Bit:         0 <sub>B</sub> Read Access         1 <sub>B</sub> Write Access                                   |

#### CMD Register

### Command Register (Identifier x00x xxxx xxxx xxxx<sub>B</sub>)Reset Value: 0<sub>H</sub>

| 15  | 14  | 13  | 12    | 11    | 10    | 9     | 8 | 7 | 6 | 5 | 4 | 3 | 2    | 1    | 0    |

|-----|-----|-----|-------|-------|-------|-------|---|---|---|---|---|---|------|------|------|

| R/W | AD1 | AD0 | VR_T1 | VR_T0 | VR_L1 | VR_L0 |   |   |   |   |   |   | CTR5 | CTR4 | CTR2 |

|     |     | Į.  | rw    | rw    | rw    | rw    |   |   |   |   |   |   | rw   | rw   | rw   |

| Field        | Bits   | Туре | Description                                            |

|--------------|--------|------|--------------------------------------------------------|

| CTR2         | 0      | rw   | Control Bit Channel 2:                                 |

|              |        |      | 0 <sub>B</sub> Channel 2 is switched off (Reset State) |

|              |        |      | 1 <sub>B</sub> Channel 2 is switched on                |

| CTR4         | 1      | rw   | Control Bit Channel 4:                                 |

|              |        |      | 0 <sub>B</sub> Channel 4 is switched off (Reset State) |

|              |        |      | 1 <sub>B</sub> Channel 4 is switched on                |

| CTR5         | 2      | rw   | Control Bit Channel 5:                                 |

|              |        |      | 0 <sub>B</sub> Channel 5 is switched off (Reset State) |

|              |        |      | 1 <sub>B</sub> Channel 5 is switched on                |

| VR_L1: VR_L0 | [10:9] | rw   | Load Register of VR Interface:                         |

|              |        |      | (c.f. VR Sensor Interface Load Selection)              |

|              |        |      | $00_{B} R_{Load} = 75 k\Omega$ (Reset State)           |

|              |        |      | $01_B R_{Load} = 4.5 k\Omega$                          |

|              |        |      | $10_B R_{Load} = 2.2 k\Omega$                          |

|              |        |      | $11_B R_{Load} = 1.2 k\Omega$                          |

### Serial Peripheral Interface (SPI)

| Field        | Bits    | Туре | Description                         |  |

|--------------|---------|------|-------------------------------------|--|

| VR_T1: VR_T0 | [12:11] | rw   | Threshold Register of VR Interface: |  |

|              |         |      | 00 <sub>B</sub> -50mV (Reset State) |  |

|              |         |      | 01 <sub>B</sub> –100mV              |  |

|              |         |      | 10 <sub>B</sub> -500mV              |  |

|              |         |      | 11 <sub>B</sub> -1V                 |  |

### Diag Register

### Diagnosis Register (Identifier x01x xxxx xxxx xxxx<sub>B</sub>)Reset Value: 0<sub>H</sub>

| 15  | 14  | 13  | 12          | 11         | 10         | 9          | 8          | 7          | 6          | 5          | 4          | 3          | 2          | 1          | 0          |

|-----|-----|-----|-------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|

| R/W | AD1 | AD0 | CH45_<br>OT | CH5_<br>OC | CH5_<br>OL | CH4_<br>OC | CH4_<br>OL | СН3_<br>ОТ | СН3_<br>ОС | CH3_<br>OL | СН2_<br>ОТ | CH2_<br>OC | CH1_<br>OT | CH1_<br>OC | CH1_<br>OL |

|     |     |     | r           | r          | r          | r          | r          | r          | r          | r          | r          | r          | r          | r          | r          |

| Field  | Bits | Туре | Description                                                                                                                                           |

|--------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| CH1_OL | 0    | r    | Open Load Diagnosis Bit of Channel 1:<br>0 <sub>B</sub> no open load in off detected (Reset State)<br>1 <sub>B</sub> open load in off detected        |

| CH1_OC | 1    | r    | Over Current Diagnosis Bit of Channel 1:<br>0 <sub>B</sub> no over current detected (Reset State)<br>1 <sub>B</sub> over current detected             |

| CH1_OT | 2    | r    | Over Temperature Diagnosis Bit of Channel 1:<br>0 <sub>B</sub> no over temperature detected (Reset State)<br>1 <sub>B</sub> over temperature detected |

| CH2_OC | 3    | r    | Over Current Diagnosis Bit of Channel 2:<br>0 <sub>B</sub> no over current detected (Reset State)<br>1 <sub>B</sub> over current detected             |

| CH2_OT | 4    | r    | Over Temperature Diagnosis Bit of Channel 2:<br>0 <sub>B</sub> no over temperature detected (Reset State)<br>1 <sub>B</sub> over temperature detected |

| CH3_OL | 5    | r    | Open Load Diagnosis Bit of Channel 3:<br>0 <sub>B</sub> no open load in off detected (Reset State)<br>1 <sub>B</sub> open load in off detected        |

| СН3_ОС | 6    | r    | Over Current Diagnosis Bit of Channel 3:<br>0 <sub>B</sub> no over current detected (Reset State)<br>1 <sub>B</sub> over current detected             |

| СН3_ОТ | 7    | r    | Over Temperature Diagnosis Bit of Channel 3:<br>0 <sub>B</sub> no over temperature detected (Reset State)<br>1 <sub>B</sub> over temperature detected |

| CH4_OL | 8    | r    | Open Load Diagnosis Bit of Channel 4:<br>0 <sub>B</sub> no open load in off detected (Reset State)<br>1 <sub>B</sub> open load in off detected        |

| CH4_OC | 9    | r    | Over Current Diagnosis Bit of Channel 4:<br>0 <sub>B</sub> no over current detected (Reset State)<br>1 <sub>B</sub> over current detected             |

| Field   | Bits | Туре | Description                                                                                                                                                 |

|---------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CH5_OL  | 10   | r    | Open Load Diagnosis Bit of Channel 5:<br>0 <sub>B</sub> no open load in off detected (Reset State)<br>1 <sub>B</sub> open load in off detected              |

| CH5_OC  | 11   | r    | Over Current Diagnosis Bit of Channel 5:<br>0 <sub>B</sub> no over current detected (Reset State)<br>1 <sub>B</sub> over current detected                   |

| CH45_OT | 12   | r    | Over Temperature Diagnosis Bit of Channel 4 and 5:<br>0 <sub>B</sub> no over temperature detected (Reset State)<br>1 <sub>B</sub> over temperature detected |

### Stat Register Status Register (Identifier x10x xxxx xxxx xxxx<sub>B</sub>)Reset Value: 0<sub>H</sub>

| 15  | 14  | 13  | 12     | 11    | 10 | 9 | 8 | 7 | 6 | 5 | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|--------|-------|----|---|---|---|---|---|-----|-----|-----|-----|-----|

| R/W | AD1 | AD0 | WD_DIS | WD_TO |    |   |   |   |   |   | ST5 | ST4 | ST3 | ST2 | ST1 |

|     |     |     | r      | r     |    |   |   |   |   |   | r   | r   | r   | r   | r   |

| Field          | Bits | Туре | Description                                              |  |  |  |  |

|----------------|------|------|----------------------------------------------------------|--|--|--|--|

| ST1            | 0    | r    | Status Bit Channel 1:                                    |  |  |  |  |

|                |      |      | 0 <sub>B</sub> Channel 1 is switched off (Reset State)   |  |  |  |  |

|                |      |      | 1 <sub>B</sub> Channel 1 is switched on                  |  |  |  |  |

| ST2            | 1    | r    | Status Bit Channel 2:                                    |  |  |  |  |

|                |      |      | 0 <sub>B</sub> Channel 2 is switched off (Reset State)   |  |  |  |  |

|                |      |      | 1 <sub>B</sub> Channel 2 is switched on                  |  |  |  |  |

| ST3            | 2    | r    | Status Bit Channel 3:                                    |  |  |  |  |

|                |      |      | 0 <sub>B</sub> Channel 3 is switched off (Reset State)   |  |  |  |  |

|                |      |      | 1 <sub>B</sub> Channel 3 is switched on                  |  |  |  |  |

| <b>ST4</b> 3   |      | r    | Status Bit Channel 4:                                    |  |  |  |  |

|                |      |      | 0 <sub>B</sub> Channel 4 is switched off (Reset State)   |  |  |  |  |

|                |      |      | 1 <sub>B</sub> Channel 4 is switched on                  |  |  |  |  |

| <b>ST5</b> 4 r |      | r    | Status Bit Channel 5:                                    |  |  |  |  |

|                |      |      | 0 <sub>B</sub> Channel 5 is switched off (Reset State)   |  |  |  |  |

|                |      |      | 1 <sub>B</sub> Channel 5 is switched on                  |  |  |  |  |

| WD_TO          | 11   | r    | Watchdog Time Out Bit:                                   |  |  |  |  |

|                |      |      | 0 <sub>B</sub> no watchdog time out                      |  |  |  |  |

|                |      |      | 1 <sub>B</sub> watchdog time out occurred                |  |  |  |  |

| WD_DIS         | 12   | r    | Watchdog Status Bit:                                     |  |  |  |  |

|                |      |      | $0_{\rm B}$ Watchdog enabled (V <sub>WD DIS</sub> = 0V)  |  |  |  |  |

|                |      |      | $1_{\rm B}$ Watchdog disabled (V <sub>WD DIS</sub> = 5V) |  |  |  |  |

### 8.2.2 Set and Reset of Diagnosis Register Bits

Set of the over current diagnosis bits of channels 1, 3, 4 and 5:

The over current diagnosis bits of channels 1, 3, 4 and 5 are set asynchronously of the internal clock with the output signal of the detection circuit (details see **Chapter 6.1**).

Reset of the over current diagnosis bits of channels 1 and 3:

- Diagnosis register was read out:

- input pin INx remains high: no reset of the over current diagnosis bit, the channel remains switched off

- input pin INx transition from high to low: the over current diagnosis bit is reset, the channel could be switched on again

- Diagnosis register was not read out

- channel remains switched off and no reset of the over current diagnosis bit is done

- input pin INx is low: with the next read access of the diagnosis register the diagnosis bits are reset

Reset of the over current diagnosis bits of channels 4 and 5:

- Diagnosis register was not read out

- channel remains switched off and no reset of the over current diagnosis bit is done

- Diagnosis register was read out:

- <u>SPI command register write command is not sent</u>: **no reset** of the over current diagnosis bit, the channel remains switched off

- <u>SPI command register write command is sent</u>: the over current diagnosis bit is **reset**, the channel will be switched according the status of the control bit

### Set and Reset of the over current diagnosis bit of channel 2:

The over current diagnosis register bit for channel 2 is set asynchronously of the internal clock with the output signal of the detection circuit. With this signal the output is switched off and the counter for the off time  $t_{oc,off}$  of the repetitive switching cycle starts. After  $t_{oc,off}$  the channel will be switched on again. With an remaining over current condition the channel will be switched on repetitively. This internal overcurrent status of the channel is latched internally. The internal over current status is reset in two situations.

- over current condition exists no longer: the internal over current status is reset after the time t<sub>oc.St</sub>

- <u>over current condition remains and the channel is switched off</u>: the internal over current status is reset after the time t<sub>oc,off</sub>

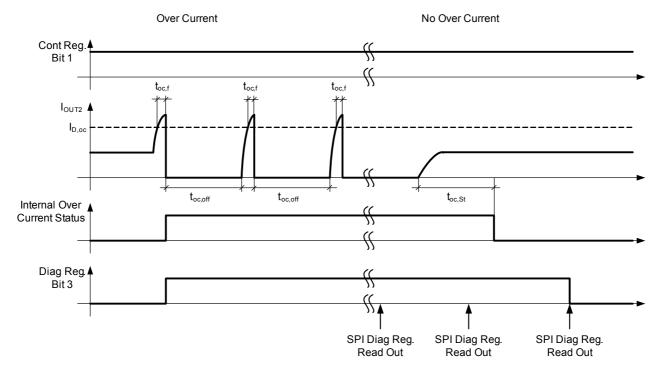

The reset of the over current diagnosis register bit for channel 2 is related to the internal over current status. In Figure 14 and Figure 15 the behavior of the diagnosis with temporary and permanent over current condition is drawn.

#### Figure 14 Behavior of diagnosis with temporary over current condition at channel 2

Permanent Over Current

### Figure 15 Behavior if diagnosis with permanent over current condition at channel 2

Reset of the over temperature diagnosis bits:

The over temperature diagnosis bits will be reset with read access of the diagnosis register if no over temperature condition is detected.

Reset of the open load in off diagnosis bits:

The open load in off diagnosis bits will be reset with read access of the diagnosis register if no open load condition is detected.

### 8.3 Electrical Characteristics SPI

### Table 8 Electrical Characteristics: SPI

$V_s$ =13.5V,  $T_j$ = -40°C to +150°C: All voltages with respect to ground. Positive current flowing into pin (unless otherwise specified).

| Parameter                                | Symbol                 | Values       |      |          | Unit     | Note /                                  | Number |

|------------------------------------------|------------------------|--------------|------|----------|----------|-----------------------------------------|--------|

|                                          |                        | Min.         | Тур. | Max.     | -        | <b>Test Condition</b>                   |        |

| Input Characteristics (CSN,              | SCLK, SI):             |              | 1    |          | <b>!</b> | -                                       |        |

| Low Level Input Voltage                  | $V_{x,L}$              | -            | -    | 1        | V        |                                         | 8.1.1  |

| High Level Input Voltage                 | V <sub>x,H</sub>       | 2            | -    | _        | V        |                                         | 8.1.2  |

| Hysteresis                               | V <sub>x,Hys</sub>     | 50           |      | 250      | mV       |                                         |        |

| Pull Up Current CSN                      | I <sub>x,pu</sub>      | -25          | -50  | -100     | μA       | at V <sub>IN</sub> = 0V                 | 8.1.3  |

| Pull Up Current CSN                      | I <sub>x.pu</sub>      | -25          | -    | -        | μA       | at $V_{\rm IN}$ = $V_{\rm V5DD}$ - 0.6V | 8.1.4  |

| Pull Down Current SCLK, SI               | I <sub>x,pu</sub>      | 20           | 50   | 100      | μA       | at $V_{IN} = V_{V5DD}$                  | 8.1.5  |

| Pull Down Current SCLK, SI               | I <sub>x.pu</sub>      | 2.4          | -    | -        | μA       | at V <sub>IN</sub> = 0.6V               | 8.1.6  |

| Output Characteristics (SO)              | ):                     | I            | 1    | <b>I</b> |          |                                         | 1      |

| Low Level Output Voltage                 | $V_{\rm So,L}$         | -            | -    | 0.4      | V        | <i>I</i> <sub>x</sub> = 100μA           | 8.2.1  |

| High Level Output Voltage                | V <sub>SO,H</sub>      | V5DD-<br>0.4 | -    | -        | V        | <i>I</i> <sub>x</sub> = -100μA          | 8.2.2  |

| Output High Impedance<br>Leakage Current | $I_{\rm SO,TRI}$       | -3           | -    | 3        | μA       | 0V < V <sub>SO</sub> < 5V               | 8.2.3  |

| Timings:                                 |                        |              |      |          |          |                                         |        |

| Lead Time                                | <i>t</i> <sub>1</sub>  | 210          | -    | -        | ns       | CSN falling to<br>SCLK rising           | 8.3.1  |

| Lag Time                                 | <i>t</i> <sub>2</sub>  | 75           | -    | -        | ns       | SCLK falling to<br>CSN rising           | 8.3.2  |

| CSN High Time                            | t <sub>3</sub>         | 550          | -    | -        | ns       | CSN rising to<br>CSN falling            | 8.3.3  |

| Period of SCLK                           | $t_4$                  | 200          | -    | _        | ns       |                                         | 8.3.4  |

| SCLK to CSN Set Up Time                  | <i>t</i> <sub>5</sub>  | 10           | -    | -        | ns       | SCLK falling to<br>CSN falling          | 8.3.5  |

| SCLK Low Time                            | <i>t</i> <sub>7</sub>  | 60           | -    | _        | ns       |                                         | 8.3.6  |

| CSN to SCLK Hold Time                    | t <sub>8</sub>         | 15           | -    | -        | ns       | CSN rising to<br>SCLK rising            | 8.3.7  |

| SI Set Up Time                           | t <sub>9</sub>         | 30           | -    | -        | ns       | SI set up time to SCLK falling          | 8.3.8  |

| SI Hold Up Time                          | <i>t</i> <sub>10</sub> | 30           | -    | -        | ns       | SI holdup time<br>after SCLK falling    | 8.3.9  |

| SO Enable Time                           | <i>t</i> <sub>11</sub> | -            | -    | 165      | ns       | CSN falling to SO active                | 8.3.10 |

| SO Valid Time                            | <i>t</i> <sub>12</sub> | -            | -    | 120      | ns       | SO data valid<br>after SCLK rising      | 8.3.11 |

### Table 8 Electrical Characteristics: SPI (cont'd)

$V_{s}$ =13.5V,  $T_{j}$ = -40°C to +150°C: All voltages with respect to ground. Positive current flowing into pin (unless otherwise specified).

| Parameter                                 | Symbol               | Values |      |      | Unit   | Note /                                   | Number |

|-------------------------------------------|----------------------|--------|------|------|--------|------------------------------------------|--------|

|                                           |                      | Min.   | Тур. | Max. |        | <b>Test Condition</b>                    |        |

| SO Disable Time                           | t <sub>13</sub>      | -      | -    | 165  | ns     | SO high<br>impedance after<br>CSN rising | 8.3.12 |

| Number of Clock Pulses while<br>CSN = low |                      | 16     | -    | 16   | pulses |                                          | 8.3.13 |

| SO Rise Time                              | t <sub>SO_rise</sub> | -      | -    | 75   | ns     | 20% to 80%,<br>C <sub>load</sub> =1.6pF  | 8.3.14 |

| SO Fall Time                              | t <sub>SO_fall</sub> | -      | -    | 75   | ns     | 80% to 20%<br>C <sub>load</sub> =1.6pF   | 8.3.15 |

### 9 K-Line

### 9.1 K-Line

The K-Line module is a serial link bus interface device designed to provide bi-directional half-duplex communication interfacing. It is designed to interface vehicles via the special ISO K-Line and meets the ISO standard 9141. The device's K-Line bus driver's output is protected against bus shorts.

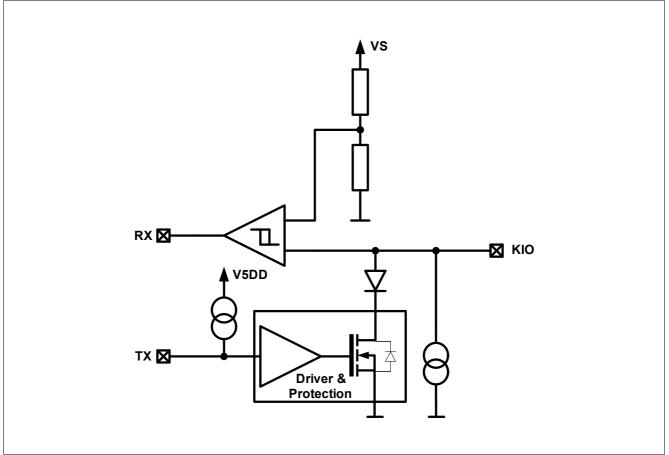

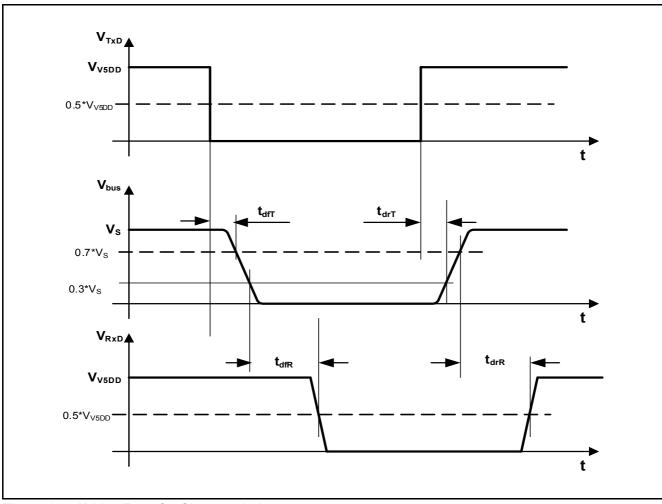

Figure 17 K-Line Block Diagram

### 9.2 Electrical Characteristics K-Line

### Table 9 Electrical Characteristics: K-Line

$V_s$ =13.5V,  $T_j$ = -40°C to +150°C: All voltages with respect to ground. Positive current flowing into pin (unless otherwise specified).

| Parameter                                                        | Symbol                | Values               |      |                            | Unit | Note /                                           | Number |

|------------------------------------------------------------------|-----------------------|----------------------|------|----------------------------|------|--------------------------------------------------|--------|

|                                                                  |                       | Min.                 | Тур. | Max.                       |      | Test Condition                                   |        |

| Output RX                                                        |                       | <del> </del>         | ł    |                            | I.   | -                                                | -      |

| Low Level Output Voltage                                         | $V_{RX,L}$            | -                    | -    | 0,4                        | V    | <i>I</i> <sub>RX</sub> = 100μA                   | 9.1.1  |

| High Level Output Voltage                                        | V <sub>RX,H</sub>     | V5DD-<br>0.4         | -    | -                          | V    | <i>I</i> <sub>RX</sub> = -100μA                  | 9.1.2  |

| Input TX                                                         |                       |                      |      |                            |      |                                                  |        |

| Low Level Input Voltage                                          | $V_{TX,L}$            | _                    | _    | 1                          | V    |                                                  | 9.2.1  |

| High Level Input Voltage                                         | V <sub>TX,H</sub>     | 3.2                  | -    | -                          | V    |                                                  | 9.2.2  |

| Hysteresis                                                       | V <sub>TX,Hys</sub>   | 280                  | 500  | 700                        | mV   |                                                  | 9.2.3  |

| Pull Up Current                                                  | I <sub>PU_L</sub>     | -70                  | -100 | -150                       | μA   | at V <sub>TX</sub> = 0V                          | 9.2.4  |

| Pull Up Current                                                  | <br>I <sub>PU_L</sub> | -30                  | -    | -                          | μA   | at V <sub>TX</sub> = V <sub>V5DD</sub> -<br>0.6V | 9.2.5  |

| K-Line Bus Driver Input/Out                                      | put <mark>KIO</mark>  | 1                    |      | 1                          |      |                                                  | I      |

| Low Level Output Voltage                                         | V <sub>KIO,O,L</sub>  | -                    | -    | 1.4                        | V    | TX = low,<br>R <sub>KIO</sub> =480Ω              | 9.3.1  |