# PSoC<sup>®</sup> 4: PSoC 4000 Family Datasheet

Programmable System-on-Chip (PSoC<sup>®</sup>)

# **General Description**

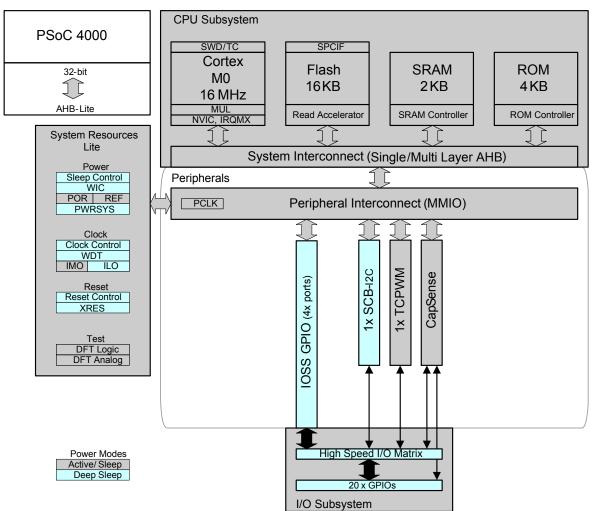

PSoC<sup>®</sup> 4 is a scalable and reconfigurable platform architecture for a family of programmable embedded system controllers with an ARM<sup>®</sup> Cortex <sup>™</sup>-M0 CPU. It combines programmable and reconfigurable analog and digital blocks with flexible automatic routing. The PSoC 4000 product family is the smallest member of the PSoC 4 platform architecture. It is a combination of a microcontroller with standard communication and timing peripherals, a capacitive touch-sensing system (CapSense) with best-in-class performance, and general-purpose analog. PSoC 4000 products will be fully upward compatible with members of the PSoC 4 platform for new applications and design needs.

# Features

# 32-bit MCU Subsystem

- 16-MHz ARM Cortex-M0 CPU

- Up to 16 KB of flash with Read Accelerator

- Up to 2 KB of SRAM

# **Programmable Analog**

- Two current DACs (IDACs) for general-purpose or capacitive sensing applications

- One low-power comparator with internal reference

# Low Power 1.71-V to 5.5-V operation

Deep Sleep mode with wake-up on interrupt and I<sup>2</sup>C address detect

# **Capacitive Sensing**

- Cypress CapSense Sigma-Delta (CSD) provides best-in-class signal-to-noise ratio (SNR) and water tolerance

- Cypress-supplied software component makes capacitive sensing design easy

- Automatic hardware tuning (SmartSense<sup>™</sup>) over a sensor range of 5 pF to 45 pF

# **Serial Communication**

Multi-master I<sup>2</sup>C block with the ability to do address matching during Deep Sleep and generate a wake-up on match

# **Timing and Pulse-Width Modulation**

- One 16-bit timer/counter/pulse-width modulator (TCPWM) block

- Center-aligned, Edge, and Pseudo-Random modes

- Comparator-based triggering of Kill signals for motor drive and other high-reliability digital logic applications

# Up to 20 Programmable GPIO Pins

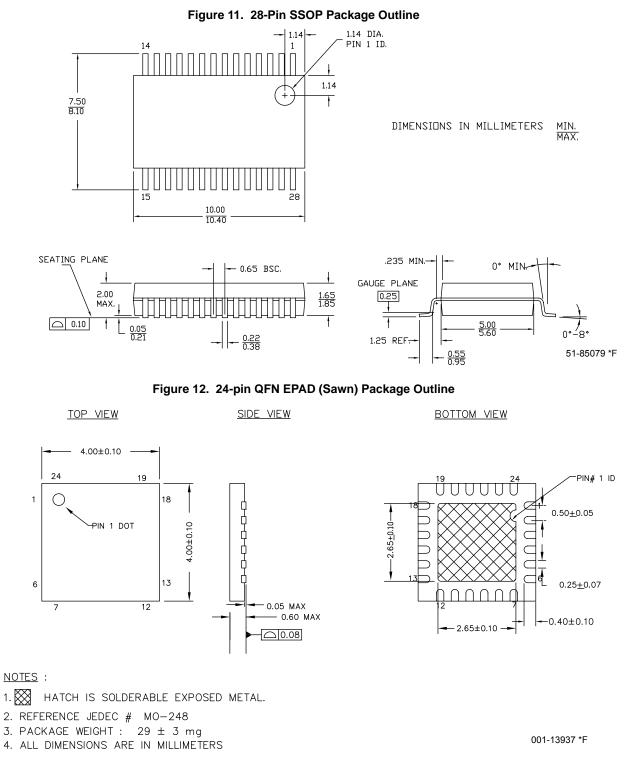

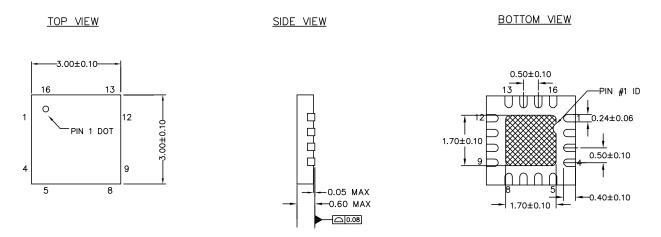

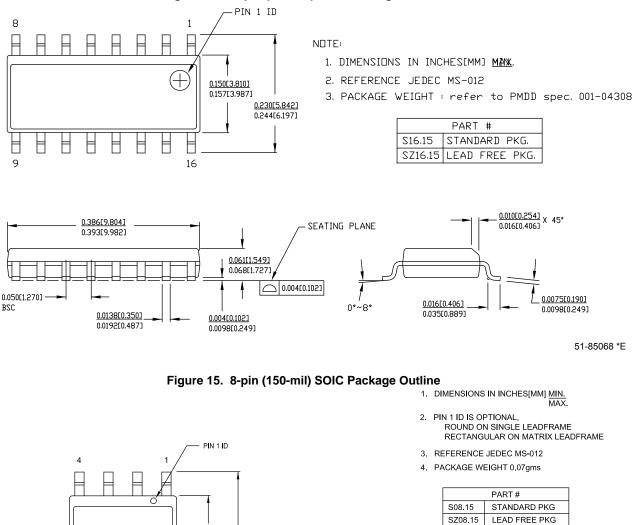

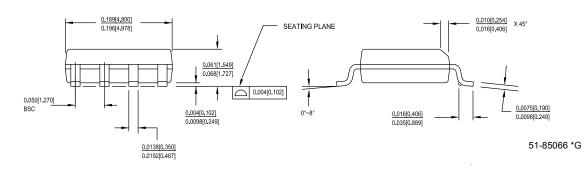

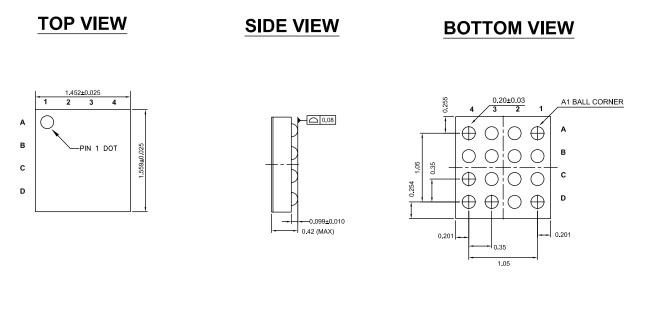

- 28-pin SSOP, 24-pin QFN, 16-pin SOIC, 16-pin QFN, 16 ball WLCSP, and 8-pin SOIC packages

- GPIO pins on Ports 0, 1, and 2 can be CapSense or have other functions

- Drive modes, strengths, and slew rates are programmable

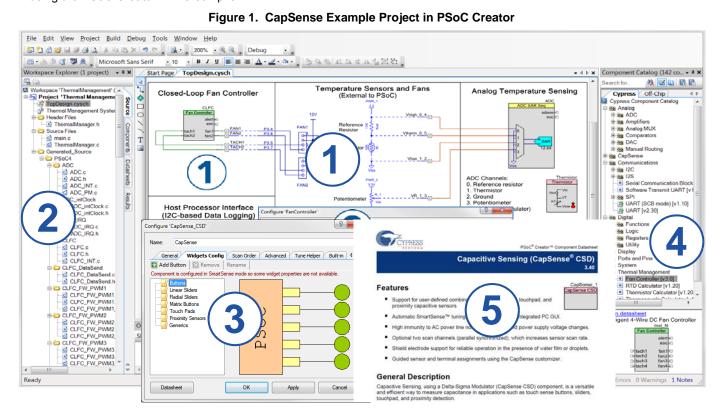

# **PSoC Creator Design Environment**

- Integrated Development Environment (IDE) provides schematic design entry and build (with analog and digital automatic routing)

- Applications Programming Interface (API) component for all fixed-function and programmable peripherals

# Industry-Standard Tool Compatibility

■ After schematic entry, development can be done with ARM-based industry-standard development tools

198 Champion Court

San Jose, CA 95134-1709

408-943-2600

Revised May 26, 2015

# **More Information**

Cypress provides a wealth of data at www.cypress.com to help you to select the right PSoC device for your design, and to help you to quickly and effectively integrate the device into your design. For a comprehensive list of resources, see the knowledge base article KBA86521, How to Design with PSoC 3, PSoC 4, and PSoC 5LP. Following is an abbreviated list for PSoC 4:

- Overview: PSoC Portfolio, PSoC Roadmap

- Product Selectors: PSoC 1, PSoC 3, PSoC 4, PSoC 5LP In addition, PSoC Creator includes a device selection tool.

- Application notes: Cypress offers a large number of PSoC application notes covering a broad range of topics, from basic to advanced level. Recommended application notes for getting started with PSoC 4 are:

- □ AN79953: Getting Started With PSoC 4

- □ AN88619: PSoC 4 Hardware Design Considerations

- □ AN86439: Using PSoC 4 GPIO Pins

- AN57821: Mixed Signal Circuit Board Layout

- □ AN81623: Digital Design Best Practices

- AN73854: Introduction To Bootloaders

- AN89610: ARM Cortex Code Optimization

- Technical Reference Manual (TRM) is in two documents:

- Architecture TRM details each PSoC 4 functional block.

- Registers TRM describes each of the PSoC 4 registers.

- Development Kits:

- □ CY8CKIT-040, PSoC 4000 Pioneer Kit, is an easy-to-use and inexpensive development platform with debugging capability. This kit includes connectors for Arduino<sup>™</sup> compatible shields and Digilent<sup>®</sup> Pmod<sup>™</sup> daughter cards.

- The MiniProg3 device provides an interface for flash programming and debug.

# **PSoC Creator**

PSoC Creator is a free Windows-based Integrated Design Environment (IDE). It enables concurrent hardware and firmware design of PSoC 3, PSoC 4, and PSoC 5LP based systems. Create designs using classic, familiar schematic capture supported by over 100 pre-verified, production-ready PSoC Components; see the list of component datasheets. With PSoC Creator, you can:

- 1. Drag and drop component icons to build your hardware system design in the main design workspace

- 3. Configure components using the configuration tools

- 4. Explore the library of 100+ components

- Codesign your application firmware with the PSoC hardware, using the PSoC Creator IDE C compiler

Review component datasheets

# Contents

| 5<br>5<br>6<br>6                     |

|--------------------------------------|

| 6<br>6                               |

| 6                                    |

|                                      |

|                                      |

| 0                                    |

| 6                                    |

| 7                                    |

| 12                                   |

| 12                                   |

| 12                                   |

| 13                                   |

| 13                                   |

| 13                                   |

| 13                                   |

| 14                                   |

| 14                                   |

| 14                                   |

| 17                                   |

| 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 |

Figure 2. Block Diagram

PSoC 4000 devices include extensive support for programming, testing, debugging, and tracing both hardware and firmware.

The ARM Serial-Wire Debug (SWD) interface supports all programming and debug features of the device.

Complete debug-on-chip functionality enables full-device debugging in the final system using the standard production device. It does not require special interfaces, debugging pods, simulators, or emulators. Only the standard programming connections are required to fully support debug.

The PSoC Creator IDE provides fully integrated programming and debug support for the PSoC 4000 devices. The SWD interface is fully compatible with industry-standard third-party tools. The PSoC 4000 family provides a level of security not possible with multi-chip application solutions or with microcontrollers. It has the following advantages:

- Allows disabling of debug features

- Robust flash protection

- Allows customer-proprietary functionality to be implemented in on-chip programmable blocks

The debug circuits are enabled by default and can only be disabled in firmware. If they are not enabled, the only way to re-enable them is to erase the entire device, clear flash protection, and reprogram the device with new firmware that enables debugging.

Additionally, all device interfaces can be permanently disabled (device security) for applications concerned about phishing attacks due to a maliciously reprogrammed device or attempts to defeat security by starting and interrupting flash programming sequences. All programming, debug, and test interfaces are disabled when maximum device security is enabled. Therefore, PSoC 4000, with device security enabled, may not be returned for failure analysis. This is a trade-off the PSoC 4000 allows the customer to make.

# **Functional Definition**

# **CPU and Memory Subsystem**

# CPU

The Cortex-M0 CPU in the PSoC 4000 is part of the 32-bit MCU subsystem, which is optimized for low-power operation with extensive clock gating. Most instructions are 16 bits in length and the CPU executes a subset of the Thumb-2 instruction set. This enables fully compatible, binary, upward migration of the code to higher performance processors, such as the Cortex-M3 and M4. It includes a nested vectored interrupt controller (NVIC) block with eight interrupt inputs and also includes a Wakeup Interrupt Controller (WIC). The WIC can wake the processor from the Deep Sleep mode, allowing power to be switched off to the main processor when the chip is in the Deep Sleep mode. The CPU subsystem also includes a 24-bit timer called SYSTICK, which can generate an interrupt.

The CPU also includes a debug interface, the serial wire debug (SWD) interface, which is a 2-wire form of JTAG. The debug configuration used for PSoC 4000 has four breakpoint (address) comparators and two watchpoint (data) comparators.

# Flash

The PSoC 4000 device has a flash module with a flash accelerator, tightly coupled to the CPU to improve average access times from the flash block. The low-power flash block is designed to deliver zero wait-state (WS) access time at 16 MHz.

SRAM

Two KB of SRAM are provided with zero wait-state access at 16 MHz.

# SROM

A supervisory ROM that contains boot and configuration routines is provided.

# System Resources

### Power System

The power system is described in detail in the section on Power on page 12. It provides an assurance that voltage levels are as required for each respective mode and either delays mode entry (for example, on power-on reset (POR)) until voltage levels are as required for proper functionality, or generates resets (for example, on brown-out detection). The PSoC 4000 operates with a single external supply over the range of either 1.8 V  $\pm$ 5% (externally regulated) or 1.8 to 5.5 V (internally regulated) and has three different power modes, transitions between which are managed by the power system. The PSoC 4000 provides Active, Sleep, and Deep Sleep low-power modes.

All subsystems are operational in Active mode. The CPU subsystem (CPU, flash, and SRAM) is clock-gated off in Sleep mode, while all peripherals and interrupts are active with instantaneous wake-up on a wake-up event. In Deep Sleep mode, the high-speed clock and associated circuitry is switched off; wake-up from this mode takes 35  $\mu$ S.

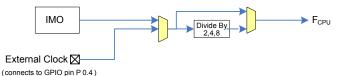

#### Clock System

The PSoC 4000 clock system is responsible for providing clocks to all subsystems that require clocks and for switching between different clock sources without glitching. In addition, the clock system ensures that there are no metastable conditions.

The clock system for the PSoC 4000 consists of the internal main oscillator (IMO) and the internal low-frequency oscillator (ILO) and provision for an external clock.

# Figure 3. PSoC 4000 MCU Clocking Architecture

The  $F_{CPU}$  signal can be divided down to generate synchronous clocks for the analog and digital peripherals. There are four clock dividers for the PSoC 4000, each with 16-bit divide capability The 16-bit capability allows flexible generation of fine-grained frequency values and is fully supported in PSoC Creator.

### IMO Clock Source

The IMO is the primary source of internal clocking in the PSoC 4000. It is trimmed during testing to achieve the specified accuracy. The IMO default frequency is 24 MHz and it can be adjusted from 24 to 48 MHz in steps of 4 MHz. The IMO tolerance with Cypress-provided calibration settings is  $\pm 2\%$  (24 and 32 MHz).

### ILO Clock Source

The ILO is a very low power, 40-kHz oscillator, which is primarily used to generate clocks for the watchdog timer (WDT) and peripheral operation in Deep Sleep mode. ILO-driven counters can be calibrated to the IMO to improve accuracy.

### Watchdog Timer

A watchdog timer is implemented in the clock block running from the ILO; this allows watchdog operation during Deep Sleep and generates a watchdog reset if not serviced before the set timeout occurs. The watchdog reset is recorded in a Reset Cause register, which is firmware readable.

### Reset

The PSoC 4000 can be reset from a variety of sources including a software reset. Reset events are asynchronous and guarantee reversion to a known state. The reset cause is recorded in a register, which is sticky through reset and allows software to determine the cause of the reset. An XRES pin is reserved for external reset on the 24-pin package. An internal POR is provided on the 16-pin and 8-pin packages. The XRES pin has an internal pull-up resistor that is always enabled. Reset is Active Low.

### Voltage Reference

The PSoC 4000 reference system generates all internally required references. A 1.2-V voltage reference is provided for the comparator. The IDACs are based on a  $\pm 5\%$  reference.

# Analog Blocks

#### Low-power Comparators

The PSoC 4000 has a low-power comparator, which uses the built-in voltage reference. Any one of up to 16 pins can be used as a comparator input and the output of the comparator can be brought out to a pin. The selected comparator input is connected to the minus input of the comparator with the plus input always connected to the 1.2-V voltage reference. This comparator is also used for CapSense purposes and is not available during CapSense operation.

### Current DACs

The PSoC 4000 has two IDACs, which can drive any of up to 16 pins on the chip. These IDACs have programmable current ranges.

### Analog Multiplexed Buses

The PSoC 4000 has two concentric independent buses that go around the periphery of the chip. These buses (called amux buses) are connected to firmware-programmable analog switches that allow the chip's internal resources (IDACs, comparator) to connect to any pin on Ports 0, 1, and 2.

# **Fixed Function Digital**

### Timer/Counter/PWM (TCPWM) Block

The TCPWM block consists of a 16-bit counter with user-programmable period length. There is a capture register to record the count value at the time of an event (which may be an I/O event), a period register that is used to either stop or auto-reload the counter when its count is equal to the period register, and compare registers to generate compare value signals that are used as PWM duty cycle outputs. The block also provides true and complementary outputs with programmable offset between them to allow use as dead-band programmable complementary PWM outputs. It also has a Kill input to force outputs to a predetermined state; for example, this is used in motor drive systems when an over-current state is indicated and the PWM driving the FETs needs to be shut off immediately with no time for software intervention.

### Serial Communication Block (SCB)

The PSoC 4000 has a serial communication block, which implements a multi-master  $\mathsf{I}^2\mathsf{C}$  interface.

**I<sup>2</sup>C Mode**: The hardware I<sup>2</sup>C block implements a full multi-master and slave interface (it is capable of multi-master arbitration). This block is capable of operating at speeds of up to 400 kbps (Fast Mode) and has flexible buffering options to reduce interrupt overhead and latency for the CPU. It also supports EZI2C that creates a mailbox address range in the memory of the PSoC 4000 and effectively reduces I<sup>2</sup>C communication to reading from and writing to an array in memory. In addition, the block supports an 8-deep FIFO for receive and transmit which, by increasing the time given for the CPU to read data, greatly reduces the need for clock stretching caused by the CPU not having read data on time.

The I<sup>2</sup>C peripheral is compatible with the I<sup>2</sup>C Standard-mode and Fast-mode devices as defined in the NXP I<sup>2</sup>C-bus specification and user manual (UM10204). The I<sup>2</sup>C bus I/O is implemented with GPIO in open-drain modes.

The PSoC 4000 is not completely compliant with the  $I^2C$  spec in the following respect:

- GPIO cells are not overvoltage tolerant and, therefore, cannot be hot-swapped or powered up independently of the rest of the I<sup>2</sup>C system.

- Fast-mode minimum fall time is not met in Fast Strong mode; Slow Strong mode can help meet this spec depending on the Bus Load.

# GPIO

The PSoC 4000 has up to 20 GPIOs. The GPIO block implements the following:

- Eight drive modes:

- Analog input mode (input and output buffers disabled)

- Input only

- Weak pull-up with strong pull-down

- Strong pull-up with weak pull-down

- Open drain with strong pull-down

- Open drain with strong pull-up

- Strong pull-up with strong pull-down

Weak pull-up with weak pull-down

- Input threshold select (CMOS or LVTTL).

- Individual control of input and output buffer enabling/disabling in addition to the drive strength modes

- Selectable slew rates for dV/dt related noise control to improve EMI

The pins are organized in logical entities called ports, which are 8-bit in width (less for Ports 2 and 3). During power-on and reset, the blocks are forced to the disable state so as not to crowbar any inputs and/or cause excess turn-on current. A multiplexing network known as a high-speed I/O matrix is used to multiplex between various signals that may connect to an I/O pin.

Data output and pin state registers store, respectively, the values to be driven on the pins and the states of the pins themselves. Every I/O pin can generate an interrupt if so enabled and each I/O port has an interrupt request (IRQ) and interrupt service routine (ISR) vector associated with it (4 for PSoC 4000).

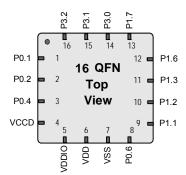

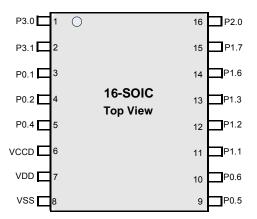

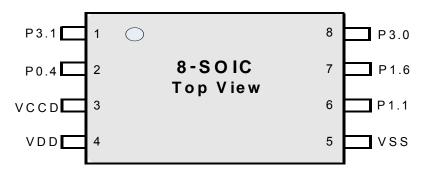

The 28-pin and 24-pin packages have 20 GPIOs. The 16-pin SOIC has 13 GPIOs. The 16-pin QFN and the 16-ball WLCSP have 12 GPIOs. The 8-pin SOIC has 5 GPIOs.

# **Special Function Peripherals**

### CapSense

CapSense is supported in the PSoC 4000 through a CSD block that can be connected to up to 16 pins through an analog mux bus via an analog switch (pins on Port 3 are not available for CapSense purposes). CapSense function can thus be provided on any available pin or group of pins in a system under software control. A PSoC Creator component is provided for the CapSense block to make it easy for the user.

Shield voltage can be driven on another mux bus to provide water-tolerance capability. Water tolerance is provided by driving the shield electrode in phase with the sense electrode to keep the shield capacitance from attenuating the sensed input. Proximity sensing can also be implemented.

The CapSense block has two IDACs, which can be used for general purposes if CapSense is not being used (both IDACs are available in that case) or if CapSense is used without water tolerance (one IDAC is available).

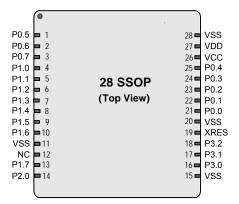

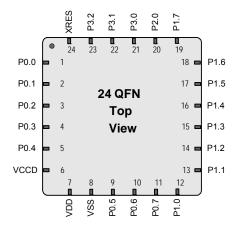

# Pinouts

All port pins support GPIO. Ports 0, 1, and 2 support CSD CapSense and analog multiplexed bus connections. TCPWM functions and Alternate Functions are multiplexed with port pins as follows for the five PSoC 4000 packages.

#### Table 1. Pin Descriptions

|     | 28-Pin SSOP                         |     | 24-Pin QFN                          |     | 16-Pin QFN                      |     | 16-Pin SOIC                     |     | 8-Pin SOIC                      |                                                         |                                                                      |

|-----|-------------------------------------|-----|-------------------------------------|-----|---------------------------------|-----|---------------------------------|-----|---------------------------------|---------------------------------------------------------|----------------------------------------------------------------------|

| Pin | Name                                | Pin | Name                                | Pin | Name                            | Pin | Name                            | Pin | Name                            | TCPWM Signals                                           | Alternate Functions                                                  |

| 20  | VSS                                 |     |                                     |     |                                 |     |                                 |     |                                 |                                                         |                                                                      |

| 21  | P0.0/TRIN0                          | 1   | P0.0/TRIN0                          |     |                                 |     |                                 |     |                                 | TRIN0: Trigger Input<br>0                               |                                                                      |

| 22  | P0.1/TRIN1/CMPO<br>_0               | 2   | P0.1/TRIN1/CMPO<br>_0               | 1   | P0.1/TRIN1/CMPO<br>_0           | 3   | P0.1/TRIN1/CMPO<br>_0           |     |                                 | TRIN1: Trigger Input<br>1                               | CMPO_0: Sense<br>Comp Out                                            |

| 23  | P0.2/TRIN2                          | 3   | P0.2/TRIN2                          | 2   | P0.2/TRIN2                      | 4   | P0.2/TRIN2                      |     |                                 | TRIN2: Trigger Input<br>2                               |                                                                      |

| 24  | P0.3/TRIN3                          | 4   | P0.3/TRIN3                          |     |                                 |     |                                 |     |                                 | TRIN3: Trigger Input<br>3                               |                                                                      |

| 25  | P0.4/TRIN4/CMPO<br>_0/EXT_CLK       | 5   | P0.4/TRIN4/CMPO<br>_0/EXT_CLK       | 3   | P0.4/TRIN4/CMPO<br>_0/EXT_CLK   | 5   | P0.4/TRIN4/CMPO<br>_0/EXT_CLK   | 2   | P0.4/TRIN4/CMPO<br>_0/EXT_CLK   | TRIN4: Trigger Input<br>4                               | CMPO_0: Sense<br>Comp Out, External<br>Clock, CMOD Cap               |

| 26  | VCC                                 | 6   | VCC                                 | 4   | VCC                             | 6   | VCC                             | 3   | VCC                             |                                                         |                                                                      |

| 27  | VDD                                 | 7   | VDD                                 | 6   | VDD                             | 7   | VDD                             | 4   | VDD                             |                                                         |                                                                      |

| 28  | VSS                                 | 8   | VSS                                 | 7   | VSS                             | 8   | VSS                             | 5   | VSS                             |                                                         |                                                                      |

| 1   | P0.5                                | 9   | P0.5                                | 5   | VDDIO                           | 9   | P0.5                            |     |                                 |                                                         |                                                                      |

| 2   | P0.6                                | 10  | P0.6                                | 8   | P0.6                            | 10  | P0.6                            |     |                                 |                                                         |                                                                      |

| 3   | P0.7                                | 11  | P0.7                                |     |                                 |     |                                 |     |                                 |                                                         |                                                                      |

| 4   | P1.0                                | 12  | P1.0                                |     |                                 |     |                                 |     |                                 |                                                         |                                                                      |

| 5   | P1.1/OUT0                           | 13  | P1.1/OUT0                           | 9   | P1.1/OUT0                       | 11  | P1.1/OUT0                       | 6   | P1.1/OUT0                       | OUT0: PWM OUT 0                                         |                                                                      |

| 6   | P1.2/SCL                            | 14  | P1.2/SCL                            | 10  | P1.2/SCL                        | 12  | P1.2/SCL                        |     |                                 |                                                         | I2C Clock                                                            |

| 7   | P1.3/SDA                            | 15  | P1.3/SDA                            | 11  | P1.3/SDA                        | 13  | P1.3/SDA                        |     |                                 |                                                         | I2C Data                                                             |

| 8   | P1.4/UND0                           | 16  | P1.4/UND0                           |     |                                 |     |                                 |     |                                 | UND0: Underflow<br>Out                                  |                                                                      |

| 9   | P1.5/OVF0                           | 17  | P1.5/OVF0                           |     |                                 |     |                                 |     |                                 | OVF0: Overflow Out                                      |                                                                      |

| 10  | P1.6/OVF0/UND0/n<br>OUT0<br>/CMPO_0 | 18  | P1.6/OVF0/UND0/n<br>OUT0<br>/CMPO_0 | 12  | P1.6/OVF0/UND0/n<br>OUT0/CMPO_0 | 14  | P1.6/OVF0/UND0/n<br>OUT0/CMPO_0 | 7   | P1.6/OVF0/UND0/n<br>OUT0/CMPO_0 | nOUT0:<br>Complement of<br>OUT0, UND0,<br>OVF0 as above | CMPO_0: Sense<br>Comp Out, Internal<br>Reset function <sup>[1]</sup> |

#### Note

1. Must not have load to ground during POR (should be an output).

| Table 1. | Pin Desc | riptions | (continued) |

|----------|----------|----------|-------------|

|----------|----------|----------|-------------|

|     | 28-Pin SSOP                    |     | 24-Pin QFN             |     | 16-Pin QFN             |     | 16-Pin SOIC            | 8-Pin SOIC |                      |                  |                         |

|-----|--------------------------------|-----|------------------------|-----|------------------------|-----|------------------------|------------|----------------------|------------------|-------------------------|

| Pin | Name                           | Pin | Name                   | Pin | Name                   | Pin | Name                   | Pin        | Name                 | TCPWM Signals    | Alternate Functions     |

| 11  | VSS                            |     |                        |     |                        |     |                        |            |                      |                  |                         |

| 12  | No Connect (NC) <sup>[2]</sup> |     |                        |     |                        |     |                        |            |                      |                  |                         |

| 13  | P1.7/MATCH/EXT_<br>CLK         | 19  | P1.7/MATCH/EXT_<br>CLK | 13  | P1.7/MATCH/EXT_<br>CLK | 15  | P1.7/MATCH/EXT_<br>CLK |            |                      | MATCH: Match Out | External Clock          |

| 14  | P2.0                           | 20  | P2.0                   |     |                        | 16  | P2.0                   |            |                      |                  |                         |

| 15  | VSS                            |     |                        |     |                        |     |                        |            |                      |                  |                         |

| 16  | P3.0/SDA/SWD_IO                | 21  | P3.0/SDA/SWD_IO        | 14  | P3.0/SDA/SWD_IO        | 1   | P3.0/SDA/SWD_IO        | 8          | P3.0/SDA/SWD_IO      |                  | I2C Data, SWD I/O       |

| 17  | P3.1/SCL/SWD_CL<br>K           | 22  | P3.1/SCL/SWD_CL<br>K   | 15  | P3.1/SCL/SWD_CL<br>K   | 2   | P3.1/SCL/SWD_CL<br>K   | 1          | P3.1/SCL/SWD_CL<br>K |                  | I2C Clock, SWD<br>Clock |

| 18  | P3.2                           | 23  | P3.2                   | 16  | P3.2                   |     |                        |            |                      | OUT0:PWM OUT 0   |                         |

| 19  | XRES                           | 24  | XRES                   |     |                        |     |                        |            |                      |                  | XRES: External<br>Reset |

#### Descriptions of the Pin functions are as follows:

**VDD**: Power supply for both analog and digital sections.

VDDIO: Where available, this pin provides a separate voltage domain (see the Power section for details).

VSS: Ground pin.

VCCD: Regulated digital supply (1.8 V ±5%).

Pins belonging to Ports 0, 1, and 2 can all be used as CSD sense or shield pins connected to AMUXBUS A or B. They can also be used as GPIO pins that can be driven by the firmware, in addition to their alternate functions listed in the Table 1.

Pins on Port 3 can be used as GPIO, in addition to their alternate functions listed above.

The following packages are provided: 28-pin SSOP, 24-pin QFN, 16-pin QFN, 16-pin SOIC, and 8-pin SOIC.

2. This pin is not to be used; it must be left floating.

# Figure 4. 28-Pin SSOP Pinout

## Figure 6. 16-Pin QFN Pinout

Figure 7. 16-Pin SOIC Pinout

# Table 2. 16-ball WLCSP Pin Descriptions and Diagram

| Pin | Name                            | TCPWM Signal                               | Alternate<br>Functions                                               | Pin Diagram |

|-----|---------------------------------|--------------------------------------------|----------------------------------------------------------------------|-------------|

| B4  | P3.2                            | OUT0:PWMOUT0                               | -                                                                    | Bottom View |

| C3  | P0.2/TRIN2                      | TRIN2:Trigger Input 2                      | -                                                                    | 4 3 2 1     |

| C4  | P0.4/TRIN4/CMPO_0/<br>EXT_CLK   | TRIN4: Trigger Input 4                     | CMPO_0: Sense<br>Comp Out, Ext.<br>Clock, CMOD Cap                   | A           |

| D4  | VCCD                            | -                                          | -                                                                    | В           |

| D3  | VDD                             | -                                          | -                                                                    |             |

| D2  | VSS                             | -                                          | -                                                                    |             |

| C2  | VDDIO                           | -                                          | _                                                                    |             |

| D1  | P0.6                            | -                                          | -                                                                    |             |

| C1  | P1.1/OUT0                       | OUT0:PWMOUT0                               | -                                                                    | Top View    |

| B1  | P1.2/SCL                        | -                                          | I <sup>2</sup> C Clock                                               |             |

| A1  | P1.3/SDA                        | _                                          | I <sup>2</sup> C Data                                                | 1 2 3 4     |

| A2  | P1.6/OVF0/UND0/nO<br>UT0/CMPO_0 | nOUT0:Complement<br>of OUT0, UND0,<br>OVF0 | CMPO_0: Sense<br>Comp Out, Internal<br>Reset function <sup>[3]</sup> | A PIN 1 DOT |

| B2  | P1.7/MATCH/<br>EXT_CLK          | MATCH: Match Out                           | External Clock                                                       | C           |

| A3  | P2.0                            | -                                          | -                                                                    |             |

| B3  | P3.0/SDA/SWD_IO                 | -                                          | I <sup>2</sup> C Data, SWD I/O                                       | D           |

| A4  | P3.1/SCL/SWD_CLK                | _                                          | I <sup>2</sup> C Clock, SWD<br>Clock                                 |             |

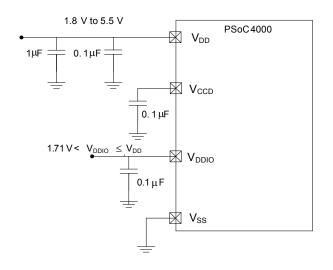

# Power

The following power system diagrams (Figure 9 and Figure 10) show the set of power supply pins as implemented for the PSoC 4000. The system has one regulator in Active mode for the digital circuitry. There is no analog regulator; the analog circuits run directly from the  $V_{DD}$  input. There is a separate regulator for the Deep Sleep mode. The supply voltage range is either 1.8 V ±5% (externally regulated) or 1.8 V to 5.5 V (unregulated externally; regulated internally) with all functions and circuits operating over that range.

The V<sub>DDIO</sub> pin, available in the 16-pin QFN package, provides a separate voltage domain for the following pins: P3.0, P3.1, and P3.2. P3.0 and P3.1 can be I<sup>2</sup>C pins and the chip can thus communicate with an I<sup>2</sup>C system, running at a different voltage (where V<sub>DDIO</sub>  $\leq$  V<sub>DD</sub>). For example, V<sub>DD</sub> can be 3.3 V and V<sub>DDIO</sub> can be 1.8 V.

The PSoC 4000 family allows two distinct modes of power supply operation: Unregulated External Supply and Regulated External Supply.

# **Unregulated External Supply**

In this mode, the PSoC 4000 is powered by an external power supply that can be anywhere in the range of 1.8 to 5.5 V. This range is also designed for battery-powered operation. For example, the chip can be powered from a battery system that starts at 3.5 V and works down to 1.8 V. In this mode, the internal regulator of the PSoC 4000 supplies the internal logic and the V<sub>CCD</sub> output of the PSoC 4000 must be bypassed to ground via an external capacitor (0.1  $\mu$ F; X5R ceramic or better).

Bypass capacitors must be used from V<sub>DD</sub> to ground. The typical practice for systems in this frequency range is to use a capacitor in the 1-µF range, in parallel with a smaller capacitor (0.1 µF, for example). Note that these are simply rules of thumb and that, for critical applications, the PCB layout, lead inductance, and the bypass capacitor parasitic should be simulated to design and obtain optimal bypassing.

An example of a bypass scheme follows (V\_{DDIO} is available on the 16-QFN package).

# Figure 9. 16-pin QFN Bypass Scheme Example - Unregulated External Supply

Power supply connections when  $1.8 \leq V_{\text{DD}} \leq ~5.5\,\text{V}$

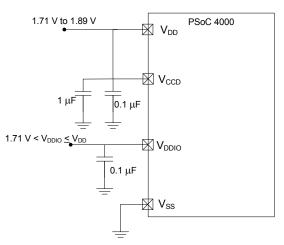

# **Regulated External Supply**

In this mode, the PSoC 4000 is powered by an external power supply that must be within the range of 1.71 to 1.89 V; note that this range needs to include the power supply ripple too. In this mode, the  $V_{DD}$  and  $V_{CCD}$  pins are shorted together and bypassed. The internal regulator should be disabled in the firmware. Note that in this mode VDD (VCCD) should never exceed 1.89 in any condition, including flash programming.

An example of a bypass scheme follows (V\_{DDIO} is available on the 16-QFN package).

# Figure 10. 16-pin QFN Bypass Scheme Example - Regulated External Supply

Power supply connections when  $1.71 \leq V_{DD} \leq 1.89 \; V$

# **Development Support**

The PSoC 4000 family has a rich set of documentation, development tools, and online resources to assist you during your development process. Visit www.cypress.com/go/psoc4 to find out more.

# Documentation

A suite of documentation supports the PSoC 4000 family to ensure that you can find answers to your questions quickly. This section contains a list of some of the key documents.

**Software User Guide**: A step-by-step guide for using PSoC Creator. The software user guide shows you how the PSoC Creator build process works in detail, how to use source control with PSoC Creator, and much more.

**Component Datasheets**: The flexibility of PSoC allows the creation of new peripherals (components) long after the device has gone into production. Component data sheets provide all of the information needed to select and use a particular component, including a functional description, API documentation, example code, and AC/DC specifications.

Application Notes: PSoC application notes discuss a particular application of PSoC in depth; examples include brushless DC motor control and on-chip filtering. Application notes often include example projects in addition to the application note document.

**Technical Reference Manual**: The Technical Reference Manual (TRM) contains all the technical detail you need to use a PSoC device, including a complete description of all PSoC registers. The TRM is available in the Documentation section at www.cypress.com/psoc4.

# Online

In addition to print documentation, the Cypress PSoC forums connect you with fellow PSoC users and experts in PSoC from around the world, 24 hours a day, 7 days a week.

# Tools

With industry standard cores, programming, and debugging interfaces, the PSoC 4000 family is part of a development tool ecosystem. Visit us at www.cypress.com/go/psoccreator for the latest information on the revolutionary, easy to use PSoC Creator IDE, supported third party compilers, programmers, debuggers, and development kits.

# **Electrical Specifications**

# **Absolute Maximum Ratings**

# Table 3. Absolute Maximum Ratings<sup>[4]</sup>

| Spec ID# | Parameter                   | Description                                                                                                       | Min  | Тур | Max                  | Units | Details/<br>Conditions      |

|----------|-----------------------------|-------------------------------------------------------------------------------------------------------------------|------|-----|----------------------|-------|-----------------------------|

| SID1     | V <sub>DD_ABS</sub>         | Digital supply relative to V <sub>SS</sub>                                                                        | -0.5 | -   | 6                    | V     |                             |

| SID2     | V <sub>CCD_ABS</sub>        | Direct digital core voltage input relative to $V_{SS}$                                                            | -0.5 | -   | 1.95                 | V     |                             |

| SID3     | V <sub>GPIO_ABS</sub>       | GPIO voltage                                                                                                      | -0.5 | -   | V <sub>DD</sub> +0.5 | V     |                             |

| SID4     | I <sub>GPIO_ABS</sub>       | Maximum current per GPIO                                                                                          | -25  | -   | 25                   | mA    |                             |

| SID5     | I <sub>GPIO_injection</sub> | GPIO injection current, Max for V <sub>IH</sub> > V <sub>DD</sub> , and Min for V <sub>IL</sub> < V <sub>SS</sub> | -0.5 | _   | 0.5                  | mA    | Current injected<br>per pin |

| BID44    | ESD_HBM                     | Electrostatic discharge human body model                                                                          | 2200 | -   | -                    | V     |                             |

| BID45    | ESD_CDM                     | Electrostatic discharge charged device model                                                                      | 500  | -   | -                    | V     |                             |

| BID46    | LU                          | Pin current for latch-up                                                                                          | -140 | _   | 140                  | mA    |                             |

# **Device Level Specifications**

All specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C and T<sub>J</sub>  $\leq$  100 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

# Table 4. DC Specifications

Typical values measured at V<sub>DD</sub> = 3.3 V and 25 °C.

| Spec ID#      | Parameter                                                      | Description                                         | Min  | Тур | Max             | Units | Details/<br>Conditions             |  |  |  |

|---------------|----------------------------------------------------------------|-----------------------------------------------------|------|-----|-----------------|-------|------------------------------------|--|--|--|

| SID53         | V <sub>DD</sub>                                                | Power supply input voltage                          | 1.8  | -   | 5.5             | V     | With regulator enabled             |  |  |  |

| SID255        | V <sub>DD</sub>                                                | Power supply input voltage ( $V_{CCD}$ = $V_{DD}$ ) | 1.71 | -   | 1.89            | V     | Internally unreg-<br>ulated supply |  |  |  |

| SID54         | V <sub>DDIO</sub>                                              | V <sub>DDIO</sub> domain supply                     | 1.71 | -   | V <sub>DD</sub> | V     |                                    |  |  |  |

| SID55         | C <sub>EFC</sub>                                               | External regulator voltage bypass                   | -    | 0.1 | -               | μF    | X5R ceramic or<br>better           |  |  |  |

| SID56         | C <sub>EXC</sub>                                               | Power supply bypass capacitor                       | _    | 1   | -               | μF    | X5R ceramic or<br>better           |  |  |  |

| Active Mode,  | V <sub>DD</sub> = 1.8 to 5.5                                   | V                                                   |      |     |                 |       |                                    |  |  |  |

| SID9          | I <sub>DD5</sub>                                               | Execute from flash; CPU at 6 MHz                    | -    | 2.0 | 2.85            | mA    |                                    |  |  |  |

| SID12         | I <sub>DD8</sub>                                               | Execute from flash; CPU at 12 MHz                   | -    | 3.2 | 3.75            | mA    |                                    |  |  |  |

| SID16         | I <sub>DD11</sub>                                              | Execute from flash; CPU at 16 MHz                   | -    | 4.0 | 4.5             | mA    |                                    |  |  |  |

| Sleep Mode, V | / <sub>DD</sub> = 1.71 to 5.5                                  | ν.                                                  |      |     |                 |       |                                    |  |  |  |

| SID25         | I <sub>DD20</sub>                                              | I <sup>2</sup> C wakeup, WDT on. 6 MHz              | -    | 1.1 | -               | mA    |                                    |  |  |  |

| SID25A        | I <sub>DD20A</sub>                                             | I <sup>2</sup> C wakeup, WDT on. 12 MHz             | _    | 1.4 | _               | mA    |                                    |  |  |  |

| Deep Sleep M  | Deep Sleep Mode, V <sub>DD</sub> = 1.8 to 3.6 V (Regulator on) |                                                     |      |     |                 |       |                                    |  |  |  |

| SID31         | I <sub>DD26</sub>                                              | I <sup>2</sup> C wakeup and WDT on                  | -    | 2.5 | 8.2             | μA    |                                    |  |  |  |

#### Note

<sup>4.</sup> Usage above the absolute maximum conditions listed in Table 1 may cause permanent damage to the device. Exposure to Absolute Maximum conditions for extended periods of time may affect device reliability. The Maximum Storage Temperature is 150 °C in compliance with JEDEC Standard JESD22-A103, High Temperature Storage Life. When used below Absolute Maximum conditions but above normal operating conditions, the device may not operate to specification.

# Table 4. DC Specifications (continued)

Typical values measured at V\_DD = 3.3 V and 25  $^\circ\text{C}.$

| Spec ID#                                                       | Parameter                               | Description                             | Min | Тур | Max | Units | Details/<br>Conditions |  |  |  |

|----------------------------------------------------------------|-----------------------------------------|-----------------------------------------|-----|-----|-----|-------|------------------------|--|--|--|

| Deep Sleep Mode, V <sub>DD</sub> = 3.6 to 5.5 V (Regulator on) |                                         |                                         |     |     |     |       |                        |  |  |  |

| SID34                                                          | I <sub>DD29</sub>                       | I <sup>2</sup> C wakeup and WDT on      | _   | 2.5 | 12  | μA    |                        |  |  |  |

| Deep Sleep M                                                   | ode, V <sub>DD</sub> = V <sub>CCI</sub> | ) = 1.71 to 1.89 V (Regulator bypassed) | )   |     |     |       |                        |  |  |  |

| SID37                                                          | I <sub>DD32</sub>                       | I <sup>2</sup> C wakeup and WDT on      | -   | 2.5 | 9.2 | μA    |                        |  |  |  |

| XRES Current                                                   | XRES Current                            |                                         |     |     |     |       |                        |  |  |  |

| SID307                                                         | I <sub>DD_XR</sub>                      | Supply current while XRES asserted      | _   | 2   | 5   | mA    |                        |  |  |  |

# Table 5. AC Specifications

| Spec ID#             | Parameter              | Description                 | Min | Тур | Max | Units | Details/<br>Conditions      |

|----------------------|------------------------|-----------------------------|-----|-----|-----|-------|-----------------------------|

| SID48                | F <sub>CPU</sub>       | CPU frequency               | DC  | -   | 16  | MHz   | $1.71 \leq V_{DD} \leq 5.5$ |

| SID49 <sup>[5]</sup> | T <sub>SLEEP</sub>     | Wakeup from Sleep mode      | -   | 0   | _   | μs    |                             |

| SID50 <sup>[5]</sup> | T <sub>DEEPSLEEP</sub> | Wakeup from Deep Sleep mode | -   | 35  | -   | μs    |                             |

GPIO

# Table 6. GPIO DC Specifications (referenced to $V_{DDIO}$ for 16-Pin QFN $V_{DDIO}$ pins)

| Spec ID# | Parameter                      | Description                             | Min                  | Тур | Max                 | Units | Details/<br>Conditions                             |

|----------|--------------------------------|-----------------------------------------|----------------------|-----|---------------------|-------|----------------------------------------------------|

| SID57    | V <sub>IH</sub> <sup>[6]</sup> | Input voltage high threshold            | $0.7 \times V_{DD}$  | -   | -                   | V     | CMOS Input                                         |

| SID58    | V <sub>IL</sub>                | Input voltage low threshold             | -                    | -   | $0.3 \times V_{DD}$ | V     | CMOS Input                                         |

| SID241   | V <sub>IH</sub> <sup>[6]</sup> | LVTTL input, V <sub>DD</sub> < 2.7 V    | 0.7× V <sub>DD</sub> | -   | -                   | V     |                                                    |

| SID242   | V <sub>IL</sub>                | LVTTL input, V <sub>DD</sub> < 2.7 V    | -                    | -   | $0.3 \times V_{DD}$ | V     |                                                    |

| SID243   | V <sub>IH</sub> <sup>[6]</sup> | LVTTL input, $V_{DD} \ge 2.7 \text{ V}$ | 2.0                  | -   | -                   | V     |                                                    |

| SID244   | V <sub>IL</sub>                | LVTTL input, $V_{DD} \ge 2.7 \text{ V}$ | -                    | -   | 0.8                 | V     |                                                    |

| SID59    | V <sub>OH</sub>                | Output voltage high level               | V <sub>DD</sub> –0.6 | -   | -                   | V     | I <sub>OH</sub> = 4 mA at<br>3 V V <sub>DD</sub>   |

| SID60    | V <sub>OH</sub>                | Output voltage high level               | V <sub>DD</sub> -0.5 | -   | -                   | V     | I <sub>OH</sub> = 1 mA at<br>1.8 V V <sub>DD</sub> |

| SID61    | V <sub>OL</sub>                | Output voltage low level                | -                    | -   | 0.6                 | V     | I <sub>OL</sub> = 4 mA at<br>1.8 V V <sub>DD</sub> |

| SID62    | V <sub>OL</sub>                | Output voltage low level                | -                    | -   | 0.6                 | V     | I <sub>OL</sub> = 10 mA at<br>3 V V <sub>DD</sub>  |

| SID62A   | V <sub>OL</sub>                | Output voltage low level                | -                    | -   | 0.4                 | V     | I <sub>OL</sub> = 3 mA at 3 V<br>V <sub>DD</sub>   |

| SID63    | R <sub>PULLUP</sub>            | Pull-up resistor                        | 3.5                  | 5.6 | 8.5                 | kΩ    |                                                    |

| SID64    | R <sub>PULLDOWN</sub>          | Pull-down resistor                      | 3.5                  | 5.6 | 8.5                 | kΩ    |                                                    |

| SID65    | IIL                            | Input leakage current (absolute value)  | -                    | _   | 2                   | nA    | 25 °C, V <sub>DD</sub> =<br>3.0 V                  |

| SID66    | C <sub>IN</sub>                | Input capacitance                       | -                    | 3   | 7                   | pF    |                                                    |

#### Notes

Guaranteed by characterization.

V<sub>IH</sub> must not exceed V<sub>DD</sub> + 0.2 V.

| Spec ID#              | Parameter               | Description                                         | Min                       | Тур | Max | Units | Details/<br>Conditions     |

|-----------------------|-------------------------|-----------------------------------------------------|---------------------------|-----|-----|-------|----------------------------|

| SID67 <sup>[7]</sup>  | V <sub>HYSTTL</sub>     | Input hysteresis LVTTL                              | 15                        | 40  | _   | mV    | $V_{DD} \ge 2.7 \text{ V}$ |

| SID68 <sup>[7]</sup>  | V <sub>HYSCMOS</sub>    | Input hysteresis CMOS                               | 0.05 ×<br>V <sub>DD</sub> | -   | _   | mV    | V <sub>DD</sub> < 4.5 V    |

| SID68A <sup>[7]</sup> | V <sub>HYSCMOS5V5</sub> | Input hysteresis CMOS                               | 200                       | -   | _   | mV    | V <sub>DD</sub> > 4.5 V    |

| SID69 <sup>[7]</sup>  | IDIODE                  | Current through protection diode to $V_{DD}/V_{SS}$ | -                         | -   | 100 | μA    |                            |

| SID69A <sup>[7]</sup> | I <sub>TOT_GPIO</sub>   | Maximum total source or sink chip current           | _                         | -   | 85  | mA    |                            |

# Table 6. GPIO DC Specifications (referenced to V<sub>DDIO</sub> for 16-Pin QFN V<sub>DDIO</sub> pins) (continued)

# Table 7. GPIO AC Specifications

(Guaranteed by Characterization)

| Spec ID# | Parameter            | Description                                                                           | Min | Тур | Max | Units | Details/<br>Conditions                     |

|----------|----------------------|---------------------------------------------------------------------------------------|-----|-----|-----|-------|--------------------------------------------|

| SID70    | T <sub>RISEF</sub>   | Rise time in fast strong mode                                                         | 2   | -   | 12  | ns    | 3.3 V V <sub>DD</sub> ,<br>Cload = 25 pF   |

| SID71    | T <sub>FALLF</sub>   | Fall time in fast strong mode                                                         | 2   | -   | 12  | ns    | 3.3 V V <sub>DD</sub> ,<br>Cload = 25 pF   |

| SID72    | T <sub>RISES</sub>   | Rise time in slow strong mode                                                         | 10  | -   | 60  | -     | 3.3 V V <sub>DD</sub> ,<br>Cload = 25 pF   |

| SID73    | T <sub>FALLS</sub>   | Fall time in slow strong mode                                                         | 10  | _   | 60  | -     | 3.3 V V <sub>DD</sub> ,<br>Cload = 25 pF   |

| SID74    | F <sub>GPIOUT1</sub> | GPIO $F_{OUT}$ ; 3.3 V $\leq$ V <sub>DD</sub> $\leq$ 5.5 V. Fast strong mode.         | -   | -   | 16  | MHz   | 90/10%, 25 pF<br>load, 60/40 duty<br>cycle |

| SID75    | F <sub>GPIOUT2</sub> | GPIO $F_{OUT}$ ; 1.71 V $\leq$ V <sub>DD</sub> $\leq$ 3.3 V.<br>Fast strong mode.     | -   | -   | 16  | MHz   | 90/10%, 25 pF<br>load, 60/40 duty<br>cycle |

| SID76    | F <sub>GPIOUT3</sub> | GPIO $F_{OUT}$ ; 3.3 V $\leq$ V <sub>DD</sub> $\leq$ 5.5 V. Slow strong mode.         | -   | -   | 7   | MHz   | 90/10%, 25 pF<br>load, 60/40 duty<br>cycle |

| SID245   | F <sub>GPIOUT4</sub> | GPIO F <sub>OUT</sub> ; 1.71 V $\leq$ V <sub>DD</sub> $\leq$ 3.3 V. Slow strong mode. | -   | -   | 3.5 | MHz   | 90/10%, 25 pF<br>load, 60/40 duty<br>cycle |

| SID246   | F <sub>GPIOIN</sub>  | GPIO input operating frequency; 1.71 V $\leq$ V <sub>DD</sub> $\leq$ 5.5 V            | -   | -   | 16  | MHz   | 90/10% V <sub>IO</sub>                     |

# XRES

# Table 8. XRES DC Specifications

| Spec ID#             | Parameter            | Description                  | Min                      | Тур                      | Max                      | Units | Details/<br>Conditions                                        |

|----------------------|----------------------|------------------------------|--------------------------|--------------------------|--------------------------|-------|---------------------------------------------------------------|

| SID77                | V <sub>IH</sub>      | Input voltage high threshold | 0.7 ×<br>V <sub>DD</sub> | -                        | -                        | V     | CMOS Input                                                    |

| SID78                | V <sub>IL</sub>      | Input voltage low threshold  | -                        | -                        | 0.3 ×<br>V <sub>DD</sub> | V     | CMOS Input                                                    |

| SID79                | R <sub>PULLUP</sub>  | Pull-up resistor             | 3.5                      | 5.6                      | 8.5                      | kΩ    |                                                               |

| SID80                | C <sub>IN</sub>      | Input capacitance            | -                        | 3                        | 7                        | pF    |                                                               |

| SID81 <sup>[8]</sup> | V <sub>HYSXRES</sub> | Input voltage hysteresis     | _                        | 0.05*<br>V <sub>DD</sub> | _                        | mV    | Typical hysteresis<br>is 200 mV for V <sub>DD</sub><br>> 4.5V |

# Table 9. XRES AC Specifications

| Spec ID#               | Parameter              | Description                     | Min | Тур | Max | Units | Details/<br>Conditions |

|------------------------|------------------------|---------------------------------|-----|-----|-----|-------|------------------------|

| SID83 <sup>[8]</sup>   | TRESETWIDTH            | Reset pulse width               | 5   | -   | Ι   | μs    |                        |

| BID#194 <sup>[8]</sup> | T <sub>RESETWAKE</sub> | Wake-up time from reset release | -   | -   | 3   | ms    |                        |

# Analog Peripherals

Comparator

# Table 10. Comparator DC Specifications

| Spec ID#              | Parameter            | Description                           | Min   | Тур | Max   | Units | Details/<br>Conditions                                       |

|-----------------------|----------------------|---------------------------------------|-------|-----|-------|-------|--------------------------------------------------------------|

| SID330 <sup>[8]</sup> | I <sub>CMP1</sub>    | Block current, High Bandwidth mode    | -     | -   | 110   | μA    |                                                              |

| SID331 <sup>[8]</sup> | I <sub>CMP2</sub>    | Block current, Low Power mode         | -     | -   | 85    | μA    |                                                              |

| SID332 <sup>[8]</sup> | V <sub>OFFSET1</sub> | Offset voltage, High Bandwidth mode   | -     | 10  | 30    | mV    |                                                              |

| SID333 <sup>[8]</sup> | V <sub>OFFSET2</sub> | Offset voltage, Low Power mode        | -     | 10  | 30    | mV    |                                                              |

| SID334 <sup>[8]</sup> | Z <sub>CMP</sub>     | DC input impedance of comparator      | 35    | -   | _     | MΩ    |                                                              |

| SID338 <sup>[8]</sup> | VINP_COMP            | Comparator input range                | 0     | -   | 3.6   | V     | Max input voltage<br>is lower of 3.6 V or<br>V <sub>DD</sub> |

| SID339                | VREF_COMP            | Comparator internal voltage reference | 1.188 | 1.2 | 1.212 | V     |                                                              |

# Table 11. Comparator AC Specifications (Guaranteed by Characterization)

| Spec ID#              | Parameter          | Description                                           | Min | Тур | Max | Units | Details/<br>Conditions |

|-----------------------|--------------------|-------------------------------------------------------|-----|-----|-----|-------|------------------------|

| SID336 <sup>[8]</sup> | T <sub>COMP1</sub> | Response Time High Bandwidth mode,<br>50-mV overdrive | -   | Ι   | 90  | ns    |                        |

| SID337 <sup>[8]</sup> | T <sub>COMP2</sub> | Response Time Low Power mode,<br>50-mV overdrive      | _   | _   | 110 | ns    |                        |

# CSD

# Table 12. CSD and IDAC Block Specifications

| Spec ID#     | Parameter                | Description                                                           | Min  | Тур   | Мах                  | Units | Details/<br>Conditions                                                                                                                  |

|--------------|--------------------------|-----------------------------------------------------------------------|------|-------|----------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------|

| CSD and IDAC | C Specifications         | •                                                                     |      |       |                      |       |                                                                                                                                         |

| SYS.PER#3    | VDD_RIPPLE               | Max allowed ripple on power supply,<br>DC to 10 MHz                   | -    | -     | ±50                  | mV    | VDD > 2V (with ripple),<br>25 °C T <sub>A</sub> ,<br>Sensitivity = 0.1 pF                                                               |

| SYS.PER#16   | VDD_RIPPLE_1.8           | Max allowed ripple on power supply,<br>DC to 10 MHz                   | _    | -     | ±25                  | mV    | VDD > 1.75V (with ripple),<br>25 C T <sub>A</sub> , Parasitic Capaci-<br>tance (C <sub>P</sub> ) < 20 pF, Sensi-<br>tivity $\ge$ 0.4 pF |

| SID.CSD#15   | VREFHI                   | Reference Buffer Output                                               | 1.1  | 1.2   | 1.3                  | V     |                                                                                                                                         |

| SID.CSD#16   | IDAC1IDD                 | IDAC1 (8-bits) block current                                          | -    | -     | 1125                 | μA    |                                                                                                                                         |

| SID.CSD#17   | IDAC2IDD                 | IDAC2 (7-bits) block current                                          | _    | -     | 1125                 | μA    |                                                                                                                                         |

| SID308       | V <sub>CSD</sub>         | Voltage range of operation                                            | 1.71 | -     | 5.5                  | V     | 1.8 V ±5% or 1.8 V to 5.5 V                                                                                                             |

| SID308A      | VCOMPIDAC                | Voltage compliance range of IDAC                                      | 0.8  | -     | V <sub>DD</sub> –0.8 | V     |                                                                                                                                         |

| SID309       | IDAC1 <sub>DNL</sub>     | DNL for 8-bit resolution                                              | -1   | -     | 1                    | LSB   |                                                                                                                                         |

| SID310       | IDAC1 <sub>INL</sub>     | INL for 8-bit resolution                                              | -3   | -     | 3                    | LSB   |                                                                                                                                         |

| SID311       | IDAC2 <sub>DNL</sub>     | DNL for 7-bit resolution                                              | -1   | -     | 1                    | LSB   |                                                                                                                                         |

| SID312       | IDAC2 <sub>INL</sub>     | INL for 7-bit resolution                                              | -3   | -     | 3                    | LSB   |                                                                                                                                         |

| SID313       | SNR                      | Ratio of counts of finger to noise.<br>Guaranteed by characterization | 5    | -     | -                    | Ratio | Capacitance range of 9 to 35 pF, 0.1 pF sensitivity                                                                                     |

| SID314       | IDAC1 <sub>CRT1</sub>    | Output current of IDAC1 (8 bits) in high range                        | -    | 612   | -                    | μA    |                                                                                                                                         |

| SID314A      | IDAC1 <sub>CRT2</sub>    | Output current of IDAC1(8 bits) in low range                          | -    | 306   | -                    | μA    |                                                                                                                                         |

| SID315       | IDAC2 <sub>CRT1</sub>    | Output current of IDAC2 (7 bits) in high range                        | _    | 304.8 | -                    | μA    |                                                                                                                                         |

| SID315A      | IDAC2 <sub>CRT2</sub>    | Output current of IDAC2 (7 bits) in low range                         | _    | 152.4 | -                    | μA    |                                                                                                                                         |

| SID320       | IDAC <sub>OFFSET</sub>   | All zeroes input                                                      | -    | -     | ±1                   | LSB   |                                                                                                                                         |

| SID321       | IDAC <sub>GAIN</sub>     | Full-scale error less offset                                          | _    | -     | ±10                  | %     |                                                                                                                                         |

| SID322       | IDAC <sub>MISMATCH</sub> | Mismatch between IDACs                                                | -    | -     | 7                    | LSB   |                                                                                                                                         |

| SID323       | IDAC <sub>SET8</sub>     | Settling time to 0.5 LSB for 8-bit IDAC                               | -    | -     | 10                   | μs    | Full-scale transition. No external load.                                                                                                |

| SID324       | IDAC <sub>SET7</sub>     | Settling time to 0.5 LSB for 7-bit IDAC                               | -    | -     | 10                   | μs    | Full-scale transition. No external load.                                                                                                |

| SID325       | CMOD                     | External modulator capacitor.                                         | _    | 2.2   | _                    | nF    | 5-V rating, X7R or NP0 cap.                                                                                                             |

# **Digital Peripherals**

Timer Counter Pulse-Width Modulator (TCPWM)

# Table 13. TCPWM Specifications

| Spec ID      | Parameter             | Description                         | Min  | Тур | Max | Units | Details/Conditions                                                                                          |

|--------------|-----------------------|-------------------------------------|------|-----|-----|-------|-------------------------------------------------------------------------------------------------------------|

| SID.TCPWM.1  | ITCPWM1               | Block current consumption at 3 MHz  | -    | -   | 45  | μA    | All modes (TCPWM)                                                                                           |

| SID.TCPWM.2  | ITCPWM2               | Block current consumption at 8 MHz  | -    | -   | 145 | μA    | All modes (TCPWM)                                                                                           |

| SID.TCPWM.2A | ITCPWM3               | Block current consumption at 16 MHz | _    | -   | 160 | μA    | All modes (TCPWM)                                                                                           |

| SID.TCPWM.3  | TCPWM <sub>FREQ</sub> | Operating frequency                 | _    | -   | Fc  | MHz   | Fc max = CLK_SYS.<br>Maximum = 16 MHz                                                                       |

| SID.TCPWM.4  | TPWM <sub>ENEXT</sub> | Input trigger pulse width           | 2/Fc | Ι   | -   | ns    | For all trigger events <sup>[9]</sup>                                                                       |

| SID.TCPWM.5  | TPWM <sub>EXT</sub>   | Output trigger pulse widths         | 2/Fc | Ι   | _   | ns    | Minimum possible<br>width of Overflow,<br>Underflow, and CC<br>(Counter equals<br>Compare value)<br>outputs |

| SID.TCPWM.5A | TC <sub>RES</sub>     | Resolution of counter               | 1/Fc | -   | _   | ns    | Minimum time<br>between successive<br>counts                                                                |

| SID.TCPWM.5B | PWM <sub>RES</sub>    | PWM resolution                      | 1/Fc | -   | -   | ns    | Minimum pulse width<br>of PWM Output                                                                        |

| SID.TCPWM.5C | Q <sub>RES</sub>      | Quadrature inputs resolution        | 1/Fc | -   | _   | ns    | Minimum pulse width<br>between Quadrature<br>phase inputs.                                                  |

# βĈ

# Table 14. Fixed I<sup>2</sup>C DC Specifications<sup>[10]</sup>

| Spec ID   | Parameter         | Description                                 | Min | Тур | Max | Units | Details/Conditions |

|-----------|-------------------|---------------------------------------------|-----|-----|-----|-------|--------------------|

| SID149    | I <sub>I2C1</sub> | Block current consumption at 100 kHz        | -   | -   | 25  | μA    |                    |

| SID150    | I <sub>I2C2</sub> | Block current consumption at 400 kHz        | -   | -   | 135 | μA    |                    |

| SID.PWR#5 | ISBI2C            | I <sup>2</sup> C enabled in Deep Sleep mode | _   | _   | 2.5 | μA    |                    |

# Table 15. Fixed I<sup>2</sup>C AC Specifications<sup>[10]</sup>

| Spec ID | Parameter         | Description | Min | Тур | Max | Units | <b>Details/Conditions</b> |

|---------|-------------------|-------------|-----|-----|-----|-------|---------------------------|

| SID153  | F <sub>I2C1</sub> | Bit rate    | -   | -   | 400 | Kbps  |                           |

Note 9. Trigger events can be Stop, Start, Reload, Count, Capture, or Kill depending on which mode of operation is selected. 10. Guaranteed by characterization.

# Memory

# Table 16. Flash DC Specifications

| Spec ID | Parameter       | Description               | Min  | Тур | Max | Units | Details/Conditions |

|---------|-----------------|---------------------------|------|-----|-----|-------|--------------------|

| SID173  | V <sub>PE</sub> | Erase and program voltage | 1.71 | -   | 5.5 | V     |                    |

### Table 17. Flash AC Specifications

| Spec ID                  | Parameter                              | Description                                                  | Min   | Тур | Max | Units   | Details/Conditions     |

|--------------------------|----------------------------------------|--------------------------------------------------------------|-------|-----|-----|---------|------------------------|

| SID174                   | T <sub>ROWWRITE</sub> <sup>[11]</sup>  | Row (block) write time (erase and program)                   | -     | _   | 20  | ms      | Row (block) = 64 bytes |

| SID175                   | T <sub>ROWERASE</sub> <sup>[11]</sup>  | Row erase time                                               | -     | _   | 13  | ms      |                        |

| SID176                   | TROWPROGRAM <sup>[1</sup>              | Row program time after erase                                 | -     | -   | 7   | ms      |                        |

| SID178                   | T <sub>BULKERASE</sub> <sup>[11]</sup> | Bulk erase time (16 KB)                                      | -     | -   | 15  | ms      |                        |

| SID180 <sup>[12]</sup>   | T <sub>DEVPROG</sub> <sup>[11]</sup>   | Total device program time                                    | -     | -   | 7.5 | seconds |                        |

| SID181 <sup>[12]</sup>   | F <sub>END</sub>                       | Flash endurance                                              | 100 K | -   | -   | cycles  |                        |

| SID182 <sup>[12]</sup>   | F <sub>RET</sub>                       | Flash retention. T <sub>A</sub> ≤ 55 °C, 100 K<br>P/E cycles | 20    | _   | _   | years   |                        |

| SID182A <sup>[12</sup> ] |                                        | Flash retention. $T_A \le 85 \text{ °C}$ , 10 K P/E cycles   | 10    | _   | _   | years   |                        |

#### System Resources

Power-on Reset (POR)

# Table 18. Power On Reset (PRES)

| Spec ID                | Parameter             | Description            | Min  | Тур | Max | Units | Details/Conditions |

|------------------------|-----------------------|------------------------|------|-----|-----|-------|--------------------|

| SID.CLK#6              | SR_POWER_UP           | Power supply slew rate | 1    | -   | 67  | V/ms  | At power-up        |

| SID185 <sup>[12]</sup> | V <sub>RISEIPOR</sub> | Rising trip voltage    | 0.80 | -   | 1.5 | V     |                    |

| SID186 <sup>[12]</sup> | V <sub>FALLIPOR</sub> | Falling trip voltage   | 0.70 | -   | 1.4 | V     |                    |

# Table 19. Brown-out Detect (BOD) for V<sub>CCD</sub>

| Spec ID                | Parameter              | Description                                | Min  | Тур | Max  | Units | Details/Conditions |

|------------------------|------------------------|--------------------------------------------|------|-----|------|-------|--------------------|

| SID190 <sup>[12]</sup> | V <sub>FALLPPOR</sub>  | BOD trip voltage in active and sleep modes | 1.48 | -   | 1.62 | V     |                    |

| SID192 <sup>[12]</sup> | V <sub>FALLDPSLP</sub> | BOD trip voltage in Deep Sleep             | 1.11 | -   | 1.5  | V     |                    |

Notes

11. It can take as much as 20 milliseconds to write to Flash. During this time the device should not be Reset, or Flash operations will be interrupted and cannot be relied on to have completed. Reset sources include the XRES pin, software resets, CPU lockup states and privilege violations, improper power supply levels, and watchdogs. Make certain that these are not inadvertently activated.

# SWD Interface

# Table 20. SWD Interface Specifications

| Spec ID                 | Parameter    | Description                                            | Min    | Тур | Max   | Units | Details/Conditions                  |

|-------------------------|--------------|--------------------------------------------------------|--------|-----|-------|-------|-------------------------------------|

| SID213                  | F_SWDCLK1    | $3.3~V \leq V_{DD} \leq 5.5~V$                         | -      | _   | 14    | MHz   | SWDCLK ≤ 1/3 CPU<br>clock frequency |

| SID214                  | F_SWDCLK2    | $1.71 \text{ V} \leq \text{V}_{DD} \leq 3.3 \text{ V}$ | -      | _   | 7     | MHz   | SWDCLK ≤ 1/3 CPU<br>clock frequency |

| SID215 <sup>[13]</sup>  | T_SWDI_SETUP | T = 1/f SWDCLK                                         | 0.25*T | -   | -     | ns    |                                     |

| SID216 <sup>[13]</sup>  | T_SWDI_HOLD  | T = 1/f SWDCLK                                         | 0.25*T | -   | -     | ns    |                                     |

|                         | T_SWDO_VALID |                                                        | -      | -   | 0.5*T | ns    |                                     |

| SID217A <sup>[13]</sup> | T_SWDO_HOLD  | T = 1/f SWDCLK                                         | 1      | -   | -     | ns    |                                     |

Internal Main Oscillator

# Table 21. IMO DC Specifications

(Guaranteed by Design)

| Spec ID | Parameter         | Description                     | Min | Тур | Max | Units | <b>Details/Conditions</b> |

|---------|-------------------|---------------------------------|-----|-----|-----|-------|---------------------------|

| SID218  | I <sub>IMO1</sub> | IMO operating current at 48 MHz | _   | -   | 250 | μA    |                           |

| SID219  | I <sub>IMO2</sub> | IMO operating current at 24 MHz | -   | -   | 180 | μA    |                           |

# Table 22. IMO AC Specifications

| Spec ID | Parameter               | Description                                    | Min | Тур | Max | Units | Details/Conditions                                                                                   |

|---------|-------------------------|------------------------------------------------|-----|-----|-----|-------|------------------------------------------------------------------------------------------------------|

| SID223  | F <sub>IMOTOL1</sub>    | Frequency variation at 24 and 32 MHz (trimmed) | _   | _   | ±2  | %     | 2 V $\leq$ V $_{DD}$ $\leq$ 5.5 V, and –25 $^\circ\text{C}$ $\leq$ T $_A$ $\leq$ 85 $^\circ\text{C}$ |