# 73M1866B/73M1966B MicroDAA™ with PCM Highway

## Simplifying System Integration™

**DATA SHEET**

DS\_1x66B\_001

April 2010

#### **DESCRIPTION**

The 73M1866B and 73M1966B use the Teridian patented Data Access Arrangement function (MicroDAA®) designed exclusively for Foreign-Exchange-Office (FXO) in Voice-over-IP (VoIP) applications. These devices provide much of the circuitry required to connect PCM formatted voice channels to a PSTN via a two-wire twisted pair interface. The package options provide the necessary functional programmability and protection required for easy worldwide homologation.

The family of devices consists of the 73M1866B and the 73M1966B. The 73M1866B MicroDAA is the world's first single-package silicon Data Access Arrangement (DAA). Suitable applications for the 73M1866B and 73M1966B devices include VoIP equipment that must provide connectivity to the PSTN for purposes of guaranteeing emergency service calling, redundancy for supplementary connectivity for voice, and maintenance services.

The 73M1966B device set consists of the 73M1906B Host-Side Device that provides digital data, control interfaces and power to the 73M1916 Line-Side Device.

These devices are based on an innovative and patented technology, which sets new standards in reliability and cost. A small pulse transformer forms a digital isolation barrier, transferring both power and data to the PSTN line-side components. This method results in reliable operation in the presence of EMI and a tolerance to line voltage variations by providing power to the Line-Side Device across the barrier. The devices also support the ability to provide up to an additional +6 dB of analog gain to the line-side transmit and +3 dB in the receive signal paths. The device supports transmit and receive digital gain ranging from –18 dB to +7.375 dB by increments of 0.125 dB.

The digital side provides a PCM highway interface with automatic clock rate detection. With an 8-kHz sampling rate, the devices include an ITU-T G.711 compliant codec with selectable  $\mu$ -law and A-law companding modes. The devices also provide a 16-bit linear mode, which is suitable for interfacing with wide band codecs, as well as 16 kHz sampling rate. Device control is performed over an SPI interface. The SPI supports daisy chain operation.

Through its PCM interface, the 73M1966B can be connected to other PCM enabled devices such as POTS codecs, ISDN codecs, E1/T1 framers, etc.

Additional DAA functions supported by the 73M1x66B devices include a call progress monitor, Caller ID Type I and II, ring detection, pulse dialing, billing tone detection and polarity reversal detection.

#### **APPLICATIONS**

- Computer Telephony

- VOIP Equipment

- PBX Systems

- Internet Appliances

- Voicemail Systems

- POTS Termination Equipment

#### **FEATURES**

- PCM highway data interface supporting both slave and master modes

- PCM highway interface supporting both E-1 and T-1

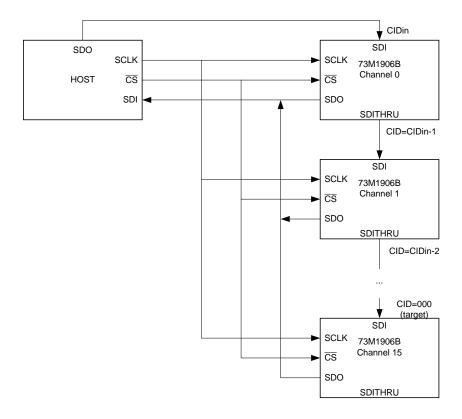

- SPI control interface, with daisy chain support for up to 16 devices

- Designed to meet global DAA compliance FCC, ETSI ES 203 021-2, JATE and other PTT standards.

- 8 kHz and 16 kHz sample rates

- 16-bit linear mode

- TX and RX gains adjustable in 0.125 dB increments

- μ-Law, A-law *ITU-T Recommendation G.711* compliant compander operation

- Automatic clock rate detection

- Low power modes

- Polarity Reversal detection

- GPIO for user-configurable I/O ports

- Call Progress Monitor

- Isolation up to 6 kV

- THD -80 dB

- 5 V tolerant I/O on selected pins

- 3.0 V 3.6 V operating voltage

- Industrial temperature range (-40 °C to +85 °C)

- 5x5 mm 32-pin QFN or 20-pin TSSOP packages

- RoHS compliant (6/6) lead-free package

# **Table of Contents**

| 1 | Intro      | duction                                                                   | 6  |

|---|------------|---------------------------------------------------------------------------|----|

| 2 | Pino       | ut                                                                        | 8  |

|   | 2.1        | 73M1906B 20-Pin TSSOP Pinout.                                             | 8  |

|   | 2.2        | 73M1916 20-Pin TSSOP Pinout                                               | 9  |

|   | 2.3        | 73M1906B 32-Pin QFN Pinout                                                |    |

|   | 2.4        | 73M1916 32-Pin QFN Pinout                                                 |    |

|   | 2.5        | 73M1866B Pinout                                                           |    |

|   | 2.6        | Requisite Use of Exposed Bottom Pad on 73M1866B and 73M1966B QFN Packages |    |

| 3 | Elec       | trical Characteristics and Specifications                                 | 16 |

|   | 3.1        | Isolation Barrier Characteristics                                         |    |

|   | 3.2        | Electrical Specifications                                                 |    |

|   |            | 3.2.1 Absolute Maximum Ratings                                            |    |

|   |            | 3.2.2 Recommended Operating Conditions                                    |    |

|   | 3.3        | 3.2.3 DC Characteristics                                                  |    |

|   | 3.3        | Interface Timing Specification                                            |    |

|   |            | 3.3.2 PCM Highway Interface                                               |    |

|   | 3.4        | Analog Specifications                                                     |    |

|   |            | 3.4.1 DC Specifications                                                   |    |

|   |            | 3.4.2 Call Progress Monitor                                               | 21 |

|   | 3.5        | 73M1x66B Line-Side Electrical Specifications (73M1916)                    | 22 |

|   | 3.6        | Reference and Regulation                                                  |    |

|   | 3.7        | DC Transfer Characteristics                                               |    |

|   | 3.8<br>3.9 | Transmit Path                                                             |    |

|   |            | Transmit Hybrid Cancellation                                              |    |

|   |            | Receive Notch Filter                                                      |    |

|   |            | Detectors                                                                 |    |

|   |            | 3.12.1 Over-Voltage Detector                                              |    |

|   |            | 3.12.2 Over-Current Detector                                              |    |

|   |            | 3.12.3 Under-Voltage Detector                                             |    |

|   |            | 3.12.4 Over-Load Detector                                                 |    |

| 4 | Appl       | ications Information                                                      |    |

|   | 4.1        | Example Schematic of the 73M1966B and 73M1866B                            |    |

|   | 4.2        | Bill of Materials                                                         |    |

|   | 4.3        | Over-Voltage and EMI Protection                                           |    |

|   | 4.4        | Isolation Barrier Pulse Transformer                                       |    |

| 5 |            | nterfacenterface                                                          |    |

| 6 | Cont       | rol and Status Registers                                                  | 37 |

| 7 | Hard       | ware Control Functions                                                    | 41 |

|   | 7.1        | Device Revision                                                           |    |

|   | 7.2        | Interrupt Control                                                         |    |

|   | 7.3        | Power Management                                                          |    |

|   | 7.4        | Device Clock Management                                                   | 42 |

|   | 7.5        | GPIO Registers                                                            |    |

|   | 7.6        | Call Progress Monitor                                                     |    |

|   | 7.7        | 16 kHz Operation of Call Progress Monitor                                 |    |

| _ | 7.8        | Device Reset                                                              |    |

| 8 |            | Highway Interface and Signal Processing                                   |    |

|   | 8.1        | PCM Highway Interface Timing                                              |    |

|   | 8.2        | PCM Clock Frequencies                                                     |    |

|   | 8.3        | Master Mode                                                               |    |

|   | 8.4        | A-law / μ-law Compander                                                   | 41 |

|     | 8.5   | Transmit and Receive Levels                                      |    |

|-----|-------|------------------------------------------------------------------|----|

|     |       | 8.5.2 µ-Law                                                      |    |

|     |       | 8.5.3 Transmit and Receive Level Control                         |    |

|     | 8.6   | Transmit Path Signal Processing                                  |    |

|     | 0.0   | 8.6.1 General Description                                        |    |

|     |       | 8.6.2 Total Transmit Path Response.                              |    |

|     |       | 8.6.3 73M1x66B Transmit Spectrum                                 |    |

|     | 8.7   | Receive Path Signal Processing.                                  |    |

|     |       | 8.7.1 General Description                                        |    |

|     |       | 8.7.2 Total Receive Path Response                                |    |

|     |       | 8.7.3 Receiver DC Offset Subtraction                             | 51 |

|     | 8.8   | PCM Control Functions                                            |    |

|     |       | 8.8.1 Transmit and Receive Level Control                         | 57 |

|     |       | 8.8.2 Time Slot Assignment Example                               | 59 |

| 9   | Barri | ier Information                                                  | 60 |

|     | 9.1   | Isolation Barrier                                                | 60 |

|     | 9.2   | Barrier Powered Options                                          |    |

|     | 0.2   | 9.2.1 Barrier Powered Operation                                  |    |

|     |       | 9.2.2 Line Powered Operation                                     |    |

|     | 9.3   | Synchronization of the Barrier                                   |    |

|     | 9.4   | Auto-Poll                                                        |    |

|     | 9.5   | Barrier Control Functions                                        |    |

|     | 9.6   | Line-Side Device Operating Modes                                 |    |

|     | 9.7   | Fail-Safe Operation of Line-Side Device                          |    |

| 10  | Conf  | figurable Direct Access Arrangement (DAA)                        | 64 |

|     |       | Pulse Dialing                                                    |    |

|     |       | DC Termination                                                   |    |

|     |       | AC Termination                                                   |    |

|     |       | Billing Tone Rejection                                           |    |

|     |       | Trans-Hybrid Cancellation                                        |    |

|     |       | Direct Access Arrangement Control Functions                      |    |

|     | 10.7  | International Register Settings Table for DC and AC Terminations | 72 |

| 11  | Line  | Sensing and Status                                               | 73 |

|     |       | Auxiliary A/D Converter                                          |    |

|     |       | Ring Detection                                                   |    |

|     |       | Line In Use Detection (LIU)                                      |    |

|     |       | Parallel Pick Up (PPU)                                           |    |

|     | 11.5  | Polarity Reversal Detection                                      | 73 |

|     |       | Off-hook Detection of Caller ID Type II                          |    |

|     |       | Voltage and Current Detection                                    |    |

|     |       | Under Voltage Detection (UVD)                                    |    |

|     |       | Over Voltage Detection (OVD)                                     |    |

|     |       | 0 AC Signal Overload Detection                                   |    |

|     |       | 1 Over Current Detection (OID)                                   |    |

|     | 11.12 | 2 Line Sensing Control Functions                                 | 75 |

| 12  | Loop  | bback and Testing Modes                                          | 78 |

| 13  | -     | ormance                                                          |    |

| 13  |       |                                                                  |    |

|     |       | Transmit                                                         |    |

| _   |       | Receive                                                          |    |

| 14  |       | rage Layout                                                      |    |

| 15  | Orde  | ering Information                                                | 87 |

| 16  | Cont  | act Information                                                  | 87 |

| Rev | ision | History                                                          | 88 |

| •   |       | ,                                                                |    |

# **Figures**

| Figure 1: Simple 73M1x66B Reference Block Diagram                                                        |    |

|----------------------------------------------------------------------------------------------------------|----|

| Figure 2: 73M1906B 20-Pin TSSOP Pinout                                                                   | 8  |

| Figure 3: 73M1916 20-Pin TSSOP Pinout                                                                    | 9  |

| Figure 4: 73M1906B 32-Pin QFN Pinout                                                                     | 10 |

| Figure 5: 73M1916 32-Pin QFN Pinout                                                                      |    |

| Figure 6: 73M1866B 42-Pin Pinout                                                                         | 14 |

| Figure 7: SPI Timing Diagram                                                                             | 18 |

| Figure 8: PCM Timing Diagram for Positive Edge Transmit Mode and Negative Edge Receive Mode              |    |

| Figure 9: PCM Timing Diagram for Negative Edge Transmit Mode and Positive Edge Receive Mode              |    |

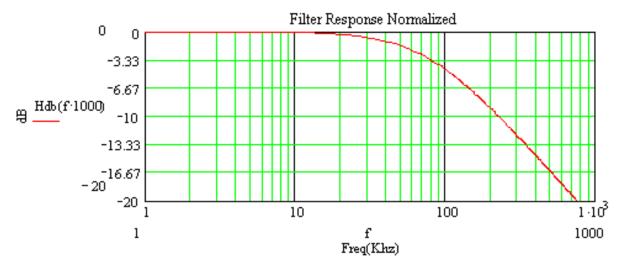

| Figure 10: Frequency Response of the Call Progress Monitor Filter                                        |    |

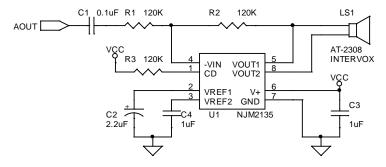

| Figure 11: Demo Board Circuit Connecting AOUT to a Speaker                                               |    |

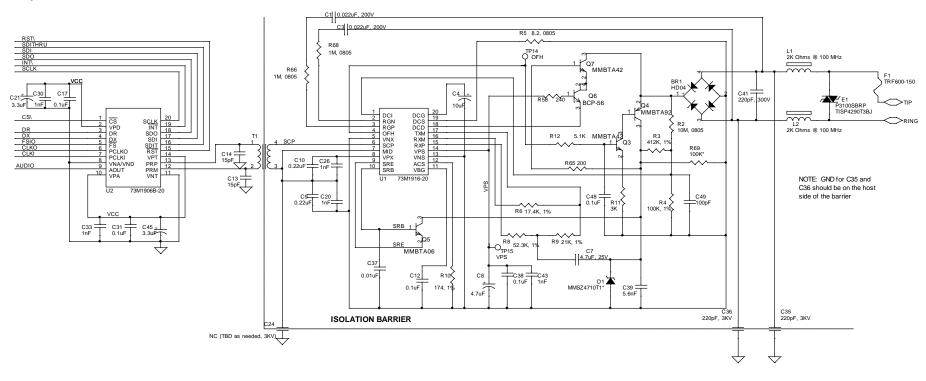

| Figure 12: Recommended Circuit for the 73M1966B                                                          |    |

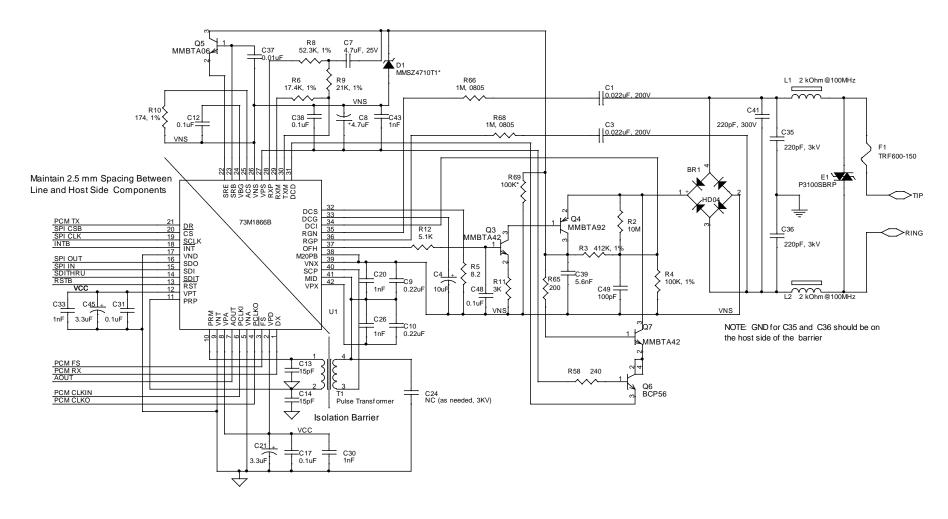

| Figure 13: Recommended Circuit for the 73M1866B                                                          |    |

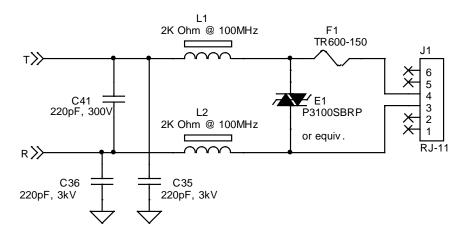

| Figure 14: Suggested Over-Voltage Protection and EMI Suppression Circuit                                 |    |

| Figure 15: Daisy-Chain Configuration                                                                     | 34 |

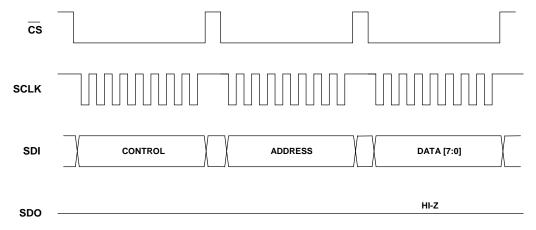

| Figure 16: SPI Write Operation – 8-bit Mode                                                              |    |

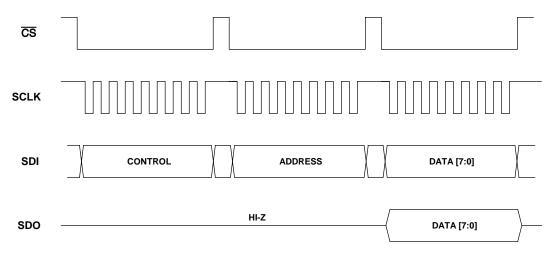

| Figure 17: SPI Read Transaction – 8-bit Mode                                                             |    |

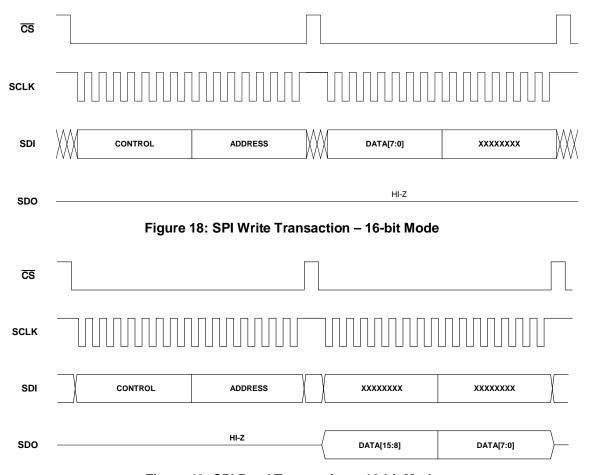

| Figure 18: SPI Write Transaction – 16-bit Mode                                                           |    |

| Figure 19: SPI Read Transaction – 16-bit Mode                                                            |    |

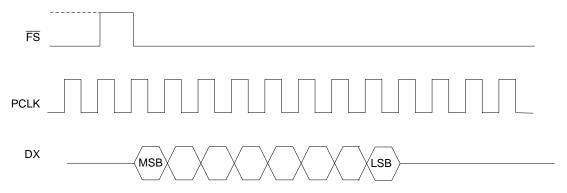

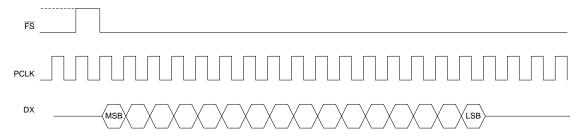

| Figure 20: 8-bit Transmission Example                                                                    |    |

| Figure 21: 16-bit Transmission Example                                                                   |    |

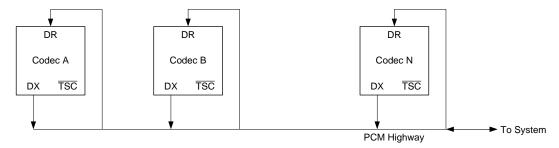

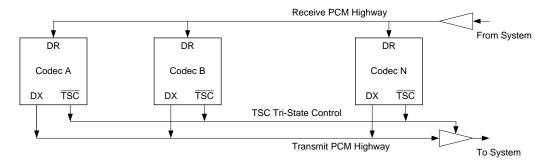

| Figure 22: Example of PCM Highway Interconnect                                                           |    |

| Figure 23: Example of PCM Highway Interconnect for Typical Large Systems                                 |    |

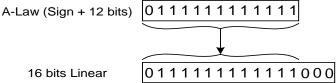

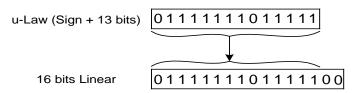

| Figure 24: Mapping of A-law Code to 16-bit Code                                                          |    |

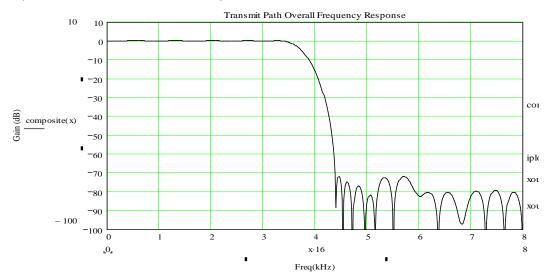

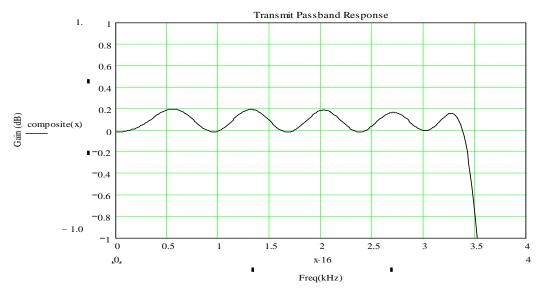

| Figure 26: Transmit Path Overall Frequency Response to Fs of 8 kHz                                       |    |

| Figure 27: Transmit Path Passband Response for an 8 kHz Sample Rate                                      |    |

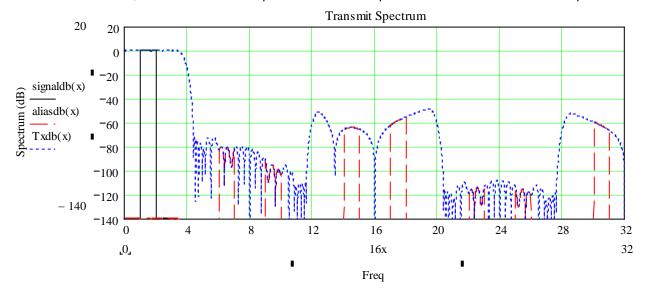

| Figure 28: Transmit Spectrum to 32 kHz for an 8 kHz Sample Rate                                          |    |

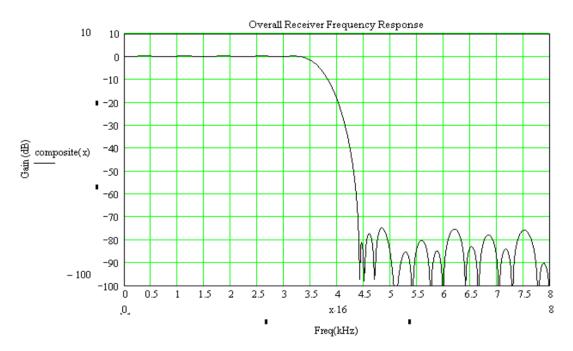

| Figure 29: Overall Frequency Response of the Receive Path                                                |    |

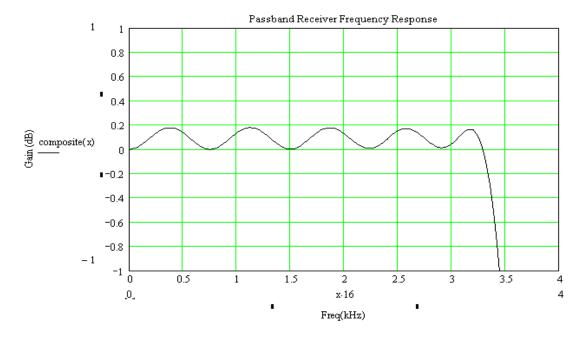

| Figure 30: Pass-band Response of the Overall Receive Path                                                |    |

| Figure 31: Timing Relationships with Various TTS, TCS, TPOL, and RTS, RCS, RPOL Settings                 |    |

| Figure 32: Line-Side Device AC and DC Circuits                                                           |    |

| Figure 33: DC-IV Characteristics                                                                         |    |

| Figure 34: Tip-Ring Voltage versus Current Using Different DCIV Settings                                 |    |

| Figure 35: Voltage versus Current in the Seize Mode is the Same for All DCIV Settings                    |    |

| Figure 36: Magnitude Response of Impedance Matching Filter, ACZ (3:0)=0010 (ES 203 021-2)                |    |

| Figure 37: Magnitude Response of Billing Tone Notch Filter                                               |    |

| Figure 38: Trans-hybrid Cancellation                                                                     | 68 |

| Figure 39: Loopback Modes Highlighted                                                                    | 78 |

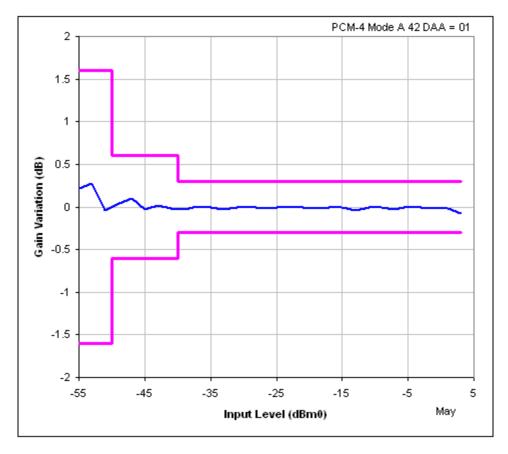

| Figure 40: Variation of Transmit Gain Digital Input to Analog Output at the Line                         | 80 |

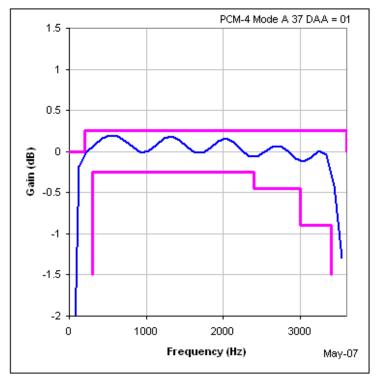

| Figure 41: Gain versus Frequency for Digital Input to Analog Output at the Line                          | 81 |

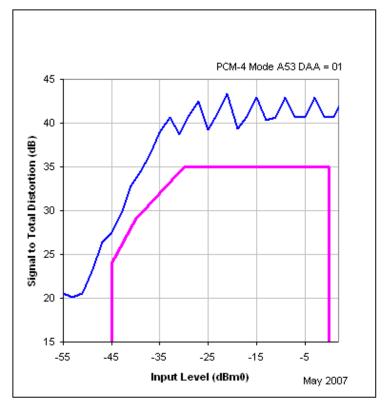

| Figure 42: Signal to Total Distortion versus Input Level for Digital Input to Analog Output to the Line  |    |

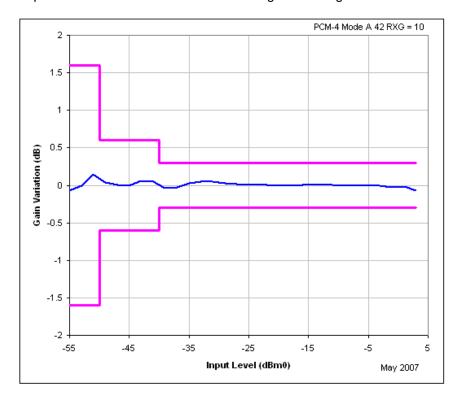

| Figure 43: Variation of Receiver Analog Gain at the Line to the Digital DX Output                        |    |

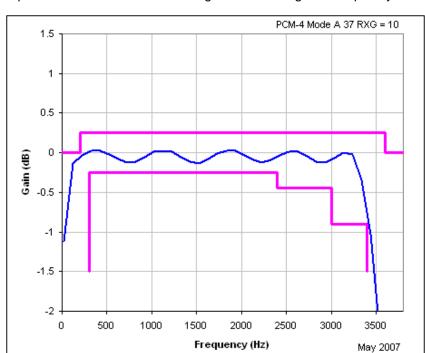

| Figure 44: Gain versus Frequency for Analog Input at the Line to the Digital DX Output                   |    |

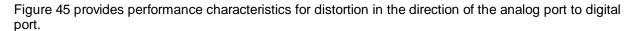

| Figure 45: Signal to Total Distortion versus Input Level for Analog at the Line to the Digital DX Output |    |

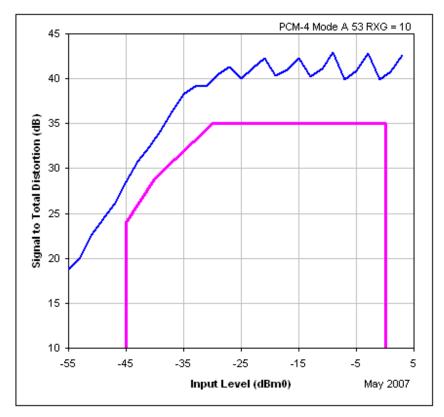

| Figure 46: Return Loss, @ 80 mA                                                                          |    |

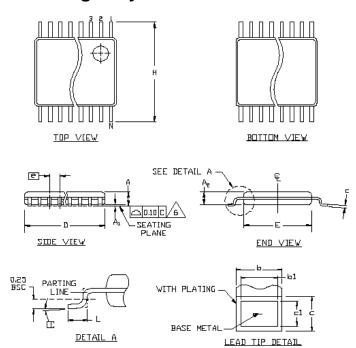

| Figure 47: 20-Pin TSSOP Package Dimensions                                                               |    |

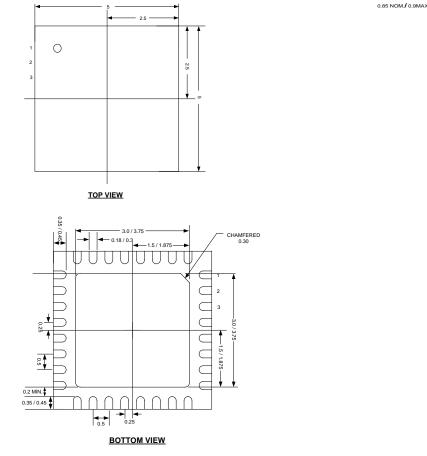

| Figure 48: 32-Pin QFN Package Dimensions                                                                 |    |

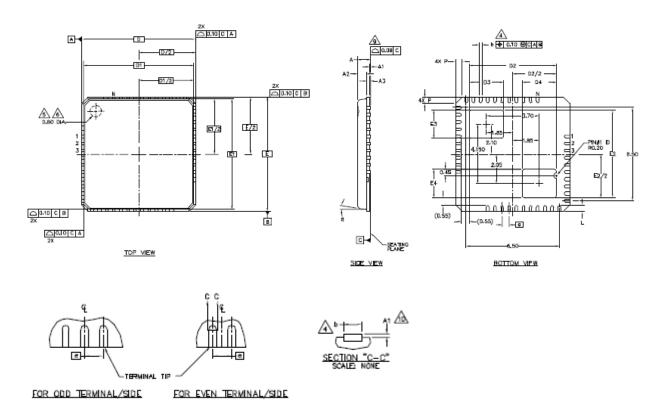

| Figure 49: 42-Pin QFN Package Dimensions                                                                 | 86 |

# **Tables**

| Table 1: 73M1906B 20-Pin TSSOP Pin Definitions                          | 8  |

|-------------------------------------------------------------------------|----|

| Table 2: 73M1916 20-Pin TSSOP Pin Definitions                           |    |

| Table 3: 73M1906B 32-Pin QFN Pin Definitions                            | 10 |

| Table 4: 73M1916 32-Pin QFN Pin Definitions                             |    |

| Table 5: 73M1866B Pin Definitions                                       |    |

| Table 6: Isolation Barrier Characteristics                              |    |

| Table 7: Absolute Maximum Device Ratings                                | 16 |

| Table 8: Recommended Operating Conditions                               | 16 |

| Table 9: DC Characteristics                                             |    |

| Table 10: SPI Interface Switching Characteristics                       |    |

| Table 11: Switching Characteristics – PCM Interface (Slave Mode)        | 19 |

| Table 12: Switching Characteristics – PCM Interface (Master Mode)       |    |

| Table 13: Reference Voltage Specifications                              |    |

| Table 14: Component Values for the Speaker Driver                       |    |

| Table 15: Call Progress Monitor Specification                           |    |

| Table 16: Line-Side Absolute Maximum Ratings                            |    |

| Table 17: VBG Specifications                                            | 23 |

| Table 18: Maximum DC Transmit Levels                                    |    |

| Table 19: Transmit Path                                                 |    |

| Table 20: Receive Path                                                  |    |

| Table 21: Transmit Hybrid Cancellation Characteristics                  |    |

| Table 22: Receive Notch Filter                                          |    |

| Table 23: Over-voltage Detector                                         |    |

| Table 24: Over-current Detector                                         |    |

| Table 25: Under-voltage Detector                                        |    |

| Table 26: Over-load Detector                                            |    |

| Table 27: Reference Bill of Materials for 73M1x66B                      |    |

| Table 28: Reference Bill of Materials for Figure 14                     |    |

| Table 29: Compatible Pulse Transformer Sources                          |    |

| Table 30: Pulse Transformer Electrical Characteristics                  |    |

| Table 31: Control and Status Register Map                               |    |

| Table 32: Alphabetical Bit Map                                          |    |

| Table 33: PCM Control Functions                                         |    |

| Table 34: Transmit Gain Control                                         |    |

| Table 35: Recommended Gain Setting                                      |    |

| Table 36: Receive Gain Control                                          |    |

| Table 37: Barrier Control Functions.                                    |    |

| Table 38: DAA Control Functions                                         |    |

| Table 39: Recommended Register Settings for International Compatibility | 72 |

| Table 40: Line Sensing Control Functions                                | 75 |

| Table 41: Loopback Modes                                                |    |

| Table 42: Loopback Modes Summary                                        |    |

| Table 43: Order Numbers and Packaging Marks                             | 87 |

#### 1 Introduction

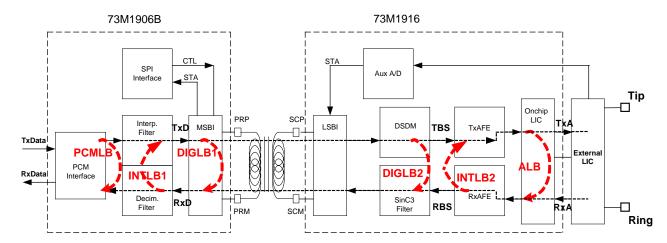

The 73M1966B is a two-device chip set that provides embedded FXO functionality by connecting a PCM interface to a voice-band PSTN. The device set supports ITU-T Recommendation G.711  $\mu$ -law and A-law companding, and also a 16-bit linear mode. High-voltage isolation is provided by the physical separation of the Host-Side (73M19106) and Line-Side (73M1916) Devices. The Host-Side and the Line-Side Devices communicate with each other using a single pulse transformer. A few low-cost components complete the DAA interface to the network. The pulse transformer transmits encoded digital data rather than analog signals as with other transformer designs. Data is transmitted and received without the usual degradation from common mode noise and magnetic coupling typical of other capacitive and voice-band transformer techniques. The data stream passed between the Host-Side and Line-Side Devices includes the media stream data, control, status, and clocking information.

This data sheet describes both the 73M1966B and 73M1866B, which will be collectively referred to as the 73M1x66B in this document.

A unique capability of the 73M1x66B Host Side device (73M1906B) is its ability to provide power to the 73M1x66B Line Side device (73M1916) via the pulse transformer.

The 73M1906B exchanges control and status information with the host using the SPI interface, while the PCM encoded media streams connect with other PCM-enabled devices using the PCM highway bus interface.

Figure 1 shows a reference block diagram of the 73M1x66B connected by a pulse transformer and example external line interface circuitry shown for clarification.

Figure 1: Simple 73M1x66B Reference Block Diagram

The Host-Side Device (73M1906B) consists of:

- 1. PCM Interface Block (PCM)

- 2. SPI Interface Block (SPI)

- 3. Transmit Interpolation Filter

- 4. Receive Decimation Filter

- 5. Host-Side Barrier Interface Circuit (HSBI)

The Line-Side Device (73M1916) consists of:

- 1. Digital Sigma Delta Modulator

- 2. Transmit Analog Front End

- 3. Receive Analog Front End including Sigma Delta Modulator

- 4. Sinc<sup>3</sup> Filter (Sinc3)

- 5. On-chip Line Interface Circuit

- 6. Line-Side Barrier Interface Circuit (LSBI)

Received data from a host connected to the PCM bus is interpolated from the sampling frequency of 8 kHz or 16 kHz (for PCM encoded streams) to twice the sampling frequency. The control information is multiplexed with the audio stream signals and transmitted across the isolation barrier to the Line-Side Device. In the Line-Side Device, the two streams are separated and the audio signal is converted to analog for transmission to the line.

An audio stream received at the analog line input pins is converted to a serialized data stream and, along with status information such as line condition from the Auxiliary Analog to Digital Converter, is transmitted over the isolation barrier using the pulse transformer. The data is extracted with status information being transmitted on the SPI. The audio stream is sent to a host using the PCM bus.

The 73M1x66B is an enhanced version of the 73M1966 that includes the additional functionality of finer resolution of transmit and receive gain, receiver DC offset subtraction and support for T-1 PCLK frequencies.

## 2 Pinout

The 73M1906B and the 73M1916 are supplied as 20-pin TSSOP packages and as 32-pin QFN packages.

## 2.1 73M1906B 20-Pin TSSOP Pinout

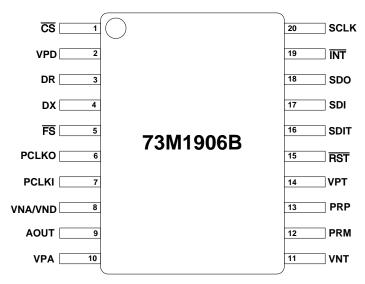

Figure 2 shows the 73M1906B 20-pin TSSOP pinout.

Figure 2: 73M1906B 20-Pin TSSOP Pinout

Table 1 describes the pin functions for the device. Decoupling capacitors on the power supplies should be included for each pair of supply pins.

| Pin<br>Number | Pin<br>Name | Туре | Description                                       |

|---------------|-------------|------|---------------------------------------------------|

| 1             | CS          | I    | SPI chip select (active low)                      |

| 2             | VPD         | PWRI | Positive digital supply                           |

| 3             | DR          | I    | PCM transmit data sent to the D to A              |

| 4             | DX          | 0    | PCM received data from the A to D                 |

| 5             | FS          | I/O  | PCM frame synchronization                         |

| 6             | PCLKO       | 0    | PCM clock output                                  |

| 7             | PCLKI       | I    | PCM clock in                                      |

| 8             | VNA/VND     | GND  | Negative analog/digital ground                    |

| 9             | AOUT        | 0    | Audio output – must be buffered for speaker       |

| 10            | VPA         | PWRI | Positive analog supply                            |

| 11            | VNT         | GND  | Negative transformer supply                       |

| 12            | PRM         | I/O  | Transformer primary minus                         |

| 13            | PRP         | I/O  | Transformer primary plus                          |

| 14            | VPT         | PWRI | Positive transformer supply                       |

| 15            | RST         | I    | Hardware reset (active low)                       |

| 16            | SDIT        | 0    | SPI data out for daisy chain mode                 |

| 17            | SDI         | I    | SPI data in                                       |

| 18            | SDO         | 0    | SPI data out                                      |

| 19            | ĪNT         | 0    | Interrupt / ring detect (active low – open drain) |

| 20            | SCLK        | I    | SPI clock                                         |

Table 1: 73M1906B 20-Pin TSSOP Pin Definitions

#### 2.2 73M1916 20-Pin TSSOP Pinout

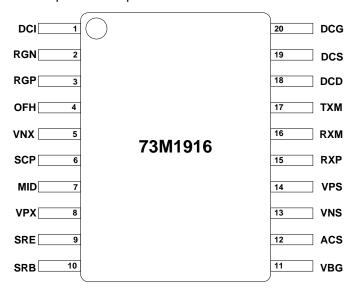

Figure 3 shows the 73M1916 20-pin TSSOP pinout.

Figure 3: 73M1916 20-Pin TSSOP Pinout

Table 2 describes the pin functions for the device. Decoupling capacitors on the power supplies should be included for each pair of supply pins.

Pin Pin Name **Description Type** Number 1 DCI ı DC loop input 2 **RGN** I Ring detect negative voltage input 3 **RGP** Ī Ring detect positive voltage input O 4 OFH Off-hook control Negative supply voltage (line side of the barrier) 5 VNX **GND** 6 SCP I/O Positive side of the secondary pulse transformer winding 7 MID I/O Charge pump midpoint PWR 8 **VPX** Supply from the barrier 9 SRE I Voltage regulator sense 10 SRB O Voltage regulator drive 11 **VBG** 0 VBG bypass, connect to 0.1 µF capacitor to VNS 12 ACS Τ AC current sense 13 **VNS GND** Analog negative supply voltage 14 **VPS PWRO** Analog positive supply voltage (output) RXP 15 Τ Receive plus - signal input **RXM** Receive minus - signal input 16 I 17 **TXM** 0 Transmit minus - transhybrid cancellation output 18 DCD 0 DC loop output 19 DCS I DC loop current sense

Table 2: 73M1916 20-Pin TSSOP Pin Definitions

Rev. 1.6

DC loop control

DCG

0

20

#### 2.3 73M1906B 32-Pin QFN Pinout

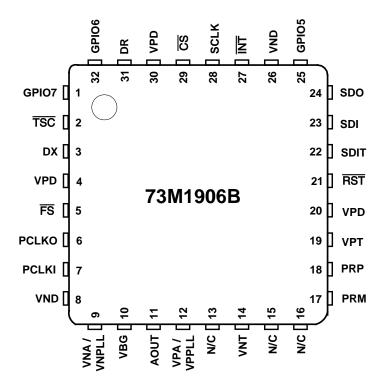

Figure 4 shows the 73M1906B 32-pin QFN pinout.

Figure 4: 73M1906B 32-Pin QFN Pinout

Table 3 describes the pin functions for the device. Decoupling capacitors on the power supplies should be included for each pair of supply pins.

Pin Pin Name Type Description Number 1 GPIO7 I/O Configurable input/output pin 2 **TSC** 0 PCM time slot control (active low) 3 DX 0 PCM received data from the A to D VPD 4 **PWR** Positive digital supply 5 FS I/O PCM frame synchronization **PCLKO** PCM clock output 6 0 7 **PCLKI** Ī PCM clock in 8 **VND GND** Negative digital ground 9 VNA/VNPLL **GND** Negative analog/PLL ground 10 **VBG** 0 Band gap voltage reference monitor 11 **AOUT** 0 Audio output – must be buffered for speaker 12 **VPA/VPPLL PWR** Positive analog/PLL supply 13 N/C No connect 14 **VNT GND** Negative transformer supply 15 N/C No connect 16 N/C No connect

Table 3: 73M1906B 32-Pin QFN Pin Definitions

| Pin<br>Number | Pin Name | Туре | Description                                       |

|---------------|----------|------|---------------------------------------------------|

| 17            | PRM      | I/O  | Transformer primary minus                         |

| 18            | PRP      | I/O  | Transformer primary plus                          |

| 19            | VPT      | PWR  | Positive transformer supply                       |

| 20            | VPD      | PWR  | Positive digital supply                           |

| 21            | RST      | I    | Hardware reset (active low)                       |

| 22            | SDIT     | 0    | SPI data out for daisy-chain mode                 |

| 23            | SDI      | I    | SPI data in                                       |

| 24            | SDO      | 0    | SPI data out                                      |

| 25            | GPIO5    | I/O  | Configurable input/output pin                     |

| 26            | VND      | GND  | Negative digital ground                           |

| 27            | ĪNT      | 0    | Interrupt / ring detect (active low – open drain) |

| 28            | SCLK     | I    | SPI clock                                         |

| 29            | CS       | I    | SPI chip select (active low)                      |

| 30            | VPD      | PWR  | Positive digital supply                           |

| 31            | DR       | I    | PCM transmit data sent to the D to A              |

| 32            | GPIO6    | I/O  | Configurable input/output pin                     |

#### 2.4 73M1916 32-Pin QFN Pinout

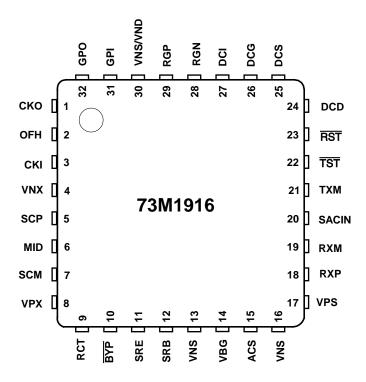

Figure 5 shows the 73M1916 32-pin QFN pinout.

Figure 5: 73M1916 32-Pin QFN Pinout

Table 4 describes the pin functions for the device. Decoupling capacitors on the power supplies should be included for each pair of supply pins.

Pin Pin Type Description Number Name CKO 0 1 Test point for recovered clock 2 OFH Off-hook control 0 3 CKI Τ Test input for clock 4 **VNX GND** Negative supply voltage 5 SCP I/O Positive side of the secondary pulse transformer winding I/O 6 MID Charge pump midpoint 7 I/O SCM Negative side of the secondary pulse transformer winding 8 **VPX PWR** Supply from the barrier 9 **RCT** External rectification – disables internal rectifier when low, leave open 10  $\overline{\mathsf{BYP}}$ Ī Test pin, leave open 11 SRE 1 Voltage regulator sense SRB 12 0 Voltage regulator drive 13 **VNS GND** Digital negative supply voltage 14 **VBG** 0 VBG bypass, connect to 0.1µF capacitor to VNS 15 ACS ı AC current sense

Table 4: 73M1916 32-Pin QFN Pin Definitions

| Pin<br>Number | Pin<br>Name | Туре | Description                                                  |  |  |  |

|---------------|-------------|------|--------------------------------------------------------------|--|--|--|

| 16            | VNS         | GND  | Analog negative supply voltage                               |  |  |  |

| 17            | VPS         | PWRO | Analog positive supply voltage (output)                      |  |  |  |

| 18            | RXP         | I    | Receive plus – signal input                                  |  |  |  |

| 19            | RXM         | I    | Receive minus – signal input                                 |  |  |  |

| 20            | SACIN       | I    | Caller ID mode AC impedance connection                       |  |  |  |

| 21            | TXM         | 0    | Transmit Minus – transhybrid cancellation output             |  |  |  |

| 22            | TST         | I    | Factory test mode, leave open                                |  |  |  |

| 23            | RST         | I    | Resets the control registers to default – weakly pulled high |  |  |  |

| 24            | DCD         | 0    | DC loop output                                               |  |  |  |

| 25            | DCS         | I    | DC loop current sense                                        |  |  |  |

| 26            | DCG         | 0    | DC loop control                                              |  |  |  |

| 27            | DCI         | I    | DC loop input                                                |  |  |  |

| 28            | RGN         | I    | Ring detect negative voltage input                           |  |  |  |

| 29            | RGP         | I    | Ring detect positive voltage input                           |  |  |  |

| 30            | VNS         | GND  | Negative supply voltage (line side of the barrier)           |  |  |  |

| 31            | GPI         | I    | General purpose input (test pin)                             |  |  |  |

| 32            | GPO         | 0    | General purpose output (test pin)                            |  |  |  |

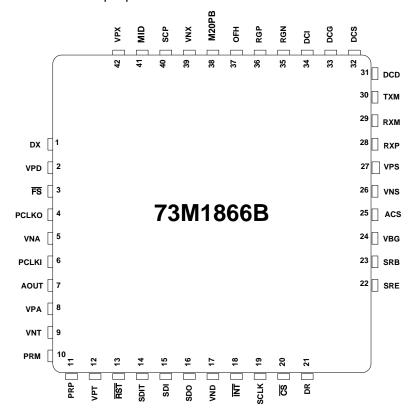

#### 2.5 73M1866B Pinout

Figure 6 shows the 73M1866B 42-pin pinout.

Figure 6: 73M1866B 42-Pin Pinout

Table 5 describes the pin functions for the device. Decoupling capacitors on the power supplies should be included for each pair of supply pins.

Pin Pin Name **Type Description** Number PCM received data from the A to D 0 1 DX 2 VPD PWR Positive digital supply 3 FS I/O PCM frame synchronization 4 0 PCM clock output **PCLKO** 5 **GND** Negative analog ground VNA 6 **PCLKI** PCM clock in 7 AOUT 0 Audio output - must be buffered for speaker 8 **VPA PWR** Positive analog supply 9 **VNT GND** Negative transformer supply 10 **PRM** I/O Transformer primary minus 11 PRP I/O Transformer primary plus 12 **PWR VPT** Positive transformer supply 13 **RST** ı Hardware reset (active low) 14 **SDIT** 0 SPI data out for daisy-chain mode 15 Ī SPI data in SDI 0 SPI data out 16 SDO

Table 5: 73M1866B Pin Definitions

| Pin<br>Number | Pin Name | Туре | Description                                              |  |

|---------------|----------|------|----------------------------------------------------------|--|

| 17            | VND      | GND  | Negative digital ground                                  |  |

| 18            | ĪNT      | 0    | Interrupt / ring detect (active low – open drain)        |  |

| 19            | SCLK     | I    | SPI clock                                                |  |

| 20            | CS       | I    | SPI chip select (active low)                             |  |

| 21            | DR       | I    | PCM transmit data sent to the D to A                     |  |

| 22            | SRE      | I    | Voltage regulator sense                                  |  |

| 23            | SRB      | 0    | Voltage regulator drive                                  |  |

| 24            | VBG      | 0    | VBG bypass, connect to 0.1µF capacitor to VNS            |  |

| 25            | ACS      | I    | AC current sense                                         |  |

| 26            | VNS      | GND  | Analog negative supply voltage                           |  |

| 27            | VPS      | PWRO | Analog positive supply voltage (output)                  |  |

| 28            | RXP      | I    | Receive plus – signal input                              |  |

| 29            | RXM      | I    | Receive minus – signal input                             |  |

| 30            | TXM      | 0    | Transmit Minus – transhybrid cancellation output         |  |

| 31            | DCD      | 0    | DC loop output                                           |  |

| 32            | DCS      | I    | DC loop current sense                                    |  |

| 33            | DCG      | 0    | DC loop control                                          |  |

| 34            | DCI      | I    | DC loop input                                            |  |

| 35            | RGN      | I    | Ring detect negative voltage input                       |  |

| 36            | RGP      | I    | Ring detect positive voltage input                       |  |

| 37            | OFH      | 0    | Off-hook control                                         |  |

| 38            | M20PB    | I    | Test pin. Connect to VNX.                                |  |

| 39            | VNX      | GND  | Negative supply voltage                                  |  |

| 40            | SCP      | I/O  | Positive side of the secondary pulse transformer winding |  |

| 41            | MID      | I/O  | Charge pump midpoint                                     |  |

| 42            | VPX      | PWR  | Supply from the barrier                                  |  |

# 2.6 Requisite Use of Exposed Bottom Pad on 73M1866B and 73M1966B QFN Packages

The exposed bottom pad is not intended for thermal relief (heat dissipation) and should not be soldered to the PCB. Soldering of the exposed pad could also compromise electrical isolation/insulation requirements for proper voltage isolation. Avoid any PCB traces or through-hole vias on the PCB beneath the exposed pad area.

# 3 Electrical Characteristics and Specifications

#### 3.1 Isolation Barrier Characteristics

Table 6 provides the characteristics of the 73M1x66B Isolation Barrier.

**Table 6: Isolation Barrier Characteristics**

| Parameter                                                            | Rating     |

|----------------------------------------------------------------------|------------|

| Barrier frequency                                                    | 768 kHz    |

| Data transfer rate across the barrier for the sampling rate of 8 kHz | 1.536 Mbps |

When 16 kHz sampling rate is selected, the frequency and data transfer rates are twice those shown above.

## 3.2 Electrical Specifications

This section provides the absolute maximum ratings, the recommended operating conditions and the DC characteristics.

#### 3.2.1 Absolute Maximum Ratings

Table 7 lists the maximum operating conditions for the 73M1x66B. Permanent device damage may occur if absolute maximum ratings are exceeded. Exposure to the extremes of the absolute maximum rating for extended periods may affect device reliability.

**Table 7: Absolute Maximum Device Ratings**

| Parameter                        | Min         | Max | Unit |

|----------------------------------|-------------|-----|------|

| Supply voltage                   | -0.5        | 4.0 | V    |

| Pin input voltage (except OSCIN) | -0.5        | 6.0 | V    |

| Pin input voltage (OSCIN)        | -0.5 to VDD | 0.5 | V    |

## 3.2.2 Recommended Operating Conditions

Function operation should be restricted to the recommended operating conditions specified in Table 8.

**Table 8: Recommended Operating Conditions**

| Parameter                                | Min | Max | Unit |

|------------------------------------------|-----|-----|------|

| Supply voltage (VDD) with respect to VSS | 3.0 | 3.6 | ٧    |

| Operating temperature                    | -40 | 85  | Ŝ    |

## 3.2.3 DC Characteristics

Table 9 lists the 73M1x66B DC characteristics.

**Table 9: DC Characteristics**

| Parameter                              | Condition           | Min                  | Nom           | Max | Unit      |    |

|----------------------------------------|---------------------|----------------------|---------------|-----|-----------|----|

| Input low voltage                      | VIL                 | _                    | -0.5          | -   | 0.2 * VDD | V  |

| Input high voltage VIH1                |                     | _                    | 0.7 VDD       | -   | 5.5       | V  |

| Output low voltage VOL                 |                     | IOL=4 mA             | _             | -   | 0.45      | V  |

| Output low voltage FSB,SCLK,           | VOL                 | IOL=1 mA             | _             | _   | 0.45      | V  |

| Output high voltage                    | VOH                 | IOH=-4 mA            | VDD - 0.45    | -   |           | V  |

| Output high voltage FSB, FSBD, SCLK    | VOH                 | IOH=-1 mA            | VDD - 0.45    | -   |           | V  |

| Input low leakage current              | IIL1                | VSS < Vin < VIL1     | 10            | _   | 40        | μA |

| Input high leakage current             | IIH1                | VIH1 < Vin < 5.5     | _             | -   | 1         | μΑ |

|                                        | IDD curre           | ent at 3.0 V - 3.6 V | Nominal at 3. | 3 V |           |    |

| Active digital current                 | IDD1 <sub>dig</sub> | _                    | _             | 1.0 | 1.5       | mΑ |

| Active PLL current                     | IDD1 <sub>pll</sub> | _                    | _             | 1.0 | 1.5       | mΑ |

| Active analog current                  | IDD1 <sub>ana</sub> | _                    | _             | 12  | 17        | mΑ |

| IDD total current*                     | IDD1                | _                    | _             | 15  | 20        | mA |

| IDD total current*                     | IDD2                | _                    | _             | 20  | 30        | mA |

| IDD current<br>PWDN=1                  | IDD3                | _                    | _             | 1.0 | 5         | μA |

| IDD current<br>SLEEP=1 (Ext Ref Clk)   | IDD4                | _                    | _             | 0.5 | 1.0       | mA |

| IDD current IDD6 ENFEH=0 (Ext Ref Clk) |                     | _                    | _             | 1.0 | 1.5       | mA |

<sup>\*</sup>Note: IDD1 is with the secondary of the barrier left open.

IDD2 is with the secondary of the barrier connected to 73M1916 fully powered.

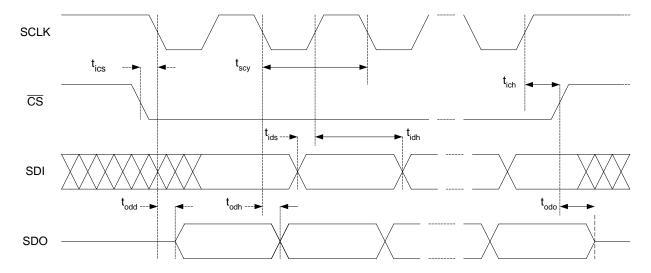

## 3.3 Interface Timing Specification

There are three interfaces associated with the 73M1x66B: the SPI interface, the PCM highway interface and the line interface. This section provides the timing specification for the SPI interface and the PCM highway interface.

#### 3.3.1 SPI Interface

Table 10 lists the characteristics for the SPI interface.

Unit **Parameter** Symbol Min Typ Max SCLK cycle time1 62.5  $t_{\text{scv}}$ ns SCLK rise time 25  $t_{scr}$ ns SCLK fall time 25 ns tscf CS setup time 25  $t_{\text{ics}}$ ns CS hold time 20 ns tich SDI setup time 25 ns tids SDI hold time 20 ns  $t_{idh}$ SDO turn on delay \_ 20 ns  $t_{odd}$ SDO turn off delay 20 ns  $t_{odo}$ SDO hold time 20  $t_{odh}$ ns SDI to SDITHRU propagation delay 6  $t_{idt}$ ns

**Table 10: SPI Interface Switching Characteristics**

Note1: The minimal value of this parameter is for the case where only one 73M1906B is connected to the host. If the daisy chain mode is used, the minimum SCLK cycle time increases according to the number of slaves in the chain.

Figure 7: SPI Timing Diagram

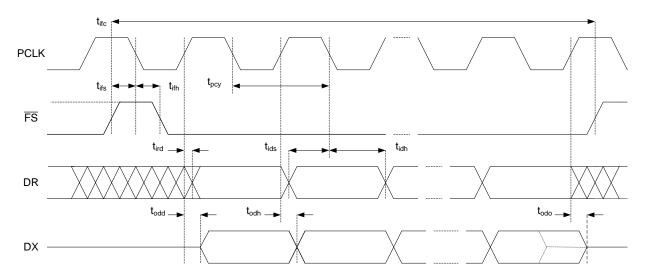

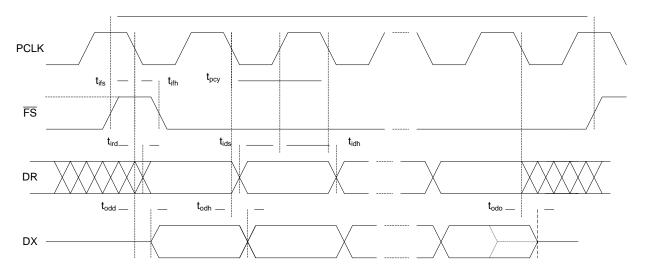

# 3.3.2 PCM Highway Interface

Table 11: Switching Characteristics – PCM Interface (Slave Mode)

| Parameter          | Symbol           | Min | Тур | Max  | Unit |

|--------------------|------------------|-----|-----|------|------|

| PCLK_IN cycle time | t <sub>pcy</sub> | 122 | ı   | 3906 | ns   |

| PCLK_IN rise time  | t <sub>pcr</sub> | _   | ı   | 25   | ns   |

| PCLK_IN fall time  | t <sub>pcf</sub> | -   | ı   | 25   | ns   |

| FS setup time      | t <sub>ifs</sub> | 25  | ı   | 1    | ns   |

| FS hold time       | t <sub>ifh</sub> | 20  | ı   | 1    | ns   |

| FS cycle time      | t <sub>ifc</sub> | _   | 125 | 1    | μs   |

| DR setup time      | t <sub>ids</sub> | 25  | ı   | ı    | ns   |

| DR hold time       | t <sub>idh</sub> | 20  | _   | _    | ns   |

| DX turn on delay   | t <sub>odd</sub> | -   | ı   | 20   | ns   |

| DX turn off delay  | t <sub>odo</sub> | _   | _   | 20   | ns   |

| DX hold time       | t <sub>odh</sub> | _   | ı   | 20   | ns   |

Table 12: Switching Characteristics – PCM Interface (Master Mode)

| Parameter           | Symbol           | Min | Тур | Max | Unit |

|---------------------|------------------|-----|-----|-----|------|

| PCLK_OUT cycle time | t <sub>pcy</sub> | _   | 488 | _   | ns   |

| PCLK_OUT rise time  | t <sub>pcr</sub> | -   | -   | 25  | ns   |

| PCLK_OUT fall time  | t <sub>pcf</sub> | _   | _   | 25  | ns   |

| FS setup time       | t <sub>ifs</sub> | 50  | -   | -   | ns   |

| FS hold time        | t <sub>ifh</sub> | 50  | -   | -   | ns   |

| FS cycle time       | t <sub>ifc</sub> | _   | 125 | _   | μs   |

| DR setup time       | t <sub>ids</sub> | 25  | -   | -   | ns   |

| DR hold time        | t <sub>idh</sub> | 20  | -   | -   | ns   |

| DX turn on delay    | t <sub>odd</sub> | _   | _   | 20  | ns   |

| DX turn off delay   | t <sub>odo</sub> | _   | _   | 20  | ns   |

| DX hold time        | t <sub>odh</sub> | _   | _   | 20  | ns   |

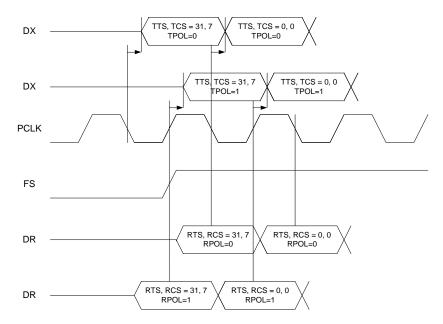

Figure 8: PCM Timing Diagram for Positive Edge Transmit Mode and Negative Edge Receive Mode

Figure 9: PCM Timing Diagram for Negative Edge Transmit Mode and Positive Edge Receive Mode

## 3.4 Analog Specifications

This section provides the electrical characterizations of the 73M1x66B analog circuitry.

## 3.4.1 DC Specifications

VBG is to be connected to an external bypass capacitor with a minimum value of 0.1  $\mu$ F. This pin is not intended for any other external use.

**Test Condition Parameter** Min **Units** Nom Max **VBG** VDD=3.0 V - 3.6 V 0.9 1.19 1.4 VBG Noise 300 Hz - 3.3 kHz dBm<sub>600</sub> -86 -80 **VBG PSRR** 300 Hz - 30 kHz 40 dΒ

**Table 13: Reference Voltage Specifications**

## 3.4.2 Call Progress Monitor

The Call Progress Monitor monitors activities on the line. The audio output contains both transmit and receive data with a configurable level individually set by Register 10h.

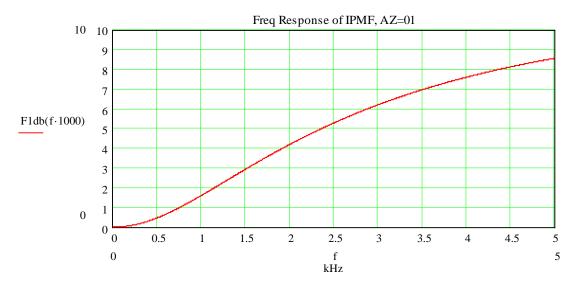

Figure 10 shows the frequency response of the Call Progress Monitor Filter based upon the characteristics of the device plus the external circuitry as shown.

Figure 10: Frequency Response of the Call Progress Monitor Filter

Figure 11: Demo Board Circuit Connecting AOUT to a Speaker

| Quantity | Reference  | Part Description    | Part                      |

|----------|------------|---------------------|---------------------------|

| 1        | C1         | Ceramic capacitor   | 0.1 μF                    |

| 1        | C2         | Ceramic capacitor   | 2.2 μF (optional)         |

| 2        | C3, C4     | Ceramic capacitor   | 1 μF                      |

| 1        | LS1        | Sound transducer    | Speaker (Intervox)        |

| 3        | R1, R2, R3 | 1/8 W resistor 0603 | 120 kΩ                    |

| 1        | U1         | Audio amplifier     | NJM2135 (New Japan Radio) |

Table 14: Component Values for the Speaker Driver

All measurements are at the AOUT pin with CMVSEL=0. Note that when CMVSEL=1, the peak signal at AOUT is increased to approximately 1.11 Vpk.

**Table 15: Call Progress Monitor Specification**

| Parameter         | Test Condition                                        | Min | Nom  | Max | Units |

|-------------------|-------------------------------------------------------|-----|------|-----|-------|

| AOUT for transmit | 1 kHz full swing code (ATX)                           | _   | _    | _   | -     |

|                   | CMRXG=11 (Mute)                                       |     |      |     |       |

|                   | Observe AOUT pin                                      |     |      |     |       |

|                   | CMTXG=00                                              | -   | 0.98 | ı   | Vpk   |

|                   | CMTXG=01 relative                                     | _   | -6   | -   | dB    |

|                   | to CMTXG=00                                           |     |      |     |       |

|                   | CMTXG=10 relative                                     | _   | -12  | -   | dB    |

|                   | to CMTXG=00                                           |     |      |     |       |

|                   | CMTXG=11 (Mute)                                       | _   | Mute | ı   | dB    |

| AOUT transmit THD | CMTXG=00                                              | _   | 40   | _   | dB    |

| AOUT for receive  | 1.0 Vpk, 1 kHz at the line or 0.5 Vpk at RXP/RXM with | _   | _    | -   | _     |

|                   | RXG=10                                                |     |      |     |       |

|                   | CMTXG=11 (Mute)                                       |     |      |     |       |

|                   | Observe AOUT pin                                      |     |      |     |       |

|                   | CMRXG=00                                              | _   | 0.96 | -   | Vpk   |

|                   | CMRXG=01 relative to CMRXG=00                         | _   | -6   | _   | dB    |

|                   | CMRXG=10 relative<br>to CMRXG=00                      | _   | -12  | _   | dB    |

|                   | CMRXG=11 (Mute)                                       | _   | Mute | _   | dB    |

| AOUT receive THD  | CMRXG=00                                              | _   | 40   | _   | dB    |

| AOUT output       |                                                       | _   | 10   | -   | kΩ    |

| impedance         |                                                       |     |      |     |       |

# 3.5 73M1x66B Line-Side Electrical Specifications (73M1916)

Table 16 lists the absolute maximum ratings for the line side. Operation outside these rating limits may cause permanent damage to this device.

**Table 16: Line-Side Absolute Maximum Ratings**

| Parameter                                 | Min  | Max | Unit |

|-------------------------------------------|------|-----|------|

| Pin input voltage from VPX to VNX         | -0.5 | 6.0 | V    |

| Pin input voltage (all other pins) to VNS | -0.5 | 4.0 | V    |

## 3.6 Reference and Regulation

Table 17 lists the VBG specifications. VBG should be connected to an external bypass capacitor with a minimum value of  $0.1 \mu F$ . This pin is not intended for any other external use.

The following conditions apply: VPX=5 V; Barrier Powered Mode; Barrier Data Rate across the Barrier=1.5 Mbps; VBG connected to 0.1 µF external cap.

**Parameter Test Condition** Min Nom Units Max **VBG** See conditions above. 1.19 VBG noise 300 Hz - 3.3 kHz -86\* -80  $dBm_{600}$ **VBG PSRR** 300 Hz - 30 kHz dB 40 VPS VPX=5.5 V 3.15 **VPS PSRR** VPX=4.5 V to 5.5 V 40 dB

**Table 17: VBG Specifications**

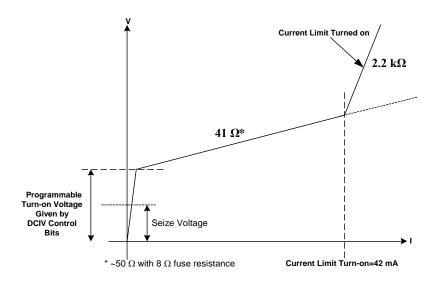

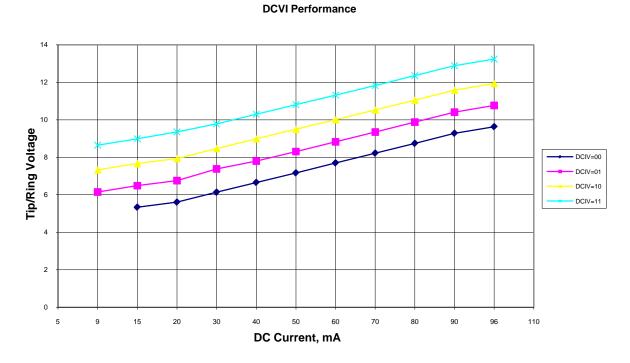

#### 3.7 DC Transfer Characteristics

Table 18 lists the maximum DC transmit levels. All tests are driven at pin DCI and measured at pin DCS. DCEN=1. ILM=1.

| Parameter                                        | Test Condition                                                | Min   | Nom  | Max   | Units |

|--------------------------------------------------|---------------------------------------------------------------|-------|------|-------|-------|

| $V_{DCON}$                                       | DCIV=00                                                       | 0.62  | 0.69 | 0.78  | V     |

| (DC "On" Voltage)                                | DCIV=01                                                       | 0.83  | 0.92 | 1.00  | V     |

|                                                  | DCIV=10                                                       | 1.08  | 1.16 | 1.24  | V     |

|                                                  | DCIV=11                                                       | 1.32  | 1.42 | 1.53  | V     |

| With ENAC=0                                      | DCIV=XX                                                       | 0.20  | 0.26 | 0.30  | V     |

| DC Gain                                          | V <sub>DCON</sub> <v<sub>DCI&lt;0.4V+V<sub>DCON</sub></v<sub> | -0.30 | 0.0  | +0.25 | dB    |

| I <sub>DCI</sub> before ILIM                     | ILM=1 V <sub>DCI</sub> =0.28V+V <sub>DCON</sub>               | _     | _    | 10    | μΑ    |

| I <sub>DCI</sub> after ILIM                      | ILM=1 V <sub>DCI</sub> =0.44V+V <sub>DCON</sub>               | 20    | _    | _     | μΑ    |

| Delta V <sub>DCS</sub><br>Delta I <sub>DCI</sub> | 8.2*45mA< V <sub>DCS</sub> < 8.2*60mA                         | _     | 0.85 | _     | mA/V  |

| *Noise                                           | At the line with 300 Ω(ac) (0.15 - 4.0 kHz)                   | _     | -85  | -80   | dBm   |

Table 18: Maximum DC Transmit Levels

## 3.8 Transmit Path

Table 19 list the transmit path characteristics. A pattern for a sinusoid of 1 kHz, full scale (code word of +/- 32,767) from the 73M1x66B is forced and ACS is measured with R10=174  $\Omega$ . Unless stated otherwise, test conditions are: ACZ=0000 (600  $\Omega$  termination), THEN=1, ATEN=1, DAA=01, TXBST=0, sample rate=8kHz.

**Table 19: Transmit Path**

| Parameter                                            | Test Condition                                 | Min    | Nom   | Max    | Units |

|------------------------------------------------------|------------------------------------------------|--------|-------|--------|-------|

| Offset voltage<br>8 and 16 kHz sample rate           | 50% 1's density relative to 1.4 V common mode. | _      | 25    | _      | mV    |

| Tx gain, relative to                                 | DAA=00                                         | 2.5    | +3    | 3.5    | dB    |

| DAA[1:0]=01                                          | DAA=01                                         | -0.5   | 0     | 0.5    | dB    |

|                                                      | DAA=10                                         | -4.5   | -4    | -3.5   | dB    |

|                                                      | DAA=11                                         | -8.5   | -8    | -7.5   | dB    |

| AC swing                                             | DAA=01                                         | _      | 0.317 | -      | Vpk   |

| (1 kHz sinusoid)                                     | DAA=00                                         | _      | 0.447 | -      | Vpk   |

| 8 and 16 kHz sample rate                             | TXBST=1, DAA=xx                                | _      | 0.634 | -      | Vpk   |

|                                                      | ACZ=0001                                       | _      | 0.211 | _      | Vpk   |

|                                                      | ACZ=0010                                       | _      | 0.211 | _      | Vpk   |

|                                                      | ACZ=0011                                       | _      | 0.200 | -      | Vpk   |

|                                                      | ACZ=0100                                       | _      | 0.254 | _      | Vpk   |

|                                                      | ACZ=0101                                       | -      | 0.220 | -      | Vpk   |

|                                                      | ACZ=0110                                       | _      | 0.171 | -      | Vpk   |

|                                                      | ACZ=0111                                       | -      | 0.194 | -      | Vpk   |

|                                                      | ACZ=1000                                       | _      | 0.222 | -      | Vpk   |

|                                                      | ACZ=1001                                       | _      | 0.205 | -      | Vpk   |

|                                                      | ACZ=1010                                       | _      | 0.223 | -      | Vpk   |

|                                                      | ACZ=1011                                       | _      | 0.313 | _      | Vpk   |

|                                                      | ACZ=1100                                       | _      | 0.208 | _      | Vpk   |

|                                                      | ACZ=1101                                       | _      | 0.211 | _      | Vpk   |

|                                                      | ACZ=1110                                       | _      | 0.285 | _      | Vpk   |

|                                                      | ACZ=1111                                       | _      | 0.235 | _      | Vpk   |

| Idle noise                                           | 300 Hz – 4 kHz                                 | _      | -80   | _      | dBm   |

| THD                                                  | 300 Hz – 4 kHz                                 | _      | -80   | _      | dB    |

| Intermod distortion<br>1.0 kHz and 1.2 kHz<br>summed | 300 Hz – 4 kHz                                 | -      | -85   | -      | dB    |

| Passband ripple                                      | 150 Hz – 3.3 kHz                               | -0.125 | _     | +0.125 | dB    |

|                                                      | Gain relative to 1 kHz                         | _      | _     | _      | dB    |

|                                                      | 0.5 kHz                                        | _      | 0.17  | -      | dB    |

|                                                      | 1.0 kHz                                        | _      | 0     | _      | dB    |

|                                                      | 2.0 kHz                                        | _      | 0.193 | _      | dB    |

|                                                      | 3.3 kHz                                        | _      | -0.12 | _      | dB    |

| Aliased image                                        | Fs +/- 1 kHz, relative to 1 kHz                | _      | -75   | _      | dB    |

## 3.9 Receive Path

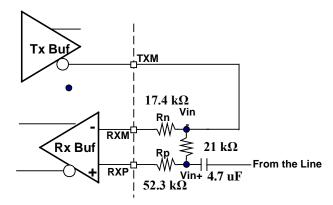

Table 20 lists the receive path characteristics. All test inputs are driven through an AC coupling network shown in Figure 29. The receive bit stream is measured at the DX pin. RXEN=1.

Table 20: Receive Path

| Parameter                                                                | Test Condition                                                                                   | Min   | Nom  | Max    | Units  |

|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------|------|--------|--------|

| Differential input resistance                                            | RXP/RXM                                                                                          | _     | 1000 | _      | kΩ     |

| Input level                                                              | Differential, RXP/RXM                                                                            | -     | 1.1  | 1.16   | Vpk    |

| Input level                                                              | Common mode, RXP/RXM                                                                             | -     | 1.37 | _      | V      |

| Overall sigma-delta ADC modulation gain inclusive of 73M1906B processing | Normalized to VBG=1.19 V. RXG=00 Divide Vrxp/m by PCM Output                                     | _     | 47.3 | -      | μV/bit |

| Offset voltage                                                           | R6=17.4 kΩ, R8=52.3 kΩ, R9=21 kΩ. See Figure 12.                                                 | _     | 0    | +/- 30 | mV     |

| Rx gain                                                                  | RXG=00                                                                                           | -0.5  | 0    | 0.5    | dB     |

| (See Note 1.)                                                            | RXG=01                                                                                           | 2.5   | 3    | 3.5    | dB     |

|                                                                          | RXG=10                                                                                           | 5.5   | 6    | 6.5    | dB     |

|                                                                          | RXG=11                                                                                           | 8.5   | 9    | 9.5    | dB     |

|                                                                          | RXBST=1, RXG=00                                                                                  | 18.3  | 19.3 | 20.3   | dB     |

| Overall receive                                                          | Relative to 1 kHz                                                                                | _     | _    | _      | _      |

| frequency response                                                       | 0.3 kHz – 3.3 kHz                                                                                | -0.25 | 0    | +0.25  | dB     |

| inclusive of 73M1906B processing                                         | Fs (8 kHz)                                                                                       | _     | -75  | _      | dB     |

| Idle noise                                                               | 300 Hz – 4 kHz                                                                                   | _     | -80  | _      | dBm    |

| THD                                                                      | RXG=00                                                                                           | _     | -85  | _      | dB     |

|                                                                          | RXBST=1                                                                                          | _     | -60  | _      |        |

| Intermod Dist 1.0 kHz and 1.2 kHz summed                                 | 300 Hz – 4 kHz                                                                                   | _     | -85  | _      | dB     |

| Crosstalk                                                                | 1 Vpk 1 kHz sine wave at TXP; FFT on Rx ADC samples, first four harmonics reflected to the line. | _     | -90  | _      | dBm    |

| CMRR                                                                     | RXP=RXM 1 Vpk                                                                                    | 40    | _    | _      | dB     |

| PSRR                                                                     | -30 dBm signal at VPX in<br>Barrier Powered Mode;<br>300 Hz – 30 kHz.                            | _     | _    | 40*    | dB     |

| On-Hook AC Impedance                                                     | 300 Hz – 4 kHz, without EMI caps.                                                                | _     | 2    | _      | ΜΩ     |

Note 1: RXG controls the amount of gain or attenuation of the receiver analog gain element as specified in Table 20. The overall receiver channel gain has 6 dB of attenuation and the net effect of the RXG bits on the receiver channel gain is defined in Table 36.

# 3.10 Transmit Hybrid Cancellation

Table 21 lists the transmit hybrid cancellation characteristics. Unless stated otherwise, test conditions are: ACZ[3:0]=0000 (600  $\Omega$  termination), THEN=1, ATEN=1, DAA[1:0]=01, TXBST=0. TXM is externally fed back into the 73M1916 to effect cancellation of transmit signal.

**Table 21: Transmit Hybrid Cancellation Characteristics**

| Parameter                    | Test Condition         | Min  | Nom  | Max  | Units |

|------------------------------|------------------------|------|------|------|-------|

| Transmit hybrid cancellation | Measure in<br>73M1906B | _    | 20   | _    | dB    |

| Offset voltage               | 50% 1's density        | -    | 0    | 25   | mV    |

| AC swing                     | 1 kHz sinusoid         | 1.00 | 1.05 | 1.10 | Vpk   |

| Idle noise                   | 300 Hz – 4 kHz         | _    | -80  | _    | dBm   |

#### 3.11 Receive Notch Filter

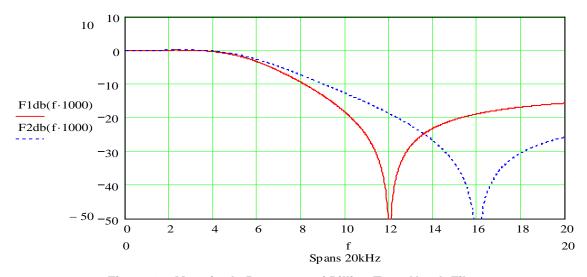

Table 22 lists the receive notch filter characteristics. All measurements taken with RLPNEN=1, TXEN=0, RXG=00, ATEN=1. RXP is driven with 1 Vpk signal.

**Table 22: Receive Notch Filter**

| Parameter           | Test Condition                      | Min | Nom      | Max | Unit |  |  |

|---------------------|-------------------------------------|-----|----------|-----|------|--|--|

|                     | RLPNH=0 (12 kHz Notch)              |     |          |     |      |  |  |

|                     | 300 Hz                              | _   | 0.0      | _   | dB   |  |  |

| Magnitude veen enee | 1 kHz                               | -   | +0.03    | _   | dB   |  |  |

| Magnitude response  | 3 kHz                               | -   | +0.04    | _   | dB   |  |  |

|                     | 12 kHz                              | -30 | -50      | _   | dB   |  |  |

|                     | Passband Ripple (0.3 kHz – 3.4 kHz) | 1   | +/- 0.15 | _   | dB   |  |  |

|                     |                                     | 1   | 28.8     | _   | μs   |  |  |

|                     | 300 Hz                              | _   | 28.93    | _   | μs   |  |  |

| Delay               | 1 kHz                               | _   | 30.25    | _   | μs   |  |  |

|                     | 3 kHz                               | -   | 41.62    | _   | μs   |  |  |

|                     | 12 kHz                              | _   | 9.95     | _   | μs   |  |  |

|                     | RLPNH=1 (16 kHz Notch)              |     |          |     |      |  |  |

|                     | 300 Hz                              | _   | 0.0      | _   | dB   |  |  |

| Manusituda nagarana | 1 kHz                               | -   | +0.04    | -   | dB   |  |  |

| Magnitude response  | 3 kHz                               | -   | +0.11    | _   | dB   |  |  |

|                     | 16 kHz                              | -30 | -50      | _   | dB   |  |  |

|                     | Passband Ripple (0.3 kHz – 3.4 kHz) | _   | +/- 0.15 | _   | dB   |  |  |

|                     |                                     | _   | 30.53    | _   | μs   |  |  |

| Delay               | 300 Hz                              | -   | 30.66    | _   | μs   |  |  |

|                     | 1 kHz                               | -   | 31.93    | _   | μs   |  |  |

|                     | 3 kHz                               | _   | 42.26    | _   | μs   |  |  |

|                     | 16 kHz                              | _   | 4.74     | _   | μs   |  |  |

#### 3.12 Detectors

This section provides electrical characteristics for the following detectors:

- Over-Voltage.

- Over-Current.

- Under-Voltage.

- Over-Load.

## 3.12.1 Over-Voltage Detector

The values in Table 23 were measured between RGP and RGN.

**Table 23: Over-voltage Detector**

| Parameter           | Test Condition | Min  | Nom | Max  | Unit |

|---------------------|----------------|------|-----|------|------|

| Over voltage levels | OVDTH=0        | 0.52 | 0.6 | 0.68 | V    |

|                     | OVDTH=1        | 0.59 | 0.7 | 0.77 | V    |

#### 3.12.2 Over-Current Detector

The values in Table 24 were measured in Barrier Powered Mode.

**Table 24: Over-current Detector**

| Parameter          | Test Condition   | Min  | Nom   | Max  | Unit |

|--------------------|------------------|------|-------|------|------|

| Over current level | Measured at DCS. | 0.90 | 1.025 | 1.20 | ٧    |

## 3.12.3 Under-Voltage Detector

The values in Table 25 were measured in Barrier Powered Mode. In the recommended schematic (see Figure 12), disconnect Q5 collector and connect to an external power supply, VPE, through a 600  $\Omega$  resistor.

Table 25: Under-voltage Detector

| Parameter            | Test Condition                                        | Min | Nom | Max | Unit |

|----------------------|-------------------------------------------------------|-----|-----|-----|------|

| Under voltage detect | Measure VPE when UVD is detected as VPE is decreased. | _   | 7.5 | _   | V    |

#### 3.12.4 Over-Load Detector

The values in Table 26 were measured in Barrier Powered Mode.

**Table 26: Over-load Detector**

| Parameter       | Test Condition              | Min | Nom  | Max | Unit |

|-----------------|-----------------------------|-----|------|-----|------|

| Over load level | Measured at DCI with 1 kHz. | 0.6 | 0.75 | 0.9 | Vpk  |

73M1866B/73M1966B Data Sheet DS\_1x66B\_001

# 4 Applications Information

This section provides general usage information for the design and implementation of the 73M1x66B.

## 4.1 Example Schematic of the 73M1966B and 73M1866B

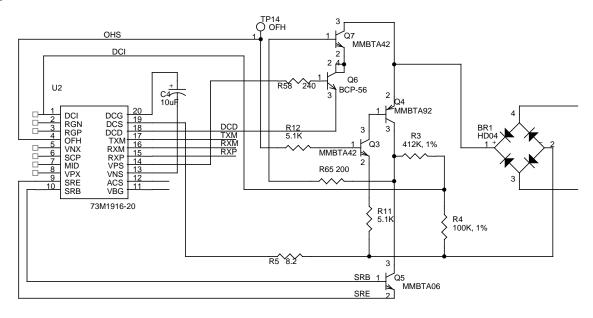

Figure 12 shows a typical application schematic for the implementation of the 73M1966B. Figure 13 shows a typical application schematic for the implementation of the 73M1866B. Note that minor changes may occur to the reference material from time to time and the reader is encouraged to contact Teridian for the latest information. For more information about schematic and layout design, see the 73M1866B/73M1966B Schematic and Layout Guidelines.

Figure 12: Recommended Circuit for the 73M1966B

DS\_1x66B\_001 73M1866B/73M1966B Data Sheet

Figure 13: Recommended Circuit for the 73M1866B

## 4.2 Bill of Materials

Table 27 provides the 73M1x66 bill of materials for the reference schematics provided in Figure 12 and Figure 13.

Table 27: Reference Bill of Materials for 73M1x66B

| Qty | Reference                  | Part Description                    | Source                                 | Example MFR P/N  |  |

|-----|----------------------------|-------------------------------------|----------------------------------------|------------------|--|

| 1   | BR1                        | HD04 rectifier bridge, 0.8A, 400V   | Diodes Inc.                            | HD04-T           |  |

| 2   | C1, C3                     | 0.022µF 200V, X7R, 1206             | Panasonic                              | ECJ-3FB2D223K    |  |

| 1   | C4                         | 10μF 6.3V, tantalum, 0805           | AVX, Panasonic                         | TCP0J106M8RA     |  |

| 1   | C7                         | 4.7μF 25V, X5R, 0805                | AVX, Panasonic                         | 08053D475KAT2A   |  |

| 1   | C8                         | 4.7uF 6.3V, tantalum, 0805          | Rohm                                   | TCP0J475M8R      |  |

| 2   | C9, C10                    | 0.22µF 16V, X7R, ceramic, 0603      | Panasonic                              | C0603C224K8RACTU |  |

| 4   | C12,C17,C31,<br>C38, C48   | 0.1µF 16V, X7R, ceramic, 0603       | Panasonic, Kemet                       | C0603C104K8RACTU |  |

| 2   | C13, C14                   | 15pF 50V, ceramic, 0603             | Panasonic                              | ECJ-1VC1H150J    |  |

| 5   | C20, C26, C30,<br>C33, C43 | 1nF 10V, X7R, ceramic, 0603         | Panasonic                              | C0603C102K8RACTU |  |

| 2   | C21, C45                   | 3.3µF 6.3V, tantalum, 0805          | Rohm                                   | TCP0J335M8R      |  |

| 1   | C37                        | 0.01µF 50V, X7R, ceramic, 0603      | AVX, Panasonic                         | 06035C103KAT2A   |  |

| 1   | C39                        | 5.6nF 50V, X7R, ±10% ceramic, 0603  | Panasonic                              | ECJ-1VB1H562K    |  |

| 1   | C49                        | 100pF 50V, ceramic, 0603            | Taiyo Yuden                            | UMK107CH101JZ-T  |  |

| 1   | D1                         | 25V, 500mW Zener diode              | ON Semi                                | MMSZ4710T1,      |  |

| 1   | Q5                         | MMBTA06, NPN 80 V transistor SOT23  | Diodes, Fairchild,<br>Central, On Semi | MMBTA06LT1G      |  |

| 1   | Q4                         | MMBTA92, PNP 300 V transistor SOT23 | Diodes, Fairchild,<br>Central, On Semi | MMBTA92LT1G      |  |

| 2   | Q3, Q7                     | MMBTA42, NPN 300 V transistor SOT23 | Diodes, Fairchild,<br>Central, On Semi | MMBTA42LT1G      |  |

| 1   | Q6                         | NPN 80 V transistor SOT223          | Fairchild, On Semi                     | BCP56            |  |

| 1   | R2                         | 10M, 5%, 1/8W resistor 0805         | Yageo                                  | RC0805JR-0710ML  |  |

| 1   | R3                         | 412K, 1%, 1/10W resistor 0603       | Yageo                                  | RC0603FR-07412KL |  |

| 1   | R4                         | 100K, 1%, 1/10W resistor 0603       | Yageo                                  | RC0603FR-07100KL |  |

| 1   | R5                         | 8.2, 5%, 1/8W resistor 0805         | Yageo                                  | RC0805JR-078R2L  |  |

| 1   | R6                         | 17.4K, 1%, 1/10W resistor 0603      | Yageo                                  | RC0603FR-0717K4L |  |

| 1   | R8                         | 52.3K, 1%, 1/10W resistor 0603      | Yageo                                  | RC0603FR-0752K3L |  |

| 1   | R9                         | 21K, 1%, 1/10W resistor 0603        | Yageo                                  | RC0603FR-0721KL  |  |

| 1   | R10                        | 174, 1%, 1/10W resistor 0603        | Yageo                                  | RC0603FR-07174RL |  |

| 1   | R11                        | 3K, 5%, 1/10W resistor 0603         | Yageo                                  | RC0603JR-073K0L  |  |