#### **General Description**

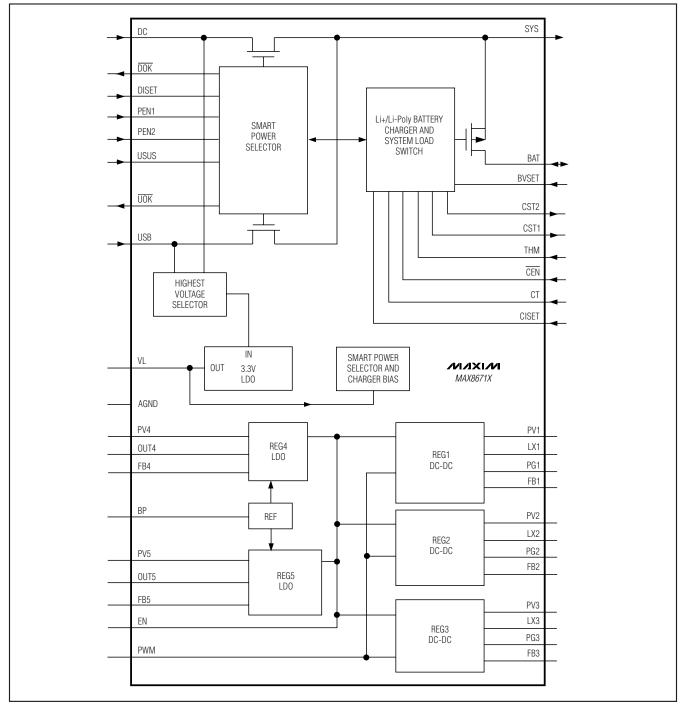

The MAX8671X integrated power-management IC (PMIC) is ideal for use in portable media players and other handheld devices. In addition to five regulated output voltages, the MAX8671X integrates a 1-cell lithium ion (Li+) or lithium polymer (Li-Poly) charger and Smart Power Selector<sup>™</sup> with dual (AC-to-DC adapter and USB) power inputs. The dual-input Smart Power Selector supports end products with dual or single power connectors. All power switches for charging and switching the system load between battery and external power are included on-chip. No external MOSFETs are required.

Maxim's Smart Power Selector makes the best use of limited USB or AC-to-DC adapter power. Battery charge current and input current limit are independently set. Input power not used by the system charges the battery. Charge current and DC current limit are programmable up to 1A while USB input current can be set to 100mA or 500mA. Automatic input selection switches the system load from battery to external power. Other features include overvoltage protection, charge status and fault outputs, power-OK monitors, charge timer, and battery thermistor monitor. In addition, on-chip thermal limiting reduces battery charge rate to prevent charger overheating.

The MAX8671X offers adjustable voltages for all outputs. Similar parts with factory-preset output voltages are also available (contact factory for availability).

#### **Applications**

Portable Audio Players GPS Portable Navigators

#### \_Features

- ♦ 16V-Tolerant USB and DC Inputs

- Automatically Powers from External Power or Battery

- Operates with No Battery Present

- Single-Cell Li+/Li-Poly Charger

- Three 2MHz Step-Down Regulators Up to 96% Efficiency

- Two Low IQ Linear Regulators

- Output Power-Up Sequencing

- Thermal-Overload Protection

#### **Ordering Information**

| PART         | TEMP RANGE     | PIN-PACKAGE                  | PKG<br>CODE |

|--------------|----------------|------------------------------|-------------|

| MAX8671XETL+ | -40°C to +85°C | 40 Thin QFN-EP*<br>5mm x 5mm | T4055-1     |

Simplified Applications Circuit

\*EP = Exposed paddle.

#### *Μ*ΛΧΙ*Ν*Ι MAX8671X DC SYS AC-TO-DC ADAPTER USB USB Li+/LiPo BATTERY ON ΕN OFF OUT1 1V TO V<sub>SYS</sub> OUT1 PWM 425mA OUT2 OUT2 1V TO Vsys PFN1 425mA PEN2 USUS OUT3 CEN 1V TO V<sub>SYS</sub> OUT3 Т 425mA μΡ -OUT4 CST1 0.6V TO V<sub>SYS</sub> OUT4 CST2 180mA DOK UOK \_ OUT5 OUT5 0.6V TO V<sub>SYS</sub> Т 180mA -

Smart Power Selector is a trademark of Maxim Integrated Products, Inc.

#### M/IXI/M

\_ Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

<sup>+</sup>Denotes a lead-free package.

**Table of Contents**

| General Description                              | 1    |

|--------------------------------------------------|------|

| Applications                                     |      |

| Features                                         | 1    |

| Ordering Information                             |      |

| Simplified Applications Circuit                  | 1    |

| Table of Contents                                | 2    |

| Absolute Maximum Ratings                         | 4    |

| Electrical Characteristics                       |      |

| Typical Operating Characteristics                |      |

| Pin Description                                  |      |

| Detailed Description                             |      |

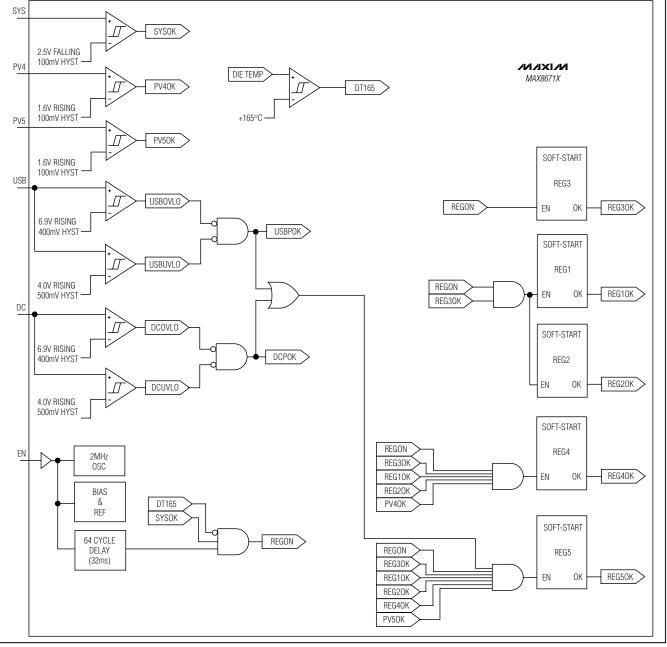

| Smart Power Selector                             | . 24 |

| System Load Switch                               |      |

| USB Power Input (USB)                            | . 25 |

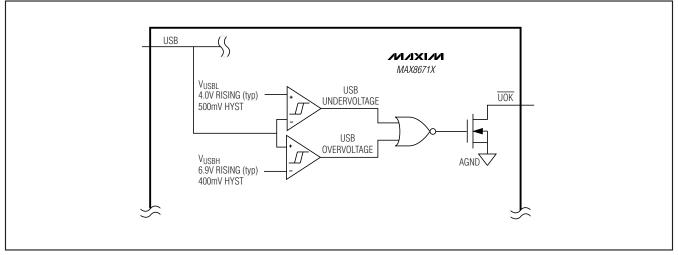

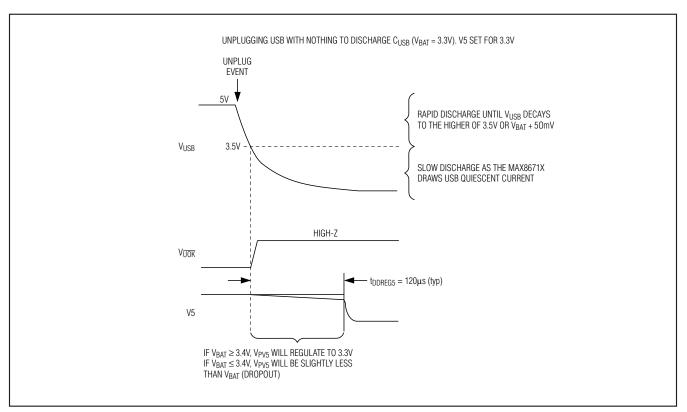

| USB Power-OK Output (UOK)                        | . 26 |

| USB Suspend (USUS)                               | . 26 |

| DC Power Input (DC)                              | . 26 |

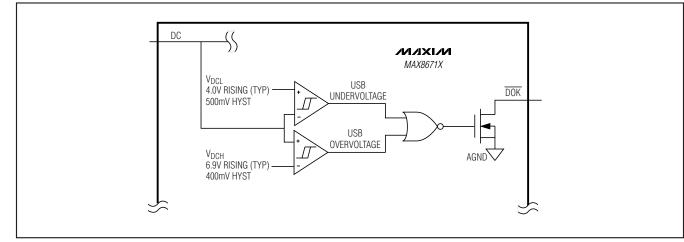

| DC Power-OK Output (DOK)                         | . 27 |

| Battery Charger                                  | . 28 |

| Battery Regulation Voltage (BVSET)               | . 28 |

| Charge Enable Input (CEN)                        |      |

| Charge Status Outputs (CST1, CST2)               | . 30 |

| Charge Timer (CT)                                | . 31 |

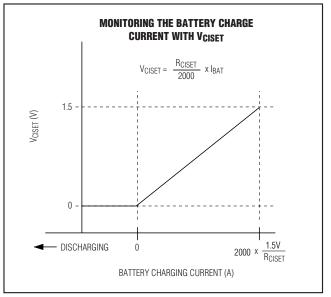

| Setting The Charger Currents (CISET)             | .31  |

| Step-Down Converters (REG1, REG2, REG3)          | . 32 |

| PWM                                              |      |

| Step-Down Dropout and Minimum Duty Cycle         | . 33 |

| Step-Down Input Capacitors                       |      |

| Step-Down Output Capacitors                      | . 33 |

| Step-Down Inductor                               |      |

| Step-Down Converter Output Current               |      |

| Linear Regulators (REG4, REG5)                   |      |

| VL Linear Regulator                              |      |

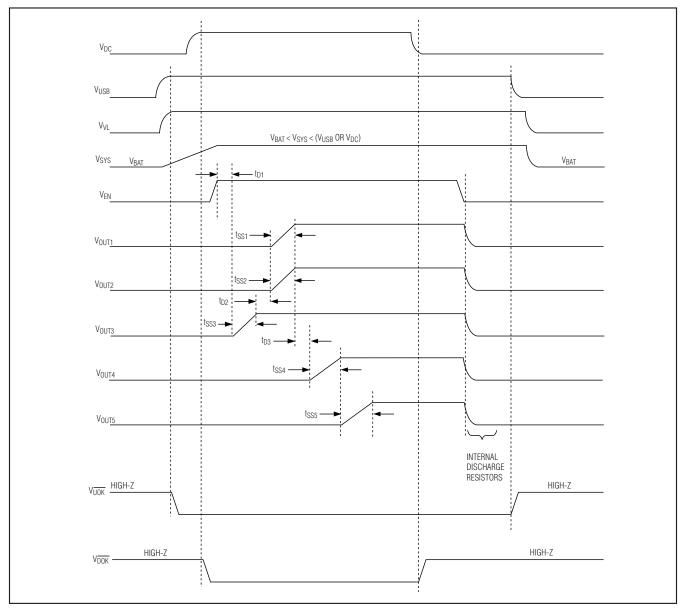

| Enable/Disable (EN) and Sequencing               |      |

| Soft-Start/Inrush Current                        |      |

| Active Discharge in Shutdown                     |      |

| Undervoltage and Overvoltage Lockout             |      |

|                                                  | . 38 |

| USB/DC OVLO                                      |      |

| SYS UVLO                                         |      |

| REG4/REG5 UVLO                                   |      |

| Thermal Limiting and Overload Protection         |      |

| Smart Power Selector Thermal-Overload Protection |      |

| Regulator Thermal-Overload Shutdown              |      |

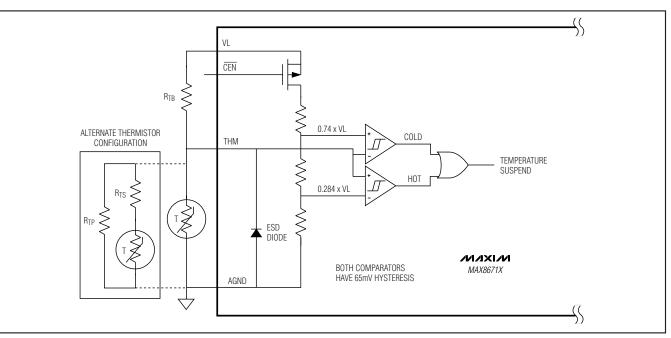

| Battery Charger Thermistor Input (THM)           |      |

| PCB Layout and Routing                           |      |

| Package Marking                                  |      |

| Chip Information                                 |      |

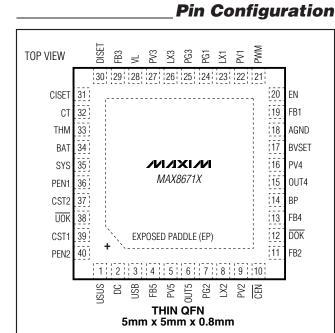

| Pin Configuration                                |      |

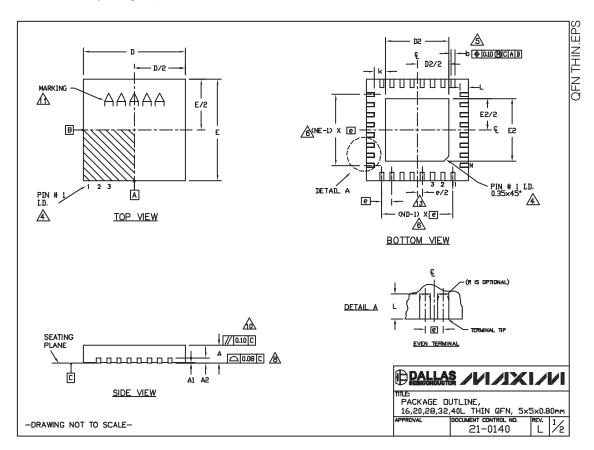

| Package Information                              |      |

| -                                                |      |

## \_Table of Contents (continued)

| Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

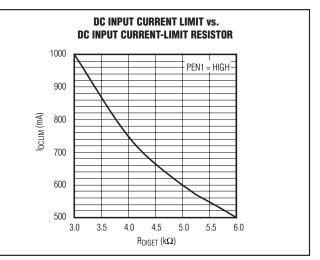

| Table 1. Input Limiter Control LogicTable 2. DC Current Limit for Standard Values of RDISETTable 3. Charge Status OutputsTable 4. Charge Times vs. CCTTable 5. Ideal Charge Currents vs. Charge Setting ResistorTable 6. Suggested InductorsTable 7. 5mm x 5mm x 0.8mm Thin QFN Thermal CharacteristicsTable 8. Trip Temperatures for Different Thermistors                                                                                                                                                                                              |  |

| Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

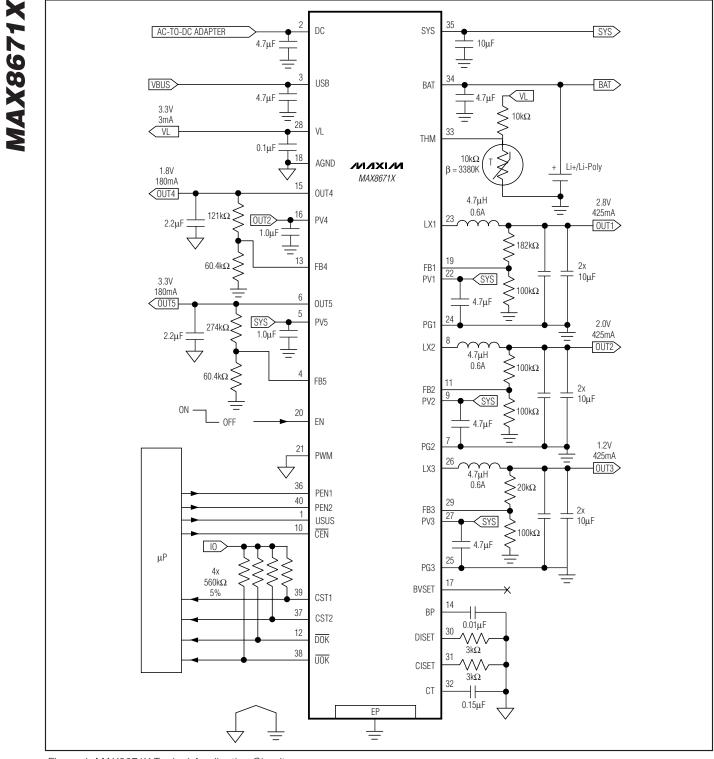

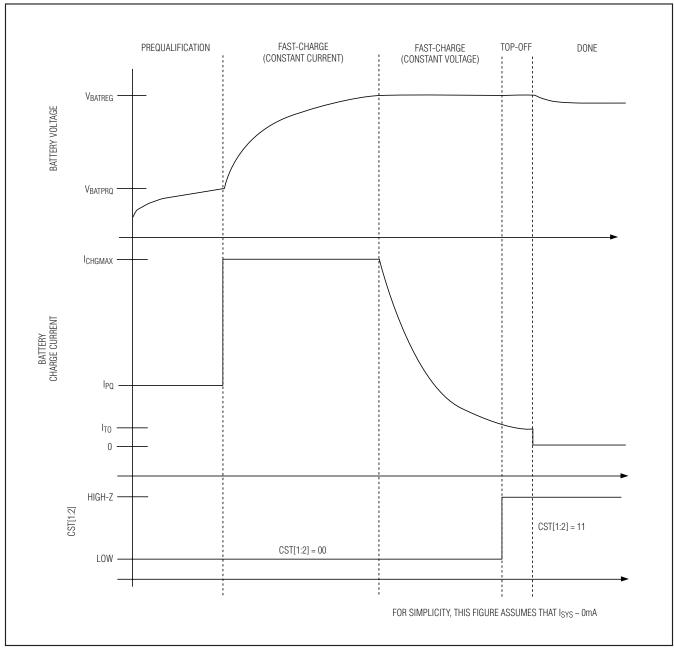

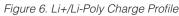

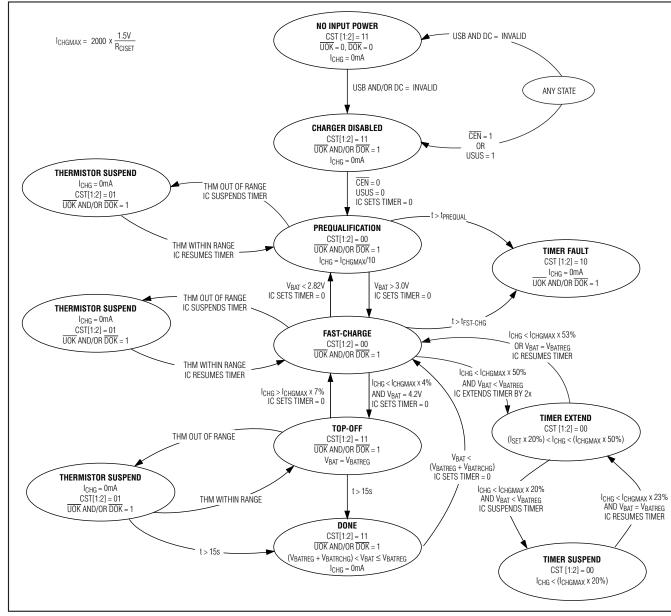

| Figure 1. MAX8671X Typical Application CircuitFigure 2. Functional DiagramFigure 3. USB Power-OK LogicFigure 4. Programming DC Current LimitFigure 5. DC Power-OK LogicFigure 6. Li+/Li-Poly Charge ProfileFigure 7. Charger State DiagramFigure 8. Programming Charge CurrentFigure 9. Monitoring the Battery Charge Current with the Voltage from CISET to AGNDFigure 10. Step-Down Converter Maximum Output Current ExampleFigure 11. Enable/Disable LogicFigure 13. REG5 Disable DetailFigure 14. Thermistor InputFigure 15. Package Marking Example |  |

#### **ABSOLUTE MAXIMUM RATINGS**

| USB, DC, PEN1 to AGND                | 0.3V to +16V                      |

|--------------------------------------|-----------------------------------|

| SYS, BAT, PV1, PV2, PV3 to AGND      | 0.3V to +6V                       |

| PG1, PG2, PG3, AGND                  | 0.3V to +0.3V                     |

| PV1, PV2, PV3 to SYS                 | 0.3V to +0.3V                     |

| VL to AGND                           |                                   |

| CISET, DISET, BVSET, CT, THM to AGND | -0.3V to (V <sub>VL</sub> + 0.3V) |

| PV4, PV5, BP, FB1, FB2, FB3 to AGND  | 0.3V to (V <sub>SYS</sub> + 0.3V) |

| PEN2, USUS, CEN, EN, PWM to AGND     |                                   |

| CST1, CST2, DOK, UOK to AGND         | 0.3V to +6V                       |

| OUT4, FB4 to AGND                    | 0.3V to (V <sub>PV4</sub> + 0.3V) |

| OUT5, FB5 to AGND0.3V to (V <sub>PV5</sub> + 0.3V)    |

|-------------------------------------------------------|

| LX1, LX2, LX3 Continuous RMS Current (Note 1)1.5A     |

| BAT Continuous Current                                |

| SYS Continuous Current1.5A                            |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |

| 40-Pin, 5mm x 5mm, Thin QFN (derate 35.7mW/°C         |

| above +70°C)                                          |

| Operating Junction Temperature+150°C                  |

| Storage Junction Temperature Range65°C to +150°C      |

| Lead Temperature (soldering, 10s)+300°C               |

M/IXI/M

Note 1: LX\_ has internal clamp diodes to PG\_ and PV\_. Applications that forward bias these diodes must take care not to exceed the package power dissipation limits.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(DC, USB, BVSET,  $\overline{\text{UOK}}$ ,  $\overline{\text{DOK}}$ , LX\_ unconnected;  $V_{THM} = V_L/2$ ,  $V_{PG_-} = V_{AGND} = 0V$ ,  $V_{BAT} = 4V$ ,  $\overline{\text{CEN}} = \text{low}$ , USUS = low, EN = high,  $V_{PEN1} = V_{PEN2} = 3.3V$ ,  $V_{PWM} = 0V$ ,  $C_{OUT4} = 1\mu$ F,  $C_{OUT5} = 1\mu$ F,  $C_{SYS} = 10\mu$ F, PV1 = PV2 = PV3 = PV4 = PV5 = SYS,  $R_{DISET} = 3k\Omega$ ,  $R_{CISET} = 3k\Omega$ ,  $C_{VL} = 0.1\mu$ F,  $C_{CT} = 0.15\mu$ F,  $C_{BP} = 0.01\mu$ F,  $V_{FB1} = 1.1V$ ,  $V_{FB2} = 1.1V$ ,  $V_{FB3} = 1.1V$ ,  $T_A = -40^{\circ}$ C to  $+85^{\circ}$ C, unless otherwise noted.) (Note 2)

| PARAMETER                               | SYMBOL           | COND                                                                                                                     | ITIONS                                                | MIN  | ТҮР   | MAX   | UNITS |

|-----------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------|-------|-------|-------|

| DC POWER INPUT (V <sub>DC</sub> = 5.0V, | EN = low)        |                                                                                                                          |                                                       |      |       |       |       |

|                                         |                  | Operating voltage                                                                                                        |                                                       | 4.1  |       | 6.6   |       |

| DC Voltage Range                        | VDC              | Withstand voltage                                                                                                        |                                                       | 0    |       | 14    | V     |

| SYS Regulation Voltage                  | VSYS_REG         | $V_{DC} = 6V$ , USUS = low<br>current is less than the                                                                   | w, <u>CEN</u> = high, system<br>e input current limit | 5.2  | 5.3   | 5.4   | V     |

| DC Undervoltage Threshold               | V <sub>DCL</sub> | V <sub>DC</sub> rising, 500mV typ                                                                                        | oical hysteresis                                      | 3.95 | 4.00  | 4.05  | V     |

| DC Overvoltage Threshold                | VDCH             | V <sub>DC</sub> rising, 400mV typ                                                                                        | oical hysteresis                                      | 6.8  | 6.9   | 7.0   | V     |

| DC Current Limit                        |                  | $V_{DC} = 6V$ , $V_{SYS} = 5V$<br>USB unconnected,<br>$\overline{CEN} = low$ ,<br>$T_A = +25^{\circ}C$ ,<br>VL = no load | PEN1 = low,<br>PEN2 = low,<br>USUS = low              | 90   | 95    | 100   |       |

|                                         | IDCLIM           |                                                                                                                          | PEN1 = low,<br>PEN2 = high,<br>USUS = low             | 450  | 475   | 500   | mA    |

|                                         |                  | (Note 3)                                                                                                                 | PEN1 = high,<br>RDISET = 3k $\Omega$                  | 950  | 1000  | 1050  |       |

| RDISET Resistance Range                 |                  |                                                                                                                          |                                                       | 3    |       | 6     | kΩ    |

|                                         |                  | PEN1 = low, USUS = high                                                                                                  |                                                       |      | 0.11  |       |       |

| DC Quiescent Current                    | IDCIQ            | USUS = low, $\overline{CEN}$ = low;<br>I <sub>SYS</sub> = 0mA, I <sub>BAT</sub> = 0mA, EN = low;<br>VL no load           |                                                       |      | 1.1   |       | mA    |

|                                         |                  | USUS = low, $\overline{CEN}$ = high;<br>I <sub>SYS</sub> = 0mA, V <sub>EN</sub> = 0V, VL no load                         |                                                       |      | 0.7   |       |       |

| Minimum DC-to-BAT Voltage<br>Headroom   |                  | V <sub>DC</sub> falling, 200mV hy                                                                                        | steresis                                              | 0    | 15    | 30    | mV    |

| Minimum DC-to-SYS Voltage<br>Headroom   |                  | V <sub>DC</sub> falling, 200mV hysteresis                                                                                |                                                       | 0    | 15    | 30    | mV    |

| DC-to-SYS Dropout Resistance            | R <sub>DS</sub>  | $V_{DC} = 5V, I_{SYS} = 4000$                                                                                            | mA, USUS = low                                        |      | 0.325 | 0.600 | Ω     |

#### **ELECTRICAL CHARACTERISTICS (continued)**

(DC, USB, BVSET,  $\overline{\text{UOK}}$ ,  $\overline{\text{DOK}}$ , LX\_ unconnected; V<sub>THM</sub> = V<sub>L</sub>/2, V<sub>PG</sub> = V<sub>AGND</sub> = 0V, V<sub>BAT</sub> = 4V,  $\overline{\text{CEN}}$  = low, USUS = low, EN = high, V<sub>PEN1</sub> = V<sub>PEN2</sub> = 3.3V, V<sub>PWM</sub> = 0V, C<sub>OUT4</sub> = 1µF, C<sub>OUT5</sub> = 1µF, C<sub>SYS</sub> = 10µF, PV1 = PV2 = PV3 = PV4 = PV5 = SYS, R<sub>DISET</sub> = 3k\Omega, R<sub>CISET</sub> = 3k\Omega, C<sub>VL</sub> = 0.1µF, C<sub>CT</sub> = 0.15µF, C<sub>BP</sub> = 0.01µF, V<sub>FB1</sub> = 1.1V, V<sub>FB2</sub> = 1.1V, V<sub>FB3</sub> = 1.1V, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted.) (Note 2)

| PARAMETER                                 | SYMBOL               | CONDITION                                                                                                        | IS                         | MIN  | ТҮР   | MAX   | UNITS |

|-------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------|----------------------------|------|-------|-------|-------|

|                                           |                      | Starting DC when no USB p                                                                                        | present                    |      | 1.0   |       | ms    |

| DC-to-SYS Soft-Start Time                 | tss-D-s              | Starting DC with USB prese                                                                                       | ent                        |      | 35    |       | μs    |

| DC Thermal-Limit Temperature              |                      | Die temperature at which cu<br>reduced                                                                           | urrent limit is            |      | +100  |       | °C    |

| DC Thermal-Limit Gain                     |                      | Amount of input current red thermal-limit temperature                                                            | uction above               |      | 5     |       | %/°C  |

| USB POWER INPUT (VUSB = 5.0)              | /, EN = low)         |                                                                                                                  |                            |      |       |       |       |

|                                           | 14                   | Operating voltage                                                                                                |                            | 4.1  |       | 6.6   | V     |

| USB Voltage Range                         | VUSB                 | Withstand voltage                                                                                                |                            | 0    |       | 14    | V     |

| SYS Regulation Voltage                    | V <sub>SYS_REG</sub> | $V_{USB} = 6V$ , USUS = low, $\overline{CEN} = high$ ,<br>system current is less than the input current<br>limit |                            | 5.2  | 5.3   | 5.4   | V     |

| USB Undervoltage Threshold                | VUSBL                | V <sub>USB</sub> rising, 500mV hystere                                                                           | sis                        | 3.95 | 4.0   | 4.05  | V     |

| USB Overvoltage Threshold                 | VUSBH                | V <sub>USB</sub> rising, 400mV hystere                                                                           |                            | 6.8  | 6.9   | 7.0   | V     |

| USB Current Limit                         | IUSBLIM              | $V_{USB} = 6V, V_{SYS} = 5V, DC$<br>unconnected, $\overline{CEN} = Iow,$                                         | PEN2 = low,<br>USUS = low  | 90   | 95    | 100   |       |

|                                           |                      | T <sub>A</sub> = +25°C,<br>I <sub>VL</sub> = 0A (Note 3)                                                         | PEN2 = high,<br>USUS = low | 450  | 475   | 500   | mA    |

|                                           |                      | USUS = high                                                                                                      |                            |      | 0.11  |       |       |

| USB Quiescent Current                     | IUSBIQ               | USUS = low, <del>CEN</del> = low;<br>I <sub>SYS</sub> = 0mA, I <sub>BAT</sub> = 0mA, VL no load                  |                            |      | 1.1   | 2.0   | mA    |

|                                           |                      | USUS = low, $\overline{CEN}$ = high;<br>I <sub>SYS</sub> = 0mA, VL no load                                       |                            |      | 0.7   | 1.3   |       |

| Minimum USB-to-BAT Voltage<br>Headroom    |                      | V <sub>USB</sub> falling, 200mV hystere                                                                          | esis                       | 0    | 15    | 30    | mV    |

| Minimum USB-to-SYS Voltage<br>Headroom    |                      | V <sub>USB</sub> falling, 200mV hystere                                                                          | esis                       | 0    | 15    | 30    | mV    |

| USB-to-SYS Dropout Resistance             | R <sub>US</sub>      | V <sub>USB</sub> = 5V, I <sub>SYS</sub> = 400mA, I                                                               | USUS = low                 |      | 0.325 | 0.600 | Ω     |

| USB-to-SYS Soft-Start Time                | tss-u-s              |                                                                                                                  |                            |      | 1.0   |       | ms    |

| USB Thermal-Limit Temperature             |                      | Die temperature at which current limit is reduced                                                                |                            |      | 100   |       | °C    |

| USB Thermal-Limit Gain                    |                      | Amount of input current reduction above thermal-limit temperature                                                |                            |      | 5     |       | %/°C  |

| SYSTEM (V <sub>DC</sub> = 5.0V, EN = low) |                      |                                                                                                                  |                            |      |       |       |       |

| System Operating Voltage Range            | V <sub>SYS</sub>     |                                                                                                                  |                            | 2.6  |       | 5.5   | V     |

| System Undervoltage Threshold             | VUVLO_SYS            | SYS falling, 100mV hysteres                                                                                      | sis                        | 2.45 | 2.50  | 2.55  | V     |

#### **ELECTRICAL CHARACTERISTICS (continued)**

(DC, USB, BVSET,  $\overline{\text{UOK}}$ ,  $\overline{\text{DOK}}$ ,  $LX_{\text{unconnected}}$ ;  $V_{\text{THM}} = V_{\text{L}}/2$ ,  $V_{\text{PG}} = V_{\text{AGND}} = 0V$ ,  $V_{\text{BAT}} = 4V$ ,  $\overline{\text{CEN}} = \text{low}$ , USUS = low, EN = high,  $V_{\text{PEN1}} = V_{\text{PEN2}} = 3.3V$ ,  $V_{\text{PWM}} = 0V$ ,  $C_{\text{OUT4}} = 1\mu\text{F}$ ,  $C_{\text{OUT5}} = 1\mu\text{F}$ ,  $C_{\text{SYS}} = 10\mu\text{F}$ , PV1 = PV2 = PV3 = PV4 = PV5 = SYS,  $\text{R}_{\text{DISET}} = 3k\Omega$ ,  $\text{R}_{\text{CISET}} = 3k\Omega$ ,  $C_{\text{VL}} = 0.1\mu\text{F}$ ,  $C_{\text{BP}} = 0.01\mu\text{F}$ ,  $V_{\text{FB1}} = 1.1V$ ,  $V_{\text{FB2}} = 1.1V$ ,  $V_{\text{FB3}} = 1.1V$ ,  $T_{\text{A}} = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ , unless otherwise noted.) (Note 2)

| PARAMETER                               | SYMBOL                     | COND                                                                                                                           | ITIONS                                        | MIN   | ТҮР   | MAX   | UNITS         |

|-----------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-------|-------|-------|---------------|

| BAT-to-SYS Reverse Regulation           | \/                         | DC or USB and BAT                                                                                                              | BAT is sourcing<br>105mA                      | 65    | 82    | 115   | m)/           |

| Voltage                                 | VBSREG                     | are sourcing current                                                                                                           | BAT is sourcing<br>905mA                      |       | 130   |       | mV            |

|                                         |                            | DC and USB unconner $V_{BAT} = 4V$                                                                                             | ected, EN = low,                              |       | 0     | 10    |               |

|                                         |                            | $V_{DC} = V_{USB} = 5V, US$<br>PEN1 = low, EN = low                                                                            | -                                             |       | 0     | 10    |               |

| Quiescent Current                       | IPV1 +<br>IPV2 +<br>IPV3 + | DC and USB unconne<br>V <sub>BAT</sub> = 4V (step-dowr<br>dropout), PWM = low                                                  | n converters are not in                       |       | 155   | 285   | μA            |

|                                         | IPV4 +<br>IPV5 +<br>ISYS   | DC and USB unconnected, EN = high,<br>$V_{BAT} = 2.8V$ (at least one step-down<br>converter is in dropout), PWM = low (Note 4) |                                               |       | 425   | 550   |               |

|                                         |                            | $V_{DC} = V_{USB} = 5V$ , USUS = high, EN = high,<br>$V_{BAT} = 4V$ , PWM = low (Note 4)                                       |                                               |       | 180   | 320   |               |

|                                         |                            | DC and USB unconner $V_{BAT} = 4.0V$ , PWM = 1                                                                                 | •                                             |       | 9     |       | mA            |

| BATTERY CHARGER (V <sub>DC</sub> = 5.0) | V, EN = low)               | •                                                                                                                              |                                               |       |       |       |               |

| BAT-to-SYS On-Resistance                | R <sub>BS</sub>            | $V_{USB} = 0V, V_{BAT} = 4.2$                                                                                                  | 2V, I <sub>SYS</sub> = 1A                     |       | 0.08  | 0.16  | Ω             |

|                                         |                            | BVSET = VL or                                                                                                                  | $T_A = +25^{\circ}C$                          | 4.174 | 4.200 | 4.221 | -<br>-<br>- V |

|                                         |                            | BVSET unconnected                                                                                                              | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ | 4.145 | 4.200 | 4.242 |               |

| BAT Regulation Voltage                  |                            | BVSET = AGND                                                                                                                   | $T_A = +25^{\circ}C$                          | 4.073 | 4.100 | 4.121 |               |

| (Figure 6)                              | VBATREG                    | BVOLT - ACIND                                                                                                                  | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ | 4.047 | 4.100 | 4.141 |               |

|                                         |                            | $R_{BVSET} = 49.9 k\Omega$ to                                                                                                  | $T_A = +25^{\circ}C$                          | 4.325 | 4.350 | 4.376 |               |

|                                         |                            | AGND                                                                                                                           | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ | 4.297 | 4.350 | 4.398 | ]             |

| BAT Recharge Threshold                  | VBATRCHG                   | (Note 5)                                                                                                                       |                                               | -170  | -120  | -70   | mV            |

| BAT Prequalification Threshold          | VBATPRQ                    | VBAT rising, 180mV hy                                                                                                          | /steresis, Figure 6                           | 2.9   | 3.0   | 3.1   | V             |

| RCISET Resistance Range                 |                            | Guaranteed by BAT fa                                                                                                           | ast-charge current                            | 3     |       | 15    | kΩ            |

| CISET Voltage                           | VCISET                     | $R_{CISET} = 7.5 k\Omega$ , $I_{BAT}$                                                                                          | = 267mA, Figure 9                             | 0.9   | 1.0   | 1.1   | V             |

|                                         | 1                          | 1                                                                                                                              |                                               |       |       |       |               |

MIXIM

#### **ELECTRICAL CHARACTERISTICS (continued)**

(DC, USB, BVSET,  $\overline{\text{UOK}}$ ,  $\overline{\text{DOK}}$ , LX\_ unconnected; V<sub>THM</sub> = V<sub>L</sub>/2, V<sub>PG</sub> = V<sub>AGND</sub> = 0V, V<sub>BAT</sub> = 4V,  $\overline{\text{CEN}}$  = low, USUS = low, EN = high, V<sub>PEN1</sub> = V<sub>PEN2</sub> = 3.3V, V<sub>PWM</sub> = 0V, C<sub>OUT4</sub> = 1µF, C<sub>OUT5</sub> = 1µF, C<sub>SYS</sub> = 10µF, PV1 = PV2 = PV3 = PV4 = PV5 = SYS, R<sub>DISET</sub> = 3k\Omega, R<sub>CISET</sub> = 3k\Omega, C<sub>VL</sub> = 0.1µF, C<sub>CT</sub> = 0.15µF, C<sub>BP</sub> = 0.01µF, V<sub>FB1</sub> = 1.1V, V<sub>FB2</sub> = 1.1V, V<sub>FB3</sub> = 1.1V, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted.) (Note 2)

| PARAMETER                     | SYMBOL  | CO                                                                                                                                                                                                                                        | NDITIONS                                                                                                   | MIN | TYP  | MAX | UNITS |

|-------------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

|                               |         | input, DC unconne<br>PEN2 = low, USUS                                                                                                                                                                                                     | Low-power USB charging from the USB input, DC unconnected, $R_{CISET} = 3k\Omega$ , PEN2 = low, USUS = low |     |      | 100 |       |

|                               |         | Low-power USB cl<br>input, R <sub>CISET</sub> = 3k<br>PEN2 = low, USUS                                                                                                                                                                    |                                                                                                            | 87  | 92   | 100 |       |

|                               |         |                                                                                                                                                                                                                                           | charging from the USB<br>ected, R <sub>CISET</sub> = 3kΩ,<br>IS = Iow                                      | 450 | 472  | 500 |       |

| BAT Fast-Charge Current Limit |         | High-power USB c<br>input, R <sub>CISET</sub> = 3k<br>USUS = low                                                                                                                                                                          | charging from the DC<br>Ω, PEN2 = high,                                                                    | 450 | 472  | 500 | mA    |

|                               |         | AC-to-DC adapter<br>input, R <sub>DISET</sub> = 3k<br>PEN1 = high                                                                                                                                                                         | charging from the DC $\Omega$ , R <sub>CISET</sub> = 15k $\Omega$ ,                                        | 170 | 200  | 230 |       |

|                               |         | AC-to-DC adapter charging from the DC<br>input, $R_{DISET} = 3k\Omega$ , $R_{CISET} = 7.5k\Omega$ ,<br>PEN1 = high<br>AC-to-DC adapter charging from the DC<br>input, $R_{DISET} = 3k\Omega$ , $R_{CISET} = 3.74k\Omega$ ,<br>PEN1 = high |                                                                                                            | 375 | 400  | 425 | -     |

|                               |         |                                                                                                                                                                                                                                           |                                                                                                            | 750 | 802  | 850 |       |

| BAT Prequalification Current  |         | V <sub>BAT</sub> = 2.5V, R <sub>CIS</sub>                                                                                                                                                                                                 | $ET = 3.74 k\Omega$                                                                                        | 65  | 82   | 100 | mA    |

| Top-Off Threshold             |         |                                                                                                                                                                                                                                           | $T = 3.74$ k $\Omega$ (Note 6)                                                                             | 20  | 30   | 40  | mA    |

|                               |         | EN = low,                                                                                                                                                                                                                                 | No DC or USB power connected                                                                               |     | 0    | +5  | μΑ    |

| BAT Leakage Current           |         | $T_A = +25^{\circ}C$                                                                                                                                                                                                                      | DC and/or USB power connected, $\overline{CEN} = high$                                                     | -5  | 1    | +5  |       |

|                               |         | Slew rate                                                                                                                                                                                                                                 |                                                                                                            |     | 450  |     | mA/ms |

| Charger Soft-Start Time       | tss chg | Time from 0mA to                                                                                                                                                                                                                          | 500mA                                                                                                      |     | 1.10 |     |       |

| Sharger Solt Start Time       | 135_CHG | Time from 0mA to                                                                                                                                                                                                                          | 100mA                                                                                                      |     | 0.22 |     | ms    |

|                               |         | Time from 100mA                                                                                                                                                                                                                           | to 500mA                                                                                                   |     | 0.88 |     |       |

| Timer Accuracy                |         | $C_{CT} = 0.15 \mu F$                                                                                                                                                                                                                     |                                                                                                            | -20 |      | +20 | %     |

| Timer Suspend Threshold       |         | CISET voltage whe<br>suspends; 300mV<br>maximum fast-cha                                                                                                                                                                                  | 250                                                                                                        | 300 | 350  | mV  |       |

| Timer Extend Threshold        |         |                                                                                                                                                                                                                                           | en the fast-charge timer<br>translates to 50% of the<br>rge current limit                                  | 700 | 750  | 800 | mV    |

#### **ELECTRICAL CHARACTERISTICS (continued)**

(DC, USB, BVSET,  $\overline{\text{UOK}}$ ,  $\overline{\text{DOK}}$ ,  $LX_{\text{unconnected}}$ ;  $V_{\text{THM}} = V_{\text{L}}/2$ ,  $V_{\text{PG}} = V_{\text{AGND}} = 0V$ ,  $V_{\text{BAT}} = 4V$ ,  $\overline{\text{CEN}} = \text{low}$ , USUS = low, EN = high,  $V_{\text{PEN1}} = V_{\text{PEN2}} = 3.3V$ ,  $V_{\text{PWM}} = 0V$ ,  $C_{\text{OUT4}} = 1\mu\text{F}$ ,  $C_{\text{OUT5}} = 1\mu\text{F}$ ,  $C_{\text{SYS}} = 10\mu\text{F}$ , PV1 = PV2 = PV3 = PV4 = PV5 = SYS,  $\text{R}_{\text{DISET}} = 3k\Omega$ ,  $\text{R}_{\text{CISET}} = 3k\Omega$ ,  $C_{\text{VL}} = 0.1\mu\text{F}$ ,  $C_{\text{BP}} = 0.01\mu\text{F}$ ,  $V_{\text{FB1}} = 1.1V$ ,  $V_{\text{FB2}} = 1.1V$ ,  $V_{\text{FB3}} = 1.1V$ ,  $T_{\text{A}} = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ , unless otherwise noted.) (Note 2)

| PARAMETER                            | SYMBOL            | CONDI                                          | TIONS                  | MIN    | TYP           | MAX    | UNITS                   |

|--------------------------------------|-------------------|------------------------------------------------|------------------------|--------|---------------|--------|-------------------------|

| Prequalification Time                | tpq               | C <sub>CT</sub> = 0.15µF                       |                        |        | 33            |        | min                     |

| Fast-Charge Time                     | tFC               | C <sub>CT</sub> = 0.15µF                       |                        |        | 660           |        | min                     |

| Top-Off Time                         | tто               |                                                |                        |        | 15            |        | S                       |

| THERMISTOR INPUT (THM) (VDC          | = 5.0V, EN =      | = low)                                         |                        | •      |               |        |                         |

| THM Threshold, Cold                  | VTHMC             | V <sub>THM</sub> rising, 65mV hys              | teresis                | 73.0   | 74.0          | 75.5   | % of<br>V <sub>VL</sub> |

| THM Threshold, Hot                   | V <sub>THMH</sub> | V <sub>THM</sub> falling, 65mV hys             | steresis               | 27.0   | 28.4          | 30.0   | % of<br>V <sub>VL</sub> |

| THM Input Leakage Current            | Ітнм              | THM = AGND or VL, T,<br>THM = AGND or VL, T,   |                        | -0.100 | 0.001<br>0.01 | +0.200 | μA                      |

| POWER SEQUENCING (Figures 1          | 1 and 12)         |                                                |                        | •      |               |        |                         |

| EN to REG3 Enable Delay              | tD1               |                                                |                        |        | 120           |        | μs                      |

| REG1 Soft-Start Time                 | tss1              |                                                |                        |        | 2.6           |        | ms                      |

| REG3 to REG1/2 Delay                 | t <sub>D2</sub>   |                                                |                        |        | 0.4           |        | ms                      |

| REG2 Soft-Start Time                 | tss2              |                                                |                        |        | 2.6           |        | ms                      |

| REG3 Soft-Start Time                 | tss3              | 2.6                                            |                        |        | ms            |        |                         |

| REG1/2 to REG4 Delay                 | t <sub>D3</sub>   |                                                |                        |        | 0.3           |        | ms                      |

| REG4 Soft-Start Time                 | tss4              |                                                |                        |        | 3.0           |        | ms                      |

| REG5 Soft-Start Time                 | tss5              | 3.0                                            |                        |        | ms            |        |                         |

| REGULATOR THERMAL SHUTDO             | OWN               | •                                              |                        | •      |               |        |                         |

| Thermal Shutdown Temperature         |                   | T <sub>J</sub> rising                          |                        |        | +165          |        | °C                      |

| Thermal Shutdown Hysteresis          |                   |                                                |                        |        | 15            |        | °C                      |

| REG1—SYNCHRONOUS STEP-D              | OWN CONV          | ERTER                                          |                        | •      |               |        |                         |

| Input Voltage                        |                   | PV1 supplied from SYS                          | 6                      |        | Vsys          |        | V                       |

| Maximum Output Current               |                   | $L = 4.7 \mu H, R_L = 0.13 \Omega$             | (Note 7)               | 425    |               |        | mA                      |

| FB1 Voltage                          |                   | (Note 8)                                       |                        | 0.997  | 1.012         | 1.028  | V                       |

| Adjustable Output Voltage Range      |                   |                                                |                        | 1      |               | VSYS   | V                       |

|                                      |                   |                                                | $T_A = +25^{\circ}C$   | -50    | -5            | +50    |                         |

| FB1 Leakage Current                  |                   | $V_{FB1} = 1.012V$                             | T <sub>A</sub> = +85°C | -5     |               |        | nA                      |

| Load Regulation                      |                   | PWM mode                                       |                        |        | 4.4           |        | %/A                     |

| Line Regulation                      |                   | PWM mode (Note 9)                              |                        |        | 1             |        | %/D                     |

| p-Channel On-Resistance              |                   | $V_{PV1} = 4V, I_{LX1} = 180mA$                |                        |        | 165           | 330    | mΩ                      |

| n-Channel On-Resistance              |                   | V <sub>PV1</sub> = 4V, I <sub>LX1</sub> = 180r |                        |        | 200           | 400    | mΩ                      |

| p-Channel Current-Limit<br>Threshold |                   |                                                |                        | 0.555  | 0.615         | 0.675  | A                       |

#### **ELECTRICAL CHARACTERISTICS (continued)**

(DC, USB, BVSET,  $\overline{\text{UOK}}$ ,  $\overline{\text{DOK}}$ , LX\_ unconnected;  $V_{THM} = V_L/2$ ,  $V_{PG_-} = V_{AGND} = 0V$ ,  $V_{BAT} = 4V$ ,  $\overline{\text{CEN}} = 10w$ , USUS = 10w, EN = high,  $V_{PEN1} = V_{PEN2} = 3.3V$ ,  $V_{PWM} = 0V$ ,  $C_{OUT4} = 1\mu$ F,  $C_{OUT5} = 1\mu$ F,  $C_{SYS} = 10\mu$ F, PV1 = PV2 = PV3 = PV4 = PV5 = SYS,  $R_{DISET} = 3k\Omega$ ,  $R_{CISET} = 3k\Omega$ ,  $C_{VL} = 0.1\mu$ F,  $C_{CT} = 0.15\mu$ F,  $C_{BP} = 0.01\mu$ F,  $V_{FB1} = 1.1V$ ,  $V_{FB2} = 1.1V$ ,  $V_{FB3} = 1.1V$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted.) (Note 2)

| PARAMETER                                 | SYMBOL   | CON                                         | DITIONS                                       | MIN   | TYP       | MAX   | UNITS |

|-------------------------------------------|----------|---------------------------------------------|-----------------------------------------------|-------|-----------|-------|-------|

| Skip Mode Transition Current              |          | (Note 10)                                   |                                               |       | 60        |       | mA    |

| n-Channel Zero-Crossing<br>Threshold      |          |                                             |                                               |       | 10        |       | mA    |

| Maximum Duty Cycle                        |          |                                             |                                               |       | 100       |       | %     |

| Minimum Duty Cycle                        |          | PWM mode                                    |                                               |       | 12.5      |       | %     |

| Internal Oscillator Frequency             |          |                                             |                                               | 1.8   | 2.0       | 2.2   | MHz   |

| Internal Discharge Resistance in Shutdown |          | EN = low, resistance                        | from LX1 to PG1                               | 0.5   | 1.0       | 2.0   | kΩ    |

| REG2—SYNCHRONOUS STEP-D                   | OWN CONV | ERTER                                       |                                               |       |           |       |       |

| Input Voltage                             |          | PV2 supplied from S                         | ŕS                                            |       | Vsys      |       | V     |

| Maximum Output Current                    |          | L = 4.7µH, R <sub>L</sub> = 0.13            | Ω (Note 7)                                    | 425   |           |       | mA    |

| FB2 Voltage                               |          | (Note 8)                                    |                                               | 0.997 | 1.012     | 1.028 | V     |

| Adjustable Output Voltage Range           |          |                                             |                                               | 1     |           | VSYS  | V     |

|                                           |          | 10101/                                      | $T_A = +25^{\circ}C$                          | -50   | -5        | +50   |       |

| FB2 Leakage Current                       |          | $V_{FB2} = 1.012V$                          | T <sub>A</sub> = +85°C                        |       | -50       |       | nA    |

| Load Regulation                           |          | PWM mode                                    |                                               |       | 4.4       |       | %/A   |

| Line Regulation                           |          | PWM mode (Note 9)                           |                                               |       | 1         |       | %/D   |

| p-Channel On-Resistance                   |          | $V_{PV2} = 4V$ , $I_{LX2} = 180mA$          |                                               |       | 200       | 400   | mΩ    |

| n-Channel On-Resistance                   |          | $V_{PV2} = 4V, I_{LX2} = 180mA$             |                                               |       | 150       | 265   | mΩ    |

| p-Channel Current-Limit<br>Threshold      |          |                                             |                                               | 0.555 | 0.615     | 0.675 | А     |

| Skip Mode Transition Current              |          | (Note 10)                                   |                                               |       | 60        |       | mA    |

| n-Channel Zero-Crossing<br>Threshold      |          |                                             |                                               |       | 10        |       | mA    |

| Maximum Duty Cycle                        |          |                                             |                                               |       | 100       |       | %     |

| Minimum Duty Cycle                        |          | PWM mode                                    |                                               |       | 12.5      |       | %     |

| Internal Oscillator Frequency             |          |                                             |                                               | 1.8   | 2.0       | 2.2   | MHz   |

| Internal Discharge Resistance in Shutdown |          | EN = low, resistance                        | from LX2 to PG2                               | 0.5   | 1.0       | 2.0   | kΩ    |

| REG3—SYNCHRONOUS STEP-D                   | OWN CONV | ERTER                                       |                                               | 1     |           |       |       |

| Input Voltage                             |          | PV3 supplied from S                         | ŕS                                            |       | VSYS      |       | V     |

| Maximum Output Current                    |          | $L = 4.7 \mu H, R_L = 0.13 \Omega$ (Note 7) |                                               | 425   |           |       | mA    |

| FB3 Voltage                               |          | (Note 8)                                    |                                               | 0.997 | 1.012     | 1.028 | V     |

| Adjustable Output Voltage Range           |          |                                             |                                               | 1     |           | VSYS  | V     |

| FB3 Leakage Current                       |          | V <sub>FB2</sub> = 1.012V                   | $T_{A} = +25^{\circ}C$ $T_{A} = +85^{\circ}C$ | -50   | -5<br>-50 | +50   | nA    |

| Load Regulation                           |          | PWM mode                                    | · A = 100 0                                   |       | 4.4       |       | %/A   |

|                                           | 1        |                                             |                                               |       |           |       |       |

#### **ELECTRICAL CHARACTERISTICS (continued)**

(DC, USB, BVSET,  $\overline{\text{UOK}}$ ,  $\overline{\text{DOK}}$ , LX\_ unconnected;  $V_{THM} = V_L/2$ ,  $V_{PG_-} = V_{AGND} = 0V$ ,  $V_{BAT} = 4V$ ,  $\overline{\text{CEN}} = 10w$ , USUS = 10w, EN = high,  $V_{PEN1} = V_{PEN2} = 3.3V$ ,  $V_{PWM} = 0V$ ,  $C_{OUT4} = 1\mu$ F,  $C_{OUT5} = 1\mu$ F,  $C_{SYS} = 10\mu$ F, PV1 = PV2 = PV3 = PV4 = PV5 = SYS,  $R_{DISET} = 3k\Omega$ ,  $R_{CISET} = 3k\Omega$ ,  $C_{VL} = 0.1\mu$ F,  $C_{CT} = 0.15\mu$ F,  $C_{BP} = 0.01\mu$ F,  $V_{FB1} = 1.1V$ ,  $V_{FB2} = 1.1V$ ,  $V_{FB3} = 1.1V$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted.) (Note 2)

| PARAMETER                                 | SYMBOL | CONDITIONS                                                                                          |                                | MIN   | ТҮР   | MAX   | UNITS |

|-------------------------------------------|--------|-----------------------------------------------------------------------------------------------------|--------------------------------|-------|-------|-------|-------|

| Line Regulation                           |        | PWM mode (Note 9)                                                                                   |                                | 1     |       | %/D   |       |

| p-Channel Current-Limit<br>Threshold      |        |                                                                                                     |                                | 0.555 | 0.615 | 0.675 | А     |

| Skip Mode Transition Current              |        | (Note 10)                                                                                           |                                |       | 60    |       | mA    |

| n-Channel Zero-Crossing<br>Threshold      |        |                                                                                                     |                                |       | 10    |       | mA    |

| p-Channel On-Resistance                   |        | V <sub>PV3</sub> = 4V, I <sub>LX3</sub> = 180n                                                      | nA                             |       | 230   | 460   | mΩ    |

| n-Channel On-Resistance                   |        | V <sub>PV3</sub> = 4V, I <sub>LX3</sub> = 180n                                                      | nA                             |       | 120   | 210   | mΩ    |

| Maximum Duty Cycle                        |        |                                                                                                     |                                |       | 100   |       | %     |

| Minimum Duty Cycle                        |        | PWM mode                                                                                            |                                |       | 12.5  |       | %     |

| Internal Oscillator Frequency             |        |                                                                                                     |                                | 1.8   | 2.0   | 2.2   | MHz   |

| Internal Discharge Resistance in Shutdown |        | EN = low, resistance from LX3 to PG3                                                                |                                | 0.5   | 1.0   | 2.0   | kΩ    |

| REG4—LINEAR REGULATOR                     | 1      |                                                                                                     |                                | 1     |       |       |       |

| PV4 Operating Range                       | VPV4   |                                                                                                     |                                | 1.7   |       | VSYS  | V     |

| PV4 Undervoltage Lockout<br>Threshold     |        | V <sub>PV4</sub> rising, 100mV hysteresis                                                           |                                | 1.55  | 1.60  | 1.65  | V     |

| FB4 Voltage                               |        | No load                                                                                             |                                | 0.582 | 0.600 | 0.618 | V     |

|                                           |        |                                                                                                     | $T_A = +25^{\circ}C$           | -50   | -5    | +50   |       |

| FB4 Leakage Current                       |        | $V_{FB4} = 0.6V$                                                                                    | T <sub>A</sub> = +85°C         |       | -5    |       | nA    |

|                                           |        | PV4 to OUT4, $V_{PV4} = 3$                                                                          | .3V                            |       | 0.45  |       | 0     |

| Drop-Out Resistance                       |        | PV4 to OUT4, $V_{PV4} = 2$                                                                          | 2.0V                           |       | 0.75  | 1.8   | Ω     |

| Ourrent Limit                             |        | $V_{FB4} = 0.54V$                                                                                   |                                | 200   | 230   | 265   | A     |

| Current Limit                             |        | $V_{FB4} = 0V$                                                                                      |                                |       | 235   |       | mA    |

| Output Noise                              |        | 10Hz to 100kHz;<br>C <sub>OUT4</sub> = 3.3µF, I <sub>OUT4</sub> =<br>V <sub>OUT4</sub> set for 1.8V | = 10mA, V <sub>PV4</sub> = 2V, |       | 120   |       | μVrms |

| DCDD                                      |        | f = 1kHz, $I_{OUT4}$ = 10mA, $V_{PV4}$ = 2V,<br>V <sub>OUT4</sub> set for 1.8V                      |                                |       | 67    |       | dB    |

| PSRR                                      |        | $f = 10kHz$ , $I_{OUT4} = 10n$<br>V <sub>OUT4</sub> set for 1.8V                                    | nA, $V_{PV4} = 2V$ ,           |       | 50    |       | uр    |

| Internal Discharge Resistance in Shutdown |        | EN = low, resistance fr                                                                             | om OUT4 to AGND                | 0.5   | 1.0   | 2.0   | kΩ    |

**MAX8671X**

#### **ELECTRICAL CHARACTERISTICS (continued)**

(DC, USB, BVSET,  $\overline{UOK}$ ,  $\overline{DOK}$ , LX\_ unconnected;  $V_{THM} = V_L/2$ ,  $V_{PG_-} = V_{AGND} = 0V$ ,  $V_{BAT} = 4V$ ,  $\overline{CEN} = Iow$ , USUS = Iow, EN = high,  $V_{PEN1} = V_{PEN2} = 3.3V$ ,  $V_{PWM} = 0V$ ,  $C_{OUT4} = 1\mu$ F,  $C_{OUT5} = 1\mu$ F,  $C_{SYS} = 10\mu$ F, PV1 = PV2 = PV3 = PV4 = PV5 = SYS,  $R_{DISET} = 3k\Omega$ ,  $R_{CISET} = 3k\Omega$ ,  $C_{VL} = 0.1\mu$ F,  $C_{CT} = 0.15\mu$ F,  $C_{BP} = 0.01\mu$ F,  $V_{FB1} = 1.1V$ ,  $V_{FB2} = 1.1V$ ,  $V_{FB3} = 1.1V$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted.) (Note 2)

| PARAMETER                                 | SYMBOL           | CONDI                                                                                               | TIONS                     | MIN      | ТҮР   | МАХ                      | UNITS |

|-------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------|---------------------------|----------|-------|--------------------------|-------|

| REG5-LINEAR REGULATOR                     | •                |                                                                                                     |                           | •        |       |                          | •     |

| PV5 Operating Range                       | V <sub>PV5</sub> |                                                                                                     |                           | 1.7      |       | VSYS                     | V     |

| PV5 Undervoltage Lockout<br>Threshold     |                  | V <sub>PV5</sub> rising, 100mV hys                                                                  | steresis                  | 1.55     | 1.60  | 1.65                     | V     |

| FB5 Voltage                               |                  | No load                                                                                             |                           | 0.582    | 0.600 | 0.618                    | V     |

|                                           |                  |                                                                                                     | $T_A = +25^{\circ}C$      | -50      | -5    | +50                      |       |

| FB5 Leakage Current                       |                  | $V_{FB5} = 0.6V$                                                                                    | $T_A = +85^{\circ}C$      |          | -5    |                          | nA    |

| Drop Out Registeres                       |                  | V <sub>PV5</sub> to OUT5, V <sub>PV5</sub> =                                                        | 3.3V                      |          | 0.45  |                          |       |

| Drop-Out Resistance                       |                  | V <sub>PV5</sub> to OUT5, V <sub>PV5</sub> =                                                        | 2.0V                      |          | 0.75  | 1.8                      | Ω     |

| Current Limit                             |                  | $V_{FB5} = 0.54V$                                                                                   |                           | 200      | 230   | 265                      | mA    |

|                                           |                  | $V_{FB5} = 0V$                                                                                      | V <sub>FB5</sub> = 0V     |          | 235   |                          | ША    |

| Output Noise                              |                  | 10Hz to 100kHz,<br>C <sub>OUT5</sub> = 2.2µF, I <sub>OUT5</sub> =<br>V <sub>OUT5</sub> set for 3.3V |                           | 180      |       | μV <sub>RMS</sub>        |       |

|                                           |                  | f = 1kHz, $I_{OUT5}$ = 10mA, $V_{PV5}$ = 3.5V, $V_{OUT5}$ set for 3.3V                              |                           | 62<br>44 |       | - dB                     |       |

| PSRR                                      |                  | f = 10kHz, I <sub>OUT5</sub> = 10mA, V <sub>PV5</sub> = 3.5V,<br>V <sub>OUT5</sub> set for 3.3V     |                           |          |       |                          |       |

| Internal Discharge Resistance in Shutdown |                  | EN = low, resistance from OUT5 to AGND                                                              |                           | 0.5      | 1.0   | 2.0                      | kΩ    |

| VL—LINEAR REGULATOR                       |                  |                                                                                                     |                           |          |       |                          | 1     |

| VL Voltage                                | V <sub>VL</sub>  | $I_{VL} = 0 \text{mA to } 3 \text{mA}$                                                              |                           | 3.0      | 3.3   | 3.6                      | V     |

| LOGIC (UOK, DOK, PEN1, PEN2,              | USUS, CEN        | CST1, CST2, EN, PWN                                                                                 | 1)                        |          |       |                          |       |

| Logic Input-Voltage Low                   |                  | $V_{USB}$ or $V_{DC} = 4.1V$ to 5.5V                                                                | 6.6V, $V_{SYS} = 2.6V$ to |          |       | 0.6                      | V     |

| Logic Input-Voltage High                  |                  | $V_{USB}$ or $V_{DC} = 4.1V$ to 5.5V                                                                | 6.6V, $V_{SYS} = 2.6V$ to | 1.3      |       |                          | V     |

|                                           |                  |                                                                                                     | $T_A = +25^{\circ}C$      |          | 0.001 | 1                        |       |

| Logic Input Leakage Current               |                  | $V_{LOGIC} = 0V$ to 5.5V                                                                            | $T_A = +85^{\circ}C$      |          | 0.01  |                          | μA    |

| Logic Output-Voltage Low                  |                  | I <sub>SINK</sub> = 1mA                                                                             | •                         |          | 10    | 30                       | mV    |

| Logic Output-High Leakage                 |                  |                                                                                                     | $T_A = +25^{\circ}C$      |          | 0.001 | 1                        |       |

| Current                                   |                  | $V_{\text{LOGIC}} = 5.5V \qquad \qquad T_{\text{A}} = +85^{\circ}\text{C}$                          |                           |          | 0.01  |                          | μΑ    |

| TRI-STATE INPUT (BVSET)                   |                  |                                                                                                     |                           |          |       |                          |       |

| BVSET Input-Voltage Low                   |                  | $V_{USB}$ or $V_{DC} = 4.1V$ to                                                                     | 6.6V                      |          |       | 0.3                      | V     |

| BVSET Input-Voltage Mid                   |                  | $V_{\text{USB}}$ or $V_{\text{DC}} = 4.1 \text{V}$ to                                               | 6.6V                      | 1.2      |       | V <sub>VL</sub> -<br>1.2 | V     |

#### **ELECTRICAL CHARACTERISTICS (continued)**

(DC, USB, BVSET,  $\overline{\text{UOK}}$ ,  $\overline{\text{DOK}}$ , LX\_ unconnected;  $V_{THM} = V_L/2$ ,  $V_{PG_-} = V_{AGND} = 0V$ ,  $V_{BAT} = 4V$ ,  $\overline{\text{CEN}} = \text{low}$ , USUS = low, EN = high,  $V_{PEN1} = V_{PEN2} = 3.3V$ ,  $V_{PWM} = 0V$ ,  $C_{OUT4} = 1\mu$ F,  $C_{OUT5} = 1\mu$ F,  $C_{SYS} = 10\mu$ F, PV1 = PV2 = PV3 = PV4 = PV5 = SYS,  $R_{DISET} = 3k\Omega$ ,  $R_{CISET} = 3k\Omega$ ,  $C_{VL} = 0.1\mu$ F,  $C_{CT} = 0.15\mu$ F,  $C_{BP} = 0.01\mu$ F,  $V_{FB1} = 1.1V$ ,  $V_{FB2} = 1.1V$ ,  $V_{FB3} = 1.1V$ ,  $T_A = -40^{\circ}$ C to  $+85^{\circ}$ C, unless otherwise noted.) (Note 2)

| PARAMETER                                                  | SYMBOL | CONDITIONS                           | MIN                      | ТҮР  | MAX                      | UNITS |

|------------------------------------------------------------|--------|--------------------------------------|--------------------------|------|--------------------------|-------|

| BVSET Input-Voltage High                                   |        | $V_{USB}$ or $V_{DC}$ = 4.1V to 6.6V | V <sub>VL</sub> -<br>0.3 |      | V <sub>VL</sub> +<br>0.3 | V     |

| Internal BVSET Pullup Resistance                           |        |                                      |                          | 52.5 |                          | kΩ    |

| External BVSET Pulldown<br>Resistance for Midrange Voltage | RBVSET |                                      | 45                       | 50   | 55                       | kΩ    |

**Note 2:** Limits are 100% production tested at  $T_A = +25^{\circ}$ C. Limits over the operating temperature range are guaranteed through correlation using statistical quality control (SQC) methods.

Note 3: The USB/DC current limit does not include the VL output current. See the VL Linear Regulator section for more information.

Note 4: Quiescent current excludes the energy needed for the REG1–REG5 external resistor-dividers. All typical operating characteristics include the energy for the REG1–REG5 external resistor-dividers. For the circuit of Figure 1, the typical quiescent current with DC and USB unconnected, EN = high, V<sub>BAT</sub> = 4V, and PWM = low is 175μA.

Note 5: The charger transitions from done to fast-charge mode at this BAT recharge threshold (Figure 7).

Note 6: The charger transitions from fast-charge to top-off mode at this top-off threshold (Figure 7).

**Note 7:** The maximum output current is guaranteed by correlation to the p-channel current-limit threshold, p-channel on-resistance, n-channel on-resistance, oscillator frequency, input voltage range, and output voltage range. The parameter is stated for a 4.7µH inductor with 0.13Ω series resistance. See the *Step-Down Converter Output Current* section for more information.

Note 8: The step-down output voltages are 1% high with no load due to the load-line architecture. When calculating the external resistor-dividers, use an FB\_ voltage of 1.000V.

- Note 9: Line regulation for the step-down converters is measured as ΔV<sub>OUT</sub>/ΔD, where D is the duty cycle (approximately V<sub>OUT</sub>/V<sub>IN</sub>).

- **Note 10:** The skip mode current threshold is the transition point between fixed-frequency PWM operation and skip mode operation. The specification is given in terms of output load current for inductor values shown in the typical application circuits.

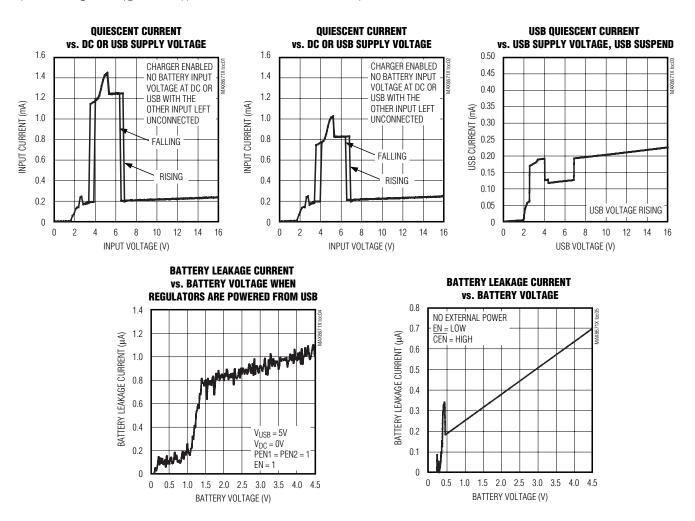

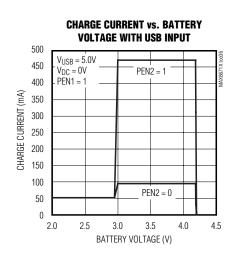

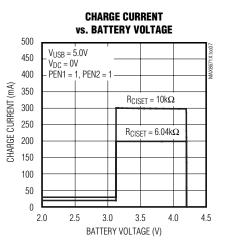

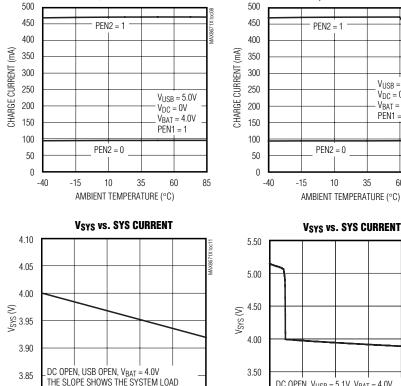

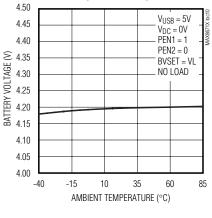

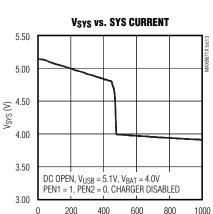

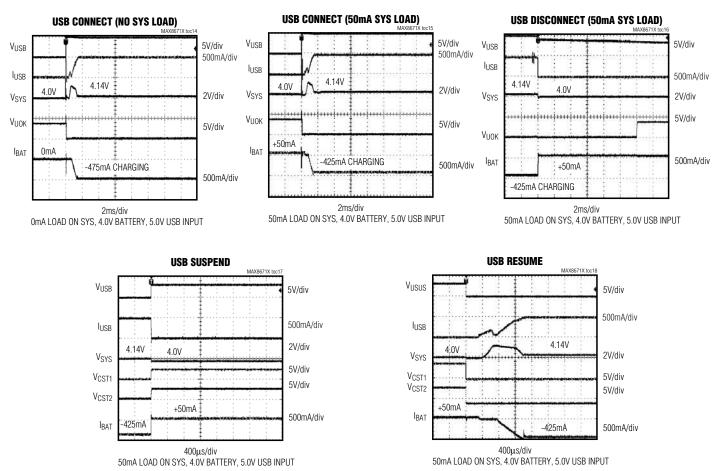

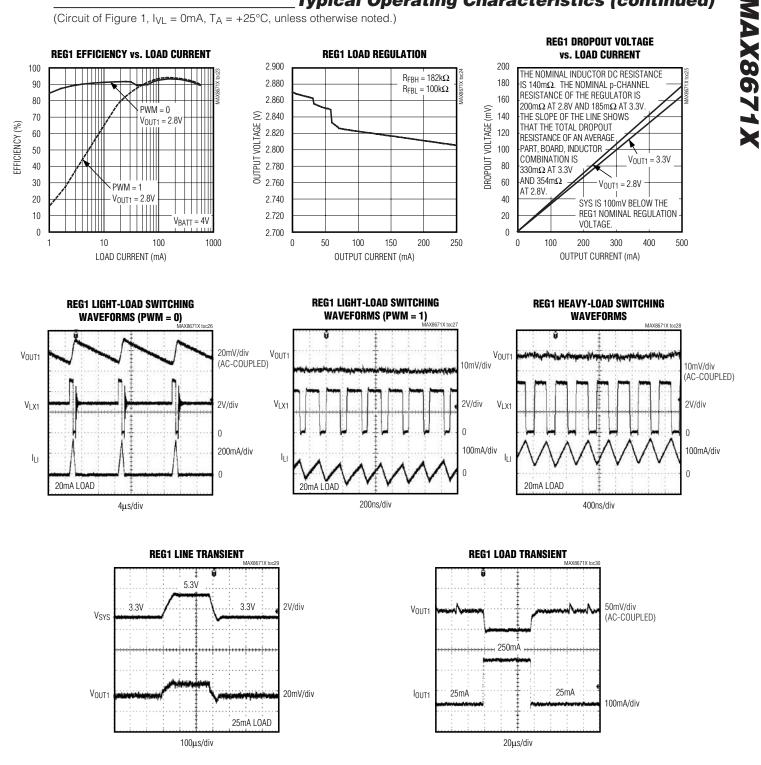

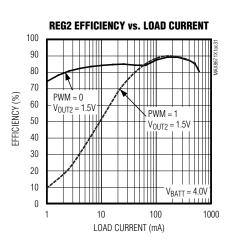

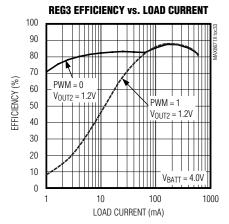

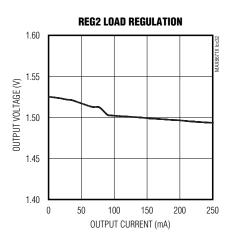

(Circuit of Figure 1,  $I_{VL}$  = 0mA,  $T_A$  = +25°C, unless otherwise noted.)

**Typical Operating Characteristics**

**MAX8671X**

M/XI/M

#### **Typical Operating Characteristics (continued)**

(Circuit of Figure 1,  $I_{VL}$  = 0mA,  $T_A$  = +25°C, unless otherwise noted.)

**CHARGE CURRENT vs. AMBIENT TEMPERATURE, LOW POWER DISSIPATION**

**CHARGE CURRENT vs. AMBIENT TEMPERATURE. HIGH IC POWER DISSIPATION**

$V_{USB} = 6.5V$

$V_{BAT} = 3.1V$

60

85

1000

$V_{DC} = 0V$

PFN1 = 1

PEN2 = 1

PEN2 = 0

10

DC OPEN,  $V_{USB} = 5.1V$ ,  $V_{BAT} = 4.0V$

400

200

3.00

0

PEN1 = 1, PEN2 = 0, CHARGER DISABLED

SYS CURRENT (mA)

600

800

35

**BATTERY REGULATION VOLTAGE** vs. TEMPERATURE

200 400 600 800 SYS CURRENT (mA)

M/XX/M

3.80

14

0

200

SWITCH HAS AN ON-RESISTANCE OF 81m Ω.

SYS CURRENT (mA)

600

800

1000

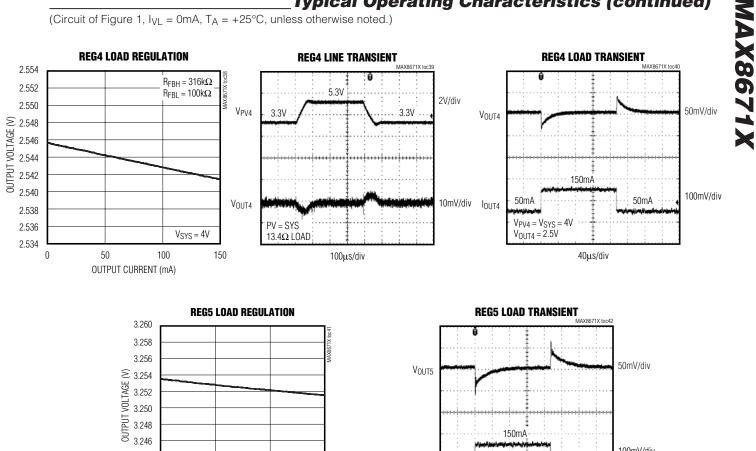

#### **Typical Operating Characteristics (continued)**

(Circuit of Figure 1,  $I_{VL}$  = 0mA,  $T_A$  = +25°C, unless otherwise noted.)

**MAX8671X**

**Typical Operating Characteristics (continued)**

(Circuit of Figure 1,  $I_{VL}$  = 0mA,  $T_A$  = +25°C, unless otherwise noted.)

4ms/div

#### **Typical Operating Characteristics (continued)**

(Circuit of Figure 1,  $I_{VL}$  = 0mA,  $T_A$  = +25°C, unless otherwise noted.)

MIXIM

#### **Typical Operating Characteristics (continued)**

(Circuit of Figure 1,  $I_{VI}$  = 0mA,  $T_A$  = +25°C, unless otherwise noted.)

(Circu

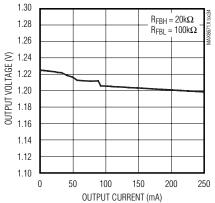

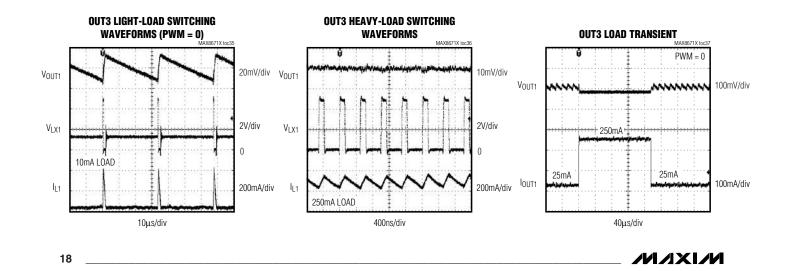

**REG3 LOAD REGULATION**

**Typical Operating Characteristics (continued)**

150mA

40µs/div

50mA

$V_{USB} = 5V,$

$V_{OUT5} = 3.3V$

I<sub>OUT5</sub>

$V_{USB} = 5V$

150

100

100mV/div

50mA

19

3.244

3.242

3.240 0

50

OUTPUT CURRENT (mA)

#### **Pin Description**

| PIN | NAME  | FUNCTION                                                                                                                                                                                                                                                                  |

|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | USUS  | USB Suspend Digital Input. As shown in Table 1, driving USUS high suspends the DC or USB inputs if they are configured as a USB power input.                                                                                                                              |

| 2   | DC    | DC Power Input. DC is capable of delivering 1A to SYS. DC supports both AC adaptors and USB inputs. As shown in Table 1, the DC current limit is controlled by PEN1, PEN2, USUS, and R <sub>DISET</sub> .                                                                 |

| 3   | USB   | USB Power Input. USB is capable of delivering 0.5A to SYS. As shown in Table 1, the USB current limit is controlled by PEN1, PEN2, and USUS.                                                                                                                              |

| 4   | FB5   | Feedback Input for REG5. Connect FB5 to the center of a resistor voltage-divider from OUT5 to AGND to set the REG5 output voltage from 0.6V to $V_{PV5}$ .                                                                                                                |

| 5   | PV5   | Power Input for REG5. Connect PV5 to SYS, or a supply between 1.7V and V_{SYS}. Bypass PV5 to power ground with a $1\mu F$ ceramic capacitor.                                                                                                                             |

| 6   | OUT5  | Linear Regulator Power Output. OUT5 is internally pulled to AGND by $1k\Omega$ in shutdown.                                                                                                                                                                               |

| 7   | PG2   | Power Ground for the REG2 Step-Down Regulator                                                                                                                                                                                                                             |

| 8   | LX2   | Inductor Switching Node for REG2. LX2 is internally pulled to PG2 by $1k\Omega$ in shutdown.                                                                                                                                                                              |

| 9   | PV2   | Power Input for the REG2 Step-Down Regulator. Connect PV2 to SYS. Bypass PV2 to PG2 with a 4.7µF ceramic capacitor.                                                                                                                                                       |

| 10  | CEN   | Active-Low Charger Enable Input. Pull CEN low to enable the charger, or drive CEN high to disable charging. The battery charger is also disabled when USUS is high.                                                                                                       |

| 11  | FB2   | Feedback Input for REG2. Connect FB2 to the center of a resistor voltage-divider from the REG2 output capacitors to AGND to set the output voltage from 1V to V <sub>SYS</sub> .                                                                                          |