# ICS9169C-26

# Integrated Circuit Systems, Inc.

# Frequency Generator and Integrated Buffers

### **General Description**

The ICS9169C-26 is a low-cost frequency generator designe specifically for Pentium<sup>™</sup>-based chip set systems. The integrated buffer minimizes skew and provides all the clocks required. A 14.318 MHz XTAL oscillator provides the reference clock to generate standard Pentium frequencies. The CPU clock makes gradual frequency transitions without violating the PLL timing of internal microprocessor clock multipliers.

Either synchronous (CPU/2) or asynchronous (32 MHz) PCI bus operation can be selected.

### Features

- Twelve selectable CPU clocks operate up to 83.3 MHZ

- Eight selectable CPU clocks operate up to100 MHz

- Maximum CPU jitter of ±200ps •

- Seven BUS clocks support sync or async bus operation •

- 500ps skew window for all synchronous clock edges CPU clocks to BUS clocks in sync mode skew 1-4ns (CPU early)

- Integrated buffer outputs drive up to 30pF loads

- 3.0V 3.7V supply range

VDD

GND

CPU8

CPU7

VDD

CPU6

CPU5

GND

CPU4 -

CPU3 -

VDD -

CPU2 -

CPU1

GND

FS2

FS1

X1

X2

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

- 36-pin SSOP package

- 48 MHz clock for USB support and 24 MHz clock for FD

**Pin Configuration**

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

REF3

REF2

RFF1

VDD

GND

BUS7

BUS6

VDD

BUS5

BUS4

BUS3

GND

BUS2

BUS1

BSEL

FS0

24MHz

48MHz

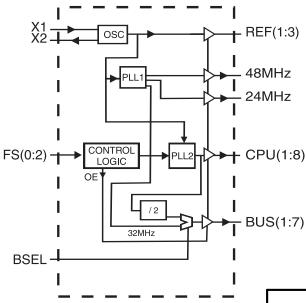

### **Block Diagram**

#### 18 19 36-Pin SSOP

CS169C-26

CPU BUS REF BSEL FS2 FS1 FS0 48 MHz 24 MHz (1:8)(0:7)(1:3)MHz MHz 0 0 0 0 27.548 24 14.318 55 0 0 0 1 80 40 48 24 14.318 0 0 1 0 100 50 48 24 14.318 0 0 1 1 75 37.5 48 24 14.318 1 0 0 0 24 14.318 50 25 48 0 1 0 1 66.6 33.3 48 24 14.318 0 1 1 0 30.0 48 24 14.318 60 0 1 1 1 Tristate Tristate Tristate Tristate Tristate 1 select Tristate 32.0 select select 48 24 14.318

# Functionality

3.3V±10%. 0-70°C Crystal (X1, X2) = 14.31818 MHz

#### Pentium is a trademark on Intel Corporation

PRODUCT PREVIEW documents contain information on new products in the sampling or preproduction phase of development Characteristic data and other specifications are subject to change without notice.

### 9169C-26RevB091997P

| <b>Preliminary Product Preview</b> | Preliminary | Product | Preview |

|------------------------------------|-------------|---------|---------|

|------------------------------------|-------------|---------|---------|

# **Pin Descriptions**

| PIN NUMBER                 | PIN NAME | ТҮРЕ | DESCRIPTION                                                                                                                                                      |

|----------------------------|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 7, 13, 27, 33           | VDD      | PWR  | Power for control logic, PLL and output buffers.                                                                                                                 |

| 2                          | X1       | IN   | XTAL or external reference frequency input. This input<br>includes XTAL load capacitance and feedback bias for a 12 -<br>16 MHz crystal, nominally 14.31818 Mhz. |

| 3                          | X2       | OUT  | XTAL output which includes XTAL load capacitance.                                                                                                                |

| 4, 10, 16, 23, 30          | GND      | PWR  | Ground for logic, PLL and output buffers.                                                                                                                        |

| 5, 6, 8, 9, 11, 12, 14, 15 | CPU(1:8) | OUT  | Processor clock outputs which are a multiple of the input<br>reference frequency as shown in the table above.                                                    |

| 17, 18, 19                 | FS(1:2)  | IN   | Frequency multiplier select pins. See table above. These inputs have internal pull-up devices.                                                                   |

| 20                         | BSEL     | IN   | Selector for synchronous or asynchronous bus operation.                                                                                                          |

| 21, 22, 24, 25, 26, 28, 29 | BUS(1:7) | OUT  | Bus clock outputs.                                                                                                                                               |

| 31                         | 48MHz    | OUT  | Fixed 48 MHz clock (with 14.318 MHz input).                                                                                                                      |

| 32                         | 24MHz    | OUT  | Fixed 24 MHz clock (with 14.318 MHz input).                                                                                                                      |

| 34, 35, 36                 | REF(1:3) | OUT  | REF is a buffered copy of the crystal oscillator or reference input clock, nominally 14.31818 Mhz.                                                               |

### **Absolute Maximum Ratings**

| Supply Voltage                | 7.0V                              |

|-------------------------------|-----------------------------------|

| Logic Inputs                  | GND –0.5 V to $V_{DD}$ +0.5 V $$  |

| Ambient Operating Temperature | $0^{\circ}C$ to $+70^{\circ}C$    |

| Storage Temperature           | $-65^{\circ}C$ to $+150^{\circ}C$ |

Stresses above those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These ratings are stress specifications only and functional operation of the device at these or any other conditions above those listed in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

### Electrical Characteristics at 3.3V

$V_{DD} = 3.0 - 3.7 \text{ V}, T_A = 0 - 70^{\circ} \text{ C}$  unless otherwise stated

|                      |             | DC Characteristics              |               |       |        |       |

|----------------------|-------------|---------------------------------|---------------|-------|--------|-------|

| PARAMETER            | SYMBOL      | TEST CONDITIONS                 | MIN           | ТҮР   | MAX    | UNITS |

| Input Low Voltage    | VIL         | $\sim$ $\sim$                   |               | -     | 0.2Vdd | V     |

| Input High Voltage   | VIH         |                                 | 0.7Vdd        | -     | -      | V     |

| Input Low Current    | In          | VIN=0V                          | -28.0         | -10.5 | -      | μA    |

| Input High Current   | Цн          | VIN=VDD                         | -5.0          | -     | 5.0    | μA    |

| Output Low Current1  | Iol         | Vol=0.8V; for CPUs & BUSes      | 30.0          | 47.0  |        | mA    |

| Output High Current1 | Іон         | Vol=2.0V; for CPUs & BUSes      |               | -66.0 | -42.0  | mA    |

| Output Low Current1  | Iol         | VoL=0.8V; for fixed CLKs        | 25.0          | 38.0  | -      | mA    |

| Output High Current1 | Іон         | Vol=2.0V; for fixed CLKs        | 5 10          | -47.0 | -30.0  | mA    |

| Output Low Voltage1  | Vol         | IoL=15mA; for CPUs & BUSes      | <u>-</u>      | 0.3   | 0.4    | V     |

| Output High Voltage1 | Vон         | Iон=-30mA; for CPUs & BUSes     | 2.4           | 2.8   | -      | V     |

| Output Low Voltage1  | Vol         | IoL=12.5mA; for fixed CLKs      | 9 <u>-</u> KA | 0.3   | 0.4    | V     |

| Output High Voltage1 | <b>V</b> он | Iон=-20mA; for fixed CLKs       | 2.4           | 2.8   | -      | V     |

| Supply Current       | IDD         | @66.6 MHz; all outputs unloaded |               | 55    | 110    | mA    |

Note 1: Parameter is guaranteed by design and characterization. Not 100% tested in production.

# **Preliminary Product Preview**

### **Electrical Characteristics at 3.3V**

$V_{DD}$  = 3.0 – 3.7 V,  $T_A$  = 0 – 70° C unless otherwise stated

|                                             |        | AC Characteristics                                                     |                                                   |        |      | $\sim$ |

|---------------------------------------------|--------|------------------------------------------------------------------------|---------------------------------------------------|--------|------|--------|

| PARAMETER                                   | SYMBOL | TEST CONDITIONS                                                        | MIN                                               | ТҮР    | MAX  | UNITS  |

| Rise Time <sup>1</sup>                      | Trl    | 20pF load, 0.8 to 2.0V<br>CPU & BUS                                    |                                                   | 0.9    | 1.5  | ns     |

| Fall Time <sup>1</sup>                      | Tfl    | 20pF load, 2.0 to 0.8V<br>CPU & BUS                                    | (( -))                                            | 0.8    | 1,4  | ns     |

| Rise Time <sup>1</sup>                      | Tr2    | 20pF load, 20% to 80%<br>CPU & BUS                                     | -                                                 | 1.5    | 2.5  | ns     |

| Fall Time <sup>1</sup>                      | Tr2    | 20pF load, 80% to 20%<br>CPU & BUS                                     | ,                                                 | 1.4    | 2.4  | ns     |

| Duty Cycle <sup>1</sup>                     | Dt     | 20pF load @ VOUT=1.4V                                                  | 45                                                | 50     | 55   | %      |

| Jitter, One Sigma <sup>1</sup>              | Tjtsl  | CPU & BUS Clocks;<br>Load=20pF, >25 MHz                                | $\left(\begin{array}{c} \cdot \end{array}\right)$ | 50     | 150  | ps     |

| Jitter, Absolute <sup>1</sup>               | Tjab1  | PCLK & BCLK Clocks;<br>Load=20pF, FOUT>25 MHz                          | -200                                              | -      | 200  | ps     |

| Jitter, One Sigma <sup>1</sup>              | Tj1s2  | Fixed CLK; Load=20pF                                                   | ) - <                                             | 1      | 3    | %      |

| Jitter, Absolute <sup>1</sup>               | Tjab2  | Fixed CLK; Load=20pF                                                   | -5                                                | 2      | 5    | %      |

| Input Frequency <sup>1</sup>                | Fi     | $\bigcirc$ $\land$ $\lor$                                              | 12.0                                              | 14,318 | 16.0 | MHz    |

| Logic Input Capacitance <sup>1</sup>        | CIN    | Logic input pins                                                       | <u>} -                                   </u>     | 5      |      | pF     |

| Crystal Oscillator Capacitance <sup>1</sup> | CINX   | X1, X2 pins                                                            |                                                   | 18     | -    | pF     |

| Power-on Time <sup>1</sup>                  | ton    | From VDD=1.6V to 1st crossing<br>of 66.6 MHz VDD supply<br>ramp < 40ms |                                                   | 2.5    | 4.5  | ms     |

| Frequency Settling Time <sup>1</sup>        | ts     | From 1st crossing of acquisition to < 1% settling                      |                                                   | 2.0    | 4.0  | ms     |

| Clock Skew <sup>1</sup>                     | Tsk1   | CPU to CPU;<br>Load=20pF; @1.4V                                        | <u> </u>                                          | 150    | 250  | ps     |

| Clock Skew <sup>1</sup>                     | Tsk2   | BUS to BUS;<br>Load=20pF; @1.4V                                        | -                                                 | 300    | 500  | ps     |

| Clock Skew <sup>1</sup>                     | Tsk3   | CPU & BUS;<br>Load=20pF; @1.4V                                         | 1                                                 | 2.6    | 4    | ns     |

Note 1: Parameter is guaranteed by design and characterization. Not 100% tested in production.

## **Preliminary Product Preview**

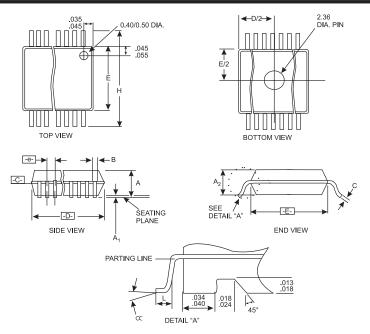

### **SSOP** Package

| SYMBOL | CO             | MMON DIMI | ENSIONS | VARIATIONS |      | D    |      | Ν  |

|--------|----------------|-----------|---------|------------|------|------|------|----|

|        | MIN.           | NOM.      | MAX.    |            | MIN. | NOM. | MAX. |    |

| А      | .097           | .101      | .110    | AA         | .602 | .607 | 612  | 36 |

| A1     | .008           | .010      | .0116   | AB         | .701 | .706 | .711 | 44 |

| A2     | .090           | .092      | .094    | AC         | .620 | .625 | .630 | 48 |

| В      | .0091          | .014      | .017    | AD         | .720 | .725 | .730 | 56 |

| С      | .0091          | .010      | .0125   |            |      |      |      |    |

| D      | See Variations |           |         |            |      |      |      |    |

| Е      | .292           | .296      | .299    |            |      |      |      |    |

| e      |                | .0315 BSC |         |            |      |      |      |    |

| Н      | .400           | .406      | .410    |            |      |      |      |    |

| h      | .010           | .013      | .016    |            |      |      |      |    |

| L      | .024           | .032      | .040    |            |      |      |      |    |

| Ν      | See Variations |           |         |            |      |      |      |    |

| ~      | 0°             | 5°        | 8°      |            |      |      |      |    |

| Х      | .085           | .093      | .100    |            |      |      |      |    |

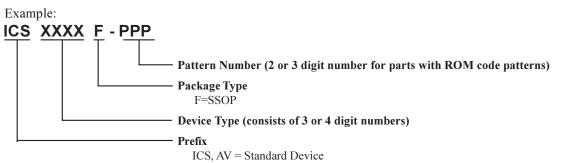

### **Ordering Information**

This table in inches