Inc.

Semiconductor

131,072 x 8 bit MNOS EEPROM

#### **Features**

Fast Access Time of 150/200/250 ns.

Operating Power 200 mW typical.

Standby Power 5mW TTL (Max)

100µA CMOS (Max)

Software Data Protection.

**Data Polling**

Byte or Page Write Cycle: 5ms typical.

128 Byte Page Size

High Density VIL™ Package.

Data Retention > 10 years.

Endurance > 104 Write Cycles.

Data Protection by RES pin.

May be Processed to MIL-STD-883 Method 5004, non-compliant.

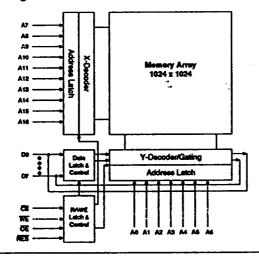

#### **Block Diagram**

# 128K x 8 EEPROM

#### MEM8129-15/20/25

Issue 1.3: July 1993

## ADVANCE PRODUCT INFORMATION

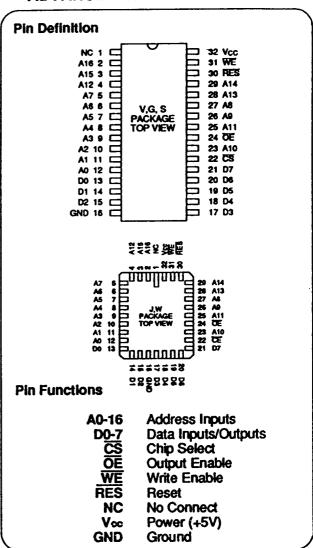

#### Package Details (See package details section for details)

| Pin Count | Description              | Package Type | Material | Pin Out |

|-----------|--------------------------|--------------|----------|---------|

| 32        | 100 mil Vertical-In-Line | VILTM        | Ceramic  | ASIC    |

| 32        | 600 mil Dual-In-Line     | DIP          | Ceramic  | ASIC    |

| 32        | Bottom Brazed Flatpack   | Flatpack     | Ceramic  | ASIC    |

| 32        | Leadless Chip Carrier    | LCC          | Ceramic  | ASIC    |

| 32        | J-Leaded Chip Carrier    | JLCC         | Ceramic  | ASIC    |

VIL is a Trademark of Mosaic Semiconductor Inc. US patent number D316251

#### **Absolute Maximum Ratings**

| Voltage on any pin relative to GND | V,               | -0.6 to +7.0 | ٧        |

|------------------------------------|------------------|--------------|----------|

| Power Dissipation                  | ₽,`              | 1            | W        |

| Storage Temperature                | T <sub>sto</sub> | -65 to +150  | <b>℃</b> |

Notes: (1) Stresses above those listed may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

(2) V, can be -3.0V pulse of less than 50ns.

| Pacomm/ | hobne | norsting | <b>Conditions</b> |

|---------|-------|----------|-------------------|

| necomm  |       | Dei aumu | COHUMBIONS        |

|                       |                 | min  | typ | max                 |                  |

|-----------------------|-----------------|------|-----|---------------------|------------------|

| Supply Voltage        | V <sub>∞</sub>  | 4.5  | 5.0 | 5.5                 | V                |

| Input High Voltage    | <b>√</b> ਔ2)    | 2.2  | -   | V <sub>∞</sub> +0.3 | V                |

| Input Low Voltage     | <b>V</b>        | -0.3 | •   | <b>0.8</b>          | V                |

| Operating Temperature | T,              | 0    | -   | 70                  | <b>°C</b>        |

|                       | T <sub>AI</sub> | -40  | -   | 85                  | °C (MEM8129I)    |

|                       | T <sub>AM</sub> | -55  | -   | 125                 | °C (MEM8129M,MB) |

Note: (1) V<sub>L</sub> can be -1.0V pulse of less than 50ns.

(2) Except RES pin.

DC Electrical Characteristics (T<sub>4</sub>=-55°C to +125°C)

| Parameter              | Symbol           | Test Condition                                                  |       | max | Unit |  |

|------------------------|------------------|-----------------------------------------------------------------|-------|-----|------|--|

| Input Leakage Current  | l <sub>u</sub>   | V <sub>w</sub> =GND to V <sub>∞</sub>                           | •     | 2   | μА   |  |

| Output Leakage Current | الَّه            | V <sub>io</sub> =GND to V <sub>∞</sub>                          | -     | 2   | μА   |  |

| Average Current        | l <sub>cc1</sub> | l <sub>so</sub> =0mA,Duty = 100%, Cycles = 20                   | Ons - | 40  | mA   |  |

| Standby Current TTL    | l <sub>sa</sub>  | CE=V <sub>H</sub>                                               | -     | 1   | mA   |  |

| Standby Current CMOS   | <sub>S81</sub>   | CE =V <sub>cc</sub> , OE =V <sub>E</sub> , I <sub>co</sub> =0mA | •     | 20  | μА   |  |

| Output Voltage         | Voc              | l <sub>ot</sub> =2.1mA                                          | •     | 0.4 | ٧    |  |

|                        | VoH              | l <sub>αμ</sub> =-400 μA                                        | 2.4   | -   | V    |  |

Note: (1)  $I_{\mu}$  on  $\overline{RES} = 100\mu A \text{ max}$

Capacitance (V<sub>cc</sub>=5V±10%,T<sub>A</sub>=25°C, f=1MHz)

| Parameter         | Symbol           | Test Condition       | typ | max | Unit |

|-------------------|------------------|----------------------|-----|-----|------|

| Input Capacitance | C <sub>IN</sub>  | V <sub>w</sub> = 0V  | -   | 6   | pF   |

| I/O Capacitance   | C <sub>w</sub> o | V <sub>10</sub> = 0V | -   | 12  | рF   |

Note: This parameter is periodically sampled and not 100% tested.

| AC Test Conditions                                                                                                                                                                         | Output Test Load    |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--|--|

| * Input pulse levels: 0.4V to 2.4V  * Input rise and fall times: 20ns  * Input and Output timing reference levels: 0.8V,1.8V  * Output load: 1 TTL gate + 100pF  * V <sub>cc</sub> =5V±10% | 1.8 kΩ \$  Output σ |  |  |

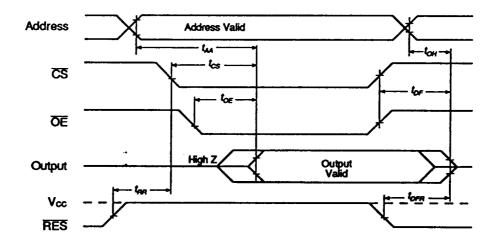

#### **AC READ CHARACTERISTICS**

| Read | Cycle |

|------|-------|

|      |       |

|                                 |                  |     | -15       | -2  | 20  | -2  | 25   |      |       |

|---------------------------------|------------------|-----|-----------|-----|-----|-----|------|------|-------|

| Parameter                       | Symbol           | min | max       | min | max | min | max  | Unit | Notes |

| Address Access Time             | t <sub>M</sub>   | -   | 150       | -   | 200 | -   | 250  | ns   |       |

| CS Access Time                  | tcs              | -   | 150       | -   | 200 | -   | 250  | ns   |       |

| OE Access Time                  | to∈              | 10  | <b>75</b> | 10  | 80  | 10  | 90   | ns   |       |

| OE high to output float         | t <sub>DF</sub>  | 0   | 50        | 0   | 55  | 0   | 60 - | ns   | (1)   |

| •                               | t <sub>DFR</sub> | 0   | 350       | 0   | 350 | 0   | 350  | ns   | (1)   |

| Output Hold from Address Change | t <sub>ort</sub> | 0   | -         | 0   | -   | 0   | -    | ns   | , ,   |

| RES to output delay             | t <sub>RR</sub>  | 0   | 600       | 0   | 600 | 0   | 600  | ns   |       |

Notes: (1) t<sub>off</sub> is defined as the time at which the output achieves the open circuit condition and data is no longer driven.

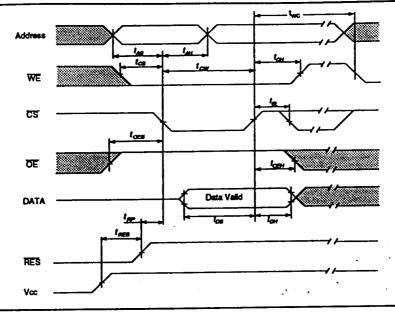

## **Read Cycle Timing Waveform**

Copyright (c) 1993 Information Handling Services Group, Inc. ALL RIGHTS RESERVED.

This image database has been created by Information Handling Services, a Division of TBG Holding nv, and is proprietary to Information Handling Services. No part of this database may be duplicated in hard copy or machine readable form without prior written authorization from Information Handling Services, except that licensee is granted a limited, non-exclusive license to reproduce limited portions of the database for licensee's internal use provided that a suitable notice of copyright is included on all copies. Under no circumstances may copies be made for resale in any media.

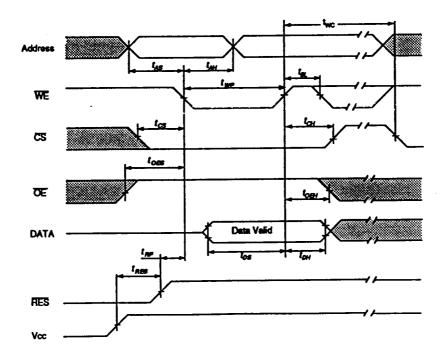

## **AC WRITE CHARACTERISTICS**

## Byte and Page Write Cycle

| Parameter                        | Symbol               | min               | typ | max | Unit |  |

|----------------------------------|----------------------|-------------------|-----|-----|------|--|

| Write Cycle Time                 | t <sub>wc</sub>      | 15 <sup>(1)</sup> |     | -   | ms   |  |

| Address Set-up Time              | t <sub>AS</sub>      | 0                 | -   | -   | ns   |  |

| Address Hold Time                | t <sub>AH</sub>      | 150               | -   | -   | ns   |  |

| OE Set-up Time                   | •                    | 0                 | -   | -   | ns   |  |

| OE Hold Time                     | toes                 | 0                 | -   | -   | ns - |  |

| OE to Output Delay               | гоен<br>t            | 10                | -   | 75  | ns   |  |

| Chip Select Set-up Time          | to∈<br>t             | 0                 | -   | -   | ns   |  |

|                                  | tcs (P)              | -                 | -   | 150 | ns   |  |

| Chip Select Hold Time            | •                    | 0                 | -   | -   | ns   |  |

| Chip Select Pulse Width          | <sup>L</sup> СН<br>t | 250               | -   | -   | ns   |  |

| Write Pulse Width                | t                    | 250               | -   | -   | ns   |  |

| Data Set-up Time                 | t <sub>e e</sub>     | 100               | -   | -   | กร   |  |

| Data Hold Time                   | tos<br>t             | 10                | -   | -   | ns   |  |

| Delay to Next Write              | <sup>ъ</sup> рн<br>‡ | 150               | -   | -   | ns   |  |

| Byte Load Cycle                  | t <sub>ow</sub>      | 0.55              | -   | 30  | μs   |  |

| Byte Load Window                 | LBLC<br>t            | 100               | -   | -   | μs   |  |

| Data Latch Time                  | <sup>L</sup> BL<br>† | 300               | -   | -   | ns . |  |

| RES to Write setup time          | tor<br>t             | 100               | -   | -   | μs   |  |

| V <sub>m</sub> to RES setup time | l <sub>RP</sub>      | 1                 | -   | -   | μs   |  |

| v <sup>∞</sup> to ure semb mile  | RES                  |                   |     |     | F    |  |

Note: (1) Use this device in longer cycle than this value.

(2) This parameter is for Data Polling Characteristics.

(3) Normal writing is not possible when the RES terminal becomes low during writing. The RES terminal should not be made low for at least 10ms after the last writing pulse is input.

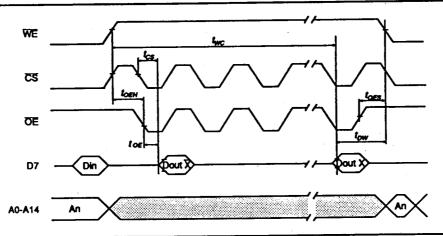

# AC Write Waveform - WE Controlled

# AC Write Waveform - CS Controlled

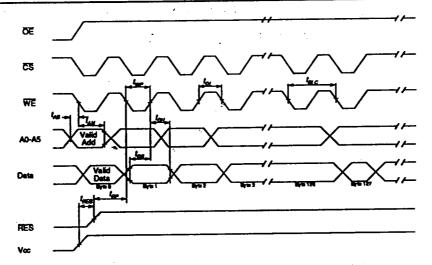

# Page Mode Write Waveform

Note:

A7 through A14 must specify the page address during each high to low transition of WE (or CE). OE must be high only when WE and CE are both low.

# **DATA Polling Waveform**

#### **DEVICE OPERATION**

#### Read

The MEM8129 read operations are initiated by both  $\overline{OE}$  and  $\overline{CE}$  LOW. The read operation is terminated by either  $\overline{CE}$  or  $\overline{OE}$  returning HIGH. This 2-line control architecture eliminates bus contention in a system environment. The data bus will be in a high impedence state when either  $\overline{OE}$  or  $\overline{CE}$  is HIGH.

#### Write

Write operations are initated when both  $\overline{CE}$  and  $\overline{WE}$  are LOW and  $\overline{OE}$  is HIGH. The MEM8129 supports both a  $\overline{CE}$  and  $\overline{WE}$  controlled write cycle. That is, the address is latched by the falling edge of either  $\overline{CE}$  or  $\overline{WE}$ , whichever occurs tast. Similarly, the data is tatched internally by the rising edge of either  $\overline{CE}$  or  $\overline{WE}$ , whichever occurs first. A byte write operation, once initiated, will automatically continue to completion, typically within 5 ms.

#### Page Mode Write

The page write feature of the MEM8129 allows the entire memory to be written. Page Write allows 128 bytes of data to be written prior to the commencement of internal programming cycle. The host can fetch data from another location within the system during a page write operation (change the source address), but the page address (A7 through A16) for each subsequent valid write cycle to the part during this operation must be the same as the initial page address.

The page write mode can be initiated during any write operation. Following the initial byte write cycle, the host can write up to 128 bytes in the same manner as the first byte written. Each successive byte load cycle, started by the WE HIGH to LOW transition, must begin within 30  $\mu s$  of the falling edge of the preceding WE. If a subsequent WE HIGH to LOW transition is not detected within 100  $\mu s$ , the internal automatic programming cycle will commence.

#### **DATA Polling**

The MEM8129 features DATA Polling to indicate if the write cycle is completed. During the internal programming cycle, any attempt to read the last byte written will produce the compliment of that data on D7. Once the programming is complete, D7 will reflect the true data. Note: If the the MEM8129 is in a protected state and an illegal write operation is attempted DATA Polling will not operate.

#### **Hardware Data Protection**

The MEM8129 provides hardware features to protect non-volatile data from inadvertent writes.

\* Noise Protection - A WE pulse less than 20 ns will not initiate a write cycle.

#### **RES Data Protection**

The RES singal disables the device, preventing read and write operations. This offers the greatest protection against inadvertant writes during system reset or power-up/down. A full description of this function can be found in "Write Protection for 1M EEPROM Device" available from Mosaic Semiconductor Inc. The RES pin should not be made low during two.

#### **Mode Selection**

| Mode          | Œ    | ŌĒ   | WE   | RES  | DATA     |

|---------------|------|------|------|------|----------|

| Read          | LOW  | LOW  | HIGH | HIGH | Dout     |

| Standby       | HIGH | ×    | x    | ×    | High-Z   |

| Write         | LOW  | HIGH | LOW  | HIGH | Din      |

| Deselect      | LOW  | HIGH | HIGH | HIGH | High-Z   |

| Write inhibit | ×    | ×    | HIGH | x    | -        |

|               | ×    | LOW  | ×    | x    | -        |

| Data Polling  | LOW  | LOW  | HIGH | HIGH | Data out |

| Program       | ×    | ×    | ×    | LOW  | High-Z   |

X Don't Care

Low V<sub>IL</sub>

High V<sub>IL</sub>

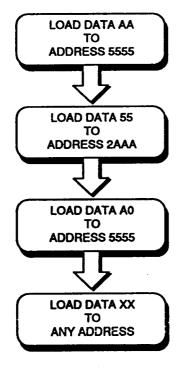

#### **Software Algorithms**

The MEM8129 offers the industry standard software algorithms for data protection.

#### **Software Write Protection**

The array can be protected against inadvertant writes during power up/ power down or illegal access to the system by employing the Software Write Protect Algorithm.

Selecting the software data protection mode requires the host system to precede the data write operations to three specific addresses. The three byte sequence opens the page write window enabling the host to write from 1 to 128 bytes of data.

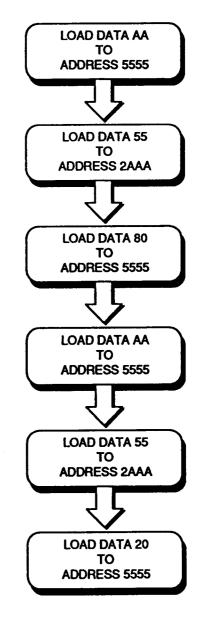

### **Software Write Protect Algorithm**

#### **Software Write Disable**

In the event the user wants to deactivate the software data protection feature for testing or reprogramming in an E<sup>2</sup>PROM programmer.

The following six step algorithm will reset the internal protection circuit. After  $t_{\rm wc}$ , the MEM8129 will be in standard operating mode.

## **Software Write Disable Algorithm**

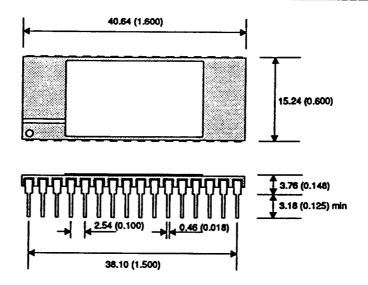

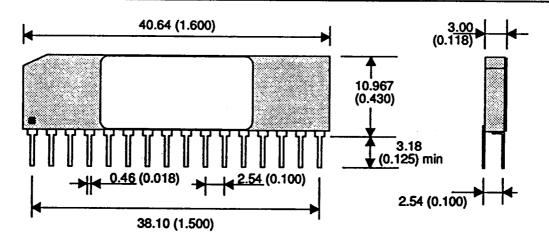

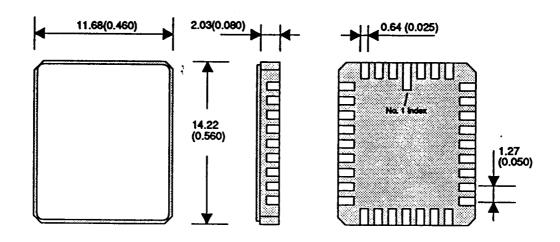

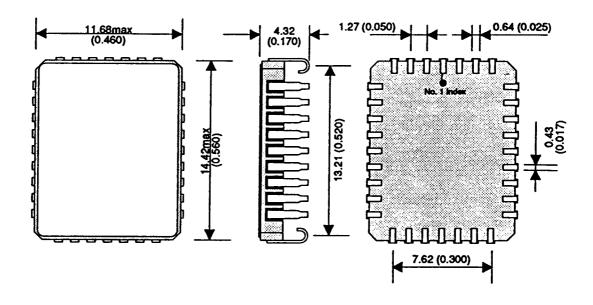

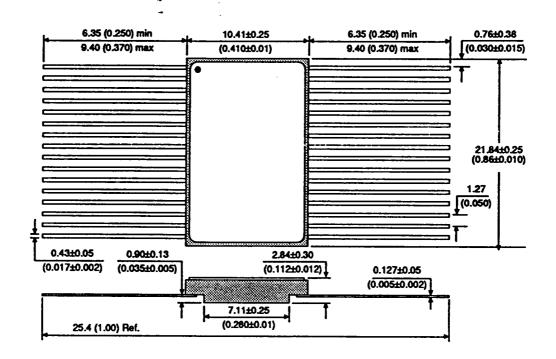

# Package Details All dimensions in mm (inches). Tolerance on all dimensions $\pm$ 0.254 (0.010).

# 32 Pin 600 mil Dual-in Line (DIP) "S"- Package

# 32 Pin 0.1" Vertical-in Line (VIL™) "V"- Package

# 32 pad Leadiess Chip Cerrier (LCC) - 'W' Package

# 32 pad 'J' Leaded Chip Carrier (JLCC) - 'J' Package

# 32 pin Ceramic Flatpack - 'G' Package

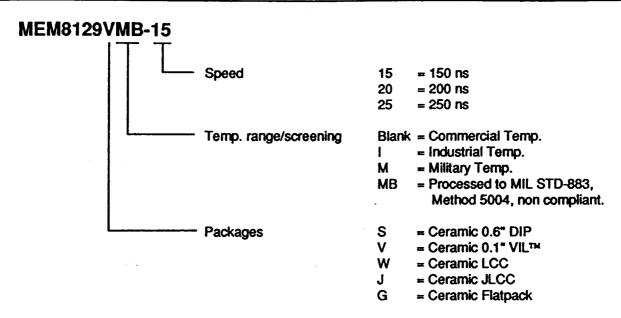

## Ordering Information

Note: For more information regarding screening flows contact Mosaic Semiconductor Inc. for a 'Screening Flow **Applications Note.**\*