### Preliminary Information September 2014

### **GENERAL DESCRIPTION**

IS31AP2111 is a digital audio amplifier capable of driving a pair of  $8\Omega$ , 20W operating at 24V supply without external heat-sink or fan requirement with play music.

IS31AP2111 can provide advanced audio processing capabilities, such as volume control, 20 bands speaker EQ, audio mixing, 3D surround and Dynamic Range Control (DRC). These functions are fully programmable via a simple I2C control interface.

Robust protection circuits are provided to protect IS31AP2111 from damage due to accidental erroneous operating condition. IS31AP2111 is more tolerant to noise and PVT (Process, Voltage, and Temperature) variation than the analog Class-AB or Class-D audio amplifier counterpart implemented by analog circuit design. IS31AP2111 is pop free during instantaneous power switch because of its built-in, robust anti-pop circuit.

## APPLICATIONS

- TV audio

- Boom-box, CD and DVD receiver, docking system

- Powered speaker

- Wireless audio

#### FEATURES

•

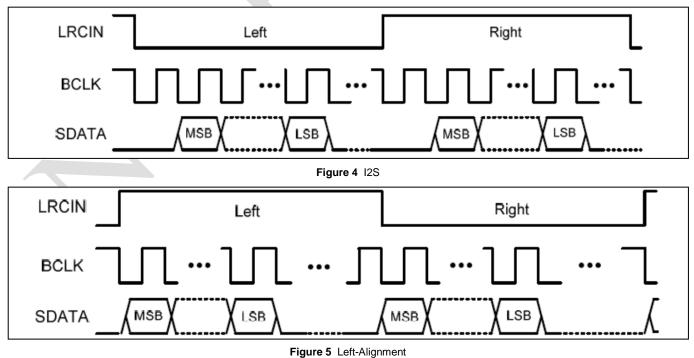

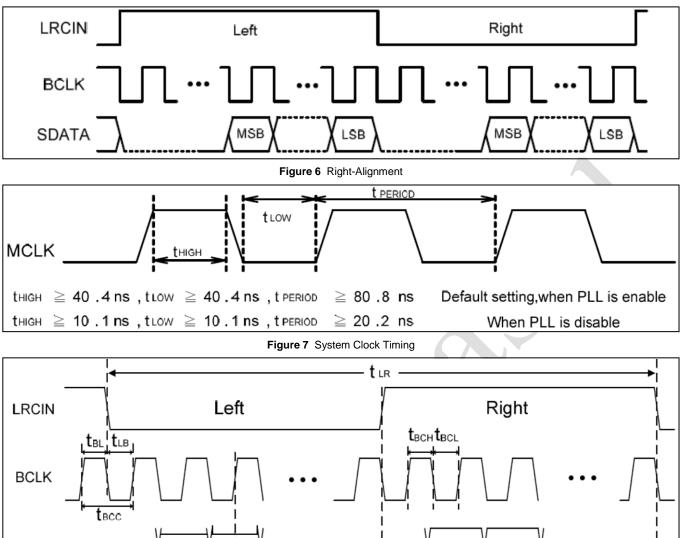

- 16/18/20/24-bits input with I2S, Left-alignment and Right-alignment data format

- PSNR & DR (A-weighting) Loudspeaker: 99dB (PSNR), 104dB (DR) @24V

- Multiple sampling frequencies (F<sub>S</sub>)

- 32kHz / 44.1kHz / 48kHz and

- 64kHz / 88.2kHz / 96kHz and

- 128kHz / 176.4kHz / 192kHz

- System clock = 64x, 128x, 192x, 256x, 384x, 512x, 576x, 768x, 1024x Fs

- 64x~1024x F<sub>S</sub> for 32kHz / 44.1kHz / 48kHz

- 64x~512x F<sub>s</sub> for 64kHz / 88.2kHz / 96kHz

- 64x~256x F<sub>s</sub> for 128kHz / 176.4kHz / 192kHz

- Supply voltage

- 3.3V for digital circuit

- 10V~26V for loudspeaker driver

- Loudspeaker output power for at 24V

- 10W  $\times$  2CH into 8 $\Omega$  @0.24% THD+N for stereo

- 20W  $\times$  2CH into 8 $\Omega$  @0.38% THD+N for stereo

- Sound processing including:

- 20 bands parametric speaker EQ

- Volume control (+24dB ~ -103dB, 0.125dB/step),

- Dynamic range control (DRC)

- Dual band dynamic range control

- Power clipping

- 3D surround sound

- Channel mixing

- Noise gate with hysteresis window

- Bass/Treble tone control

- DC-blocking high-pass filter

- Anti-pop design

- Short circuit and over-temperature protection

- I2C control interface with selectable device address

- Support hardware and software reset

- Internal PLL

- LV Under-voltage shutdown and HV Under-voltage detection

- Power saving mode

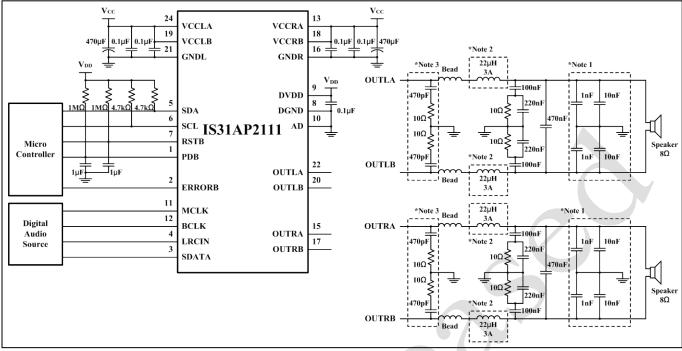

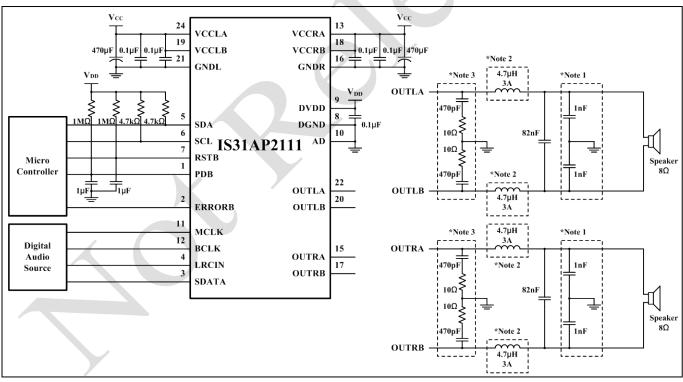

### TYPICAL APPLICATION CIRCUIT

Figure 1 Typical Application Circuit (for BTL Stereo, Single-ended Input)

Figure 2 Typical Application Circuit (Economic Type, Moderate EMI Suppression)

Note 1: These capacitors should be placed as close to speaker jack as possible, and their values should be determined according to EMI test results.

Note 2: When concerning about short-circuit protection, it is suggested using the choke with its  $I_{DC}$  larger than 5A.

Note 3: The snubber circuit can be removed while the V<sub>CC</sub>  $\leq$ 20V.

# **PIN CONFIGURATION**

| Package   | Pin Configuration (Top View)                                                                |                                                      |                                                                                                                                      |

|-----------|---------------------------------------------------------------------------------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| eTSSOP-24 | PDB<br>ERRORB<br>SDATA<br>LRCIN<br>SDA<br>SCL<br>RSTB<br>DGND<br>DVDD<br>AD<br>MCLK<br>BCLK | 2 2 3<br>3 4 2<br>5 6 1<br>7 1<br>8 1<br>9 1<br>10 1 | 24 VCCLA<br>23 NC<br>22 OUTLA<br>21 GNDL<br>20 OUTLB<br>19 VCCLB<br>18 VCCRB<br>17 OUTRB<br>16 GNDR<br>15 OUTRA<br>14 NC<br>13 VCCRA |

### **PIN DESCRIPTION**

| No.    | Pin         | Description                          | Characteristics                  |

|--------|-------------|--------------------------------------|----------------------------------|

| 1      | PDB         | Power down, low active.              | Schmitt trigger TTL input buffer |

| 2      | ERRORB      | Error status, low active.            | Open-drain output                |

| 3      | SDATA       | I2S serial audio data input.         | Schmitt trigger TTL input buffer |

| 4      | LRCIN       | Left/Right clock input (Fs).         | Schmitt trigger TTL input buffer |

| 5      | SDA         | I2C serial data.                     | Schmitt trigger TTL input buffer |

| 6      | SCL         | I2C serial clock input.              | Schmitt trigger TTL input buffer |

| 7      | RSTB        | Reset, low active.                   | Schmitt trigger TTL input buffer |

| 8      | DGND        | Digital ground.                      |                                  |

| 9      | DVDD        | Digital power.                       |                                  |

| 10     | AD          | I2C select address.                  | Schmitt trigger TTL input buffer |

| 11     | MCLK        | Master clock input.                  | Schmitt trigger TTL input buffer |

| 12     | BCLK        | Bit clock input (64F <sub>s</sub> ). | Schmitt trigger TTL input buffer |

| 13     | VCCRA       | Right channel supply A.              |                                  |

| 14, 23 | NC          | No connection.                       |                                  |

| 15     | OUTRA       | Right channel output A.              |                                  |

| 16     | GNDR        | Right channel ground.                |                                  |

| 17     | OUTRB       | Right channel output B.              |                                  |

| 18     | VCCRB       | Right channel supply B.              |                                  |

| 19     | VCCLB       | Left channel supply B.               | Z \ 7                            |

| 20     | OUTLB       | Left channel output B.               |                                  |

| 21     | GNDL        | Left channel ground.                 |                                  |

| 22     | OUTLA       | Left channel output A.               |                                  |

| 24     | VCCLA       | Left channel supply A.               |                                  |

|        | Thermal Pad | Connect to GND.                      |                                  |

#### **ORDERING INFORMATION** INDUSTRIAL RANGE: 0°C TO +70°C

| Order Part No.                        | Package              | QTY                  |

|---------------------------------------|----------------------|----------------------|

| IS31AP2111-ZLS1-TR<br>IS31AP2111-ZLS1 | eTSSOP-24, Lead-free | 2500/Reel<br>62/Tube |

Copyright © 2014 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products. Integrated Silicon Solution, Inc. does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not

authorized for use in such applications unless Integrated Silicon Solution, Inc. receives written assurance to its satisfaction, that: a.) the risk of injury or damage has been minimized;

b.) the user assume all such risks; and

c.) potential liability of Integrated Silicon Solution, Inc is adequately protected under the circumstances

### ABSOLUTE MAXIMUM RATINGS

| Supply for driver stage (VCCR, VCCL), V <sub>CC</sub>                              | -0.3V ~ +30V   |

|------------------------------------------------------------------------------------|----------------|

| Supply for digital circuit (DVDD), V <sub>DD</sub>                                 | -0.3V ~ +3.6V  |

| Input voltage (SDA,SCL,RSTB,PDB,ERRORB,MCLK,<br>BCLK,LRCIN,SDATA), V <sub>IN</sub> | -0.3V ~ +3.6V  |

| Thermal resistance, $\theta_{JA}$                                                  | 32.8°C/W       |

| Junction temperature range, T <sub>J</sub>                                         | 0°C ~ 150°C    |

| Storage temperature range, T <sub>STG</sub>                                        | −65°C ~ +150°C |

| ESD (HBM)<br>ESD (CDM)                                                             | TBD            |

#### Note:

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other condition beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **RECOMMENDED OPERATING CONDITIONS**

| Symbol          | Parameter                         | Condition | Min. | Тур. | Max. | Unit |

|-----------------|-----------------------------------|-----------|------|------|------|------|

| V <sub>cc</sub> | Supply for driver stage to VCCR/L |           | 10   |      | 26   | V    |

| V <sub>DD</sub> | Supply for digital circuit        |           | 3.15 |      | 3.45 | V    |

| TJ              | Junction operating temperature    |           | 0    |      | 125  | °C   |

| T <sub>A</sub>  | Ambient operating temperature     |           | 0    |      | 70   | °C   |

#### DC ELECTRICAL CHARACTERISTICS

$V_{CC}=24V$ ,  $T_A=25^{\circ}C$ ,  $R_L=8\Omega$  (unless otherwise noted).

| Symbol              | Parameter                                            | Condition                                                | Min. | Тур. | Max. | Unit |

|---------------------|------------------------------------------------------|----------------------------------------------------------|------|------|------|------|

| I <sub>PDH</sub>    | VCC supply current during power down                 | $V_{CC} = 24V$                                           |      | 4    | 200  | μA   |

| I <sub>PDL</sub>    | DVDD supply current during power down                | $V_{DD} = 3.3V$                                          |      | 3.6  | 10   | μA   |

| $V_{\text{UVH}}$    | Under voltage disabled (For DVDD)                    |                                                          |      | 2.9  |      | V    |

| $V_{\text{UVL}}$    | Under voltage enabled (For DVDD)                     |                                                          |      | 2.8  |      | V    |

| D                   | Static drain-to-source on-state resistor, PMOS       | )/ 24)/ L 500mA                                          |      | 245  |      |      |

| R <sub>DS(ON)</sub> | Static drain-to-source on-state resistor, NMOS       | -V <sub>CC</sub> =24V, I <sub>D</sub> = 500mA            |      | 150  |      | mΩ   |

| I <sub>SC</sub>     | Channel over-current protection                      | V <sub>CC</sub> =24V, I <sub>D</sub> = 500mA<br>(Note 1) |      | 5.1  |      | А    |

| Ŧ                   | Junction temperature for driver shutdown             |                                                          |      | 158  |      | °C   |

| Τ <sub>s</sub>      | Temperature hysteresis for recovery<br>from shutdown |                                                          |      | 33   |      | °C   |

| _ogic Ele           | ectrical Characteristics                             |                                                          |      |      | •    |      |

| V <sub>IH</sub>     | High level input voltage                             |                                                          | 2.0  |      |      | V    |

| VIL                 | Low level input voltage                              |                                                          |      |      | 0.8  | V    |

| V <sub>OH</sub>     | High level output voltage                            |                                                          | 2.4  |      |      | V    |

| V <sub>OL</sub>     | Low level output voltage                             |                                                          |      |      | 0.4  | V    |

| CIN                 | Input capacitance                                    |                                                          |      | 6.4  |      | pF   |

**Note 1:** Loudspeaker over-current protection is only effective when loudspeaker drivers are properly connected with external LC filters. Please refer to the application circuit example for recommended LC filter configuration.

# AC ELECTRICAL CHARACTERISTICS

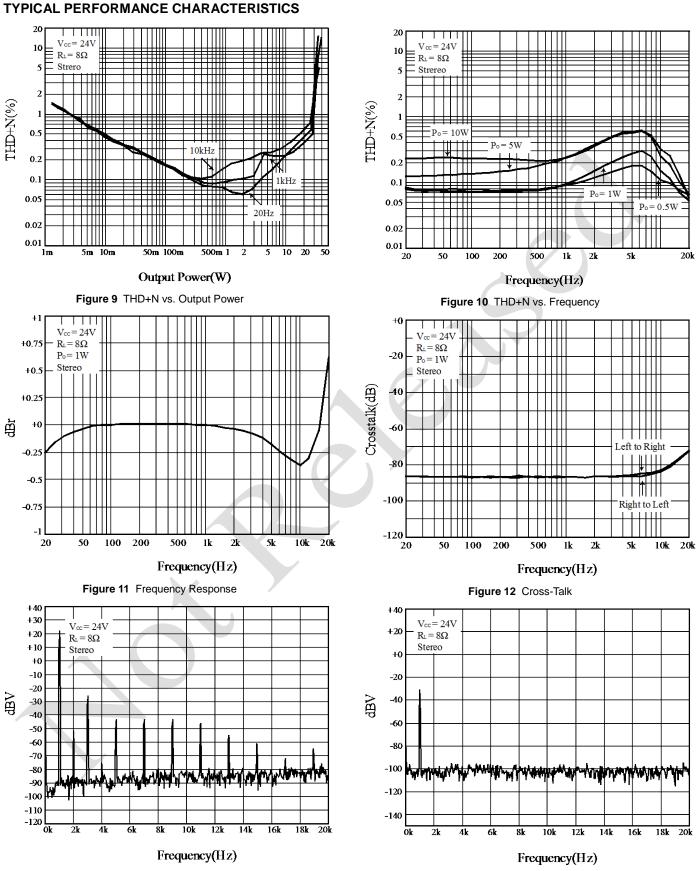

$T_A=25^{\circ}C$ ,  $V_{CC}=24V$ ,  $V_{DD}=3.3V$ ,  $f_S=48kHz$ ,  $R_L=8\Omega$  with passive LC lowpass filter (L= 22µH,  $R_{DC}=0.12\Omega$ , C=470nF), input is 1kHz sinewave, volume is 0dB unless otherwise specified.

| Symbol          | Parameter                            | Condition                                       | Min. | Тур. | Max. | Unit |

|-----------------|--------------------------------------|-------------------------------------------------|------|------|------|------|

| Po              | RMS output power                     | THD+N=0.38%, +8dB volume<br>(Note 2)            |      | 20   |      | W    |

| THD+N           | Total harmonic distortion +<br>noise | P <sub>o</sub> = 10W                            |      | 0.24 |      | %    |

| V <sub>NO</sub> | Output noise                         | 20Hz ~ 20kHz (Note 3)                           |      | 179  |      | μV   |

| SNR             | Signal-to-noise ratio                | +8dB volume, input level is -9dB<br>(Note 3)    |      | 99   |      | dB   |

| DR              | Dynamic range                        | +8dB volume, input level is -68dB<br>(Note 3)   |      | 104  |      | dB   |

| PSRR            | Power supply ripple rejection        | V <sub>RIPPLE</sub> = 1V <sub>RMS</sub> at 1kHz |      | -68  |      | dB   |

|                 | Channel separation                   | 1W @1kHz                                        |      | -85  |      | dB   |

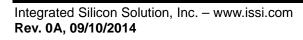

#### I2C DIGITAL INPUT SWITCHING CHARACTERISTICS (Note 4)

| Ourseland I          | Demonster                                                                       | Standar            | d Mode | Fast N               | lode | 11   |

|----------------------|---------------------------------------------------------------------------------|--------------------|--------|----------------------|------|------|

| Symbol               | Parameter                                                                       | Min.               | Max.   | Min.                 | Max. | Unit |

| f <sub>SCL</sub>     | Serial-Clock frequency                                                          | 0                  | 100    | 0                    | 400  | kHz  |

| t <sub>BUF</sub>     | Bus free time between a STOP and a START condition                              | 4.7                |        | 1.3                  |      | μs   |

| t <sub>HD, STA</sub> | Hold time (repeated) START condition                                            | 4.0                |        | 0.6                  |      | μs   |

| t <sub>SU, STA</sub> | Repeated START condition setup time                                             | 4.7                |        | 0.6                  |      | μs   |

| t <sub>SU, STO</sub> | STOP condition setup time                                                       | 4.0                |        | 0.6                  |      | μs   |

| t <sub>HD, DAT</sub> | Data hold time                                                                  | 0                  | 3.45   | 0                    | 0.9  | μs   |

| t <sub>SU, DAT</sub> | Data setup time                                                                 | 250                |        | 100                  |      | ns   |

| t <sub>LOW</sub>     | SCL clock low period                                                            | 4.7                |        | 1.3                  |      | μs   |

| t <sub>HIGH</sub>    | SCL clock high period                                                           | 4.0                |        | 0.6                  |      | μs   |

| t <sub>R</sub>       | Rise time of both SDA and SCL signals, receiving                                |                    | 1000   | 20+0.1C <sub>b</sub> | 300  | ns   |

| t <sub>F</sub>       | Fall time of both SDA and SCL signals, receiving                                |                    | 300    | 20+0.1C <sub>b</sub> | 300  | ns   |

| Cb                   | Capacitive load for each bus line                                               |                    | 400    |                      | 400  | pF   |

| V <sub>NL</sub>      | Noise margin at the low level for each connected device (including hysteresis)  | 0.1V <sub>DD</sub> |        | $0.1V_{DD}$          |      | V    |

| V <sub>NH</sub>      | Noise margin at the high level for each connected device (including hysteresis) | 0.2V <sub>DD</sub> |        | 0.2V <sub>DD</sub>   |      | V    |

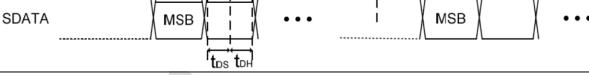

### **I2S DIGITAL INPUT SWITCHING CHARACTERISTICS (Note 4)**

| Symbol           | Parameter                         | Condition | Min.   | Тур. | Max.  | Unit |

|------------------|-----------------------------------|-----------|--------|------|-------|------|

| t <sub>LR</sub>  | LRCIN period (1/F <sub>s</sub> )  |           | 10.41  |      | 31.25 | μs   |

| t <sub>BL</sub>  | BCLK rising edge to LRCIN edge    |           | 50     |      |       | ns   |

| t <sub>LB</sub>  | LRCIN edge to BCLK rising edge    |           | 50     |      |       | ns   |

| t <sub>BCC</sub> | BCLK period (1/64F <sub>S</sub> ) |           | 162.76 |      | 488.3 | ns   |

| t <sub>BCH</sub> | BCLK pulse width high             |           | 81.38  |      | 244   | ns   |

| t <sub>BCL</sub> | CBLK pulse width low              |           | 81.38  |      | 244   | ns   |

| t <sub>DS</sub>  | SDATA set up time                 |           | 50     |      |       | ns   |

| t <sub>DH</sub>  | SDATA hold time                   |           | 50     |      |       | ns   |

Note 2: Thermal dissipation is limited by package type and PCB design. The external heat-sink or system cooling method should be adopted for maximum power output.

Note 3: Measured with A-weighting filter.

Note 4: Guaranteed by design.

Figure 3 I2C Timing

Figure 8 Timing Relationship (Using I2S format as an example)

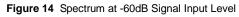

Figure 13 Spectrum at Peak SNR at -1dB Signal Input

35

40

45

50

#### **IS31AP2111** 100 100 Vcc=12V Vcc=12V 90 90 15V 80 80 243 2v=24V v. Vcc=22V Efficiency(%) 70 Efficiency(%) 70 =183 Vcc=18V 60 60 50 50 40 40 30 30 20 20 $R_L = 8\Omega$ $R_L = 8\Omega$ 10 10 Stereo Stereo 0 0 30 35 40 45 10 15 20 25 30 5 10 15 20 25 50 0 5 0 Output Power(W) Output Power(W) Figure 15 Efficiency vs. Total Output Power (Without Power Figure 16 Efficiency vs. Total Output Power (With Power Saving Saving Mode) Mode) 20 Т Switch Level: 26 10 $R_L = 8\Omega$ 12\ 5 Strero 2 THD+N(%) 1 0.5 24V 0.2 18V 0.1 22V0.05

10 20 50

5

2

0.02 0.01

10m 20m

50m 100m 200m

500m 1

Output Power(W)

Figure 17 THD+N vs. Output Power

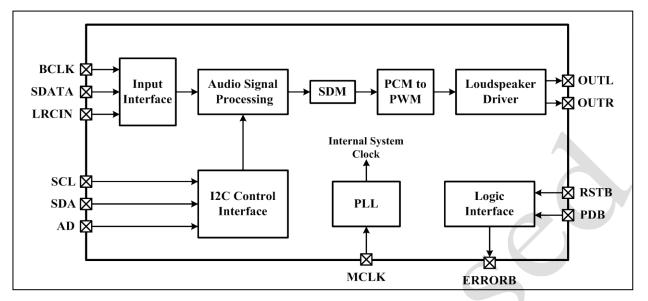

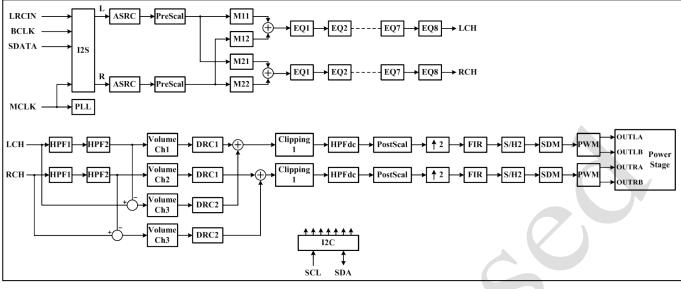

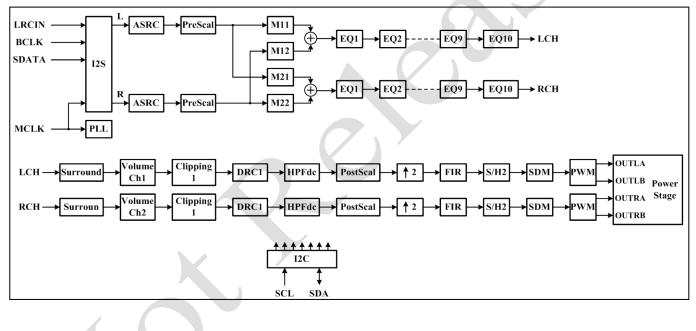

## FUNCTIONAL BLOCK DIAGRAM

## APPLICATIONS INFORMATION

### **OPERATION MODES**

### Without I2C Control

The default settings, Bass, Treble, EQ, Volume, DRC, ..., and PLL are applied to register table content when using IS31AP2111 without I2C control. The more information about default settings, please refer to the highlighted column of register table section.

#### With I2C Control

When using I2C control, user can program suitable parameters into IS31AP2111 for their specific applications. Please refer to the register table section to get the more detail.

#### INTERNAL PLL

IS31AP2111 has a built-in PLL internally. The MCLK/F<sub>S</sub> ratio will be fixed at 1024x, 512x, or 256x with a sample frequency of 48kHz, 96kHz, or 192kHz respectively. A career clock frequency is the frequency divided by 128 of master clock.

#### Table 1 MCLK/F<sub>s</sub> Ratio

| Fs      | MCLK Frequency |

|---------|----------------|

| 48kHz   | 49.152MHz      |

| 44.1kHz | 45.158MHz      |

| 32kHz   | 32.768MHz      |

#### DEFAULT VOLUME

The default volume level of IS31AP2111 is +1.675dB, the default volume register table setting is muted. Please give a de-mute command via I2C when the whole system is stable. About the more detailed information, please refer to the register table section.

#### RESET

When the RSTB pin is lowered, IS31AP2111 will clear the stored data and reset the register table to default values. IS31AP2111 will exit reset state at the 256<sup>th</sup> MCLK cycle after the RSTB pin is raised to high.

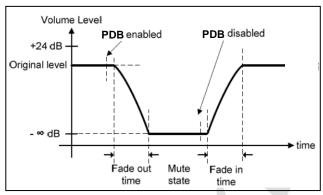

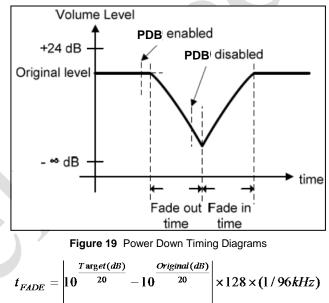

### POWER DOWN CONTROL

IS31AP2111 has a built-in volume fade-in/fade-out design for power down and mute function. The relative power down timing diagrams for loudspeakers are shown below.

The volume level will be decreased to - $\infty$ dB in several LRCIN cycles. Once the fade-out procedure is finished, IS31AP2111 will turn off the power stages, stop clock signals (MCLK, BCLK) from feeding into digital circuit and turn off the current of the internal analog circuits. After PDB pin is pulled low, IS31AP2111 needs t<sub>FADE</sub> time to finish the above works before entering power down state. Users can't program IS31AP2111 during power down state, but all the settings of register table will still be kept except that DVDD is removed.

If the power down function is disabled in the midway of the fade-out procedure, IS31AP2111 will also execute the fade-in procedure. In addition, IS31AP2111 will establish the analog circuits' bias current and feed the clock signals (MCLK, BCLK) into digital circuits. Then, IS31AP2111 will return to its normal operation without power down.

### **SELF-PROTECTION CIRCUITS**

IS31AP2111 has built-in protection circuits including thermal, short-circuit and under-voltage detection circuits.

#### **Thermal Protection**

When the internal junction temperature is higher than 158°C, power stages will be turned off and IS31AP2111 will return to normal operation once the temperature drops to 125°C. The temperature values may vary around 10%.

#### **Short-Circuit Protection**

The short-circuit protection circuit protects the output stage when the wires connected to loudspeakers are shorted to each other or GND/VDD. For normal 24V operations, the current flowing through the power stage will be less than 5.1A for stereo configuration. Otherwise, the short-circuit detectors may pull the ERRORB pin to DGND, disabling the output stages. When the over-temperature or short-circuit condition occurs, the open-drain ERRORB pin will be pulled low and latched into ERROR state.

Once the over-temperature or short-circuit condition is removed, IS31AP2111 will exit ERROR state when one of the following conditions is met: (1) RSTB pin is pulled low. (2) PDB pin is pulled low. (3) Master mute is enabled through the I2C interface.

#### **Under-Voltage Protection**

Once the  $V_{DD}$  voltage is lower than 2.8V, IS31AP2111 will turn off its loudspeaker power stages and cease the operation of digital processing circuits. When  $V_{DD}$  becomes larger than 2.9V, IS31AP2111 will return to normal operation.

#### ANTI-POP DESIGN

IS31AP2111 will generate appropriate control signals to suppress pop sounds during initial power on/off, power down/up, mute, and volume level changes.

#### **3D SURROUND SOUND**

IS31AP2111 provides the virtual surround sound technology with greater separation and depth voice quality for stereo signals.

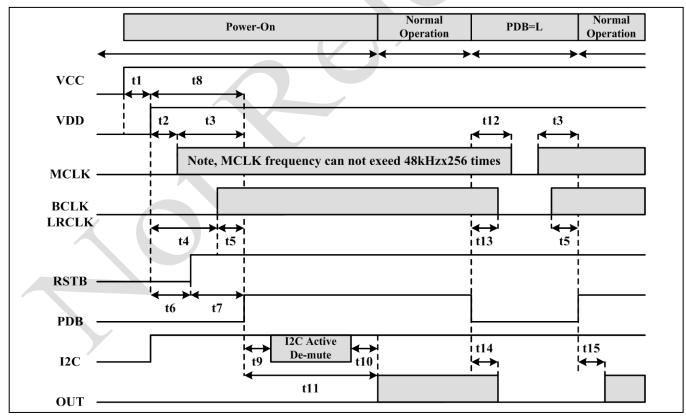

#### POWER ON SEQUENCE

Hereunder is IS31AP2111's power on sequence. Please note that IS31AP2111 default volume setting is muted initially. Please give a de-mute command via I2C when the whole system is stable.

Figure 20 Power On Sequence

# Table 2 Power On Sequence

| Symbol | Condition  | Min. | Max. | Unit |

|--------|------------|------|------|------|

| t1     |            | 0    | -    | ms   |

| t2     |            | 0    | -    | ms   |

| t3     |            | 10   | -    | ms   |

| t4     |            | 0    | -    | ms   |

| t5     |            | 10   | -    | ms   |

| t6     |            | 10   | -    | ms   |

| t7     |            | 0    | -    | ms   |

| t8     |            | 200  | -    | ms   |

| t9     |            | 20   | -    | ms   |

| t10    |            | -    | 0.1  | ms   |

| t11    |            | -    | 0.1  | ms   |

| t12    |            | 25   | -    | ms   |

| t13    |            | 25   | -    | ms   |

| t14    |            | -    | 22   | ms   |

| t15    | DEF=L or H | -    | 0.1  | ms   |

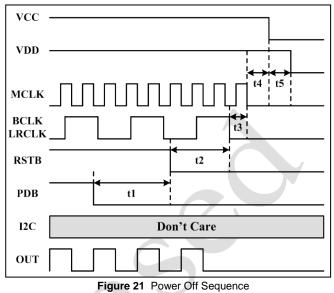

### POWER OFF SEQUENCE

Hereunder is IS31AP2111's power off sequence.

# Table 3 Power Off Sequence

| Table 5 Fower On Sequence |                                |  |  |

|---------------------------|--------------------------------|--|--|

| Symbol                    | Min.                           |  |  |

| t1                        | 35ms                           |  |  |

| t2                        | 0.1ms                          |  |  |

| t3                        | 0ms                            |  |  |

| t4                        | 1ms                            |  |  |

| t5                        | 1ms                            |  |  |

|                           | Symbol<br>t1<br>t2<br>t3<br>t4 |  |  |

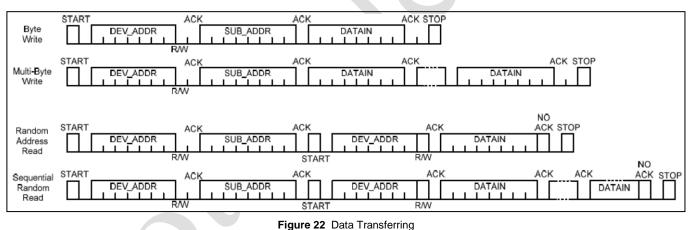

### **I2C-BUS TRANSFER PROTOCOL**

#### INTRODUCTION

IS31AP2111 employs I2C-bus transfer protocol. Two wires, serial data and serial clock carry information between the devices connected to the bus. Each device is recognized by a unique 7-bit address and can operate as either a transmitter or a receiver. The master device initiates a data transfer and provides the serial clock on the bus. IS31AP2111 is always an I2C slave device.

#### PROTOCOL

#### **START And STOP Condition**

START is identified by a high to low transition of the SDA signal. A START condition must precede any command for data transfer. A STOP is identified by a low to high transition of the SDA signal. A STOP condition terminates communication between IS31AP2111 and the master device on the bus. In both START and STOP, the SCL is stable in the high state.

#### **Data Validity**

The SDA signal must be stable during the high period of the clock. The high or low change of SDA

only occurs when SCL signal is low. IS31AP2111 samples the SDA signal at the rising edge of SCL signal.

#### **Device Addressing**

The master generates 7-bit address to recognize slave devices. When IS31AP2111 receives 7-bit address matched with 0110x00 (where x can be selected by external AD pin, respectively), IS31AP2111 will acknowledge at the 9th bit (the 8th bit is for R/W bit). The bytes following the device identification address are for IS31AP2111 internal sub-addresses.

#### Data Transferring

Each byte of SDA signaling must consist of 8 consecutive bits, and the byte is followed by an acknowledge bit. Data is transferred with MSB first, as shown in the figure below. In both write and read operations, IS31AP2111 supports both single-byte and multi-byte transfers. Refer to the figure below for detailed data-transferring protocol.

### **REGISTER DEFINITIONS**

The IS31AP2111's audio signal processing data flow is shown below. Users can control these functions by programming appropriate settings in the register table. In this section, the register table is summarized first. The definition of each register follows in the next section.

# Dual Band DRC Enable

#### **Dual Bands DRC Disable**

### Table 4 Register Function

| Address | Name                                       | Table | Default   |

|---------|--------------------------------------------|-------|-----------|

| 00h     | State Control 1 Register                   | 5     | 000x 0000 |

| 01h     | State Control 2 Register                   | 6     | xx00 0000 |

| 02h     | State Control 3 Register                   | 7     | xxxx 0000 |

| 03h     | Master Volume Control Register             | 8     | 0001 1000 |

| 04h~06h | Channel 1~3 Volume Register                | 9     | 0001 0100 |

| 07h,08h | Bass/Treble Tone Register                  | 10    | xxx1 0000 |

| 09h     | Reserved (Note)                            | -     | -         |

| 0Ah     | State Control 4 Register                   | 11    | 1001 0000 |

| 0Bh~0Ch | Channel 1~2 Configuration Register         | 12    | xxx1 0000 |

| 0Dh     | Reserved                                   | -     | -         |

| 0Eh     | DRC Limiter Attack/Release Rate Register   | 13    | 0110 1010 |

| 0Fh~10h | Reserved (Note)                            |       | -         |

| 11h     | State Control 5 Register                   | 14    | xx11 x010 |

| 12h     | VCC Under Voltage Selection Register       | 15    | 1xxx 0001 |

| 13h     | Noise Gate Gain Register                   | 16    | xxx0 xx00 |

| 14h     | Coefficient RAM Base Address Register      | 17    | x000 0000 |

| 15h~23h | User-Defined Coefficients Register         | 18~22 | -         |

| 24h     | Coefficients Control Register              | 23    | xxxx 0000 |

| 25h~29h | Reserved (Note)                            | -     | -         |

| 2Ah     | Power Saving Mode Switching Level Register | 24    | 0000 1101 |

| 2Bh     | Volume Fine Tune Register                  | 25    | 0011 1111 |

Note: The reserved registers are not allowed to write any bits in them, or the IC will be abnormal.

#### Table 5 00h State Control 1 Register

| Bit     | D7:D5  | D4       | D3     |

|---------|--------|----------|--------|

| Name    | IF     | -        | PWML_X |

| Default | 000    | x        | 0      |

| Bit     | D2     | D1       | D0     |

| Name    | PWMR_X | LV_UVSEL | LREXC  |

| Default | 0      | 0        | 0      |

IS31AP2111 supports multiple serial data input formats including I2S, Left-alignment and Rightalignment. These formats are selected by users via D7~D5 of address 00h. The left/right channels can be exchanged to each other by programming to address 00h/D0, LREXC.

| IF  | Input Format              |

|-----|---------------------------|

| 000 | I2S 16-24 bits            |

| 001 | Left-alignment 16-24 bits |

| 010 | Right-alignment 16 bits   |

| 011             | Right-alignment 18 bits      |

|-----------------|------------------------------|

| 100             | Right-alignment 20 bits      |

| 101             | Right-alignment 24 bits      |

| Others          | Not available                |

| <b>PWML_X</b>   | OUTLA/B exchange             |

| 0               | No exchange                  |

| 1               | Exchange                     |

| <b>PWMR_X</b>   | OUTRA/B exchange             |

| 0               | No exchange                  |

| 1               | Exchange                     |

| <b>LV_UVSEL</b> | LV Under Voltage Selection   |

| 0               | 2.8V                         |

| 1               | 3.1V                         |

| <b>LREXC</b>    | Left/Right Channel Exchanged |

| 0               | No exchange                  |

| 1               | Left/Right exchange          |

#### Table 6 01h State Control 2 Register

| Bit     | D7:D6 | D5:D4 | D3:D0 |

|---------|-------|-------|-------|

| Name    | -     | FS    | PMF   |

| Default | XX    | 00    | 0000  |

IS31AP2111 has a built-in PLL which can be bypassed by pulling the PLL pin High. When PLL is bypassed, IS31AP2111 only supports 1024x, 512x and 256x MCLK/Fs ratio for Fs is 32/44.1/48kHz, 64/88.2/96kHz, and 128/176.4/192kHz respectively. When PLL is enabled, multiple MCLK/Fs ratios are supported. Detail setting is shown in the following table.

- FS Sampling Frequency

- 00 32/44.1/48kHz

- 01 64/88.2/96kHz

- 1x 128/176.4/192kHz

- PMF Multiple MCLK/FS Ratio Setting (PLL is not bypassed)

- 0000 1024x(FS=00)/ 512x(FS=01)/ 256x(FS=1x)

- 0001 64x

- 0010 128x

- 0011 192x

- 0100 256x

- 0101 384x (Not available when FS=1x)

- 0110 512x (Not available when FS=1x)

- 0111 576x (Not available when FS=01,1x)

- 1000 768x (Not available when FS=01,1x)

- 1001 1024x (Not available when FS=01,1x)

Others Not available

Note: The FS × PMF should be lower than

49.152MHz, or the system will be error.

### Table 7 02h State Control 3 Register

| Bit     | D7:D4 | D3   | D2:D0   |

|---------|-------|------|---------|

| Name    | -     | MUTE | CM1:CM3 |

| Default | хххх  | 0    | 000     |

IS31AP2111 has mute function including master mute and channel mute. When master mute is enabled, all 3 processing channels are muted. User can mute these 3 channels individually by channel mute. When the mute function is enabled or disabled, the fade-out or fade-in process will be initiated.

#### MUTE Master Mute

- 0 All channel not muted

- 1 All channel muted

CMx Channel x Mute

- 0 Channel x not muted

- 1 Channel x muted

#### Table 8 03h Master Volume Control Register

| Bit     | D7:D0     |

|---------|-----------|

| Name    | MV        |

| Default | 0001 1000 |

|         |           |

IS31AP2111 supports both master-volume (03h Register) and channel-volume control (04h, 05h and 06h Registers) modes. Both volume control settings range from +12dB ~ -103dB and 0.5dB per step. Note that the master volume control is added to the individual channel volume control as the total volume control. For example, if the master volume level is set at, Level A (in dB unit) and the channel volume level is set at Level B (in dB unit), the total volume control setting is equal to Level A plus with Level B. - 103dB  $\leq$  Total volume (Level A + Level B)  $\leq$  +24dB.

| MV<br>0000 0000        | Master Volume<br>+12.0dB |

|------------------------|--------------------------|

| 0000 0001<br>0000 0010 | +11.5dB<br>+11.0dB       |

| 0001 1000              | 0dB                      |

| 1110 0110              | -103.0dB                 |

| 1110 0111              | -∞                       |

| Others                 | -∞                       |

#### Table 9 04h~06h Channel 1~3 Volume Registers

| Bit     | D7:D0     |

|---------|-----------|

| Name    | CxV       |

| Default | 0001 0100 |

| <b>CxV</b><br>0000 0000<br>0000 0001 | Channel x Volume<br>+12.0dB<br>+11.5dB |

|--------------------------------------|----------------------------------------|

| <br>0001 0100                        | +2dB                                   |

| <br>1110 0110<br>1110 0111<br>Others | -103.0dB<br>-∞<br>-∞                   |

#### Table 10 07h/08h Bass/Treble Tone Registers

| Bit     | D7:D5 | D6:D0   |

|---------|-------|---------|

| Name    | -     | BTC/TTC |

| Default | XXX   | 10000   |

Last two sets of EQ can be programmed as bass/treble tone boost and cut. When, 0Ah Register, D6, BTE is set to high, the EQ-8 and EQ-9 will

perform as bass and treble respectively. The -3dB corner frequency of bass is 360Hz, and treble is 7kHz. The gain range for both filters is +12db ~ - 12dB with 1dB per step.

| <b>BTC/TTC</b> 00000 | Bass/Treble Gain Setting<br>+12dB |

|----------------------|-----------------------------------|

| <br>00100<br>00101   | +12dB<br>+11dB                    |

| <br>10000<br>10001   | 0dB<br>-1dB                       |

| <br>111xx            | -12dB                             |

#### Table 11 0Ah State Control 4 Register

| Bit     | D7   | D6  | D5         | D4  |

|---------|------|-----|------------|-----|

| Name    | SRBP | BTE | TBDRCE     | NGE |

| Default | 1    | 0   | 0          | 1   |

| Bit     | D3   | D2  | D1         | D0  |

| Dit     | 20   | 22  | <b>_</b> . | 20  |

| Name    | EQL  | PSL | DSPB       | HPB |

The IS31AP2111 provides several DSP setting as following.

- 0 Surround enable

- 1 Surround bypass

#### **BTE** Bass/Treble Selection Bypass

- 0 Bass/treble disable

- 1 Bass/treble enable

#### TBDRCE Two Band DRC Enable

- 0 Two band DRC disable

- 1 Two band DRC enable

# NGE Noise Gate Enable

- 0 Noise gate disable

- 1 Noise gate enable

# EQL EQ Link

- 0 Each channel uses individual EQ

- 1 Channel-2 uses channel-1 EQ

# PSL Post-Scale Link

- 0 Each channel uses individual post-scale

- 1 Use channel-1 post-scale

# DSPB EQ Bypass

- 0 EQ enable

- 1 EQ bypass

| HPB | DC Blocking HPF Bypass |

|-----|------------------------|

| 0   | HPF DC enable          |

- 1 HPF DC bypass

- I HPF DC bypass

####

| Bit     | D7:D5   | D4     | D3     |

|---------|---------|--------|--------|

| Name    | -       | CxDRCM | CxPCBP |

| Default | XXX     | 1      | 0      |

| Bit     | D2      | D1     | D0     |

| Name    | CxDRCBP |        | CxVBP  |

| Default | 0       | x      | 0      |

The IS31AP2111 can configure each channel to enable or bypass DRC and channel volume and select the limiter set. IS31AP2111 support two mode of DRC, RMS and PEAK detection which can be selected via D4.

| <b>CxDRCM</b><br>0<br>1  | Channel 1/2 DRC Mode<br>Peak detection<br>RMS detection                                        |

|--------------------------|------------------------------------------------------------------------------------------------|

| CxPCBP                   | Channel 1/2 Power Clipping Bypass                                                              |

| 0                        | Channel 1/2 PC enable                                                                          |

| 1                        | Channel 1/2 PC bypass                                                                          |

| <b>CxDRCBP</b><br>0<br>1 | Channel 1/2 DRC Bypass<br>Channel 1/2 DRC enable<br>Channel 1/2 DRC bypass                     |

|                          | Channel 1/2 Volume Bypass<br>el 1/2's master volume operation<br>el 1/2's master volume bypass |

# Table 13 0Eh DRC Limiter Attack/Release Rate Register

| Bit     | D7:D5 | D6:D0    |

|---------|-------|----------|

| Name    | LA    | LR       |

| Default | 0110  | 1010     |

|         |       | <u> </u> |

The IS31AP2111 defines a set of limiter. The attack/release rates are defines as following table.

| DRC Attack Rate |

|-----------------|

| 3dB/ms          |

| 2.667dB/ms      |

|                 |

| 0010 | 2.182dB/ms  |

|------|-------------|

| 0011 | 1.846dB/ms  |

| 0100 | 1.333dB/ms  |

| 0101 | 0.889dB/ms  |

| 0110 | 0.4528dB/ms |

| 0111 | 0.2264dB/ms |

| 1000 | 0.15dB/ms   |

| 1001 | 0.1121dB/ms |

| 1010 | 0.0902dB/ms |

| 1011 | 0.0752dB/ms |

| 1100 | 0.0645dB/ms |

1101 0.0563dB/ms 1110 0.0501dB/ms

1111 0.0451dB/ms

| LR   | DRC Release Rate |

|------|------------------|

| 0000 | 0.5106dB/ms      |

| 0001 | 0.1371dB/ms      |

| 0010 | 0.0743dB/ms      |

| 0011 | 0.0499dB/ms      |

| 0100 | 0.0360dB/ms      |

| 0101 | 0.0299dB/ms      |

| 0110 | 0.0264dB/ms      |

| 0111 | 0.0208dB/ms      |

| 1000 | 0.0198dB/ms      |

| 1001 | 0.0172dB/ms      |

| 1010 | 0.0147dB/ms      |

| 1011 | 0.0137dB/ms      |

| 1100 | 0.0134dB/ms      |

| 1101 | 0.0117dB/ms      |

| 1110 | 0.0112dB/ms      |

| 1111 | 0.0104dB/ms      |

### Table 14 11h State Control 5 Register

| Bit     | D7:D6        | D5      |   | D4     |     | D3    |

|---------|--------------|---------|---|--------|-----|-------|

| Name    | -            | SW_RSTE | 3 | VUV_F/ | ٩DE | -     |

| Default | хх           | 1       |   | 1      |     | х     |

| Bit     |              | D2      | - | D1     |     | D0    |

| Name    | DIS_MCLK_DET |         | Q | T_EN   | PW  | M_SEL |

| Default | 0            |         |   | 1      |     | 0     |

The IS31AP2111 provides several DSP setting as following.

| SW_RSTB | Software Reset         |  |  |

|---------|------------------------|--|--|

| 0       | Reset                  |  |  |

| 1       | Normal operation       |  |  |

|         | Low Linder Voltogo For |  |  |

| LVUV_FADE | Low Under Voltage Fade |

|-----------|------------------------|

| 0         | No fade                |

| 1         | fade                   |

### DIS\_MCLK\_DET Disable MCLK Detect Circuit

| 0            | Enable MCLK detect circuit  |

|--------------|-----------------------------|

| 1            | Disable MCLK detect circuit |

| <b>QT_EN</b> | Power Saving Mode           |

| 0            | Disable                     |

| 1            | Enable                      |

| PWM SEI      | PWM Modulation              |

| PVVIVI_SEL | Prvivi iviodulation |

|------------|---------------------|

| 0          | Qua-ternary         |

| 1          | Ternary             |

# Table 1512hVCC Under VoltageSelectionRegister

| Bit     | D7       | D6:D4 | D3:D0    |

|---------|----------|-------|----------|

| Name    | Dis_HVUV | -     | HV_UVSEL |

| Default | 1        | ххх   | 0001     |

IS31AP2111 can disable HV under voltage detection via D7. IS31AP2111 support multi-level HV under voltage detection via D3~ D0, using this function, IS31AP2111 will fade out signal to avoid pop sounds if high voltage supply disappear before low voltage supply.

| <b>Dis_HVUV</b><br>0<br>1 | Disable HV Under Voltage Selection<br>Enable<br>Disable |

|---------------------------|---------------------------------------------------------|

| HV_UVSEL                  | UV Detection Level                                      |

| 0000                      | 8.2V                                                    |

| 0001                      | 9.7V                                                    |

| 0011                      | 13.2V                                                   |

| 0100                      | 15.5V                                                   |

| 1100                      | 19.5V                                                   |

|                           |                                                         |

#### Table 16 13h Noise Gate Gain Register

9.7V

Others

| Bit     | D7:D5 | D4          |

|---------|-------|-------------|

| Name    | -     | DIS_NG_FADE |

| Default | xxx   | 0           |

| Bit     | D3:D2 | D1:D0       |

| Name    | -     | NG_GAIN     |

| Default | ХХ    | 00          |

IS31AP2111 provide noise gate function if receiving 2048 signal sample points smaller than noise gate attack level. User can change noise gate gain via D1~ D0. When noise gate function occurs, input signal will multiply noise gate gain (x1/8, x1/4 x1/2, x0). User can select fade out or not via D4.

| DIS_ | <b>IG_FADE</b> Disable Noise Gate Fade |

|------|----------------------------------------|

| 0    | Fade                                   |

| 1             | No fade                 |

|---------------|-------------------------|

| NG_GAIN<br>00 | Noise Gate Gain<br>x1/8 |

| 01            | x1/4                    |

| 10            | x1/2                    |

| 11            | Mute                    |

###

| Bit     | D7 | D6:D0    |

|---------|----|----------|

| Name    | -  | CFA      |

| Default | х  | 000 0000 |

An on-chip RAM in IS31AP2111 stores user-defined EQ and mixing coefficients. The content of this coefficient RAM is indirectly accessed via coefficient registers, which consist of one base address register (14h), five sets of registers (15h ~ 23h) of three consecutive 8-bit entries for each 24-bit coefficient, and one control register (24h) to control access of the coefficients in the RAM.

#### CFA Coefficient RAM Base Address

# Table 1815h~17hUser-DefinedCoefficientsRegisters

| (Top/Middle/Bottom | 9 hits of | coofficients | A1)       |

|--------------------|-----------|--------------|-----------|

|                    | 0-0113 01 | coentcients  | <b>יי</b> |

| Name C1B  | Bit     | ) |

|-----------|---------|---|

|           | Name    |   |

| Default - | Default |   |

(Top/Middle/Bottom 8-bits of coefficients A2)

| Bit     | D7:D0 |

|---------|-------|

| Name    | C2B   |

| Default | _     |

Table 20 1Bh~1DhUser-Defined CoefficientsRegisters

(Top/Middle/Bottom 8-bits of coefficients A1)

| Bit     | D7:D0 |

|---------|-------|

| Name    | C3B   |

| Default | -     |

# Table 21 1Eh~20hUser-Defined CoefficientsRegisters

# (Top/Middle/Bottom 8-bits of coefficients B2)

| Bit     | D7:D0 |

|---------|-------|

| Name    | C4B   |

| Default | -     |

# (Top/Middle/Bottom 8-bits of coefficients A0)

| Bit     | D7:D0 |

|---------|-------|

| Name    | C5B   |

| Default |       |

# Table 23 24h Coefficients Control Register

| Bit     | D7:D4 | D3 | D2 | D1 | D0 |

|---------|-------|----|----|----|----|

| Name    | -     | RA | R1 | WA | W1 |

| Default | XXXX  | 0  | 0  | 0  | 0  |

### RA Enable Of Reading A Set Of Coefficients From RAM

- 0 Read complete

- Read enable

1

- R1 Enable Of Reading A Single Coefficients

From RAM

0 Read complete

- 1 Read enable

- WA Enable Of Writing A Set Of Coefficients To RAM

- 0 Write complete

- 1 Write enable

- W1 Enable Of Writing A Single Coefficient To RAM

- 0 Write complete

- 1 Write enable

# Table 242AhPower Saving Mode SwitchingLevel Register

| Bit     | D7:D5        | D4:D0       |

|---------|--------------|-------------|

| Name    | QT_SW_WINDOW | QT_SW_LEVEL |

| Default | 000          | 01101       |

|         |              |             |

If the PWM exceeds the programmed switching power level (default 26×40ns), the modulation algorithm will change from quaternary into power saving mode. It results in higher power efficiency during larger power output operations. If the PWM drops below the programmed switching power level power saving mode hysteresis window, the

modulation algorithm will change back to quaternary modulation.

|       | V_WINDOW<br>esis Window<br>2<br>3<br>4<br>5<br>6<br>7<br>8 | Power Saving Mode |

|-------|------------------------------------------------------------|-------------------|

| 111   | 9                                                          |                   |

|       | 0                                                          |                   |

| QT_SV | /_LEVEL                                                    | Switching Level   |

| 00000 | 4                                                          |                   |

| 00001 | 4                                                          |                   |

| 00010 | 6                                                          |                   |

|       |                                                            |                   |

| 01101 | 26                                                         |                   |

11111 62

#### Table 25 2Bh Volume Fine Tune Register

| Bit     | D7:D6 | D5:D4  | D3:D2  | D1:D0 |

|---------|-------|--------|--------|-------|

| Name    | MV_FT | C1V_FT | C2V_FT | -     |

| Default | 00    | 11     | 11     | 11    |

IS31AP2111 supports both master-volume fine tune and channel-volume control fine tune modes. Both volume control settings range from 0dB ~ -0.375dB and 0.125dB per step. Note that the master volume fine tune is added to the individual channel volume fine tune as the total volume fine tune.

| MV_FT<br>00<br>01<br>10<br>11 | Master Volume Fine Tune<br>0dB<br>-0.125dB<br>-0.25dB<br>-0.375dB |

|-------------------------------|-------------------------------------------------------------------|

| C1V_FT                        | Channel 1 Volume Fine Tune                                        |

| 00                            | 0dB                                                               |

| 01                            | -0.125dB                                                          |

| 10                            | -0.25dB                                                           |

| 11                            | -0.375dB                                                          |

| C2V_FT                        | Channel 2 Volume Fine Tune                                        |

| 00                            | 0dB                                                               |

| 01                            | -0.125dB                                                          |

| 10                            | -0.25dB                                                           |

| 11                            | -0.375dB                                                          |

#### RAM ACCESS

The procedure to read/write coefficient(s) from/to RAM is as followings:

#### Read A Single Coefficient From RAM:

- 1. Write 7-bit of address to I2C address-0X14

- 2. Write 1 to R1 bit in address-0X24

Read top 8-bits of coefficient in I2C address-0X15

Read middle 8-bits of coefficient in I2C address-0X16

5. Read bottom 8-bits of coefficient in I2C address-0X17

### Read A Set Of Coefficients From RAM:

1. Write 7-bits of address to I2C address-0X14

2. Write 1 to RA bit in address-0X24

3. Read top 8-bits of coefficient A1 in I2C address-0X15

4. Read middle 8-bits of coefficient A1in I2C address-0X16

5. Read bottom 8-bits of coefficient A1 in I2C address-0X17

6. Read top 8-bits of coefficient A2 in I2C address-0X18

7. Read middle 8-bits of coefficient A2 in I2C address-0X19

8. Read bottom 8-bits of coefficient A2 in I2C address-0X1A

9. Read top 8-bits of coefficient B1 in I2C address-0X1B

10. Read middle 8-bits of coefficient B1 in I2C address-0X1C

11. Read bottom 8-bits of coefficient B1 in I2C address-0X1D

12. Read top 8-bits of coefficient B2 in I2C address-0X1E

13. Read middle 8-bits of coefficient B2 in I2C address-0X1F

14. Read bottom 8-bits of coefficient B2 in I2C address-0X20

15. Read top 8-bits of coefficient A0 in I2C address-0X21

16. Read middle 8-bits of coefficient A0 in I2C address-0X22

17. Read bottom 8-bits of coefficient A0 in I2C address-0X23

#### Write A Single Coefficient From RAM:

1. Write 7-bis of address to I2C address-0X14

Write top 8-bits of coefficient in I2C address-0X15

Write middle 8-bits of coefficient in I2C address-

0X16 4. Write bottom 8-bits of coefficient in I2C address-

0X17

5. Write 1 to W1 bit in address-0X24

### Write A Set Of Coefficients From RAM:

Write 7-bits of address to I2C address-0X14

Write top 8-bits of coefficient A1 in I2C address-0X15

3. Write middle 8-bits of coefficient A1 in I2C address-0X16

4. Write bottom 8-bits of coefficient A1 in I2C address-0X17

5. Write top 8-bits of coefficient A2 in I2C address-  $0 \\ X18$

6. Write middle 8-bits of coefficient A2 in I2C address-0X19

7. Write bottom 8-bits of coefficient A2 in I2C address-0X1A

8. Write top 8-bits of coefficient B1 in I2C address-0 X1B

9. Write middle 8-bits of coefficient B1 in I2C address-0X1C

10. Write bottom 8-bits of coefficient B1 in I2C address-0X1D

11. Write top 8-bits of coefficient B2 in I2C address-0X1E

12. Write middle 8-bits of coefficient B2 in I2C address-0X1F

13. Write bottom 8-bits of coefficient B2 in I2C address-0X20

14. Write top 8-bits of coefficient A0 in I2C address-0X21

15. Write middle 8-bits of coefficient A0 in I2C address-0X22

16. Write bottom 8-bits of coefficient A0 in I2C address-0X23

17. Write 1 to WA bit in address-0X24

Note: the read and write operation on RAM coefficients works only if LRCIN (Pin 15) switching on rising edge. And, before each writing operation, it is necessary to read the address-0X24 to confirm whether RAM is writable current in first. If the logic of W1 or WA is high, the coefficient writing is prohibited.

# USER-DEFINED EQUALIZER

The IS31AP2111 provides 18 parametric Equalizer (EQ). Users can program suitable coefficients via I2C control interface to program the required audio band frequency response for every EQ. The transfer function

$$H_{(z)} = \frac{A_0 + A_1 z^{-1} + A_2 z^{-2}}{1 + B_1 z^{-1} + B_2 z^{-2}}$$

The data format of 2's complement binary code for EQ coefficient is 3.21. i.e., 3-bits for integer (MSB is the sign bit) and 21-bits for mantissa. Each coefficient range is from 0x800000 (-4) to 0x7FFFFF (+3.999999523). These coefficients are stored in User Defined RAM and are referenced in following manner:

CHxEQyA0=A0 CHxEQyA1=A1 CHxEQyA2=A2 CHxEQyB1=-B1 CHxEQyB2=-B2

Where x and y represents the number of channel and the band number of EQ equalizer.

All user-defined filters are path-through, where all coefficients are defaulted to 0 after being powered up, except the A0 that is set to 0x200000 which represents 1.

# MIXER

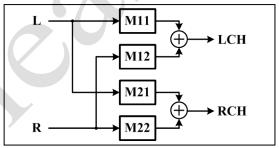

The IS31AP2111 provides mixers to generate the extra audio source from the input left and right channels. The coefficients of mixers are defined in range from 0x800000 (-1) to 0x7FFFF (0.9999998808). The function block diagram is as following figure:

Figure 23 Mixer Function Block Diagram

### PRE-SCALE

For each audio channel, IS31AP2111 can scale input signal level prior to EQ processing which is realized by a 24-bit signed fractional multiplier. The pre-scale factor, ranging from -1 (0x800000) to 0.9999998808 (0x7FFFF), for this multiplier, can be loaded into RAM. The default values of the prescaling factors are set to 0x7FFFFF. Programming of RAM is described in RAM access.

# POST-SCALE

The IS31AP2111 provides an additional multiplication after equalizing and before interpolation stage, which is realized by a 24-bit signed fractional multiplier. The post-scaling factor, ranging from -1 (0x800000) to 0.9999998808 (0x7FFFFF), for this multiplier, can be loaded into RAM. The default values of the post-scaling factors are set to 0x7FFFFF. All channels can use the channel-1 post-scale factor by setting the post-scale link. Programming of RAM is described in RAM access.

## POWER CLIPPING

The IS31AP2111 provides power clipping function to avoid excessive signal that may destroy loud speaker. The power clipping level is defined by 24bit representation and is stored in RAM address 0X6F and 0X70. The following table shows the power clipping level's numerical representation.

| Max.<br>Amplitude      | dB | Linear                     | Decimal         | Hex<br>(3.21 Format) |

|------------------------|----|----------------------------|-----------------|----------------------|

| V <sub>cc</sub>        | 0  | 1                          | 2097152         | 200000               |

| V <sub>CC</sub> ×0.707 | -3 | 0.707                      | 1484574         | 16A71E               |

| $V_{CC} \times 0.5$    | -6 | 0.5                        | 1048576         | 100000               |

| V <sub>CC</sub> ×L     | x  | L=<br>10 <sup>(x/20)</sup> | D=<br>2097152×L | H=<br>dec2hex(D)     |

**Table 26** Sample Calculation For Power Clipping

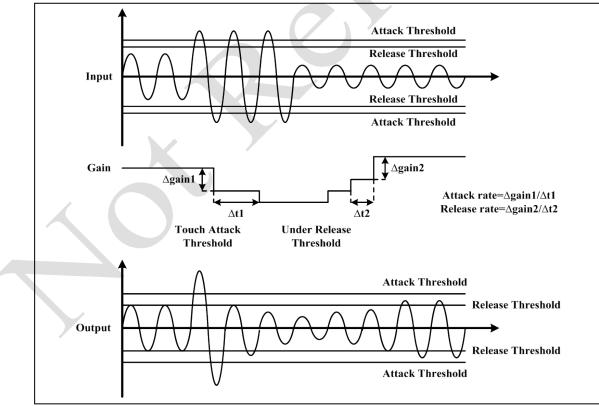

# ATTACK THRESHOLD FOR DYNAMIC RANGE CONTROL (DRC)

The IS31AP2111 provides dynamic range control (DRC) function. When the input exceeds the programmable attack threshold value, the output power will be limited by this threshold power level via gradual gain reduction. Attack threshold is defined

by 24-bit representation and is stored in RAM address 0X71 and 0X72.

# RELEASE THRESHOLD FOR DYNAMIC RANGE CONTROL (DRC)

After IS31AP2111 has reached the attack threshold, its output power will be limited to that level. The output power level will be gradually adjusted to the programmable release threshold level. Release threshold is defined by 24-bit representation and is stored in RAM address 0X73 and 0X74. The following table shows the attack and release threshold's numerical representation.

| Power                        | dB | Linear                     | Decimal         | Hex<br>(3.21 Format) |

|------------------------------|----|----------------------------|-----------------|----------------------|

| (V <sub>CC</sub> ^2)/R       | 0  | 1                          | 2097152         | 200000               |

| (V <sub>CC</sub> ^2)/2R      | -3 | 0.5                        | 1048576         | 100000               |

| (V <sub>CC</sub> ^2)/4R      | -6 | 0.25                       | 524288          | 80000                |

| (V <sub>CC</sub> ^2)/R<br>×L | x  | L=<br>10 <sup>(x/10)</sup> | D=<br>2097152×L | H=<br>dec2hex(D)     |

**Table 27** Sample Calculation For Attack AndRelease Threshold

To best illustrate the dynamic range control, please refer to the following figure.

Figure 24 Attack And Release Threshold

### NOISE GATE ATTACK LEVEL

When both left and right signals have 2048 consecutive sample points less than the programmable noise gate attack level, the audio signal will multiply noise gate gain, which can be set at x1/8, x1/4, x1/2, or zero if the noise gate function is enabled. Noise gate attack level is defined by 24bit representation and is stored in RAM address 0X75.

### NOISE GATE RELEASE LEVEL

After entering the noise gating status, the noise gain will be removed whenever IS31AP2111 receives any input signal that is more than the noise gate release level. Noise gate release level is defined by 24-bit representation and is stored in RAM address 0X76. The following table shows the noise gate attack and release threshold level's numerical representation.

| Table 28         Sample Calculation For Noise Gate Attack |        |         |     |  |  |  |

|-----------------------------------------------------------|--------|---------|-----|--|--|--|

| And Release                                               | Level  |         |     |  |  |  |

| Input                                                     | Linear | Decimal | Hex |  |  |  |

| Input<br>Amplitude | Linear                     | Decimal         | Hex<br>(1.23 Format) |

|--------------------|----------------------------|-----------------|----------------------|

| 0dB                | 1                          | 8388607         | 7FFFF                |

| -100dB             | 10 <sup>-5</sup>           | 83              | 53                   |

| -110dB             | 10 <sup>-5.5</sup>         | 26              | 1A                   |

| xdB                | L=<br>10 <sup>(x/20)</sup> | D=<br>2097152×L | H=<br>dec2hex(D)     |

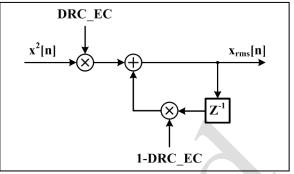

#### DRC ENERGY COEFFICIENT

Figure 25 Digital Processing Of Calculating RMS Signal Power

The above figure illustrates the digital processing of calculating RMS signal power. In this processing, a DRC energy coefficient is required, which can be programmed for different frequency range. Energy coefficient is defined by 24-bit representation and is stored in RAM address 0X77 and 0X78. The following table shows the DRC energy coefficient numerical representation.

| Table 29 Sample Calculation For DRC Energy |  |

|--------------------------------------------|--|

| Coefficient                                |  |

| Coomoloni                 |       |                            |                 |                      |

|---------------------------|-------|----------------------------|-----------------|----------------------|

| DRC Energy<br>Coefficient | dB    | Linear                     | Decimal         | Hex<br>(1.23 Format) |

| 1                         | 0     | 1                          | 8388607         | 7FFFF                |

| 1/256                     | -48.2 | 1/256                      | 524288          | 80000                |

| 1/1024                    | -60.2 | 1/1024                     | 131072          | 20000                |

| L                         | х     | L=<br>10 <sup>(x/20)</sup> | D=<br>2097152×L | H=<br>dec2hex(D)     |

# THE USER DEFINED RAM

The contents of user defined RAM is represented in following table.

### Table 30 User Defined RAM

| Address | Name             | Coefficient | Default  | Address | Name             | Coefficient | Default  |

|---------|------------------|-------------|----------|---------|------------------|-------------|----------|

| 0x00    | Channel 1<br>EQ1 | CH1EQ1A1    | 0x000000 | 0x32    | Channel 2<br>EQ1 | CH2EQ1A1    | 0x000000 |

| 0x01    |                  | CH1EQ1A2    | 0x000000 | 0x33    |                  | CH2EQ1A2    | 0x000000 |

| 0x02    |                  | CH1EQ1B1    | 0x000000 | 0x34    |                  | CH2EQ1B1    | 0x000000 |

| 0x03    |                  | CH1EQ1B2    | 0x000000 | 0x35    |                  | CH2EQ1B2    | 0x000000 |

| 0x04    |                  | CH1EQ1A0    | 0x200000 | 0x36    |                  | CH2EQ1A0    | 0x200000 |

| 0x05    |                  | CH1EQ2A1    | 0x000000 | 0x37    | Channel 2<br>EQ2 | CH2EQ2A1    | 0x000000 |

| 0x06    |                  | CH1EQ2A2    | 0x000000 | 0x38    |                  | CH2EQ2A2    | 0x000000 |

| 0x07    | Channel 1<br>EQ2 | CH1EQ2B1    | 0x000000 | 0x39    |                  | CH2EQ2B1    | 0x000000 |

| 0x08    |                  | CH1EQ2B2    | 0x000000 | 0x3A    |                  | CH2EQ2B2    | 0x000000 |

| 0x09    |                  | CH1EQ2A0    | 0x200000 | 0x3B    |                  | CH2EQ2A0    | 0x200000 |

| 0x0A    |                  | CH1EQ3A1    | 0x000000 | 0x3C    | Channel 2<br>EQ3 | CH2EQ3A1    | 0x000000 |

| 0x0B    |                  | CH1EQ3A2    | 0x000000 | 0x3D    |                  | CH2EQ3A2    | 0x000000 |

| 0x0C    | Channel 1<br>EQ3 | CH1EQ3B1    | 0x000000 | 0x3E    |                  | CH2EQ3B1    | 0x000000 |

| 0x0D    | LQU              | CH1EQ3B2    | 0x000000 | 0x3F    |                  | CH2EQ3B2    | 0x000000 |

| 0x0E    |                  | CH1EQ3A0    | 0x200000 | 0x40    |                  | CH2EQ3A0    | 0x200000 |

| 0x0F    |                  | CH1EQ4A1    | 0x000000 | 0x41    | Channel 2<br>EQ4 | CH2EQ4A1    | 0x000000 |

| 0x10    |                  | CH1EQ4A2    | 0x000000 | 0x42    |                  | CH2EQ4A2    | 0x000000 |

| 0x11    | Channel 1<br>EQ4 | CH1EQ4B1    | 0x000000 | 0x43    |                  | CH2EQ4B1    | 0x000000 |

| 0x12    | LQT              | CH1EQ4B2    | 0x000000 | 0x44    |                  | CH2EQ4B2    | 0x000000 |

| 0x13    |                  | CH1EQ4A0    | 0x200000 | 0x45    |                  | CH2EQ4A0    | 0x200000 |

| 0x14    |                  | CH1EQ5A1    | 0x000000 | 0x46    |                  | CH2EQ5A1    | 0x000000 |

| 0x15    |                  | CH1EQ5A2    | 0x000000 | 0x47    | Channel 2<br>EQ5 | CH2EQ5A2    | 0x000000 |

| 0x16    | Channel 1<br>EQ5 | CH1EQ5B1    | 0x000000 | 0x48    |                  | CH2EQ5B1    | 0x000000 |

| 0x17    |                  | CH1EQ5B2    | 0x000000 | 0x49    |                  | CH2EQ5B2    | 0x000000 |

| 0x18    |                  | CH1EQ5A0    | 0x200000 | 0x4A    |                  | CH2EQ5A0    | 0x200000 |

| 0x19    | Channel 1<br>EQ6 | CH1EQ6A1    | 0x000000 | 0x4B    | Channel 2<br>EQ6 | CH2EQ6A1    | 0x000000 |

| 0x1A    |                  | CH1EQ6A2    | 0x000000 | 0x4C    |                  | CH2EQ6A2    | 0x000000 |

| 0x1B    |                  | CH1EQ6B1    | 0x000000 | 0x4D    |                  | CH2EQ6B1    | 0x000000 |

| 0x1C    |                  | CH1EQ6B2    | 0x000000 | 0x4E    |                  | CH2EQ6B2    | 0x000000 |

| 0x1D    |                  | CH1EQ6A0    | 0x200000 | 0x4F    |                  | CH2EQ6A0    | 0x200000 |

## Table 30 User Defined RAM (Continues)

| Address | Name              | Coefficient | Default  | Address | Name              | Coefficient | Default  |

|---------|-------------------|-------------|----------|---------|-------------------|-------------|----------|

| 0x1E    | Channel 1<br>EQ7  | CH1EQ7A1    | 0x000000 | 0x50    | Channel 2<br>EQ7  | CH2EQ7A1    | 0x000000 |

| 0x1F    |                   | CH1EQ7A2    | 0x000000 | 0x51    |                   | CH2EQ7A2    | 0x000000 |

| 0x20    |                   | CH1EQ7B1    | 0x000000 | 0x52    |                   | CH2EQ7B1    | 0x000000 |

| 0x21    |                   | CH1EQ7B2    | 0x000000 | 0x53    |                   | CH2EQ7B2    | 0x000000 |

| 0x22    |                   | CH1EQ7A0    | 0x200000 | 0x54    |                   | CH2EQ7A0    | 0x200000 |

| 0x23    |                   | CH1EQ8A1    | 0x000000 | 0x55    | Channel 2<br>EQ8  | CH2EQ8A1    | 0x000000 |

| 0x24    | Channel 1<br>EQ8  | CH1EQ8A2    | 0x000000 | 0x56    |                   | CH2EQ8A2    | 0x000000 |

| 0x25    |                   | CH1EQ8B1    | 0x000000 | 0x57    |                   | CH2EQ8B1    | 0x000000 |

| 0x26    |                   | CH1EQ8B2    | 0x000000 | 0x58    |                   | CH2EQ8B2    | 0x000000 |

| 0x27    |                   | CH1EQ8A0    | 0x200000 | 0x59    |                   | CH2EQ8A0    | 0x200000 |

| 0x28    | Channel 1<br>EQ9  | CH1EQ9A1    | 0x000000 | 0x5A    | Channel 2<br>EQ9  | CH2EQ9A1    | 0x000000 |

| 0x29    |                   | CH1EQ9A2    | 0x000000 | 0x5B    |                   | CH2EQ9A2    | 0x000000 |

| 0x2A    |                   | CH1EQ9B1    | 0x000000 | 0x5C    |                   | CH2EQ9B1    | 0x000000 |

| 0x2B    |                   | CH1EQ9B2    | 0x000000 | 0x5D    |                   | CH2EQ9B2    | 0x000000 |

| 0x2C    |                   | CH1EQ9A0    | 0x200000 | 0x5E    |                   | CH2EQ9A0    | 0x200000 |

| 0x2D    | Channel 1<br>EQ10 | CH3EQ1A1    | 0x000000 | 0x5F    | Channel 2<br>EQ10 | CH3EQ2A1    | 0x000000 |

| 0x2E    |                   | CH3EQ1A2    | 0x000000 | 0x60    |                   | CH3EQ2A2    | 0x000000 |

| 0x2F    |                   | CH3EQ1B1    | 0x000000 | 0x61    |                   | CH3EQ2B1    | 0x000000 |

| 0x30    |                   | CH3EQ1B2    | 0x000000 | 0x62    |                   | CH3EQ2B2    | 0x000000 |

| 0x31    |                   | CH3EQ1A0    | 0x200000 | 0x63    |                   | CH3EQ2A0    | 0x200000 |

# Table 30 User Defined RAM (Continues)

| Address                      | Name                          | Coefficient | Default  |  |

|------------------------------|-------------------------------|-------------|----------|--|

| 0x64                         | Channel 1 Mixer1              | M11         | 0x7FFFFF |  |

| 0x65                         | Channel 1 Mixer2              | M12         | 0x000000 |  |

| 0x66                         | Channel 2 Mixer1              | M21         | 0x000000 |  |

| 0x67                         | Channel 2 Mixer2              | M22         | 0x7FFFFF |  |

| 0x68~0x69                    | Reserve                       | Reserve     |          |  |

| 0x6A                         | Channel 1 Prescale            | C1PRS       | 0x7FFFFF |  |

| 0x6B                         | Channel 2 Prescale            | C2PRS       | 0x7FFFFF |  |

| 0x6C                         | Channel 1 Postscale           | C1POS       | 0x7FFFFF |  |

| 0x6D                         | Channel 2 Postscale           | C2POS       | 0x7FFFFF |  |

| 0x6E                         | Reserve                       | Reserve     |          |  |

| 0x6F                         | CH1.2 Power Clipping          | PC1         | 0x200000 |  |

| 0x70                         | Reserve                       | Reserve     | · ·      |  |

| 0x71                         | CH1.2 DRC Attack Threshold    | DRC1_ATH    | 0x200000 |  |

| 0x72                         | CH1.2 DRC Release Threshold   | DRC1_RTH    | 0x80000  |  |

| 0x73                         | CH3 DRC Attack Threshold      | DRC2_ATH    | 0x200000 |  |

| 0x74                         | CH3 DRC Release Threshold     | DRC2_RTH    | 0x80000  |  |

| 0x75                         | Noise Gate Attack Level       | NGAL        | 0x0001A  |  |

| 0x76                         | 0x76 Noise Gate Release Level |             | 0x000053 |  |

| 0x77                         | DRC1 Energy Coefficient       | DRC1_EC     | 0x8000   |  |

| 0x78 DRC2 Energy Coefficient |                               | DRC2_EC     | 0x2000   |  |

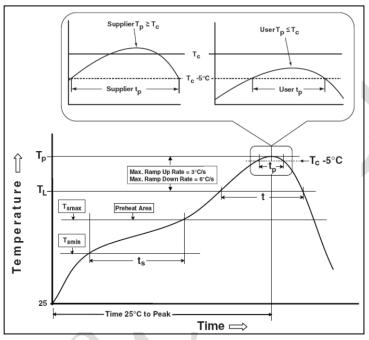

### **CLASSIFICATION REFLOW PROFILES**

| Profile Feature                                                                                               | Pb-Free Assembly                 |  |  |

|---------------------------------------------------------------------------------------------------------------|----------------------------------|--|--|

| <b>Preheat &amp; Soak</b><br>Temperature min (Tsmin)<br>Temperature max (Tsmax)<br>Time (Tsmin to Tsmax) (ts) | 150°C<br>200°C<br>60-120 seconds |  |  |

| Average ramp-up rate (Tsmax to Tp)                                                                            | 3°C/second max.                  |  |  |

| Liquidous temperature (TL)<br>Time at liquidous (tL)                                                          | 217°C<br>60-150 seconds          |  |  |

| Peak package body temperature (Tp)*                                                                           | Max 260°C                        |  |  |

| Time (tp)** within 5°C of the specified classification temperature (Tc)                                       | Max 30 seconds                   |  |  |

| Average ramp-down rate (Tp to Tsmax)                                                                          | 6°C/second max.                  |  |  |

| Time 25°C to peak temperature                                                                                 | 8 minutes max.                   |  |  |

Figure 26 Classification Profile

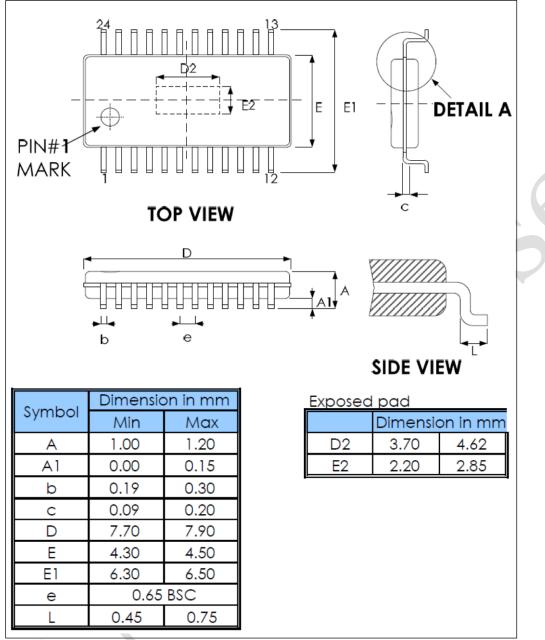

# PACKAGE INFORMATION

#### eTSSOP-24

Note: All dimensions in millimeters unless otherwise stated.