# DATA BULLETIN

# CMX980A

# Digital Radio Baseband Processor

#### **Advance Information**

#### **Features**

- RRC Filters for both Tx and Rx

- π/4 DQPSK Modulation

- 2 x 14-Bit Resolution Sigma Delta D-A

- 2 x 16-Bit Resolution Sigma Delta A-D

- 4 x 10-Bit D-A and 4 Input 10-Bit A-D

- Transmit Output Power Control

- Low Power 3.0 5.5Volt Operation

- Effective Power down Modes

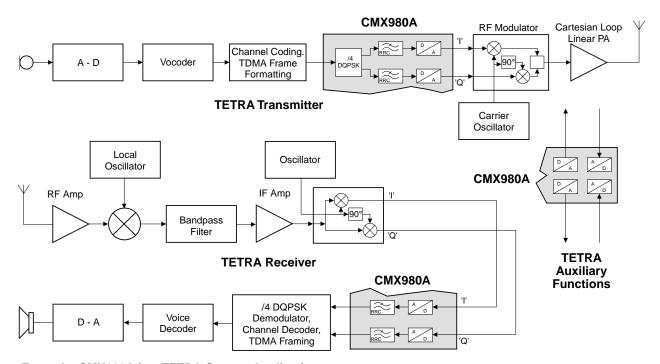

Example: CMX980A in a TETRA System Application

This device is intended to act as an interface between the analog and digital sections of a Digital Radio System, and performs many critical and DSP-intensive functions. The chip is designed with the necessary capability to meet the requirements for use in both mobile and base station applications in Terrestrial Trunked Radio (TETRA) systems, but the architecture is sufficiently flexible to allow use in other systems.

The transmit path comprises all the circuitry required to convert digital data into suitably filtered analog I and Q signals for subsequent up-conversion and transmission. This includes digital control of the output amplitudes, digital control of the output offsets and fully programmable digital filters: default coefficients provide the RRC response required for TETRA.

The receive section accepts differential analog I and Q signals at baseband and converts these into a suitably filtered digital form for further processing and data extraction. A facility is provided for digital offset correction and the digital filters are fully programmable with default coefficients providing the RRC response required for TETRA.

Auxiliary DAC and ADC functions are included for the control and measurement of the RF section of the radio system. This may include AFC, AGC, RSSI, or may be used as part of the control system for a Cartesian Loop.

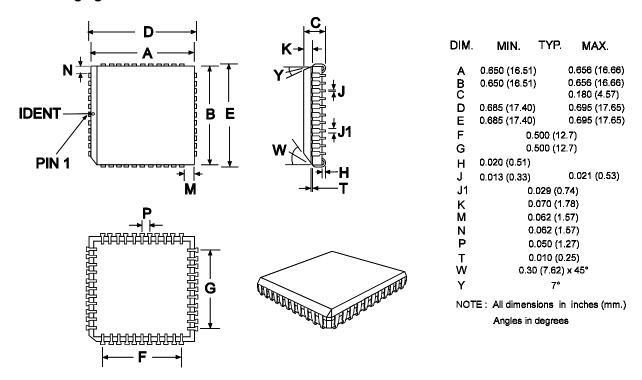

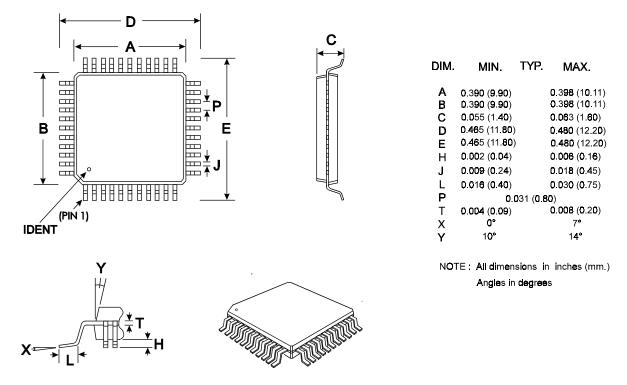

The CMX980A requires a 3.0V to 5.0V supply and is available in the following packages: 44-pin PLCC (CMX980AL6) and 44-pin QFP (CMX980AL7).

# **CONTENTS**

| Se | Section Page                             |                                                 |                                                       |    |  |  |  |  |

|----|------------------------------------------|-------------------------------------------------|-------------------------------------------------------|----|--|--|--|--|

| 1  | Blo                                      | ck Dia                                          | agram                                                 | 4  |  |  |  |  |

| 2  | Signal List5                             |                                                 |                                                       |    |  |  |  |  |

| 3  | Ext                                      | ernal (                                         | Components                                            | 7  |  |  |  |  |

|    | 3.1                                      | Rx In                                           | 7                                                     |    |  |  |  |  |

|    | 3.2                                      | Tx O                                            | utputs                                                | 7  |  |  |  |  |

| 4  | Ger                                      | neral D                                         | Description                                           | 8  |  |  |  |  |

|    | 4.1                                      | 4.1 Connection and Decoupling of Power Supplies |                                                       |    |  |  |  |  |

|    | 4.2 Programmable FIR Filter Architecture |                                                 |                                                       |    |  |  |  |  |

|    | 4.3                                      | Tx Da                                           | ata Path                                              | 9  |  |  |  |  |

|    |                                          | 4.3.1                                           | Modulator                                             | 10 |  |  |  |  |

|    |                                          | 4.3.2                                           | Filters                                               | 10 |  |  |  |  |

|    |                                          | 4.3.3                                           | Gain Multiplier                                       | 10 |  |  |  |  |

|    |                                          | 4.3.4                                           | Offset Adjust                                         | 10 |  |  |  |  |

|    |                                          | 4.3.5                                           | Sigma-Delta D-A Converters and Reconstruction Filters | 10 |  |  |  |  |

|    |                                          | 4.3.6                                           | Phase Pre-distortion                                  | 10 |  |  |  |  |

|    |                                          | 4.3.7                                           | Ramping Output Amplitude                              | 10 |  |  |  |  |

|    |                                          | 4.3.8                                           | Symbol Clock Phase Adjustment                         | 11 |  |  |  |  |

|    |                                          | 4.3.9                                           | 1.5.3.9 Direct Write to Tx 79-tap Filter Input        |    |  |  |  |  |

|    |                                          | 4.3.10                                          | •                                                     |    |  |  |  |  |

|    | 4.4                                      | Rx Da                                           | ata Path                                              |    |  |  |  |  |

|    |                                          | 4.4.1                                           | Anti-Alias Filtering and Sigma-Delta A-D Converters   |    |  |  |  |  |

|    |                                          | 4.4.2                                           | Rx FIR Filters                                        |    |  |  |  |  |

|    |                                          | 4.4.3                                           | Offset Registers                                      |    |  |  |  |  |

|    |                                          | 4.4.4                                           | I and Q Channel Gain                                  |    |  |  |  |  |

|    | 4.5                                      |                                                 | iary Circuits                                         |    |  |  |  |  |

|    |                                          | 4.5.1                                           | 10-Bit DACs                                           |    |  |  |  |  |

|    |                                          | 4.5.2                                           | 10-Bit ADC                                            |    |  |  |  |  |

|    |                                          | 4.5.3                                           | Power Ramping and Control                             |    |  |  |  |  |

|    | 4.6                                      |                                                 | Function                                              |    |  |  |  |  |

|    | 4.7                                      |                                                 | I Interface                                           |    |  |  |  |  |

|    |                                          | 4.7.1                                           | Command Interface                                     |    |  |  |  |  |

|    |                                          | 4.7.2                                           | Command Read Interface                                |    |  |  |  |  |

|    |                                          | 4.7.3                                           | Rx Data Interface                                     |    |  |  |  |  |

|    |                                          | 4.7.4                                           | Transmission of Data                                  |    |  |  |  |  |

|    |                                          | 4.7.5                                           | Confficient Moment                                    |    |  |  |  |  |

|    |                                          | 4.7.6                                           | Coefficient Memory                                    |    |  |  |  |  |

|    |                                          | 4.7.7                                           | Auto Power Save Mode                                  | 18 |  |  |  |  |

|   | 4.8 | Regis    | ster Description                                                              | 18 |

|---|-----|----------|-------------------------------------------------------------------------------|----|

|   |     | 4.8.1    | Key to Register Map                                                           | 18 |

|   |     | 4.8.2    | Register Reset State                                                          | 18 |

|   |     | 4.8.3    | Register and Access Point Summary                                             | 19 |

| 5 | Apr | olicatio | on Notes                                                                      | 64 |

| _ | 5.1 |          | upt Handling                                                                  |    |

|   |     | 5.1.1    | Tx FIFO status interrupts                                                     |    |

|   |     | 5.1.2    | Tx/Rx FIR filter tap overflow and Gain, Phase and Offset overflow interrupts  |    |

|   |     | 5.1.3    | Rx ADC I and Q channel overflow - due to excessive input amplitude interrupts |    |

|   | 5.2 | Confi    | guration                                                                      | 64 |

|   | 5.3 | Rese     | t                                                                             | 64 |

|   | 5.4 | Deve     | loping and Optimizing FIR Filter Coefficients                                 | 64 |

|   |     | 5.4.1    | Tx Path Details                                                               |    |

|   |     | 5.4.2    | Rx Path Details                                                               | 66 |

|   |     | 5.4.3    | General Procedure for Reconfiguring the CMX980A FIR Filters                   | 67 |

|   | 5.5 | Rece     | iver Re-Synchronization                                                       | 68 |

|   | 5.6 | Guide    | elines for use of Power Save Modes                                            | 69 |

|   |     | 5.6.1    | Auxiliary Section                                                             | 69 |

|   |     | 5.6.2    | Tx Section                                                                    | 69 |

|   |     | 5.6.3    | Rx Section                                                                    | 69 |

|   |     | 5.6.4    | Tx and Rx Bias Section                                                        | 69 |

|   |     | 5.6.5    | Serial Interface Section                                                      | 69 |

| 6 | Per | forma    | nce Specification                                                             | 70 |

|   | 6.1 | Electi   | rical Performance                                                             | 70 |

|   |     | 6.1.1    | Absolute Maximum Ratings                                                      | 70 |

|   |     | 6.1.2    | Operating Limits                                                              |    |

|   |     | 6.1.3    | Operating Characteristics                                                     |    |

|   | 6.2 | Packa    | aging                                                                         | 82 |

MX-COM, Inc. reserves the right to change specifications at any time and without notice.

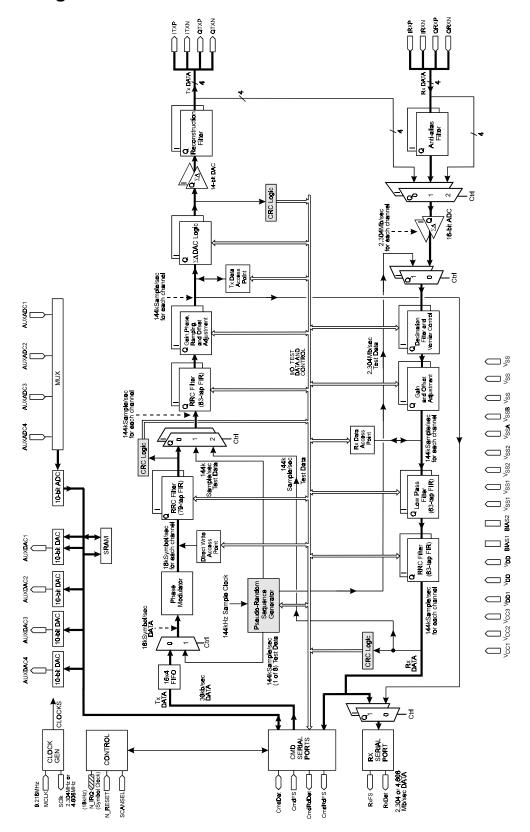

# 1 Block Diagram

Figure 1: Block Diagram

# 2 Signal List

| Pack                | ages               | Si               | gnal           | Description                                                                                                                              |

|---------------------|--------------------|------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 44-pin PLCC<br>(L6) | 44-pin QFP<br>(L7) |                  |                | ·                                                                                                                                        |

| Pin No.             | Pin No.            | Name             | Type           |                                                                                                                                          |

| 15                  | 9                  | MCLK             | input          | Master clock input (typically 9.216MHz)                                                                                                  |

| 16                  | 10                 | SCIk             | output         | Serial interface clock                                                                                                                   |

| 17                  | 11                 | CmdDat           | bi-directional | Command serial interface Data                                                                                                            |

| 18                  | 12                 | CmdFS            | input          | Command serial interface Frame                                                                                                           |

| 19                  | 13                 | CmdRdDat         | output         | Command serial interface Read Data                                                                                                       |

| 20                  | 14                 | CmdRdFS          | output         | Command serial interface Read Frame                                                                                                      |

| 11                  | 5                  | RxDat            | output         | Receive serial interface Data                                                                                                            |

| 12                  | 6                  | RxFS             | output         | Receive serial interface Strobe                                                                                                          |

| 23                  | 17                 | N_IRQ            | output         | Interrupt request                                                                                                                        |

| 14                  | 8                  | N_RESET          | input          | Chip Reset                                                                                                                               |

| 24                  | 18                 | ~                | input          | For manufacturers use only. Connect this pin to V <sub>SS</sub> .                                                                        |

| 25                  | 19                 | ITXP             | output         | Transmit "I" channel, positive output                                                                                                    |

| 26                  | 20                 | ITXN             | output         | Transmit "I" channel, negative output                                                                                                    |

| 30                  | 24                 | QTXP             | output         | Transmit "Q" channel, positive output                                                                                                    |

| 29                  | 23                 | QTXN             | output         | Transmit "Q" channel, negative output                                                                                                    |

| 42                  | 36                 | IRXP             | input          | Receive "I" channel, positive input                                                                                                      |

| 41                  | 35                 | IRXN             | input          | Receive "I" channel, negative input                                                                                                      |

| 38                  | 32                 | QRXP             | input          | Receive "Q" channel, positive input                                                                                                      |

| 37                  | 31                 | QRXN             | input          | Receive "Q" channel, negative input                                                                                                      |

| 43                  | 37                 | AUXADC1          | input          | Auxiliary ADC channel 1                                                                                                                  |

| 44                  | 38                 | AUXADC2          | input          | Auxiliary ADC channel 2                                                                                                                  |

| 1                   | 39                 | AUXADC3          | input          | Auxiliary ADC channel 3                                                                                                                  |

| 2                   | 40                 | AUXADC4          | input          | Auxiliary ADC channel 4                                                                                                                  |

| 10                  | 4                  | AUXDAC1          | output         | Auxiliary DAC channel 1                                                                                                                  |

| 9                   | 3                  | AUXDAC2          | output         | Auxiliary DAC channel 2                                                                                                                  |

| 8                   | 2                  | AUXDAC3          | output         | Auxiliary DAC channel 3                                                                                                                  |

| 7                   | 1                  | AUXDAC4          | output         | Auxiliary DAC channel 4                                                                                                                  |

| 36                  | 30                 | BIAS1            | bi-directional | Analog bias level. This pin should be decoupled to V <sub>SSB</sub> .                                                                    |

| 35                  | 29                 | BIAS2            | bi-directional | DAC reference level. This pin should normally be connected to V <sub>SSB</sub> .                                                         |

| 32                  | 26                 | V <sub>CC1</sub> | Power          | I Channel analog positive supply rail. This pin should be decoupled to V <sub>SS1</sub> .                                                |

| 33                  | 27                 | V <sub>CC2</sub> | Power          | Q Channel analog positive supply rail.<br>This pin should be decoupled to V <sub>SS2</sub> .                                             |

| 34                  | 28                 | V <sub>CC3</sub> | Power          | Analog Bias positive supply rail. Levels and voltages are dependent upon this supply. This pin should be decoupled to V <sub>SSB</sub> . |

| 6                   | 44                 | V <sub>DD1</sub> | Power          | Auxiliary analog positive supply rail. This pin should be decoupled to V <sub>SSA</sub> .                                                |

| Packa               | ages               | Si               | gnal   | Description                                                                     |  |  |

|---------------------|--------------------|------------------|--------|---------------------------------------------------------------------------------|--|--|

| 44-pin PLCC<br>(L6) | 44-pin QFP<br>(L7) |                  |        |                                                                                 |  |  |

| Pin No.             | Pin No.            | Name             | Туре   |                                                                                 |  |  |

| 3, 21               | 41, 15             | V <sub>DD</sub>  | Power  | Digital positive supply rail. This pin should be decoupled to V <sub>SS</sub> . |  |  |

| 27, 40              | 21, 34             | V <sub>SS1</sub> | Ground | I Channel analog negative supply rail.                                          |  |  |

| 28, 39              | 22, 33             | V <sub>SS2</sub> | Ground | Q Channel analog negative supply rail.                                          |  |  |

| 31                  | 25                 | V <sub>SSB</sub> | Ground | Analog Bias negative supply rail.                                               |  |  |

| 5                   | 43                 | V <sub>SSA</sub> | Ground | Auxiliary analog negative supply rail.                                          |  |  |

| 4, 13, 22           | 42, 7, 16          | V <sub>SS</sub>  | Ground | Primary digital negative supply rail.                                           |  |  |

Table 1: Signal List

## 3 External Components

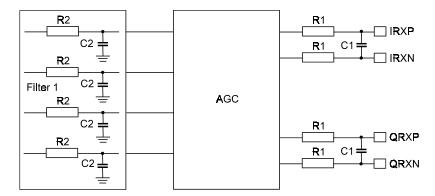

#### 3.1 Rx Inputs

When using the internal anti-alias filter, the following is recommended:

Figure 2: Recommended External Components - Rx Input

Example Values: MCLK = 9.216MHz

| R1 | = | 220Ω                                                                          |

|----|---|-------------------------------------------------------------------------------|

| R2 | = | 1.2kΩ                                                                         |

| C1 | = | 1.5nF (R1, C1 precise values are not critical, -3dB at 240kHz)                |

| C2 | = | 3.9nF (R2 x C2 product, giving –3dB at 32kHz, should be preserved within 10%) |

Table 2: Recommended External Components - Rx Inputs

The RC stage formed by R2 and C2 combined with the internal anti-alias filter and Rx FIRs gives a good approximation to the desired filter characteristics and near-constant group delay over the passband. When not using the internal anti-alias filter, it is suggested that the user should follow the guidelines in Section 4.4.1. In both cases, there should be at least one filter pole close to the chip inputs.

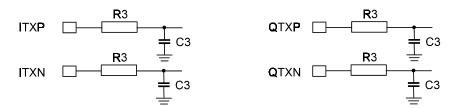

#### 3.2 Tx Outputs

Figure 3: Recommended External Components - Tx Outputs

Example Values: MCLK = 9.216MHz

|   | R3 | II | 6.2kΩ                                                                       |

|---|----|----|-----------------------------------------------------------------------------|

| Ī | C3 |    | 1nF (R3 x C3 product, giving –3dB at 25kHz, should be preserved within 10%) |

**Table 3: Recommended External Components - Tx Outputs**

The RC stage formed by R3 and C3 combined with the internal reconstruction filter and the Tx FIRs gives a good approximation to the desired filter characteristics and near-constant group delay over the passband. Decoupling capacitors should be employed as detailed in Section 4.4.1.

When the default master clock frequency is not used, the R2 x C2 and R3 x C3 products may be scaled with MCLK, but care should be taken to ensure that FIR filter coefficients are designed to compensate for any amplitude and phase distortion due to both on and off-chip filter components. This compensation is included in the default filter coefficients. See Section 5.4 for further details.

# 4 General Description

The device is designed to operate at a master clock frequency of 9.216MHz, but may be used over the full specified frequency range provided that guidelines in this document are followed. Many internal functions scale with the master clock frequency, which is referred to as "MCLK" where this is the case.

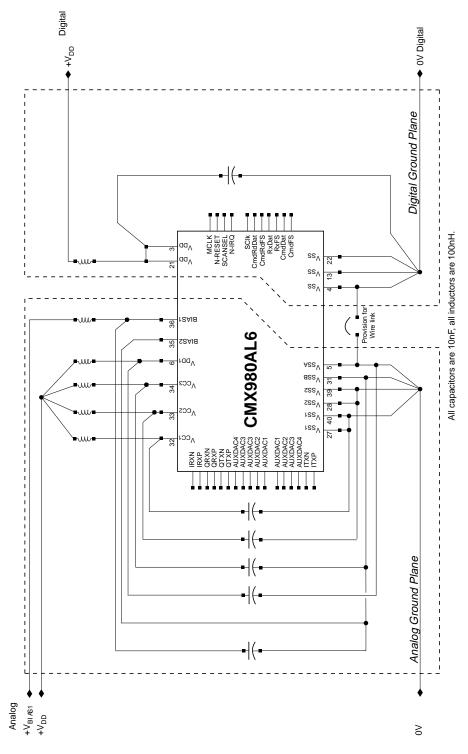

## 4.1 Connection and Decoupling of Power Supplies

Optimum performance from the CMX980A can only be obtained by the use of adequate decoupling and the separation of analog and digital signals, including the use of separate ground planes. Printed circuit board layout should follow the recommendations shown in Figure 4.

Figure 4: Recommended Decoupling Components

#### 4.2 **Programmable FIR Filter Architecture**

Within both, the transmit and receive data paths a common FIR filter architecture for the implementation of the filtering requirements is employed. The filters use a small local static RAM for efficient data and coefficient storage during filter operations, together with a dedicated hardware multiplier and accumulator for each filter.

On reset, the coefficient RAMs are loaded with default values that provide the required response to meet the needs of a TETRA baseband system. In the default modes the dynamic range of arithmetic units are sufficient for all normal input data levels without causing overflows. Each filter has an odd number of default coefficients, which are symmetrical, giving a linear phase response. These coefficients may be overwritten to adapt to other systems or compensate for deficiencies outside the device. However the user is then responsible for ensuring that user supplied values do not cause arithmetic overflows to occur within an accumulation cycle. Overflow logic within each filter can detect such events and cause interrupts to be generated under user control.

The data RAMs store the filter input data samples and operate upon these values to provide the general FIR transfer function:

$$y(k) = \sum_{n=1}^{n=FL} A_n. D_{(n-k)} \qquad \text{where: } FL \qquad \text{is the filter tap length}$$

$$A_n \qquad \text{is the nth filter coefficient}$$

$$D_{(n-k)} \qquad \text{is the data sample supplied to the filter n-k samples previously}$$

When a filter is de-activated, coefficient RAMs retain their state, while the data RAMs are reset to zero. This ensures that the filters start from a quiescent state and prevents filter "memory" from a previous data frame. Asserting the N RESET pin will cause all programmable filter coefficients to return to default values. Alternatively, the Tx and Rx path filter coefficients may be reset independently from each other by use of a control bit. The data RAMs, unlike the coefficient RAMs, are not directly accessible to the user.

Read or write operations to the coefficient RAMs can be performed by accessing the base address, which points to the MSB register of the first coefficient A1. This should be followed by a LSB register access that will auto-index the internal RAM address pointer to A2. Successive operations will continue to auto-index the RAM address pointer until A(FL) is reached. A further access after this point leads to a reserved location A0 that should not be altered. Continuing operations beyond this point returns the pointer to A1 again.

All filters, except the 79-tap Tx, allow access to the complete coefficient set, although the default values are symmetrical about (FL+1)/2. This will enable users to realize non-symmetrical filter functions should this be required.

All filters can be effectively by-passed by setting any single coefficient to normalized unity ( 211-1 in the Tx and 2<sup>15</sup>-1 in Rx) and all others to zero. The chosen position of the "unity" coefficient will vary the internal group delay, thus this feature should be used with care. For example, the Tx ramping feature has a built in delay, which defaults to the expected group delay for the Tx filter path. Ramp delay may be bypassed, if required, by setting the appropriate bit in the **BISTControl** Register. The default group delay can be retained by choosing the central coefficient as "unity".

The 79-tap filter has only one half of the coefficient RAM available, so can only implement symmetrical (linear phase) filter responses. Thus, when accessing this filter only locations A1-A40 are valid. In addition, to bypass this filter, the central coefficient (A40) should be chosen as "unity", since this is the only unique coefficient.

#### 4.3 Tx Data Path

The features described below give a high degree of flexibility for the user to compensate in the baseband processing for non-ideal performance in the IF, RF and RF linear amplifier sections.

#### 4.3.1 Modulator

This takes the 2-bit symbols, performs a Gray Code conversion and uses a recursive adder to generate a 3-bit code representing the 8 possible phase states. A look up table provides the digitally encoded I and Q values for each phase state. The modulator function can be by-passed if required; in this case, the 3-bit code representing the 8 possible phase states which are passed to the look up table is provided directly via the serial interface.

#### 4.3.2 Filters

Digital filtering is applied to the data from the modulator by two programmable FIR filters. The first has 79-taps and provides stop band rejection and sampling correction. The second has 63-taps and provides the primary Root Raised Cosine (RRC) shaping with Roll-off factor ( $\alpha$ ) of 0.35, together with correction for droop in the switched capacitor reconstruction filter. These FIR filters operate at eight times the incoming symbol rate and are configured as two filters in cascade for each I and Q channel.

#### 4.3.3 Gain Multiplier

This feature allows user control of the signal amplitudes in the I and Q channels independently. The multiplier provides a resolution of 11 bits; i.e. the gain is adjustable in steps of 1/2048 of maximum level. Additional logic allows a mode of operation that will enable ramping up to the set signal level, stay at this value while instructed by the user, then ramp back down to zero. The maximum value for each channel, the ramping up rate and the ramping down rate are all programmable via the serial interface.

#### 4.3.4 Offset Adjust

Offset registers allow any offsets introduced in the analog sections of the transmit path to be corrected digitally via the serial interface. The offset adjust is independently applied to each of the I and Q channels. The adjustment range is plus and minus full scale in each section with a resolution of 1 LSB. Thus, care must be exercised by the user to avoid excessive offsets being applied to the Sigma-Delta DAC.

### 4.3.5 Sigma-Delta D-A Converters and Reconstruction Filters

The converters are designed to have low distortion and >80dB dynamic range. These 2<sup>nd</sup> order converters operate at a frequency of 128 x symbol rate so as to over-sample the data at their inputs a further 16 times. The reconstruction filters are 3<sup>rd</sup> order, switched capacitor, low pass filters designed to work in conjunction with an external RC.

#### 4.3.6 Phase Pre-distortion

A further feature allows the user to compensate for a non-orthogonal carrier phase in the external quadrature modulator by adding a programmable fraction of up to 1/8 of the filtered I and Q channel signals to each other immediately prior to the DAC input.

#### 4.3.7 Ramping Output Amplitude

A facility is provided to allow ramping of the outputs in two modes. When enabled by the user, the signal from the gain multiplier stage is multiplied by an envelope value. The value in this register, increments or decrements at a rate programmed by the user, which is held in the TxRampUpInc and TxRampDnDec Registers respectively.

The ramping envelope can be selected by the user to be linear or non-linear. In non-linear mode, the envelope function is sigmoidal, minimizing spectrum spread whilst fast ramping is in operation. The RCR is a 11-bit register (not user accessible), representing a value from 0 to 1.0, which can be incremented by the value TxRampUpInc until the count of 2047 (1.0) is reached, or decremented by the value in TxRampDnDec until zero is reached.

In linear mode, this value (RCR) is used directly to provide the envelope amplitude, whilst in non-linear mode it is input to a look-up table of the sigmoidal function, which in turn provides the envelope amplitude. Ramping begins from zero when the user applies valid transmission data with the TxRampUp bit in the TxData Register set and continues in increments of TxRampUplnc until the set gain level (see Section 4.3.3) is reached. To begin the ramp down phase of a transmit burst the user writes post-amble data with the TxRampUp bit cleared then the RCR decrements by an amount TxRampDnDec until the result is less than or equal to zero, whereupon the gain is set to zero. Internal flag registers are available to indicate to the user that ramp down is complete.

The TxRampUpInc and TxRampDnDec Registers are both 9-bit words input via the serial interface prior to the start of a transmission; this gives programmable ramping rates from 0.125 to 64 symbol-times.

#### 4.3.8 Symbol Clock Phase Adjustment

In order to comply with the requirement to maintain the phase error between the Mobile Station (MS) and Base Station (BS) symbol clock to less than  $\pm 1/4$  symbol time, a mechanism to allow phase adjustment of the CMX980A symbol clock is provided.

This phase adjustment is achieved by writing a command to the **SymClkPhase** Register, which allows adjustment in steps of  $\pm 1/4$  or  $\pm 1/8$  symbol times. It is intended that the user determine the symbol clock phase of the BS after clock recovery has been performed on the received data. Then, allowing for the fixed Tx path delay, the CMX980A phase can be advanced or retarded until it is within the specified error limit. The internal symbol clock phase can be accessed by allowing the symbol clock reference signal to appear on the N\_IRQ pin, or alternatively using the I/Q identification mode (see Section 4.7.3) which places the symbol clock in the Rx I channel LSB. Thus via hardware or software means the internal Tx symbol clock reference time can be determined and the phase with respect to the BS adjusted.

#### 4.3.9 Direct Write to Tx 79-tap Filter Input

A mechanism to allow direct write to the I and Q Tx 79-tap filter inputs at the symbol rate is provided for use in systems where a different modulation scheme is to be employed. See Section 4.7.4 for further details.

#### 4.3.10 Test Access to DAC Input

A mechanism to allow read and write access to DAC input data is provided for use in testing or in other systems where the modulator and filter blocks are not required. By operating the serial port at the high serial clock rate and without a frame gap, it is possible to provide only half of the normal bit rate for two channels, thus data can be provided at MCLK/64 for a single channel or MCLK/128 for both channels. The user should provide the appropriate data at the required sample rate (MCLK/64 or MCLK/128) via the serial interface, which will be transferred to the DAC logic at the next internal sample clock after the data is written to the register. Write operations to the upper and lower byte register and I and Q channels must be synchronized in phase by the user to the sample clock strobe. This is to avoid splitting the I and Q channel or upper and lower bytes into different samples. The phase of the sample clock can be determined by allowing the Symbol Clock (which is in phase with the internal sample clock but 1/8 of the rate) to appear on the N\_IRQ pin.

Note that data input at this point will have to be pre-filtered to compensate for the reconstruction filter droop (approximately 2dBs at MCLK/1024), which is normally compensated by the internal FIR default coefficients. In addition, data input at a MCLK/128 sample rate will have a sinx/x alias around MCLK/128, which will be reduced to about 65dBs below the wanted signal by the reconstruction filter. There is some scope to improve this by enhancing the recommended single pole filter stage on the Tx output, but any adverse change in the in-band gain and group delay performance will have to be compensated prior to loading the data into the IC.

#### 4.4 Rx Data Path

#### 4.4.1 Anti-Alias Filtering and Sigma-Delta A-D Converters

The sampling frequency of the Sigma-Delta A-D is 128x symbol rate. The high over-sampling rate relaxes the design requirements on the anti-alias filter. However, to achieve optimum performance the anti-alias filter must reject the sampling frequency to about -110dB, of which at least 30dB must be provided externally. Additionally, in order to ease the complexity of the subsequent digital filters, there is a further requirement that the anti-alias filter suppress 8x symbol rate to about -15dB. The on-chip anti-alias filter is designed to achieve this when used in conjunction with some external filtering. If required, the on-chip anti-alias filter can be bypassed and powered down, although external anti-aliasing must then be provided. The fourth-order Sigma-Delta A-D converters are designed to have low distortion and >96dB dynamic range. The baseband I and Q channels must be provided as differential signals; this minimizes in-band pick up both on and off the chip.

Both I and Q Sigma-Delta converters produce a single bit output sampled at MCLK/4. This data is passed to a non-programmable decimation FIR filter, which is sampled at MCLK/4 and gives sufficient rejection at 8x symbol rate (MCLK/64) to permit decimation to that frequency (note that around -30dB is provided by the primary anti-alias filters).

#### 4.4.2 Rx FIR Filters

Digital filtering is applied to the data from the Sigma-Delta A-D converter decimation filters by two 63-tap FIR filters in cascade. The default coefficients are set to give a Root Raised Cosine response with roll-off factor  $(\alpha)$  of 0.35. The first filter is used to enhance stop-band rejection, while the second filter provides the primary shaping requirements for root raised cosine response.

#### 4.4.3 Offset Registers

System generated offsets may be removed by control of the offset register via the serial interface.

#### 4.4.4 I and Q Channel Gain

Programmable gain modules are provided in both I and Q channels. These blocks allow the user to adjust the dynamic range of the received data within the digital filters, thus optimizing the filter signal to noise performance for a range of levels at the Rx input pins. In the receive section the gain-multiplier sign bit is user accessible, therefore phase inversion in each channel is possible by programming negative numbers into the gain registers.

The two channels are independently programmable. This enables differential gain corrections to be made within the digital domain.

#### 4.5 Auxiliary Circuits

#### 4.5.1 10-Bit DACs

Four 10-bit DACs are provided to assist in a variety of control functions. The DACs are designed to provide an output as a proportion of the supply voltage, depending on the digital input. They are monotonic with an absolute accuracy of better than 1%. Control and Data for these come via the serial interface.

#### 4.5.2 10-Bit ADC

A 10-bit ADC is provided to assist in a variety of measurement and control functions. The ADC is designed to produce a digital output proportional to the input voltage; full scale being the positive supply. It is monotonic with an absolute accuracy of about 1%. An input multiplexer allows the input to be selected from one of four sources. Control and digital data output is via the serial interface.

#### 4.5.3 Power Ramping and Control

One of the DACs has an additional feature that enables a set of values to be sequenced out at a pre-selected frequency. This is aimed at enabling power ramping of a RF output with a suitable profile. The sequence may be reversed for power down. The sequence of values is stored in a dedicated RAM, which can be loaded via the serial interface.

### 4.6 IRQ Function

An interrupt request (IRQ) pin (labeled N\_IRQ) is provided for asynchronous communication with an external processor. The N\_IRQ pin will be asserted (taken low) when any of the error or user information flags are activated by an internal operation. Some examples of operations that may generate an interrupt are:

- 1. An attempt by the user to write to a full Tx data-input FIFO

- 2. An attempt is made by the Tx to read from the Tx data-input FIFO when it is empty.

- 3. An internal arithmetic overflow has occurred in an FIR filter.

The IRQ feature may also be used to establish the phasing of the received I and Q channel data from the RxDat serial port should synchronization be lost for any reason.

The cause of the IRQ can be obtained by reading the error flags register. All possible causes of an IRQ are masked on reset. Mask status can be altered by writing to the IRQ mask register.

Note that default coefficients and settings have been optimized to maximize performance and should not cause arithmetic overflows. However, use of non-default coefficients, large offset corrections or large Tx phase adjustments may cause problems, which can be corrected by scaling down coefficients or via the gain multiplier feature.

Additionally, the internal symbol-clock signal may be brought out to this pin. This is intended for a number of uses, primarily in the following areas:

- 1. In multi-chip systems where symbol phase synchronization between devices is necessary.

- 2. To assist in timing the write operations to the 79-tap filter input in direct write mode.

- 3. To provide a reference signal during phase synchronization to the BS symbol clock.

#### 4.7 **Serial Interface**

All digital data I/O and control functions for the CMX980A are via the serial interface. It is expected that the CMX980A will be used in conjunction with a DSP and/or other processor. The device has three serial interface ports, each port is based on the industrial standard three-wire serial interface. This interface allows communication with standard DSP ICs using a minimum of external components. The three serial interface ports are:

- Command port, generally this is an input port receiving commands and data from the host, but may also be configured as a bi-directional I/O interface.

- CmdRd Command read port, an output port to send command read data back to the host. Read data is only sent on this port in response to a read command.

- RxData Receive data port, an output port to send receive data back to the host. Data is only present on this interface when the Rx Data path is active. This port may also be configured as the CmdRd port.

### Functions performed by the serial interface include:

- Power up or down and optional bypassing of selected blocks

- Setting digital filter coefficients

- Loading ramp up and ramp down increments for Tx data operations

- Loading and transmitting data

- Loading offset correction, gain multiplier and phase adjustment registers

- Enabling/disabling of output via the Rx serial interface

- Vary sampling time for Rx data relative to the sample (MCLK/64) clock.

- Loading data into auxiliary DACs

- Initiating conversions using auxiliary ADCs and reading results

- Writing data to, and reading data from, the Waveform Generation SRAM

- Power Ramping step control

## The three interfaces consist of the following signal pins:

| SCIk     | Output | Serial Clock pin. This pin is common for all three interfaces.                                                            |  |  |  |

|----------|--------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CmdDat   | In/Out | Command port <i>Data</i> pin. This pin is by default an input, but may be configured as an open drain bi-directional pin. |  |  |  |

| CmdFS    | Input  | Command port <i>Frame Sync</i> pin. This pin is used to mark the first bit in a serial frame.                             |  |  |  |

| CmdRdDat | Output | Command read port <i>Data</i> pin. This pin only has active data on it in response to a read command.                     |  |  |  |

| CmdRdFS  | Output | Command read port <i>Frame Sync</i> pin. This pin is used to mark the first bit in a serial frame.                        |  |  |  |

| RxDat    | Output | Receive data port <i>Data</i> pin. This pin is only active when the Rx Data path is active.                               |  |  |  |

| RxFS     | Output | Receive data port <i>Frame Sync</i> pin. This pin is used to mark the first bit in a serial frame.                        |  |  |  |

|          | _      |                                                                                                                           |  |  |  |

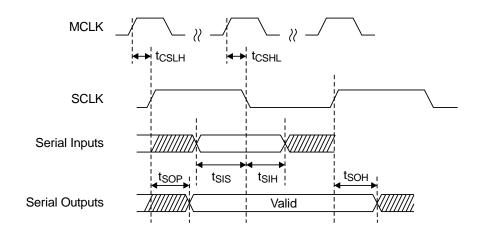

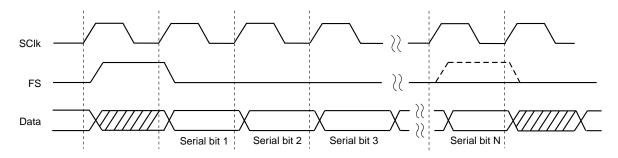

Note: All Frame Sync strobe signals are actually coincident with the last bit of a dataframe. See Figure 5 and Figure 6 for further details.

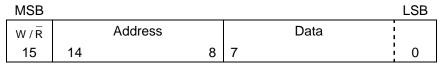

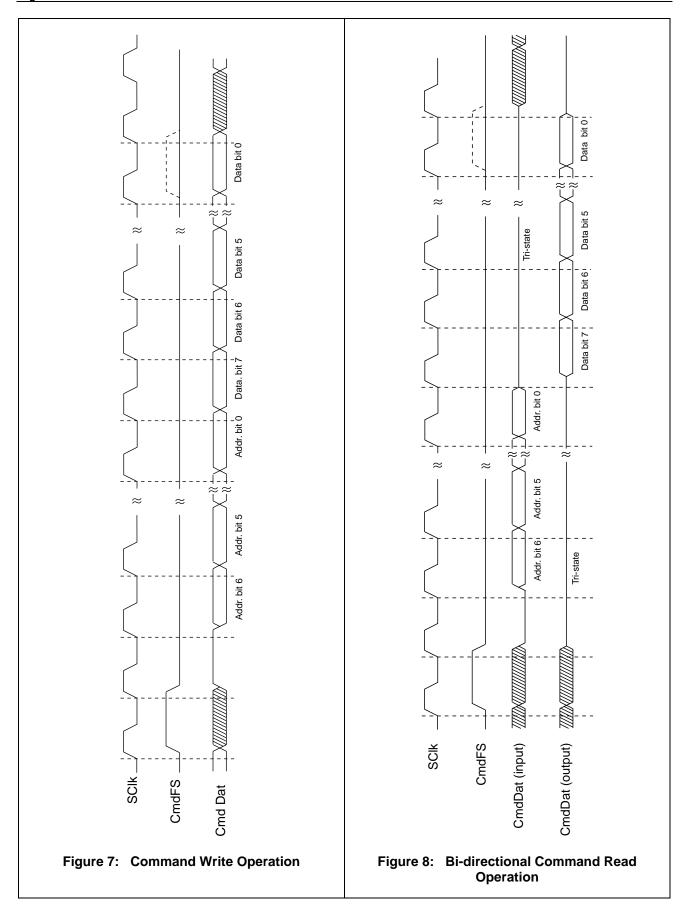

#### 4.7.1 Command Interface

A serial command word consists of a 16-bit frame. Each frame is marked by an active *Frame Sync* event that precedes the MSB bit. A command word can be either a control word or a transmit data word.

#### **Command Control Serial Word**

| MSB |         |         |     |     |   |         |        | LSB |

|-----|---------|---------|-----|-----|---|---------|--------|-----|

| 1   | Tx Data | Address | U/D | 4/1 |   | Tx Data | i<br>i |     |

| 15  | 14      | 10      | 9   | 8   | 7 |         | - !    | 0   |

**Command Transmit Data Serial Word**

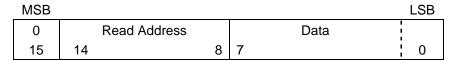

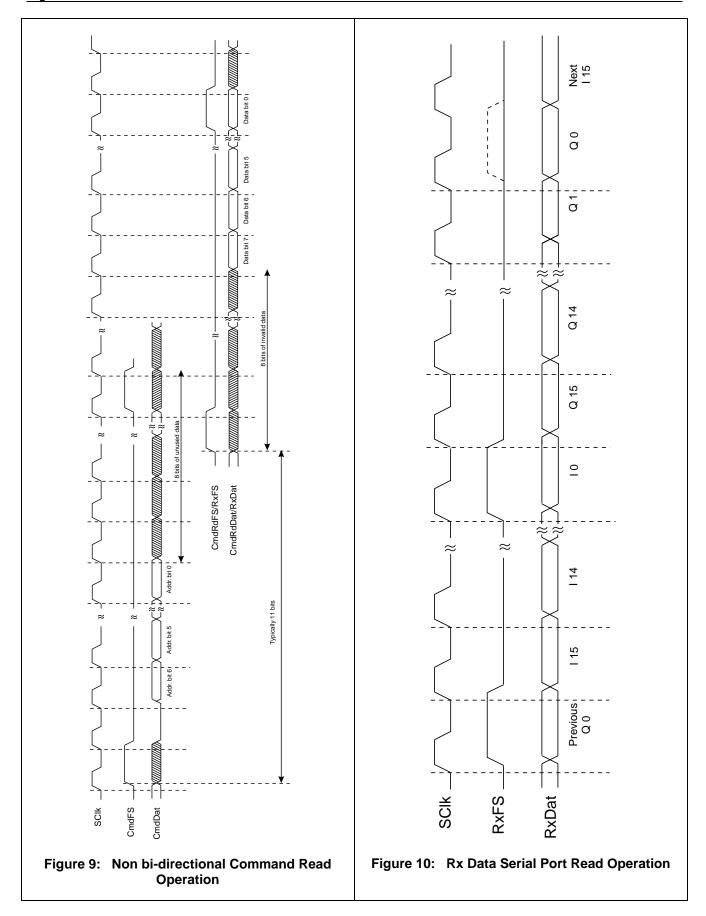

#### 4.7.2 Command Read Interface

Command read data is either output on one of the serial read ports, or driven out in the last 8 bits (data field) on the *Cmd* port. When command read data is output on a serial read port, the read address is put in the most significant half of the word and the read data in the least significant half.

**Command Read Serial Word**

#### 4.7.3 Rx Data Interface

The Rx Data interface is used only for output of the I and Q received data, unless it is operating in the mode where *CmdRd* data is directed to it. When data reception is enabled, I and Q received data will be output at either 8 x or 4 x the symbol rate, under control of command register **RxSetup1**. (see Section 4.8). This is achieved by reducing the serial interface clock rate from MCLK/2 to MCLK/4 and discarding alternate data samples under control of command registers **ConfigCtrl1** and **RxSetup1**. 16-bit I and Q data words are output at the Rx Data interface, I data and MSB first (by default), on the rising edge of SClk. To facilitate channel identification of the serial data, should initial synchronization be lost, and synchronization of the internal Tx symbol clock with received data, the CMX980A has an I/Q identification mode, which is controlled by setting the *RxIdentMode* bit in the **RxSetup1** Register.

#### 4.7.4 Transmission of Data

The address of the Tx FIFO is given consecutive locations (\$0x04-\$0x07), which allows the address bits A1 and A0 (bits 11 and 10) of the Command Transmit Data Serial Word to be utilized as transmit control functions. Data to be transmitted can be in either one or four 2-bit symbol blocks, which are subsequently modulated into the DQPSK constellation, or in 3-bit words, which map directly into constellation points according to the table shown below:

| 3 bit code | 000 | 001    | 010 | 011     | 100 | 101     | 110 | 111     |

|------------|-----|--------|-----|---------|-----|---------|-----|---------|

| l          | 1   | 0.7071 | 0   | -0.7071 | -1  | -0.7071 | 0   | 0.7071  |

| Q          | 0   | 0.7071 | 1   | 0.7071  | 0   | -0.7071 | -1  | -0.7071 |

Table 4: Constellation Map

The eight points in the DQPSK constellation each have a magnitude of 1 and are spaced at 45° intervals around the unit circle. The default operating mode modulates two bit symbols into the TETRA constellation by representing each symbol as a phase change, according to the following mapping, where the left hand bit is considered as the first bit of the symbol and corresponds to bit 0, 2, 4 or 6 of the TxData word (see the description in PAGE 0 ADDRESSED REGISTERS).

| Sym | nbol | Phase Change |

|-----|------|--------------|

| 1   | 1    | -135         |

| 0   | 1    | +135         |

| 0   | 0    | +45          |

| 1   | 0    | -45          |

The user initiates a transmit frame by asserting the TxEn bit in the TxSetup Register. However, internal transmission of the data will wait until specific conditions have been met. Firstly, a valid data word must be written into the FIFO with the TxRampEn bit of the TxSetup Register asserted. Secondly, the internal symbol clock must be active. Therefore, there is a variable delay between asserting the TxEn bit and transmission starting. The user may poll the TxPathEn bit of the TxFIFOStatus Register to establish when transmission has started, and in this case, the active state of TxPathEn is High. In general, the user will wish to know when the transmit frame has completed. This is indicated by TxPathEn returning Low.

To relieve the user of polling overheads when waiting for Tx frame completion, an interrupt can be set up to occur on the transition of the TxPathEn bit from High to Low. In such circumstances, the interrupt activation state of the TxPathEn can be considered Low.

Two control bits are associated with each data transmission word. One controls the format of the word and the other initiates and terminates a transmission cycle. This close association enables precise control of the transmission frame. To relieve the user of the need to synchronize each TxData write with the internal transmit cycle, transmit data words are written into an internal 4-word-deep FIFO. Symbols or constellation points are then read as needed from this FIFO. It is necessary to make sure that there is always a word to be read, three data interlock mechanisms.

#### 4.7.4.1 **Data Interlock Mechanisms**

There are three possible transmission data interlock mechanisms. It is recommended that the user should always use one of these methods.

Software polling

Serial Clock when ready

Interrupt data demand

Software polling requires the user to first check that the FIFO is not full before writing each TxData word. This may be accomplished by inspecting the relevant FIFO status bits before writing one or more TxData words.

The Serial Clock when ready method is a hardware interlock mechanism (enabled by setting the TxHandshakeEn bit of ConfigCtrl1 Register active). The mechanism allows the user to write TxData words without doing any FIFO checks: the hardware handshake is implemented by stopping the serial port clock when the FIFO is full. To prevent a serial port lockout-condition, the handshake is only enabled once the transmission frame has been initiated and is automatically disabled at the end of a frame. This mechanism should be used with care, because stopping the clock will freeze all other serial port transfers (the serial port clock SCIk is common to all three serial ports), including access to auxiliary data converters and receive data.

Interrupt data demand is used to request data when the FIFO has reached a defined level. An interrupt is generated when the data in the FIFO reaches the pre-defined level of "nearly" empty (1 word remaining) or when the FIFO is "nearly" full (1 location available). In each case, the user is responsible for managing the response latency in detecting and servicing the interrupt and for writing new data into the FIFO so that symbol 'run-out' does not occur.

#### 4.7.4.2 Direct write to 79-tap filter mode

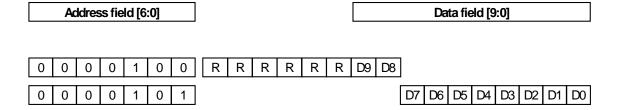

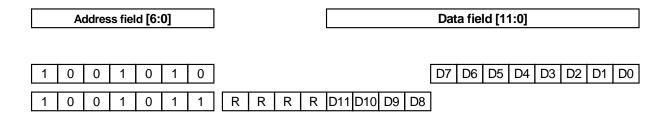

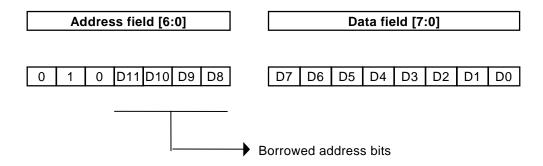

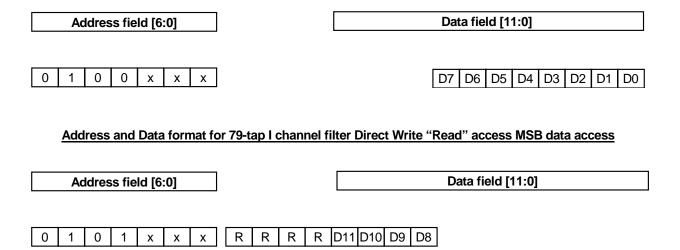

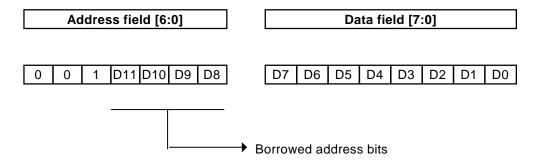

The FIFO and DQPSK modulator may be bypassed thus allowing the user direct access to the Tx filter chain input. The 12-bit data words must be supplied to input holding registers at MCLK/512 samples/sec for both I and Q channels. To allow a single serial-operation write, the TxDirectWrite79tapI and TxDirectWrite79tapQ Registers are in the page 1 address map. By utilising the four least significant address bits to map to the most significant bits of the data, a 12-bit data word can be transferred in a single serial-write frame.

#### 4.7.4.3 Power Ramping and Frame Interlock

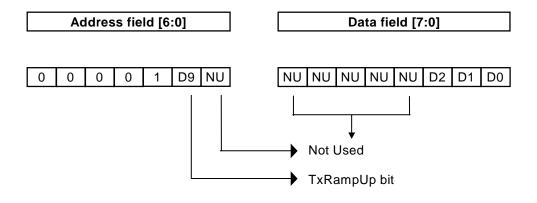

The RampUp bit in the TxData word is used to control both the power ramping function and the frame activation. To start a transmission frame, a transmission word is written with the RampUp bit active. All subsequent TxData words prior to frame termination must also have this bit active. The frame is terminated by writing transmit data words with the RampUp bit inactive. Subsequent TxData words must also have this bit inactive, until initiation of a new frame is required. While the power ramping is active, (up or down) the user must supply transmission symbols or valid constellation points. Once the ramp down operation has completed, all subsequent TxData writes with the RampUp bit inactive will be ignored.

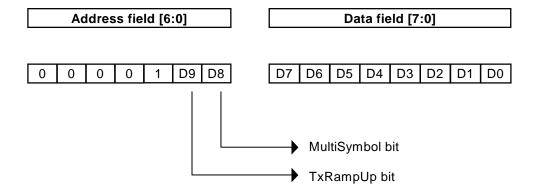

#### 4.7.5 **Command Control Serial Word**

A command word either directly accesses an internal register for a read or write operation, or addresses a memory access point to indirectly access a block of internal memory. For test purposes all registers that can be written may also be read. Not all registers may be written, as some are just status registers. Each register or memory access point is assigned a unique address: the whole (8-bit) address range is reserved for the CMX980A.

A page address technique is used to extend the available address space beyond the 128 locations allowed by 7-bit address fields. This gives four pages of 128 locations, of which the first two (page 0 and page 1) are used. The device configuration and control registers ConfigCtrl1 and ConfigCtrl2 are accessible across all pages, ConfigCtrl2 bits 6 and 7 forming the 2-bit page address.

#### 4.7.5.1 Indirect Memory Addressing

All internal memory access is via an access point. First, a command word access is used to reset the internal address pointer, then data port access operations post-increment this address pointer.

**Example:** To program the fifth and sixth locations of the Auxiliary SRAM with \$0x01AA, the commands would be:

\$0x8000⇒Cmd ; set ConfigCtrl1 all bits Low ; use default conditions

\$0x8118⇒Cmd ; set ConfigCtrl2 bits 7 and 6 Low ; required for Page 0 addressing.

set ConfigCtrl2 bit 4 High post-increment addresses on a read

operation

set ConfigCtrl2 bit 3 High enable read/write access to the

Auxiliary SRAM

\$0x7300⇒Cmd ; read **SramData** LSB Register ; read fourth memory location (LSB).

Post-increment pointer.

CmdRd \$0x73xx ; SramData LSB Register data returned ; discard this byte

\$0xF002⇒Cmd : write **SramData** LSB Register : write \$0x02 to fifth memory location

' (LSB)

\$0xF16A⇒Cmd ; write **SramData** MSB Register ; write \$0x6A to sixth memory location

' (MSB)

\$0x7000⇒Cmd ; read **SramData** LSB Register ; read fifth memory location (LSB)

CmdRd⇒\$0x7002 ; SramData LSB Register data returned ; check this byte is \$0x02

\$0x7100⇒Cmd ; read **SramData** MSB Register ; read sixth memory location (MSB)

CmdRd⇒\$0x716A ; SramData MSB Register data returned ; check this byte is \$0x6A

\$0x8110⇒Cmd : set ConfigCtrl2 bit 3 Low : disable read/write access to the

' Auxiliary SRAM

#### 4.7.6 Coefficient Memory

The convention for naming filter coefficients is A1 to An, where n is given by the filter tap length, i.e. for a 63-tap filter, n = 63. Within the filter architecture, location A0 has a special purpose and must contain zero for correct operation of the computational algorithm. The internal architecture of the 63-tap filters allows access to all coefficients, but the default values are symmetrical about the central coefficient to provide linear phase response. The user is free to write non-symmetrical values, giving the possibility of non-linear phase correction for off-chip components in these filters. The Tx 79-tap filter differs by having coefficients A1 to A40 only, taking advantage of the filter symmetry to reduce its RAM size. Thus write or read operations beyond the A40 coefficient number will be reflected about the central coefficient e.g. the 47th read operation from the 79-tap filter would access coefficient location A33 (80-47).

To access the coefficient RAMs, the user asserts the CoeffRamIoEn bit in the ConfigCtrl2 Register, then performs the operation (read or write) to the MSB of the required FIR filter. The first access after the CoeffRamIoEn bit goes high is directed to location A1. Completing the coefficient access, by addressing the LSB, automatically moves the Coefficient Ram Pointer to A2. The process is repeated until the required number of locations has been accessed.

There is no practical reason to write or read beyond location A40 in the 79-tap filter, but in any case the user must avoid write operations at the (Filter Length + 1) location in any filter. As previously stated this location must be zero for the filters to operate correctly.

Note that filter coefficient read/write operations should be performed with the appropriate path (Tx or Rx) disabled, but the clock stop bits must NOT be set.

The global reset (N\_RESET pin) forces the default coefficients in all filters when asserted (Low).

#### 4.7.7 Auto Power Save Mode

By setting the AutoClkStopMode bit in the ClkStopCtrl Register, the serial interface will enter an automatic power down mode. In this mode, if no serial port activity on the CmdFS is detected after a time out (TMO) period the serial interface will enter a standby state. In this state all master clock activity within the interface is stopped (to reduce power to a minimum) and the SClk pin stops in the high state. It will remain in this state until the user asserts the CmdFS pin for at least one MCLK cycle time, when normal serial port activity will recommence and serial port operation can continue as normal. Subsequent periods of TMO without CmdFS activity will cause the serial interface to enter power down mode again.

The time out period TMO is fixed internally to 4096 master clock periods (444µs when using a 9.216MHz master clock).

When in the power down state and the SClk pin is high, the CmdFS pin may be asserted asynchronously but, when the SClk re-starts, subsequent CmdFS strobes must respect the timing constraints given in the timing section of this document. The serial interface is stopped in the state where it tests the CmdFS pin for a high state, so re-starting from this point by asserting CmdFS will begin a serial operation cycle in the interface logic.

Applying global reset while in the power down state will return the device to normal serial mode.

The use of Auto Power Save mode, by setting the AutoClkStopMode bit, is available only in low data rate mode (set DataRateHi bit of ConfigCtrl1 Register inactive), as this mode is envisaged for use in low speed/low power applications. However, systems that use high data rate mode can make use of this facility by setting a low data rate (set DataRateHi bit of ConfigCtrl1 Register inactive) before asserting the AutoClkStopMode bit, then returning to the high data rate mode by setting the DataRateHi bit active.

#### 4.8 Register Description

This section describes in detail each of the registers and access points addressed by the Command Control Serial Word.

#### 4.8.1 Key to Register Map

Each section that follows describes in detail the operation and use of each of the registers in the device. The registers are split into their functional groups, grouping associated registers together. Each section consists of a Title, an Address, a Function Reference Field, a Description, and a Bit Specification.

The Function Reference Field describes the overall access available to this section (RW/W/R, where R = Read and W = Write).

The Bit Specification describes the function of each individual bit, or a range of bits within a register. There is a separate line for each distinct field of bits. The State column indicates the action available to each group of bits (RW/W/R). Address and data format illustrations show the bit positions in multiple-byte transfers. "R" indicates a reserved bit, which should be set to logic zero when writing. Its value is undefined when read. "X" indicates a don't know/don't care state.

#### 4.8.2 Register Reset State

All I/O access points (both read and write) are reset to logic zero on taking N\_RESET Low, except where explicitly shown in this document. The reset state of status bits will depend on the level of the status signal being monitored. Other registers (both read and write) are not affected by taking N\_RESET Low.

## 4.8.3 Register and Access Point Summary

| Contro  | l and Status Reg | gisters (Universal Ac | cess)                                         |

|---------|------------------|-----------------------|-----------------------------------------------|

| Page    |                  |                       |                                               |

| 21      | \$0x00           | ConfigCtrl1           | Configuration control register 1              |

| 22      | \$0x01           | ConfigCtrl2           | Configuration control register 2              |

| Contro  | l and Status Reg | gisters (Page 0)      |                                               |

| 23      | \$0x02           | PowerDownCtrl         | Power control register                        |

| 24      | \$0x03           | TxSetup               | Transmit setup register                       |

| 25      | \$0x04-\$0x07    | TxData                | Transmit data registers                       |

| 28      | \$0x08           | RxSetup1              | Receive setup control register 1              |

| 29      | \$0x09           | RxSetup2              | Receive setup control register 2              |

| 29      | \$0x0A           | AnaCtrl               | Analog configuration control register         |

| 30      | \$0x0B           | AuxAdcCtrl            | Auxiliary ADC data converter control register |

| 33      | \$0x0C           | RamDacCtrl            | Ram Dac control register                      |

| 36      | \$0x0D           | LoopBackCtrl          | Loopback control register                     |

| 37      | \$0x0E           | TxErrorStatus         | Transmit error status register                |

| 38      | \$0x0F           | TxErrStatMask         | Transmit error status interrupt mask register |

| 46      | \$0x3C           | ClkStopCtrl           | Clock-Stop Control register                   |

| Auxilia | ry Function Reg  | isters                |                                               |

| 31      | \$0x10-\$0x17    | AuxAdcData            | Auxiliary ADC data registers                  |

| 34      | \$0x18-\$0x1F    | AuxDacData            | Auxiliary DAC data registers                  |

| Status  | and Interrupt Re | egisters              |                                               |

| 39      | \$0x20           | RxErrorStatus         | Receive error status register                 |

| 40      | \$0x21           | RxErrorStatMask       | Receive error status interrupt mask register  |

| 41      | \$0x22           | TxFIFOStatus          | Transmission data FIFO status register        |

| 42      | \$0x23           | TxFIFOStatMask        | Tx data FIFO status interrupt mask register   |

| 43      | \$0x24           | SymClkPhase           | Tx Symbol clock phase adjustment register     |

|         | \$0x25           |                       | Not Used                                      |

| Memor   | y I/O Access Po  | ints                  |                                               |

| 44      | \$0x26-\$0x2D    | CoeffRamData          | Coefficient memory I/O access addresses       |

|         | \$0x2E-\$0x2F    |                       | Not Used                                      |

| Rx Data | a Path Registers | 5                     |                                               |

| 55      | \$0x30-\$0x31    | RxIQGainMult          | Receive I channel gain attenuation registers  |

| 56      | \$0x32-\$0x33    | RxIQOffset            | Receive I channel offset correction registers |

| 55      | \$0x34-\$0x35    | RxIQGainMult          | Receive Q channel gain attenuation registers  |

| 56      | \$0x36-\$0x37    | RxIQOffset            | Receive Q channel offset correction registers |

| Rx Data | a Path Access P  | Points                |                                               |

| 57      | \$0x38-\$0x39    | RxDataAccess          | Receive path data access point (I)            |

| 57      | \$0x3A-\$0x3B    | RxDataAccess          | Receive path data access point (Q)            |

|         | \$0x3D-\$0x3F    |                       | Not Used                                      |

| TX Data | TX Data Path Registers |                   |                                                     |  |  |  |  |  |

|---------|------------------------|-------------------|-----------------------------------------------------|--|--|--|--|--|

| 52      | \$0x40-\$0x41          | TxPhase           | Transmit I channel phase correction registers       |  |  |  |  |  |

| 50      | \$0x42-\$0x43          | TxIQGainMult      | Transmit I channel gain attenuation registers       |  |  |  |  |  |

| 51      | \$0x44-\$0x45          | TxIQOffset        | Transmit I channel offset correction registers      |  |  |  |  |  |

| 52      | \$0x46-\$0x47          | TxPhase           | Transmit Q channel phase correction registers       |  |  |  |  |  |

| 50      | \$0x48-\$0x49          | TxIQGainMult      | Transmit Q channel gain attenuation registers       |  |  |  |  |  |

| 51      | \$0x4A-\$0x4B          | TxIQOffset        | Transmit Q channel offset correction registers      |  |  |  |  |  |

| 48      | \$0x4C-\$0x4D          | TxRampUpInc       | Transmit ramp-up increment registers                |  |  |  |  |  |

| 49      | \$0x4E-\$0x4F          | TxRampDnDec       | Transmit ramp-down decrement registers              |  |  |  |  |  |

| Tx Data | a Path Access Po       | oints             |                                                     |  |  |  |  |  |

| 54      | \$0x50-\$0x51          | TxDataAccess      | Transmit path data access point (I)                 |  |  |  |  |  |

| 54      | \$0x52-\$0x53          | TxDataAccess      | Transmit path data access point (Q)                 |  |  |  |  |  |

|         | \$0x54-\$0x5F          |                   | Not Used                                            |  |  |  |  |  |

| Self Te | st Registers           |                   |                                                     |  |  |  |  |  |

| 59      | \$0x60-\$0x61          | BISTPRSG          | Built-in self test pseudo-random sequence generator |  |  |  |  |  |

| 58      | \$0x62                 | BISTControl       | Built-in self test control register                 |  |  |  |  |  |

|         | \$0x63                 |                   | Not Used                                            |  |  |  |  |  |

| 60      | \$0x64-\$0x6D          | BISTCRCRegisters  | Built-in self test cyclic redundancy code checkers  |  |  |  |  |  |

|         | \$0x6E-\$0x6F          |                   | Not Used                                            |  |  |  |  |  |

| SRAM    | Memory Access          | Points            |                                                     |  |  |  |  |  |

| 47      | \$0x70-\$0x73          | SramData          | Auxiliary DAC1 memory I/O access addresses          |  |  |  |  |  |

|         | \$0x74-\$0x7F          |                   | Not Used                                            |  |  |  |  |  |

| Direct  | Write Registers (      | Page 1)           |                                                     |  |  |  |  |  |

| 62      | \$0x10-\$0x1F          | DirectWrite79tapI | Direct write access to 79-tap I channel filter      |  |  |  |  |  |

| 63      | \$0x20-\$0x2F          | DirectWrite79tapQ | Direct write access to 79-tap Q channel filter      |  |  |  |  |  |

#### Notes:

- 1. Addresses \$0x80 to \$0xFF cannot be used as the MSB controls the direction of data flow:

- 2. "1" = High = Read and "0" = Low = Write.

#### 4.8.3.1 **UNIVERSAL REGISTERS ACCESSIBLE IN ALL PAGES**

#### ConfigCtrl1

Title: Configuration Control register

Address: \$0x00 Function: RW

General configuration bits, together with operational control signal bits. Description:

| Bit   | Name                | Active             | State | Function                                                                                                                                                                                                                                                                                                       |

|-------|---------------------|--------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | DataRateHi          | High               | RW    | When set active all serial port data transfers will be at half of the master clock rate. When inactive, all serial port data rates will be at a quarter of the master clock rate. This has the effect of altering the Rx sample output rate from 8 times the symbol rate when active to 4 times when inactive. |

| 6     | TxHandshakeEn       | High               | RW    | When set active enables the transmit hardware interlock protocol, thereby stopping the <i>Serial Clock</i> (SClk) if the transmit path is enabled and the transmit FIFO is full.                                                                                                                               |

| 5     | BiDirCmdPortEn      | High               | RW    | When this bit is set active the <i>Cmd</i> port will drive its data line out of the chip for the last 8 bits of read operations. When set inactive command read data will be returned on either the <i>Rx</i> or the <i>CmdRd</i> port (default).                                                              |

| 4     | RxDataForCmdRdEn    | High               | RW    | This bit only takes effect if the <i>BiDirCmdPortEn</i> bit is inactive. When set active this bit causes all command read operations to respond with data on the <i>Rx</i> serial port. When set inactive the command read data will be output via the <i>CmdRd</i> port (default).                            |

| (5,4) | CommandReadDataMode | 00<br>01<br>10, 11 | RW    | The BiDirCmdPortEn bit and RxDataForCmdRdEn bit together control the method by which command read data is returned to the user.  (Default) Read data returned on CmdRd port. Read data returned on Rx port and CmdRd port Read data returned on Cmd port.                                                      |

| 3     | LowRxRdFS           | High               | RW    | When set active both the CmdRdFS and the RxFS output pins will be driven active low, when set inactive the two frame sync's will be driven active high (default).                                                                                                                                              |

| 2     | RxDataPortDisable   | High               | RW    | When set active tristates the RxDat and RxFS pins.                                                                                                                                                                                                                                                             |

| 1     | RdCmdPortDisable    | High               | RW    | When set active tristates the CmdRdDat and CmdRdFS pins.                                                                                                                                                                                                                                                       |

| 0     | SymboModuBypass     | High               | RW    | Setting this bit bypasses the modulator, thereby taking the least significant 3 bits of each Command Transmit Data Serial Word received via the serial interface to represent an absolute constellation mapping.                                                                                               |

#### Address and Data format for ConfigCtrl1 access

|   | Address field [6:0] |   |   |   |   |   |    |    | Da | ta fie | ld [7 | :0] |    |    |

|---|---------------------|---|---|---|---|---|----|----|----|--------|-------|-----|----|----|

|   |                     |   |   |   |   |   |    |    |    |        |       |     |    |    |

| 0 | 0                   | 0 | 0 | 0 | 0 | 0 | D7 | D6 | D5 | D4     | D3    | D2  | D1 | D0 |

## ConfigCtrl2

Title: Configuration Control register

Address: \$0x01 RW Function:

Description: General configuration bits, together with operational control signal bits.

| Bit | Name            | Active | State | Function                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|-----------------|--------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | PageAddress     | Data   | RW    | Page address field. All registers except ConfigCtrl1 and ConfigCtrl2 use these bits to decode their actual address. Reset defaults to page 0. The page address field applies to all further commands, until a different page address is selected.                                                                                                                                                                |

| 5   | n_SlowDown      | Low    | RW    | When active, this bit reduces the slew rate of digital outputs. This reduces power consumption; ground bounce and reflection problems associated with fast edges on poorly terminated lines. De-activation speeds up the digital outputs, but increases power consumption, ground bounce and reflection problems. It is anticipated that the latter mode will be used only in 3.3V systems.                      |

| 4   | SRamloRdInc     | High   | RW    | This bit determines whether a read or write operation to the Auxiliary SRAM will increment the address pointers. When set active causes read operations to move the address pointer on, this would therefore allow an efficient write then read verify scheme to be used. When set inactive write operations increment the address pointer.                                                                      |

| 3   | SRamloEn        | High   | RW    | When set active allows read/write access to the Auxiliary SRAM. This bit should not be activated when the SRAM is being accessed by the RamDac. When this bit is set active, the first access to the SramData Register will access the first SRAM address location. Subsequent read or write accesses will increment the address pointer to the next memory location.                                            |

| 2   | CoeffRamloRdInc | High   | RW    | This bit determines whether a read or write operation to a coefficient memory will increment the address pointers. When set active the address pointer is incremented by any coefficient ram read operation, thereby allowing a write then read verification. When set inactive, write operations increment the address pointer.                                                                                 |

| 1   | CoeffRamloEn    | High   | RW    | When set active allows read/write access to all the coefficient memories. This bit is valid only when the Tx and Rx Data paths are inactive. When this bit is set active, the first access to any of the coefficient memories will access the first coefficient location (A1). Subsequent read or write accesses to any coefficient memory will increment the address pointers for all the coefficient memories. |

| 0   | n_BigEndData    | Low    | RW    | When set active causes serial port read data, from the Rx port to be generated with the MSB data bit as the first serial word bit. If inactive, the LSB is first. On taking N_RESETLow this bit is active (i.e. the default is MSB first).                                                                                                                                                                       |

#### Address and Data format for ConfigCtrl2 access

|   | Address field [6:0] |   |   |   |   |   |  |    |    | Da | ta fie | ld [7 | :0] |    |    |

|---|---------------------|---|---|---|---|---|--|----|----|----|--------|-------|-----|----|----|