# **PE9702**

### **Product Description**

Peregrine's PE9702 is a high-performance integer-N PLL capable of frequency synthesis up to 3.0 GHz. The device is designed for superior phase noise performance while providing an order of magnitude reduction in current consumption, when compared with existing commercial space PLLs.

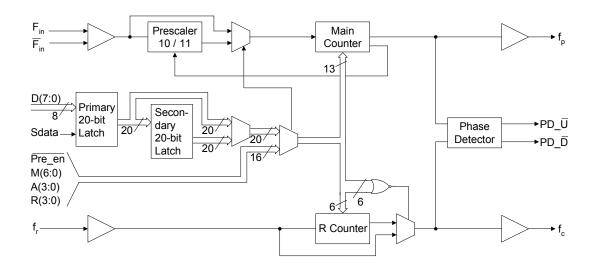

The PE9702 features a 10/11 dual modulus prescaler, counters and a phase comparator as shown in Figure 1. Counter values are programmable through either a serial or parallel interface and can also be directly hard wired.

The PE9702 is optimized for commercial space applications. Single Event Latch up (SEL) is physically impossible and Single Event Upset (SEU) is better than 10<sup>-9</sup> errors per bit / day. Fabricated in Peregrine's patented UTSi® (Ultra Thin Silicon) CMOS technology, the PE9702 offers excellent RF performance and intrinsic radiation tolerance.

# 3.0 GHz Integer-N PLL for Rad Hard Applications

#### **Features**

- 3.0 GHz operation

- ÷10/11 dual modulus prescaler

- Internal phase detector

- Serial, parallel or hardwired programmable

- Ultra-low phase noise

- SEU < 10<sup>-9</sup> errors / bit-day

- 100 Krad (Si) total dose

- 44-lead CQFJ

Figure 1. Block Diagram

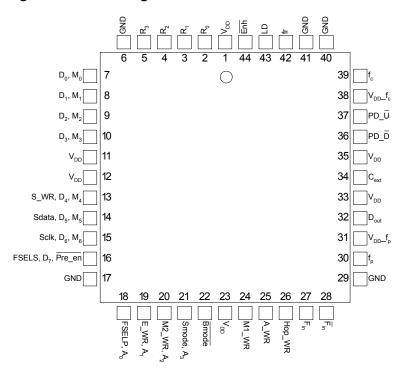

Figure 2. Pin Configuration

**Table 1. Pin Descriptions**

| Pin No. | Pin Name        | Interface Mode | Туре     | Description                                                                                                                                                                 |

|---------|-----------------|----------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | V <sub>DD</sub> | ALL            | (Note 1) | Power supply input. Input may range from 2.85 V to 3.15 V. Bypassing recommended.                                                                                           |

| 2       | R <sub>0</sub>  | Direct         | Input    | R Counter bit0 (LSB).                                                                                                                                                       |

| 3       | R <sub>1</sub>  | Direct         | Input    | R Counter bit1.                                                                                                                                                             |

| 4       | R <sub>2</sub>  | Direct         | Input    | R Counter bit2.                                                                                                                                                             |

| 5       | R <sub>3</sub>  | Direct         | Input    | R Counter bit3.                                                                                                                                                             |

| 6       | GND             | ALL            | (Note 1) | Ground.                                                                                                                                                                     |

| 7       | D <sub>0</sub>  | Parallel       | Input    | Parallel data bus bit0 (LSB).                                                                                                                                               |

| 1       | M <sub>0</sub>  | Direct         | Input    | M Counter bit0 (LSB).                                                                                                                                                       |

| 8       | D <sub>1</sub>  | Parallel       | Input    | Parallel data bus bit1.                                                                                                                                                     |

|         | M <sub>1</sub>  | Direct         | Input    | M Counter bit1.                                                                                                                                                             |

| 9       | D <sub>2</sub>  | Parallel       | Input    | Parallel data bus bit2.                                                                                                                                                     |

|         | M <sub>2</sub>  | Direct         | Input    | M Counter bit2.                                                                                                                                                             |

| 10      | D <sub>3</sub>  | Parallel       | Input    | Parallel data bus bit3.                                                                                                                                                     |

|         | M <sub>3</sub>  | Direct         | Input    | M Counter bit3.                                                                                                                                                             |

| 11      | V <sub>DD</sub> | ALL            | (Note 1) | Same as pin 1.                                                                                                                                                              |

| 12      | V <sub>DD</sub> | ALL            | (Note 1) | Same as pin 1.                                                                                                                                                              |

| 13      | S_WR            | Serial         | Input    | Serial load enable input. While S_WR is "low", Sdata can be serially clocked. Primary register data is transferred to the secondary register on S_WR or Hop_WR rising edge. |

Copyright @ Peregrine Semiconductor Corp. 2001

File No. 70/0036~00C | UTSi ® CMOS RFIC SOLUTIONS

| Pin No. | Pin Name        | Interface Mode   | Туре     | Description                                                                                                                                                                              |

|---------|-----------------|------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | D <sub>4</sub>  | Parallel         | Input    | Parallel data bus bit4                                                                                                                                                                   |

|         | M <sub>4</sub>  | Direct           | Input    | M Counter bit4                                                                                                                                                                           |

|         | Sdata           | Serial           | Input    | Binary serial data input. Input data entered MSB first.                                                                                                                                  |

| 14      | D <sub>5</sub>  | Parallel         | Input    | Parallel data bus bit5.                                                                                                                                                                  |

|         | M <sub>5</sub>  | Direct           | Input    | M Counter bit5.                                                                                                                                                                          |

|         | Sclk Serial     |                  | Input    | Serial clock input. Sdata is clocked serially into the 20-bit primary register (E_WR "low") or the 8-bit enhancement register (E_WR "high") on the rising edge of Sclk.                  |

| 15      | D <sub>6</sub>  | Parallel         | Input    | Parallel data bus bit6.                                                                                                                                                                  |

|         | M <sub>6</sub>  | Direct           | Input    | M Counter bit6.                                                                                                                                                                          |

|         | FSELS           | Serial           | Input    | Selects contents of primary register (FSELS=1) or secondary register (FSELS=0) for programming of internal counters while in Serial Interface Mode.                                      |

| 16      | D <sub>7</sub>  | Parallel         | Input    | Parallel data bus bit7 (MSB).                                                                                                                                                            |

|         | Pre_en          | Direct           | Input    | Prescaler enable, active "low". When "high", F <sub>in</sub> bypasses the prescaler.                                                                                                     |

| 17      | GND             | ALL              |          | Ground.                                                                                                                                                                                  |

| 18      | FSELP           | Parallel         | Input    | Selects contents of primary register (FSELP=1) or secondary register (FSELP=0) for programming of internal counters while in Parallel Interface Mode.                                    |

|         | A <sub>0</sub>  | Direct           | Input    | A Counter bit0 (LSB).                                                                                                                                                                    |

|         |                 | Serial           | Input    | Enhancement register write enable. While E_WR is "high", Sdata can be serially clocked into the enhancement register on the rising edge of Sclk.                                         |

| 19      | E_WR            | Parallel         | Input    | Enhancement register write. D[7:0] are latched into the enhancement register on the rising edge of E_WR.                                                                                 |

|         | A <sub>1</sub>  | Direct           | Input    | A Counter bit1.                                                                                                                                                                          |

| 20      | M2_WR           | Parallel         | Input    | M2 write. D[3:0] are latched into the primary register (R[5:4], M[8:7]) on the rising edge of M2_WR.                                                                                     |

|         | A <sub>2</sub>  | Direct           | Input    | A Counter bit2.                                                                                                                                                                          |

| 21      | Smode           | Serial, Parallel | Input    | Selects serial bus interface mode (Bmode=0, Smode=1) or Parallel Interface Mode (Bmode=0, Smode=0).                                                                                      |

|         | A <sub>3</sub>  | Direct           | Input    | A Counter bit3 (MSB).                                                                                                                                                                    |

| 22      | Bmode           | ALL              | Input    | Selects direct interface mode (Bmode=1).                                                                                                                                                 |

| 23      | V <sub>DD</sub> | ALL              | (Note 1) | Same as pin 1.                                                                                                                                                                           |

| 24      | M1_WR           | Parallel         | Input    | M1 write. D[7:0] are latched into the primary register (Pre_en, M[6:0]) on the rising edge of M1_WR.                                                                                     |

| 25      | A_WR            | Parallel         | Input    | A write. D[7:0] are latched into the primary register (R[3:0], A[3:0]) on the rising edge of A_WR.                                                                                       |

| 26      | Hop_WR          | Serial, Parallel | Input    | Hop write. The contents of the primary register are latched into the secondary register on the rising edge of Hop_WR.                                                                    |

| 27      | Fin             | ALL              | Input    | Prescaler input from the VCO. 3.0 GHz max frequency.                                                                                                                                     |

| 28      | F <sub>in</sub> | ALL              | Input    | Prescaler complementary input. A bypass capacitor in series with a 51 $\Omega$ resistor should be placed as close as possible to this pin and be connected directly to the ground plane. |

| 29      | GND             | ALL              |          | Ground.                                                                                                                                                                                  |

| 30      | f <sub>p</sub>  | ALL              | Output   | Monitor pin for main divider output. Switching activity can be disabled through enhancement register programming or by floating or grounding $V_{DD}$ pin 31.                            |

| Pin No. | Pin Name                        | Interface Mode   | Туре          | Description                                                                                                                                                                                                                                      |

|---------|---------------------------------|------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31      | $V_{DD}$ - $f_p$                | ALL              | (Note 1)      | $V_{DD}$ for $f_p.$ Can be left floating or connected to GND to disable the $f_p$ output.                                                                                                                                                        |

| 32      | Dout                            | Serial, Parallel | Output        | Data Out. The MSEL signal and the raw prescaler output are available on Dout through enhancement register programming.                                                                                                                           |

| 33      | V <sub>DD</sub>                 | ALL              | (Note 1)      | Same as pin 1.                                                                                                                                                                                                                                   |

| 34      | Cext                            | ALL              | Output        | Logical "NAND" of PD_ $\overline{U}$ and PD_ $\overline{D}$ terminated through an on chip, 2 k $\Omega$ series resistor. Connecting Cext to an external capacitor will low pass filter the input to the inverting amplifier used for driving LD. |

| 35      | V <sub>DD</sub>                 | ALL              | (Note 1)      | Same as pin 1.                                                                                                                                                                                                                                   |

| 36      | PD_D                            | ALL              | Output        | $PD\_\overline{D}$ is pulse down when $f_p$ leads $f_c$ .                                                                                                                                                                                        |

| 37      | PD_Ū                            | ALL              |               | $PD\_\overline{U}$ is pulse down when $f_c$ leads $f_p$ .                                                                                                                                                                                        |

| 38      | V <sub>DD</sub> -f <sub>c</sub> | ALL              | (Note 1)      | $V_{DD}$ for $f_c$ . Can be left floating or connected to GND to disable the $f_c$ output.                                                                                                                                                       |

| 39      | f <sub>c</sub>                  | ALL              | Output        | Monitor pin for reference divider output. Switching activity can be disabled through enhancement register programming or by floating or grounding $V_{\text{DD}}$ pin 38.                                                                        |

| 40      | GND                             | ALL              |               | Ground.                                                                                                                                                                                                                                          |

| 41      | GND                             | ALL              |               | Ground.                                                                                                                                                                                                                                          |

| 42      | f <sub>r</sub>                  | ALL              | Input         | Reference frequency input.                                                                                                                                                                                                                       |

| 43      | LD                              | ALL              | Output,<br>OD | Lock detect and open drain logical inversion of CEXT. When the loop is in lock, LD is high impedance, otherwise LD is a logic low ("0").                                                                                                         |

| 44      | Enh                             | Serial, Parallel | Input         | Enhancement mode. When asserted low ("0"), enhancement register bits are functional.                                                                                                                                                             |

Note 1:  $V_{DD}$  pins 1, 11, 12, 23, 31, 33, 35, and 38 are connected by diodes and must be supplied with the same positive voltage level.  $V_{DD}$  pins 31 and 38 are used to enable test modes and should be left floating.

Note 2: All digital input pins have 70 k $\Omega$  pull-down resistors to ground.

**Table 2. Absolute Maximum Ratings**

| Symbol         | Parameter/Conditions      | Min  | Max                   | Units |

|----------------|---------------------------|------|-----------------------|-------|

| $V_{DD}$       | Supply voltage            | -0.3 | 4.0                   | V     |

| Vı             | Voltage on any input      | -0.3 | V <sub>DD</sub> + 0.3 | >     |

| l <sub>l</sub> | DC into any input         | -10  | +10                   | mA    |

| Ιο             | DC into any output        | -10  | +10                   | mA    |

| $T_{stg}$      | Storage temperature range | -65  | 150                   | °C    |

#### **Table 3. Operating Ratings**

| Symbol         | Parameter/Conditions                | Min  | Max  | Units |

|----------------|-------------------------------------|------|------|-------|

| $V_{DD}$       | Supply voltage                      | 2.85 | 3.15 | V     |

| T <sub>A</sub> | Operating ambient temperature range | -40  | 85   | °C    |

#### Table 4. ESD Ratings

| Symbol           | Parameter/Conditions                       | Level | Units |

|------------------|--------------------------------------------|-------|-------|

| V <sub>ESD</sub> | ESD voltage (Human Body<br>Model) – Note 1 | 1000  | V     |

Note 1: Periodically sampled, not 100% tested. Tested per MIL-STD-883, M3015 C2

#### **Electrostatic Discharge (ESD) Precautions**

When handling this UTSi device, observe the same precautions that you would use with other ESD-sensitive devices. Although this device contains circuitry to protect it from damage due to ESD, precautions should be taken to avoid exceeding the rating specified in Table 4.

#### **Latch-Up Avoidance**

Unlike conventional CMOS devices, UTSi CMOS devices are immune to latch-up.

### **Table 5. DC Characteristics**

$V_{DD}$  = 3.0 V, -40° C <  $T_{A}$  < 85° C, unless otherwise specified

| Symbol                   | Parameter                                                | Conditions                                 | Min                   | Тур | Max                   | Units |

|--------------------------|----------------------------------------------------------|--------------------------------------------|-----------------------|-----|-----------------------|-------|

| I <sub>DD</sub>          | Operational supply current;                              | V <sub>DD</sub> = 2.85 to 3.15 V           |                       |     |                       |       |

|                          | Prescaler disabled                                       |                                            |                       | 10  |                       | mA    |

|                          | Prescaler enabled                                        |                                            |                       | 24  | 31                    | mA    |

| Digital Inputs:          | All except $f_r, F_{in}, \overline{F}_{in}$              |                                            |                       |     |                       |       |

| V <sub>IH</sub>          | High level input voltage                                 | V <sub>DD</sub> = 2.85 to 3.15 V           | 0.7 x V <sub>DD</sub> |     |                       | V     |

| V <sub>IL</sub>          | Low level input voltage                                  | V <sub>DD</sub> = 2.85 to 3.15 V           |                       |     | 0.3 x V <sub>DD</sub> | V     |

| I <sub>IH</sub>          | High level input current                                 | V <sub>IH</sub> = V <sub>DD</sub> = 3.15 V |                       |     | +70                   | μΑ    |

| I <sub>IL</sub>          | Low level input current                                  | $V_{IL} = 0, V_{DD} = 3.15 V$              | -1                    |     |                       | μΑ    |

| Reference Div            | ider input: f <sub>r</sub>                               |                                            |                       |     | 1                     |       |

| I <sub>IHR</sub>         | High level input current                                 | V <sub>IH</sub> = V <sub>DD</sub> = 3.15 V |                       |     | +100                  | μΑ    |

| I <sub>ILR</sub>         | Low level input current                                  | $V_{IL} = 0, V_{DD} = 3.15 V$              | -100                  |     |                       | μΑ    |

| R0 Input: R <sub>0</sub> |                                                          |                                            |                       |     | 1                     |       |

| I <sub>IHR</sub>         | High level input current                                 | V <sub>IH</sub> = V <sub>DD</sub> = 3.15 V |                       |     | +70                   | μΑ    |

| I <sub>ILR</sub>         | Low level input current                                  | $V_{IL} = 0, V_{DD} = 3.15 V$              | -5                    |     |                       | μΑ    |

| Counter and p            | hase detector outputs: f <sub>c</sub> , f <sub>p</sub> . |                                            | 1                     |     | <u> </u>              |       |

| V <sub>OLD</sub>         | Output voltage LOW                                       | I <sub>out</sub> = 6 mA                    |                       |     | 0.4                   | V     |

| $V_{OHD}$                | Output voltage HIGH                                      | I <sub>out</sub> = -3 mA                   | V <sub>DD</sub> - 0.4 |     |                       | V     |

| Lock detect or           | utputs: Cext, LD                                         | •                                          | <u> </u>              |     |                       |       |

| $V_{OLC}$                | Output voltage LOW, Cext                                 | I <sub>out</sub> = 100 mA                  |                       |     | 0.4                   | V     |

| V <sub>OHC</sub>         | Output voltage HIGH, Cext                                | I <sub>out</sub> = -100 mA                 | V <sub>DD</sub> - 0.4 |     |                       | V     |

| V <sub>OLLD</sub>        | Output voltage LOW, LD                                   | I <sub>out</sub> = 6 mA                    |                       |     | 0.4                   | V     |

#### **Table 6. AC Characteristics**

$V_{DD}$  = 3.0 V, -40° C <  $T_A$  < 85° C, unless otherwise specified

| Symbol            | Parameter                                                                                            | Conditions             | Min      | Max  | Units |

|-------------------|------------------------------------------------------------------------------------------------------|------------------------|----------|------|-------|

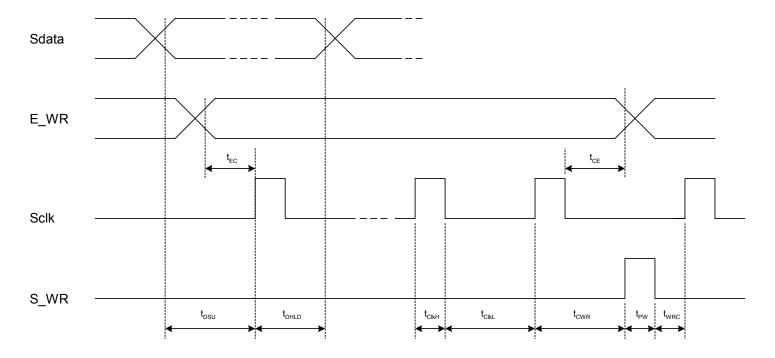

| Control Interfac  | te and Latches (see Figures 3, 4, 5)                                                                 |                        | <u>I</u> | ·I   | ·I    |

| f <sub>Clk</sub>  | Serial data clock frequency                                                                          | (Note 1)               |          | 10   | MHz   |

| t <sub>ClkH</sub> | Serial clock HIGH time                                                                               |                        | 30       |      | ns    |

| t <sub>ClkL</sub> | Serial clock LOW time                                                                                |                        | 30       |      | ns    |

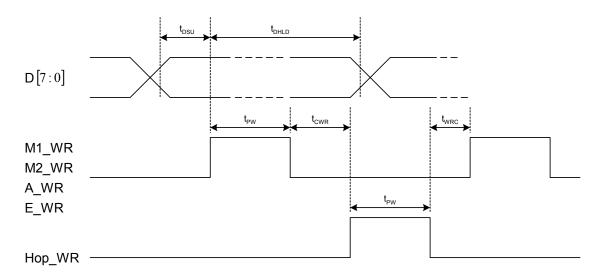

| t <sub>DSU</sub>  | Sdata set-up time after Sclk rising edge, D[7:0] set-up time to M1_WR, M2_WR, A_WR, E_WR rising edge |                        | 10       |      | ns    |

| t <sub>DHLD</sub> | Sdata hold time after Sclk rising edge, D[7:0] hold time to M1_WR, M2_WR, A_WR, E_WR rising edge     |                        | 10       |      | ns    |

| t <sub>PW</sub>   | S_WR, M1_WR, M2_WR, A_WR, E_WR pulse width                                                           |                        | 30       |      | ns    |

| $t_{\sf CWR}$     | Sclk rising edge to S_WR rising edge. S_WR, M1_WR, M2_WR, A_WR falling edge to Hop_WR rising edge    |                        | 30       |      | ns    |

| t <sub>CE</sub>   | Sclk falling edge to E_WR transition                                                                 |                        | 30       |      | ns    |

| t <sub>WRC</sub>  | S_WR falling edge to Sclk rising edge. Hop_WR falling edge to S_WR, M1_WR, M2_WR, A_WR rising edge   |                        | 30       |      | ns    |

| t <sub>EC</sub>   | E_WR transition to Sclk rising edge                                                                  |                        | 30       |      | ns    |

| t <sub>MDO</sub>  | MSEL data out delay after Fin rising edge                                                            | C <sub>L</sub> = 12 pf |          | 8    | ns    |

| Main Divider (Ir  | ncluding Prescaler)                                                                                  | <u> </u>               |          |      |       |

| F <sub>in</sub>   | Operating frequency                                                                                  |                        | 500      | 3000 | MHz   |

| $P_{Fin}$         | Input level range                                                                                    | External AC coupling   | -5       | 5    | dBm   |

| Main Divider (P   | Prescaler Bypassed)                                                                                  |                        |          | •    | •     |

| F <sub>in</sub>   | Operating frequency                                                                                  |                        | 50       | 300  | MHz   |

| $P_{Fin}$         | Input level range                                                                                    | External AC coupling   | -5       | 5    | dBm   |

| Reference Divid   | der                                                                                                  |                        |          | •    | •     |

| f <sub>r</sub>    | Operating frequency                                                                                  | (Note 3)               |          | 100  | MHz   |

| P <sub>fr</sub>   | Reference input power (Note 2)                                                                       | Single-ended input     | -2       |      | dBm   |

| Phase Detector    | r                                                                                                    |                        | •        |      |       |

| f <sub>c</sub>    | Comparison frequency                                                                                 | (Note 3)               |          | 20   | MHz   |

- **Note 1:** Fclk is verified during the functional pattern test. Serial programming sections of the functional pattern are clocked at 10 MHz to verify Fclk specification.

- Note 2: CMOS logic levels can be used to drive reference input if DC coupled. Voltage input needs to be a minimum of  $0.5V_{p-p}$ .

- Note 3: Parameter is guaranteed through characterization only and is not tested.

#### **Functional Description**

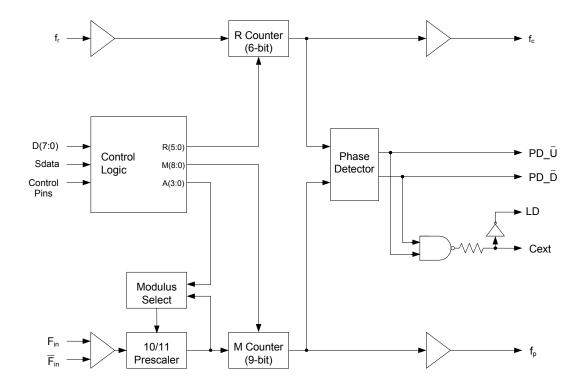

The PE9702 consists of a prescaler, counters, a phase detector, and control logic. The dual modulus prescaler divides the VCO frequency by either 10 or 11, depending on the value of the modulus select. Counters "R" and "M" divide the reference and prescaler output, respectively, by integer values stored in a 20-bit register. An additional counter ("A") is used in the modulus

select logic. The phase-frequency detector generates up and down frequency control signals. The control logic includes a selectable chip interface. Data can be written via serial bus, parallel bus, or hardwired directly to the pins. There are also various operational and test modes and a lock detect output.

Figure 3. Functional Block Diagram

#### **Main Counter Chain**

#### Normal Operating Mode

The main counter chain divides the RF input frequency,  $F_{in}$ , by an integer derived from the user-defined values in the "M" and "A" counters. It is composed of the 10/11 dual modulus prescaler, modulus select logic, and 9-bit M counter. Setting  $\overline{\text{Pre\_en}}$  "low" enables the 10/11 prescaler. Setting  $\overline{\text{Pre\_en}}$  "high" allows  $F_{in}$  to bypass the prescaler and powers down the prescaler.

The output from the main counter chain,  $f_p$ , is related to the VCO frequency,  $F_{in}$ , by the following equation:

$$f_p = F_{in} / [10 \times (M + 1) + A]$$

(1)

where  $A \le M + 1, 1 \le M \le 511$

When the loop is locked,  $F_{in}$  is related to the reference frequency,  $f_r$ , by the following equation:

$$F_{in} = [10 \times (M+1) + A] \times (f_r / (R+1))$$

(2)

where  $A \le M+1$ ,  $1 \le M \le 511$

A consequence of the upper limit on A is that  $F_{in}$  must be greater than or equal to 90 x ( $f_r$  / (R+1)) to obtain contiguous channels. Programming the M Counter with the minimum value of "1" will result in a minimum M Counter divide ratio of "2".

In Direct Interface Mode, main counter inputs  $M_7$  and  $M_8$  are internally forced low. In this mode, the M value is limited to  $1 \le M \le 127$ .

#### Prescaler Bypass Mode

Setting  $\overline{\text{Pre\_en}}$  "high" allows  $F_{\text{in}}$  to bypass and power down the prescaler. In this mode, the 10/11 prescaler and A register are not active, and the input VCO frequency is divided by the M counter directly. The following equation relates  $F_{\text{in}}$  to the reference frequency,  $f_r$ :

$$F_{in} = (M + 1) \times (f_r / (R+1))$$

(3)

where  $1 \le M \le 511$

In Direct Interface Mode, main counter inputs  $M_7$  and  $M_8$  are internally forced low. In this mode, the M value is limited to  $1 \le M \le 127$ .

#### Reference Counter

The reference counter chain divides the reference frequency,  $f_r$ , down to the phase detector comparison frequency,  $f_c$ .

The output frequency of the 6-bit R Counter is related to the reference frequency by the following equation:

$$f_c = f_r / (R + 1)$$

(4)

where  $0 \le R \le 63$

Note that programming R with "0" will pass the reference frequency,  $f_r$ , directly to the phase detector.

In Direct Interface Mode, R Counter inputs  $R_4$  and  $R_5$  are internally forced low ("0"). In this mode, the R value is limited to  $0 \le R \le 15$ .

#### Register Programming

#### Parallel Interface Mode

Parallel Interface Mode is selected by setting the Bmode input "low" and the Smode input "low".

Parallel input data, D[7:0], are latched in a parallel fashion into one of three 8-bit primary register sections on the rising edge of M1\_WR, M2\_WR, or A\_WR per the mapping shown in Table 7 on page 10. The contents of the primary register are transferred into a secondary register on the rising edge of Hop\_WR according to the timing diagram shown in Figure 5. Data is transferred to the counters as shown in Table 7 on page 10.

The secondary register acts as a buffer to allow rapid changes to the VCO frequency. This double buffering for "ping-pong" counter control is programmed via the FSELP input. When FSELP is "high", the primary register contents set the counter inputs. When FSELP is "low", the secondary register contents are utilized.

Parallel input data, D[7:0], are latched into the enhancement register on the rising edge of E\_WR according to the timing diagram shown in Figure 4. This data provides control bits as shown in Table 8 on page 10 with bit functionality enabled by asserting the Enh input "low".

#### Serial Interface Mode

Serial Interface Mode is selected by setting the Bmode input "low" and the Smode input "high".

While the E\_WR input is "low" and the S\_WR input is "low", serial input data (Sdata input), B<sub>0</sub> to B<sub>19</sub>, is clocked serially into the primary register on the rising edge of Sclk, MSB (B<sub>0</sub>) first. The contents from the primary register are transferred into the secondary register on the rising edge of either S\_WR or Hop\_WR according to the timing diagram shown in Figure 6. Data is transferred to the counters as shown in Table 7 on page 10.

The double buffering provided by the primary and secondary registers allows for "ping-pong" counter control using the FSELS input. When FSELS is "high", the primary register contents set the counter When FSELS is "low", the secondary register contents are utilized.

While the E\_WR input is "high" and the S\_WR input is "low", serial input data (Sdata input), B<sub>0</sub> to B<sub>7</sub>, is

clocked serially into the enhancement register on the rising edge of Sclk, MSB (B<sub>0</sub>) first. The enhancement register is double buffered to prevent inadvertent control changes during serial loading, with buffer capture of the serially-entered data performed on the falling edge of E\_WR according to the timing diagram shown in Figure 5. After the falling edge of E WR, the data provides control bits as shown in Table 8 with bit functionality enabled by asserting the Enh input "low".

#### Direct Interface Mode

Direct Interface Mode is selected by setting the Bmode input "high".

Counter control bits are set directly at the pins as shown in Table 7. In Direct Interface Mode, main counter inputs M<sub>7</sub> and M<sub>8</sub>, and R Counter inputs R<sub>4</sub> and R<sub>5</sub> are internally forced low ("0").

Table 7. Primary Register Programming

| Interface<br>Mode | Enh | Bmode | Smode | R <sub>5</sub> | R <sub>4</sub> | M <sub>8</sub> | M <sub>7</sub> | Pre_en         | M <sub>6</sub> | M <sub>5</sub> | M <sub>4</sub> | M <sub>3</sub> | M <sub>2</sub> | M <sub>1</sub>  | M <sub>0</sub>  | R <sub>3</sub>  | R <sub>2</sub>  | R <sub>1</sub>  | R <sub>0</sub>  | $\mathbf{A}_3$  | A <sub>2</sub>  | <b>A</b> <sub>1</sub> | A <sub>0</sub>  |

|-------------------|-----|-------|-------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------------|-----------------|

| Parallel          | 1   | 0     | 0     | M2_V           | VR risir       | ng edge        | load           |                |                | M1_V           | √R risin       | ıg edge        | load           |                 |                 |                 |                 | A_W             | R risin         | g edge          | load            |                       |                 |

|                   |     |       |       | $D_3$          | $D_2$          | $D_1$          | $D_0$          | $D_7$          | $D_6$          | $D_5$          | $D_4$          | $D_3$          | $D_2$          | $D_1$           | $D_0$           | D <sub>7</sub>  | $D_6$           | $D_5$           | $D_4$           | $D_3$           | $D_2$           | $D_1$                 | $D_0$           |

| Serial*           | 1   | 0     | 1     | B <sub>0</sub> | B <sub>1</sub> | B <sub>2</sub> | B <sub>3</sub> | B <sub>4</sub> | B <sub>5</sub> | B <sub>6</sub> | B <sub>7</sub> | B <sub>8</sub> | B <sub>9</sub> | B <sub>10</sub> | B <sub>11</sub> | B <sub>12</sub> | B <sub>13</sub> | B <sub>14</sub> | B <sub>15</sub> | B <sub>16</sub> | B <sub>17</sub> | B <sub>18</sub>       | B <sub>19</sub> |

| Direct            | 1   | 1     | Х     | 0              | 0              | 0              | 0              | Pre_en         | M <sub>6</sub> | M <sub>5</sub> | $M_4$          | M <sub>3</sub> | M <sub>2</sub> | M <sub>1</sub>  | M <sub>0</sub>  | R <sub>3</sub>  | R <sub>2</sub>  | R <sub>1</sub>  | R <sub>0</sub>  | A <sub>3</sub>  | A <sub>2</sub>  | A <sub>1</sub>        | A <sub>0</sub>  |

<sup>\*</sup>Serial data clocked serially on Sclk rising edge while E WR "low" and captured in secondary register on S WR rising edge.

Table 8. Enhancement Register Programming

| Interface<br>Mode | Enh        | Bmode | Smode | Reserved       | Reserved              | Reserved       | Power<br>down | Counter<br>load | MSEL<br>output | Prescaler output | f <sub>c</sub> , f <sub>p</sub> $\overline{\text{OE}}$ |   |   |   |   |   |   |   |   |   |   |       |       |       |       |       |       |       |       |

|-------------------|------------|-------|-------|----------------|-----------------------|----------------|---------------|-----------------|----------------|------------------|--------------------------------------------------------|---|---|---|---|---|---|---|---|---|---|-------|-------|-------|-------|-------|-------|-------|-------|

| Parallel          | 0          | 0     | 0     |                | E_WR rising edge load |                |               |                 |                |                  |                                                        |   |   |   |   |   |   |   |   |   |   |       |       |       |       |       |       |       |       |

| 1 aranci          | Parallel 0 | U     | U     | U              | U                     | U              | U             | O               | U              | U                | U                                                      | U | U | U | U | 0 | U | U | Ü | Ü | O | $D_7$ | $D_6$ | $D_5$ | $D_4$ | $D_3$ | $D_2$ | $D_1$ | $D_0$ |

| Serial*           | 0          | 0     | 1     | B <sub>0</sub> | B <sub>1</sub>        | B <sub>2</sub> | $B_3$         | B <sub>4</sub>  | B <sub>5</sub> | B <sub>6</sub>   | B <sub>7</sub>                                         |   |   |   |   |   |   |   |   |   |   |       |       |       |       |       |       |       |       |

<sup>\*</sup>Serial data clocked serially on Sclk rising edge while E\_WR "high" and captured in the double buffer on E\_WR falling edge.

(last in) LSB

Figure 4. Parallel Interface Mode Timing Diagram

Figure 5. Serial Interface Mode Timing Diagram

#### **Enhancement Register**

The functions of the enhancement register bits are shown below with all bits active "high".

Table 9. Enhancement Register Bit Functionality

| Ві    | t Function                  | Description                                                                                                         |

|-------|-----------------------------|---------------------------------------------------------------------------------------------------------------------|

| Bit 0 | Reserved**                  |                                                                                                                     |

| Bit 1 | Reserved**                  |                                                                                                                     |

| Bit 2 | Reserved**                  |                                                                                                                     |

| Bit 3 | Power down                  | Power down of all functions except programming interface.                                                           |

| Bit 4 | Counter load                | Immediate and continuous load of counter programming as directed by the $\overline{\text{Bmode}}$ and Smode inputs. |

| Bit 5 | MSEL output                 | Drives the internal dual modulus prescaler modulus select (MSEL) onto the Dout output.                              |

| Bit 6 | Prescaler output            | Drives the raw internal prescaler output (fmain) onto the Dout output.                                              |

| Bit 7 | $f_p$ , $f_c \overline{OE}$ | f <sub>p</sub> , f <sub>c</sub> outputs disabled.                                                                   |

<sup>\*\*</sup> Program to 0

#### **Phase Detector**

The phase detector is triggered by rising edges from the main Counter ( $f_p$ ) and the reference counter ( $f_c$ ). It has two outputs, namely PD\_Ū, and PD\_D. If the divided VCO leads the divided reference in phase or frequency ( $f_p$  leads  $f_c$ ), PD\_D pulses "low". If the divided reference leads the divided VCO in phase or frequency ( $f_r$  leads  $f_p$ ), PD\_Ū pulses "low". The width of either pulse is directly proportional to phase offset between the two input signals,  $f_p$  and  $f_c$ . The phase detector gain is 430 mV / radian.

$PD_{\overline{U}}$  and  $PD_{\overline{D}}$  are designed to drive an active loop filter which controls the VCO tune voltage.

PD\_U pulses result in an increase in VCO frequency and PD\_D results in a decrease in VCO frequency.

A lock detect output, LD is also provided, via the pin Cext. Cext is the logical "NAND" of PD\_Ū and PD\_D waveforms, which is driven through a series 2k ohm resistor. Connecting Cext to an external shunt capacitor provides integration. Cext also drives the input of an internal inverting comparator with an open drain output. Thus LD is an "AND" function of PD\_Ū and PD\_D. See Figure 3 for a schematic of this circuit.

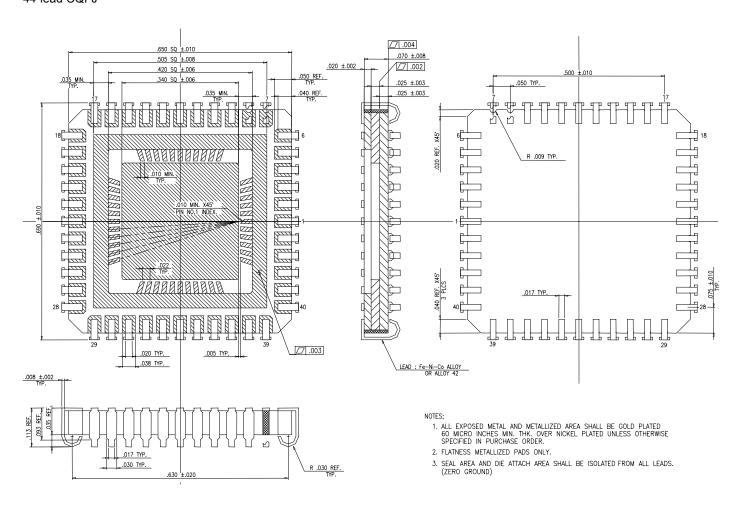

#### Figure 6. Package Drawing

44-lead CQFJ

All dimensions are in mils

## **Table 10. Ordering Information**

| Order<br>Code | Part Marking | Description         | Package     | Shipping<br>Method |

|---------------|--------------|---------------------|-------------|--------------------|

| 9702-01       | PE9702 ES    | Engineering Samples | 44-pin CQFJ | 40 units / Tray    |

| 9702-11       | PE9702       | Flight Units        | 44-pin CQFJ | 40 units / Tray    |

| 9702-00       | PE9702 EK    | Evaluation Kit      |             | 1 / Box            |

# PEREGRINE SEMICONDUCTOR

#### Sales Offices

#### **United States**

Peregrine Semiconductor Corp.

6175 Nancy Ridge Drive San Diego, CA 92121 Tel 1-858-455-0660 Fax 1-858-455-0770

#### **Europe**

#### **Peregrine Semiconductor Europe**

Aix-En-Provence Office Parc Club du Golf, bat 9 13856 Aix-En-Provence Cedex 3 France Tel 33-0-4-4239-3360 Fax 33-0-4-4239-7227

#### Japan

#### Peregrine Semiconductor K.K.

The Imperial Tower, 15th floor 1-1-1 Uchisaiawaicho, Chiyoda-ku Tokyo 100-0011 Japan

Tel: 03-3507-5755 Fax: 03-3507-5601

#### Australia

#### Peregrine Semiconductor Australia

8 Herb Elliot Ave. Homebush, NSW 2140 Australia Tel: 011-61-2-9763-4111

Fax: 011-61-2-9746-1501

For a list of representatives in your area, please refer to our Web site at: http://www.peregrine-semi.com

#### **Data Sheet Identification**

#### Advance Information

The product is in a formative or design stage. The data sheet contains design target specifications for product development. Specifications and features may change in any manner without notice.

#### **Preliminary Specification**

The data sheet contains preliminary data. Additional data may be added at a later date. Peregrine reserves the right to change specifications at any time without notice in order to supply the best possible product.

#### **Product Specification**

The data sheet contains final data. In the event Peregrine decides to change the specifications, Peregrine will notify customers of the intended changes by issuing a PCN (Product Change Notice).

The information in this data sheet is believed to be reliable. However, Peregrine assumes no liability for the use of this information. Use shall be entirely at the user's own risk.

No patent rights or licenses to any circuits described in this data sheet are implied or granted to any third party.

Peregrine's products are not designed or intended for use in devices or systems intended for surgical implant, or in other applications intended to support or sustain life, or in any application in which the failure of the Peregrine product could create a situation in which personal injury or death might occur. Peregrine assumes no liability for damages, including consequential or incidental damages, arising out of the use of its products in such applications.

Peregrine products are protected under one or more of the following U.S. patents: 6,090,648; 6,057,555; 5,973,382; 5,973,363; 5,930,638; 5,920,233; 5,895,957; 5,883,396; 5,864,162; 5,863,823; 5,861,336; 5,663,570; 5,610,790; 5,600,169; 5,596,205; 5,572,040; 5,492,857; 5,416,043. Other patents may be pending or applied for.

UTSi, the Peregrine logotype, SEL Safe, and Peregrine Semiconductor Corp. are registered trademarks of Peregrine Semiconductor Corp. All PE product names and prefixes are trademarks of Peregrine Semiconductor Corp. Copyright © 2001 Peregrine Semiconductor Corp. All rights reserved.