CCVGA7C5 Preliminary TVS

# VGA PORT COMPANION CIRCUIT

#### **■** DESCRIPTION

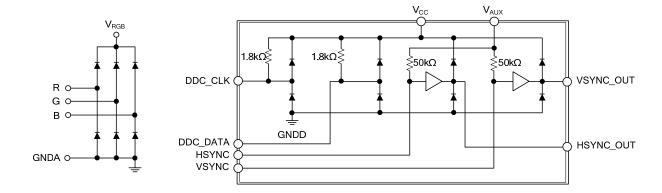

The UTC **CCVGA7C5** is an ESD solution for the VGA port connector. This device integrates ESD protection for all signals,

Two non-inverting drivers provide buffering for the HSYNC and VSYNC signals from the video controller IC. These buffers accept TTL input levels and convert them to CMOS output levels that swing between Ground and  $V_{\text{CC}}$ . These drivers have a nominal  $60\Omega$  output impedance to match the characteristic impedance of the HSYNC and VSYNC lines of the video cables typically used. The inputs of these drivers also have high impedance pull–ups (50k $\Omega$  nom.) pulling up to the VAUX rail.

In addition, the DDC\_CLOCK and DDC\_DATA channels have  $1.8k\Omega$  resistors pulling these inputs up to the main 5V (V<sub>CC</sub>) rail.

The upper ESD diodes for the R, G and B channels are connected to a separate supply rail ( $V_{RGB}$ ) to facilitate interfacing to graphics controller ICs with low voltage supplies. The remaining channels are connected to the main 5 V rail ( $V_{CC}$ ). The lower diodes for the R, G and B channels are also connected to a dedicated ground pin (GNDA) to minimize crosstalk due to common ground impedance.

ESD protection is implemented with current steering diodes designed to safely handle the high peak surge currents associated with the IEC-1000-4-2 Level-4 ESD Protection Standard (±8kV contact discharge). When the channels are subjected to an electrostatic discharge, the ESD current pulse is diverted via the protection diodes into the positive supply rails or ground where they may be safely dissipated.

### **■ FEATURES**

- \* 7 Channels of ESD Protection Designed to Meet IEC-1000-4-2 Level-4 ESD Requirements (±8kV Contact Discharge)

- $^{\star}$  Three Independent Supply Pins (V<sub>CC</sub>, V<sub>RGB</sub> and V<sub>AUX</sub>) to Facilitate Operation with Sub–Micron Graphics Controller ICs

- \* Very Low Loading Capacitance from ESD Protection Diodes at Less than 5pF Typical

- \* TTL to CMOS Level-Translating Buffers for the HSYNC and VSYNC Lines

- $^*$  High impedance Pull–Ups (50k $\!\Omega$  Nominal to VAUX) for HSYNC and VSYNC Inputs

- \* Pull-Up Resistors (1.8k $\Omega$  Nominal to V<sub>CC</sub>) for DDC\_CLK and DDC\_DATA Lines

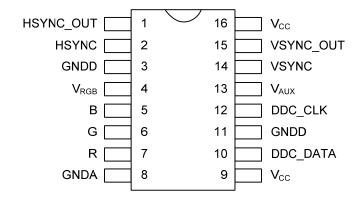

### ■ ORDERING INFORMATION

| Ordering        | Number          | Dookona | Doolsing  |  |

|-----------------|-----------------|---------|-----------|--|

| Lead Free       | Halogen Free    | Package | Packing   |  |

| CCVGA7C5L-R16-T | CCVGA7C5G-R16-T | SSOP-16 | Tube      |  |

| CCVGA7C5L-R16-R | CCVGA7C5G-R16-R | SSOP-16 | Tape Reel |  |

<u>www.unisonic.com.tw</u> 1 of 6

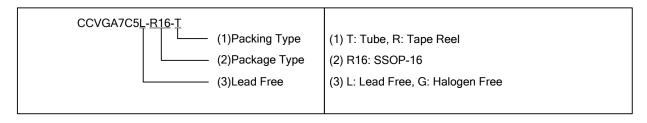

# **PIN CONFIGURATION**

# **PIN DESCRIPTION**

| PIN NO. | PIN NAME         | DESCRIPTION                                                                                                                                                                                                                                                  |  |  |

|---------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1       | HSYNC_OUT        | Horizontal sync signal buffer output. Connects to the video connector side of the horizontal sync line.                                                                                                                                                      |  |  |

| 2       | HSYNC            | Horizontal sync signal buffer input. Connects to the VGA Controller side of the horizontal sync line.                                                                                                                                                        |  |  |

| 3, 11   | GNDD             | Digital ground reference supply pin.                                                                                                                                                                                                                         |  |  |

| 4       | $V_{RGB}$        | $V_{\text{RGB}}$ supply pin. This is an isolated supply pin for the R, G and B ESD protection circuits.                                                                                                                                                      |  |  |

| 5       | В                | Blue signal video protection channel. This pin is typically tied to the B video line between the VGA controller device and the video connector.                                                                                                              |  |  |

| 6       | G                | Green signal video protection channel. This pin is typically tied to the G video line between the VGA controller device and the video connector.                                                                                                             |  |  |

| 7       | R                | Red signal video protection channel. This pin is typically tied to the R video line between the VGA controller device and the video connector.                                                                                                               |  |  |

| 8       | GNDA             | Analog ground reference supply pin.                                                                                                                                                                                                                          |  |  |

| 9, 16   | V <sub>CC</sub>  | V <sub>CC</sub> supply pin. This is the main supply input for the DDC_CLK and DDC_DATA pullup resistors and ESD protection circuits. It is also connected to the sync buffers and to the ESD protection diodes present on the HSYNC_OUT and VSYNC_OUT lines. |  |  |

| 10      | DDC_DATA         | DDC data pin.                                                                                                                                                                                                                                                |  |  |

| 12      | DDC_CLK          | DDC clock pin.                                                                                                                                                                                                                                               |  |  |

| 13      | V <sub>AUX</sub> | $V_{AUX}$ supply pin. This is the supply input for the $50k\Omega$ pullups connected to the HSYNC and VSYNC buffer inputs.                                                                                                                                   |  |  |

| 14      | VSYNC            | Vertical sync signal buffer input. Connects to the VGA Controller side of the vertical sync line.                                                                                                                                                            |  |  |

| 15      | VSYNC_OUT        | Vertical sync signal buffer output. Connects to the video connector side of the vertical sync line.                                                                                                                                                          |  |  |

# ■ BLOCK DIAGRAM

# ■ ABSOLUTE MAXIMUM RATING

| PARAMETER                                      |                   | SYMBOL                     | RATINGS                         | UNIT     |

|------------------------------------------------|-------------------|----------------------------|---------------------------------|----------|

| Supply Voltage Inputs                          |                   | $V_{CC}, V_{RGB}, V_{AUX}$ | GND-0.5 ~ +6.0                  | V        |

| Diode Forward Current<br>(One Diode Conducting |                   |                            | 20                              | mA       |

| DC Voltage at Inputs                           | R, G, B           |                            | GND-0.5 ~ V <sub>RGB</sub> +0.5 | V        |

|                                                | HSYNC, VSYNC      |                            | GND-0.5 ~ V <sub>AUX</sub> +0.5 | V        |

|                                                | DDC_CLK, DDC_DATA |                            | GND-0.5 ~ V <sub>CC</sub> +0.5  | <b>V</b> |

| Package Power Rating                           |                   |                            | 750                             | mW       |

| Operating Temperature Range                    |                   | T <sub>OPR</sub>           | 0 ~ +70                         | °C       |

| Storage Temperature Range                      |                   | T <sub>STG</sub>           | -40 ~ +150                      | ů        |

Note: Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

# ■ STANDARD OPERATING CONDITIONS

| PARAMETER                          |                   | SYMBOL           | TEST CONDITIONS | MIN | TYP | MAX       | UNIT |

|------------------------------------|-------------------|------------------|-----------------|-----|-----|-----------|------|

| Main Supply Voltage                |                   | Vcc              |                 | 4.5 |     | 5.5       | V    |

| RGB Supply Voltag                  | je                | $V_{RGB}$        |                 | 1.7 |     | 3.7       | V    |

| Auxiliary Supply Voltage           |                   | V <sub>AUX</sub> |                 | 2.9 |     | 3.7       | V    |

| Logic High Input Voltage (Note)    |                   | V <sub>IH</sub>  |                 | 2.0 |     |           | V    |

| Logic Low Input Voltage (Note)     |                   | V <sub>IL</sub>  |                 |     |     | 8.0       | V    |

| Input Voltage                      | RGB               | Vı               |                 | 0   |     | $V_{RGB}$ | V    |

|                                    | HSYNC, VSYNC      |                  |                 | 0   |     | $V_{AUX}$ | V    |

|                                    | DDC_CLK, DDC_DATA |                  |                 | 0   |     | Vcc       | V    |

| High Level Output Current (Note 1) |                   | Іон              |                 |     |     | -8        | mA   |

| Low Level Output Current (Note 1)  |                   | I <sub>OL</sub>  |                 |     |     | 8         | mA   |

| Free-Air Operating Temperature     |                   | T <sub>A</sub>   |                 | 0   |     | +70       | °C   |

Note: These parameters apply only to the HSYNC and VSYNC signals.

# ■ ELECTRICAL CHARACTERISTICS (Note 1)

| PARAMETER                                 |                        | SYMBOL                          | TEST CONDITIONS                                                                                   |       | TYP   | MAX   | UNIT |

|-------------------------------------------|------------------------|---------------------------------|---------------------------------------------------------------------------------------------------|-------|-------|-------|------|

| Diode For                                 | ward Voltage           | $V_{F}$                         | I <sub>F</sub> =10mA                                                                              |       |       | 1.0   | V    |

| Logic High                                | Output Voltage         | $V_{OH}$                        | $I_{OH}$ =-4mA, $V_{CC}$ =4.5V                                                                    | 4.0   |       |       | V    |

| Logic Low                                 | Output Voltage         | $V_{OL}$                        | I <sub>OL</sub> =4mA, V <sub>CC</sub> =4.5V                                                       |       |       | 0.4   | V    |

| Input<br>Current                          | R, G and B Pins        | I <sub>IN</sub>                 | $V_{RGB}$ =3.63V, $V_{IN}$ = $V_{RGB}$ or GND                                                     |       |       | ±1    | μΑ   |

|                                           | HSYNC, VSYNC<br>Pins   |                                 | V <sub>AUX</sub> =3.63V, V <sub>IN</sub> =V <sub>AUX</sub>                                        |       |       | ±1    | μΑ   |

|                                           | HSYNC, VSYNC<br>Pins   |                                 | V <sub>AUX</sub> =3.63V, V <sub>IN</sub> =GND                                                     | -30.0 | -72.5 | -95.0 | μA   |

| V <sub>CC</sub> upply Current             |                        | I <sub>CC</sub>                 | V <sub>CC</sub> =5.5V, V <sub>AUX</sub> =V <sub>RGB</sub> =2.97V, All Inputs and Outputs Floating |       | 35    | 100   | μΑ   |

| V <sub>RGB</sub> supply Current           |                        | I <sub>RGB</sub>                | R, G and B Pins at V <sub>CC</sub> r GND, All Inputs and Outputs Floating                         |       |       | 10    | μΑ   |

|                                           | R, G and B pins        | C <sub>IN</sub>                 | Note 2 Applies for All Cases                                                                      |       | 5     |       | pF   |

| Input                                     | HSYNC,<br>VSYNC pins   |                                 |                                                                                                   |       | 10    |       | pF   |

| Capacitance                               | DDC_DATA, DDC_CLK pins |                                 |                                                                                                   |       | 5     |       | pF   |

| Pull-up Resistance DDC_DATA, DDC_CLK pins |                        | $R_{PU}$                        |                                                                                                   | 1.52  | 1.80  | 1.98  | kΩ   |

| ESD Withstand Voltage                     |                        | $V_{ESD}$                       | V <sub>CC</sub> =5 V, V <sub>RGB</sub> =3.3V, V <sub>AUX</sub> =3.3 V                             |       |       |       | kV   |

| SYNC Buffer L≥H Propagation Delay         |                        | t <sub>PLH</sub>                | C <sub>L</sub> =50pF, V <sub>CC</sub> =5.0V, R <sub>L</sub> =500Ω (Note 3)                        |       | 7.0   | 15.0  | ns   |

| SYNC Buffer H≥L Propagation Delay         |                        | t <sub>PHL</sub>                | C <sub>L</sub> =50pF, V <sub>CC</sub> =5.0V, R <sub>L</sub> =500Ω (Note 3)                        | _     | 7.0   | 15.0  | ns   |

| SYNC Buffer Output Rise & Fall Times      |                        | t <sub>R</sub> , t <sub>F</sub> | C <sub>L</sub> =50pF, V <sub>CC</sub> =5.0V, R <sub>L</sub> =500Ω (Note 3)                        |       | 7.0   |       | ns   |

Notes: 1. All parameters specified over standard operating conditions unless otherwise noted.

- 2. Measured at 1MHz. R/G/B inputs biased at 1.65V with  $V_{RGB}$ =3.3V. DDC\_CLK and DDC\_DATA biased at 2.5V with  $V_{CC}$ =5V. HSYNC and VSYNC inputs biased at  $V_{AUX}$  or GND with  $V_{AUX}$ =3.3V and  $V_{CC}$ =5V.

- 3. Applicable to the SYNC buffers only. Input signals swing between 0V and 3.0V, with rise and fall times ≤5 ns. Guaranteed by correlation to buffer output drive currents.

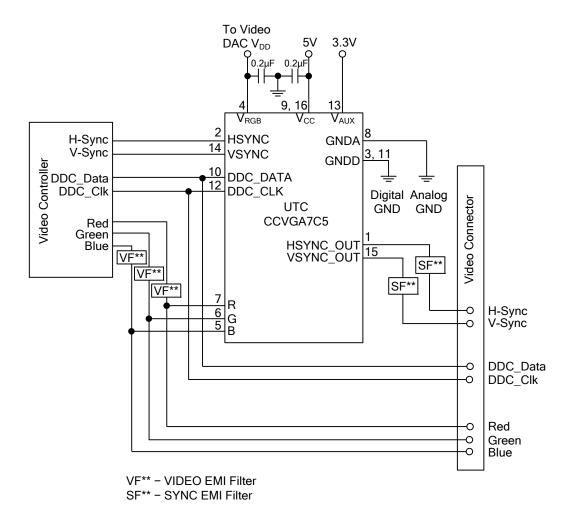

### ■ TYPICAL APPLICATION CIRCUIT

**Typical Connection Diagram**

GNDA, the negative voltage rail for the R, G and B diodes is not connected internally to GNDD. GNDA should ideally be connected to the ground of the video DAC IC. This will prevent any ground bounce caused by digital signals from injecting noise onto the R, G and B signals. Analog GND and digital GND are typically connected on the printed circuit board.

UTC assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all UTC products described or contained herein. UTC products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice.