## Single Chip CODEC/Filter Combo LSI

#### **EFEATURES**

- Single Chip CMOS CODEC with Filter in 16-pins DIL Package and 18-pins PLCC package.

- Power Supply Voltage ±5V±5%, Low Power Dissipation.

- μ-Law (HD44272P/CP, HD44274P/CP, HD44278P/CP)

A-Law (HD44271P/CP, HD44273P/CP, HD44277P/CP)

- Extremely Low Cost for the Digital PBX Terminal or Digital Handset Application.

- Internal Clock Generator.

- Anti-Aliasing Filter (2nd order CR Active Filter).

- Voltage Reference (Internal-Trimmed).

- Input Amplifier with Uncommitted Plus/Minus Terminals.

- Auto-Zero Cancel Circuit without External Component.

- Push/Pull Analog Output.

|             | 0            | Power<br>(Typ.) | Clock             |                         |                       | T                    | Output Amp   |             |  |

|-------------|--------------|-----------------|-------------------|-------------------------|-----------------------|----------------------|--------------|-------------|--|

| Туре        | Comp.<br>Law |                 | Internal<br>clock | Sync/Async<br>Operation | PCM bit<br>clock rate | Input<br>Amp         | Туре         | Min<br>load |  |

| HD44271P/CP | Α            | 70mW            | PLL               |                         | C4 20491 II           |                      | Push-        | [           |  |

| HD44272P/CP | μ            | 70mW            | Included          | 64-2048kHz              |                       | Pull                 |              |             |  |

| HD44273P/CP | A            | 50mW            | Divider           |                         | 1536/1544/2048        | Fully                | Single 600 s | 600.0       |  |

| HD44274P/CP | μ            | 50mW            | Included          | Both                    | kHz                   | Uncommited<br>Op-amp |              | 9002        |  |

| HD44277P/CP | Α            | 50mW            | PLL               | 1 1.                    | OP #11/P              | Ended                |              |             |  |

| HD44278P/CP | μ            | 50mW            | Included          |                         | 64-2048kHz            |                      |              |             |  |

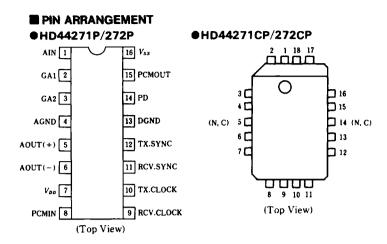

#### PIN DESCRIPTIONS

| N  | lo.       | Symbol    | Function           | Remarks                            |  |  |  |

|----|-----------|-----------|--------------------|------------------------------------|--|--|--|

| P  | CP        | Symbol    | runction           | Remarks                            |  |  |  |

| 1  | 1         | AIN       | Analog input       |                                    |  |  |  |

| 2  | 2         | GAI       | Gain adjust 1      | Feed-back input                    |  |  |  |

| 3  | 3         | GA2       | Gain adjust 2      | $10k\Omega < R_L, C_L < 100pF$     |  |  |  |

| 4  | 4         | AGND      | Analog ground      |                                    |  |  |  |

| 5  | 6 AOUT(+) |           | A \                | $R_L > 600Q$ , $C_L < 100pF$       |  |  |  |

| 6  | 7         | AOUT(-)   | Analog output      | $R_L > 600\Omega$ , $C_L < 100 pF$ |  |  |  |

| 7  | 8         | VDD       | Positive pow. sup. | 5V ± 5%                            |  |  |  |

| 8  | 9         | PCMIN     | PCM data input     | (TTL)                              |  |  |  |

| 9  | 10        | RCV. CLK  | DCM 1 % -1 - 1     | (TTL)64kHz to                      |  |  |  |

| 10 | 11        | TX. CLK   | PCM bit clock      | 2048kHz                            |  |  |  |

| 11 | 12        | RCV. SYNC | Comphysication     | (TTI \ OLII-                       |  |  |  |

| 12 | 13        | TX. SYNC  | Synchronization    | (TTL) 8kHz                         |  |  |  |

| 13 | 15        | DGND      | Digital ground     | , , , , ,                          |  |  |  |

| 14 | 16        | PD        | Power down         | (TTL) "0"=down                     |  |  |  |

| 15 | 17        | PCMOUT    | PCM data output    | Open drain                         |  |  |  |

| 16 | 18        | Vss       | Negative pow. sup. | -5V±5%                             |  |  |  |

|    | 5, 14     | N.C.      | <del></del>        | Open                               |  |  |  |

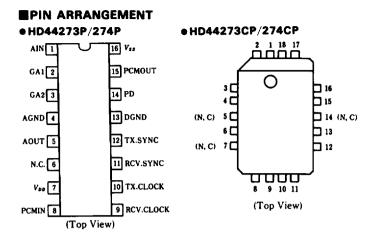

## **MPIN DESCRIPTIONS**

| N  | lo.      | Symbol    | Function           | Dama da                                      |  |  |  |

|----|----------|-----------|--------------------|----------------------------------------------|--|--|--|

| P  | CP       | Symbol    | runction           | Remarks                                      |  |  |  |

| 1  | 1        | AIN       | Analog input       |                                              |  |  |  |

| 2  | 2        | GA1       | Gain adjust 1      | Feed-back input                              |  |  |  |

| 3  | 3        | GA2       | Gain adjust 2      | 10kΩ < R <sub>L</sub> C <sub>L</sub> < 100pF |  |  |  |

| 4  | 4        | AGND      | Analog ground      |                                              |  |  |  |

| 5  | 6        | AOUT      | Analog output      | $R_L > 600\Omega$ , $C_L < 100 \mathrm{pF}$  |  |  |  |

| 7  | 8        | $V_{DD}$  | Positive pow. sup. | 5V ± 5%                                      |  |  |  |

| 8  | 9        | PCMIN     | PCM data imput     | (TTL)                                        |  |  |  |

| 9  | 10       | RCV. CLK  | PCM bit clock      | (TTL) 2048/1544/                             |  |  |  |

| 10 | 11       | TX. CLK   | PCIM BIL CIOCK     | 1536kHz                                      |  |  |  |

| 11 | 12       | RCV. SYNC | Comphanication     | (TTL) 8kHz                                   |  |  |  |

| 12 | 13       | TX. SYNC  | Synchronization    | (IIL) oknz                                   |  |  |  |

| 13 | 15       | DGND      | Digital ground     |                                              |  |  |  |

| 14 | 16       | PD        | Power down         | (TTL) "0" = down                             |  |  |  |

| 15 | 17       | PCMOUT    | PCM data output    | Open drain                                   |  |  |  |

| 16 | 18       | Vss       | Negative pow. sup. | -5V±5%                                       |  |  |  |

| 6  | 5, 7, 14 | N.C.      |                    | Open                                         |  |  |  |

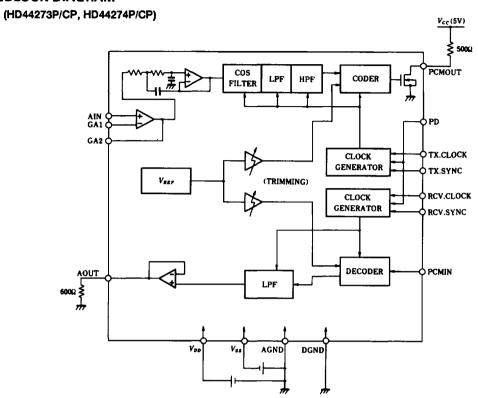

#### **BBLOCK DIAGRAM**

## **■PIN/FUNCTION DESCRIPTIONS**

# HD44271P/CP, HD44272P/CP, HD44277P/CP, HD44278P/CP

| Pin                        | N                  | lo                 | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------|--------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I :11                      | P                  | CP                 | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| TX. CLOCK<br>RCV. CLOCK    | 9<br>10            | 10<br>11           | Any of 64kHz to 2.048MHz clock can be accepted with the pins. And they are automatically divided down to provide the internal clocks.  These TTL compatible inputs shift PCM data out of the coder on the positive going edges and PCM data into the decoder on the negative going edges after receiving a positive edge on the TX. SYNC/RCV. SYNC respectively.                                                                                                                                                                                                                      |

| TX. SYNC<br>RCV. SYNC      | 11<br>12           | 12<br>13           | These TTL compatible pulse inputs (typ. 8kHz) are used for analog sampling and for initiating the PCM output from the coder and initiate clocking of PCM input data into the decoder. They must be synchronized with the TX.CLOCK/RCV.CLOCK with these positive going edges occurring after the falling edge of the TX.CLOCK/RCV. CLOCK respectively. The width of these signals are not critical. An internal bit counter generates the necessary timing for PCM output and input.                                                                                                   |

| PCMOUT                     | 15                 | 17                 | This is a LS-TTL compatible open-drain output. It is active only during transmission of PCM output for 8 bit periods of CLOCK, TX.CLOCK/RCV.CLOCK signal following a positive edge on the SYNC, TX/SYNC. RCV. SYNC input. Data is clocked out by the positive edge of the CLOCK. One $500\Omega$ pull-up per 8 CODECs is required.                                                                                                                                                                                                                                                    |

| PCMIN                      | 8                  | 8                  | This is a TTL compatible input for supplying PCM input data to the decoder. Data is clocked in by the negative edge of RCV. CLOCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| AIN<br>GA1<br>GA2          | 1<br>2<br>3        | 1 2 3              | These three pins are provided for connecting analog signals in the range of VREF to + VREF to the device the input stage can be connected as a unity gain amplifier, with gain or amplifier with adjustable gain. The adjustable gain configuration will facilitate calibration of the transmit channel. AIN is the input of analog signal of the amplifier. GA2 is the output of the amplifier. GA2 shall be loaded by the resistor above $10k\Omega$ or directly connected to GA1. GA1 is the negative feed back input of the amplifier. Ci. should be less than $100\mathrm{pF}$ . |

| AOUT(+)                    | 5                  | 6                  | This is the buffered output of the recreated analog signal from the received PCM data words. It can drive the impedance of $600\Omega$ . C <sub>I</sub> . should be less than $100\mathrm{pF}$ .                                                                                                                                                                                                                                                                                                                                                                                      |

| Vnn<br>Vss<br>AGND<br>DGND | 7<br>16<br>4<br>13 | 8<br>18<br>4<br>15 | These are power supply pins. $V_{DD}$ and $V_{SS}$ are positive and negative supply pins respectively (typ. $+5V$ , $-5V$ ).  Analog and digital ground pins are separate for minimizing crosstalk.                                                                                                                                                                                                                                                                                                                                                                                   |

| PD                         | 14                 | 16                 | This TTL compatible input when held low puts the chip into the powered down mode regardless of strobes. The chip will also power down if the strobes stop. The strobes can be high, low or floating, but as long as they are static, the powered down mode is in effect.                                                                                                                                                                                                                                                                                                              |

| AOUT(-)*                   | 6                  | 7                  | This is the inverted output of pin 5 signal output to drive the $600\Omega$ transformer as the push-pull operation. $R_L < 600\Omega$ , $C_L < 100$ pF.                                                                                                                                                                                                                                                                                                                                                                                                                               |

**<sup>\*</sup>ONLY FOR HD44271, 272P/CP**

## ■PIN/FUNCTION DESCRIPTIONS

# HD44273P/CP, HD44274P/CP

| Pin                        | No                                     |                    | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------|----------------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| t.m                        | P                                      | CP                 | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| TX. CLOCK<br>RCV. CLOCK    | 9<br>10                                | 10<br>11           | One of 1.536, 1.544 and 2.048MHz clock can be accepted with the pins. And they are automatically divided down to provide the internal clocks.  These TTL compatible inputs shift PCM data out of the coder on the positive going edges and PCM data into the decoder on the negative going edges after receiving a positive edge on the TX. SYNC/RCV. SYNC respectively.                                                                                                                                                                                                                                   |

| TX. SYNC<br>RCV. SYNC      | 11<br>12                               | 12<br>13           | These TTL compatible pulse inputs (typ. 8kHz) are used for analog sampling and for initiating the PCM output from the coder and initiate clocking of PCM input data into the decoder. They must be synchronized with the TX.CLOCK/RCV.CLOCK with these positive going edges occurring after the falling edge of the TX.CLOCK/RCV. CLOCK respectively. The width of these signals are not critical. An internal bit counter generates the necessary timing for PCM output and input.                                                                                                                        |

| PCMOUT                     | UT 15 17 output for 8 bit the SYNC, TX |                    | This is a LS-TTL compatible open-drain output. It is active only during transmisson of PCM output for 8 bit periods of CLOCK, TX.CLOCK/RCV.CLOCK signal following a positive edge on the SYNC, TX/SYNC. RCV. SYNC input. Data is clocked out by the positive edge of the CLOCK. One 500 Ω pull-up per 8 CODECs is required.                                                                                                                                                                                                                                                                                |

| PCMIN                      | 8                                      | 9                  | This is a TTL compatible input for supplying PCM input data to the decoder. Data is clocked in by the negative edge of RCV. CLOCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| AIN<br>GA1<br>GA2          | 1<br>2<br>3                            | 1<br>2<br>3        | These three pins are provided for connecting analog signals in the range of $V_{\rm REF}$ to $^{\perp}$ $V_{\rm REF}$ to the device The input stage can be connected as a unity gain amplifier, with gain or amplifier with adjustable gain. The adjustable gain configuration will facilitate calibration of the transmit channel. AIN is the input of analog signal of the amplifier. GA2 is the output of the amplifier. GA2 shall be loaded by the resistor above $10k\ \Omega$ or directly connected to GA1. GA1 is the negative feed back input of the amplifier. CL should be less than $100\ pF$ . |

| AOUT                       | 5                                      | 6                  | This is the buffered output of the recreated analog signal from the received PCM data words. It can drive the impedance of $600\Omega$ . CL should be less than $100pF$ .                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Vod<br>Vss<br>AGND<br>DGND | 7<br>16<br>4<br>13                     | 8<br>18<br>4<br>15 | These are power supply pins. $V_{\rm DD}$ and $V_{\rm SS}$ are positive and negative supply pins respectively (typ. +5V, -5V). Analog and digital ground pins are separate for minimizing crosstalk.                                                                                                                                                                                                                                                                                                                                                                                                       |

| PD                         | 14                                     | 16                 | This TTL compatible input when held low puts the chip into the powered down mode regardless of strobes. The chip will also power down if the strobes stop. The strobes can be high, low or floating, but as long as they are static, the powered down mode is in effect.                                                                                                                                                                                                                                                                                                                                   |

#### **MADSOLUTE MAXIMUM RATINGS**

| Item                         | Rating                                                   |

|------------------------------|----------------------------------------------------------|

| Von                          | -0.3 to +7V                                              |

| Vss                          | +0.3 to -7V                                              |

| Storage temperature          | -55°C to +125°C                                          |

| Power dissipation            | 0.5W                                                     |

| Digital input/output voltage | $-0.3V < V_{IN} < V_{DD} + 0.3V$                         |

| Analog input/output voltage  | $V_{SS} - 0.3 \text{V} < V_{IS} < V_{DD} + 0.3 \text{V}$ |

#### **BELECTRICAL CHARACTERISTICS**

**STATIC CHARACTERISTICS** ( $V_{DD} = 5 \pm 0.25 \text{V}$ ,  $V_{SS} = -5 \pm 0.25 \text{V}$ ,  $V_{CC} = 5 \pm 0.25 \text{V}$ ,  $T_e = 0 \text{ to } +70 ^{\circ}\text{C}$ )

| Descriptios                      | Symbol           | P               | CP               | min      | typ  | max  | Note/condition                          | Unit |

|----------------------------------|------------------|-----------------|------------------|----------|------|------|-----------------------------------------|------|

| V <sub>DD</sub> current (ope.)   | $I_{DD}$         | 7               | 8                | _        | 8.0  | 13.5 | Note 1                                  |      |

| V <sub>SS</sub> current (ope.)   | Iss              | 16              | 18               | -13.0    | -7.5 |      | AIN = 0V<br>PCMIN = +0code              |      |

| V <sub>DD</sub> current (st.by.) | IDDST            | 7               | 8                | _        | 0.4  | 1.0  | $R_L \text{ (GA2)} = 10\text{k }\Omega$ | mA   |

| Vss current (st.by.)             | ISSST            | 16              | 18               | -0.2     | _    | -    | $R_L$ (AOUT) = 600 $\Omega$             |      |

|                                  | <u> </u>         | 1, 2, 8         | 1, 2, 9          | -10.0    | _    | 10.0 | $V_{M} = 0.8V$                          | μА   |

| Leak current                     | $I_L$            | 9, 10           | 10, 11           | -10.0    | _    | 10.0 | $V_M = 2.0 \text{V}$                    | μА   |

|                                  |                  | 14              | 16               | -        | -    | 10.0 | $V_{DD} = V_M = 5.25 \text{V}$          | μA   |

| Pull up current                  | IPL              | 11, 12          | 12, 13           | -100     | -    | 0    |                                         | μA   |

| Leak current                     | IDL              | 15              | 17               | -        | _    | 10.0 | $V_{DD} = V_M = 5.25 \text{V}$          | μA   |

| Analog input cap.                | CAIN1            | 1               | 1                | -        | -    | 10   | at 1MHz Vbias = 0                       | pF   |

| Analog input cap.                | CAIN2            | 2               | 2                | -        | _    | 10   | at 1MHz Vbias = 0                       | pF   |

| Input capacitance                | CDIN             | 8,9,10,11,12,14 | 9,10,11,12,13,16 | -        | -    | 10   | at 1MHz Vbias = 0                       | pF   |

| AOUT resistance                  | ROUTA            | 5, (6)          | 6, (7)           | -        | 1    | 20   |                                         | Ω    |

| GA2 resistance                   | ROUTG            | 3               | 3                | -        | _    | 50   | Note 1                                  | Ω    |

| GA2 output swing                 | V <sub>GSW</sub> | 3               | 3                | -3.0     | -    | 3.0  | $R_L = 10 \text{k}\Omega$               | v    |

| Analog offset input              | Voffin           | 1               | 1                | -200     | _    | 200  | Note 1                                  | mV   |

| GA2 offset output                | VoffG            | 3               | 3                | -50      | _    | 50   | Note 1                                  | mV   |

| AOUT offset output               | Voffa            | 5, (6)          | 6, (7)           | -100     | _    | 100  | PCMIN = +0 code                         | mV   |

| PCMOUT capacitance               | CDOUT            | 15              | 17               | -        |      | 15.0 | at 1MHz, Vbias = 0V                     | pF   |

| PCMOUT low voltage               | Vol              | 15              | 17               | -        | _    | 0.4  | $R_L = 500\Omega$ , $+I_{OL} = 0.8$ mA  | v    |

| PCMOUT high voltage              | Vон              | 15              | 17               | Vcc -3.0 | -    | _    | <i>IoH</i> = -150μA                     | v    |

| Digital input high voltage       | V <sub>IH</sub>  | 8,9,10,11,12,14 | 9,10,11,12,13,16 | 2.0      | 1    | -    |                                         | v    |

| Digital input low voltage        | $V_{IL}$         | 8,9,10,11,12,14 | 9,10,11,12,13,16 | -        | -    | 0.8  |                                         | V    |

Note 1) Analog input amplifier gain = 0 dB (GA1 is connected to GA2)

<sup>( ):</sup> Only for HD44271, 272P/CP

#### **DYNAMIC-CHARACTERISTICS** ( $V_{DD} = 5 \pm 0.25 \text{V}$ , $V_{SS} = -5 \pm 0.25 \text{V}$ , $V_{CC} = 5 \pm 0.25 \text{V}$ , $T_{\bullet} = 0 \text{ to } + 70 ^{\circ}\text{C}$ )

| Descriptions                 | Symbol           | Note         | min | typ | max  | Uni |

|------------------------------|------------------|--------------|-----|-----|------|-----|

| Synchronization rate         | Fs               |              | -   | 8   | -    | kH  |

| PCM bit clock rate           | Fc               |              | 64  | -   | 2048 | kHz |

| Clock pulse width            | ter              |              | 200 |     | _    | ns  |

| Sync pulse high width        | t <sub>eSH</sub> |              | 200 | _   | _    | ns  |

| Sync pulse low width         | trsi.            |              | 8   | -   | -    | ns  |

| Logic input rise time        | t.               |              | 5   | _   | 50   | ns  |

| Logic input fall time        | tı               |              | 5   | _   | 50   | ns  |

| Previous clock to Sync delay | tucs             | Note 1       | 40  |     |      | ns  |

| Clock to sync delay          | t <sub>es</sub>  | Note 1, 3    | -   | -   | 100  | ns  |

| Clock to PCM MSB delay       | t <sub>ed</sub>  | Note 1, 2, 4 | _   | _   | 170  | ns  |

| Sync to PCM MSB delay        | , to a           | Note 1, 2, 4 | _   | _   | 170  | ns  |

| Clock to PCM OUT delay       | led .            | Note 1, 2, 5 | _   |     | 180  | ns  |

| PCMIN setup time             | L.               | Note 1       | 65  |     | -    | ns  |

| PCMIN hold time              | Drut             | Note 1       | 120 |     | _    | ns  |

Note 1) h, h of digital input or clock is assumed 5ns for timing measurement.

#### **OSYSTEM RELATED CHARACTERISTICS**

$(V_{DD} = 5 \pm 0.25 \text{V}, V_{SS} = -5 \pm 0.25 \text{V}, V_{CC} = 5 \pm 0.25 \text{V}, T_a = 0 \text{ to } +70 ^{\circ}\text{C}$ , INPUT AMPLIFIER GAIN = 0dB, ANALOG OUT PUT = AOUT(-), GA2 LOAD = 10k  $\Omega$ , AOUT LOAD = 600  $\Omega$ , Synchronous operation. fc (PCM BIT CLOCK) = 2048kHz)

#### A-law (HD44271P/CP, HD44273P/CP, HD44277P/CP)

| Descriptions                   | Symbol | Test condition          | ons                        | min   | typ | max | Unit  | Note         |

|--------------------------------|--------|-------------------------|----------------------------|-------|-----|-----|-------|--------------|

|                                |        |                         | - 45dBm0                   | 23    | -   | _   |       | <del> </del> |

| Signal to dist,(A to A)        | SDA    | 820Hz tone              | -40                        | 28    | 1   | _   | dB    | p-wgt        |

|                                |        |                         | -30, -20, -10,0            | 34    | _   | _   | Ì     |              |

|                                |        | 90011-4                 | -55dBm0                    | - 1.0 | -   | 1.0 |       |              |

| Gain track. (A to A)           | GTA    | 820Hz tone              | -50                        | -0.5  | -   | 0.5 | dB    |              |

|                                |        | Relative to -10dBm0     | -40, -30, -20,<br>-10, 0,3 | -0.3  |     | 0.3 |       |              |

| <del></del>                    |        |                         | 0.06kHz                    | 24    | -   | _   |       | •            |

| Freq. response. (A to D)(Loss) |        | 0.2                     |                            | 0     |     | 2.5 |       |              |

|                                | FRX    | Relative to 820Hz 0dBm0 | 0.3 to 3                   | - 0.3 | _   | 0.3 | dB    |              |

|                                |        |                         | 3.4                        | 0     | -   | 0.8 | }     |              |

|                                |        |                         | 3.78                       | 6.5   |     |     |       |              |

|                                |        | Relative to 820Hz 0dBm0 | 0 to 3kHz                  | - 0.3 | _   | 0.3 |       |              |

| Freq. response.(D to A)(Loss)  | FRR    |                         | 3.4                        | 0     | _   | 0.8 | dB    |              |

|                                |        |                         | 3.78                       | 6.5   | -   | -   |       |              |

| Analog input level variation   | AIL    | 820Hz 0dBm0             | Relative to<br>1.231 Vrms  | - 0.5 | _   | 0.5 | dB    |              |

| Analog output level            | AOL    | 820Hz 0dBm0             | Relative to<br>1.231 Vrms  | -0.5  | _   | 0.5 | dB    |              |

| Idle ch. noise                 | ICNX   | A to D                  | AIN=AGND                   | 1     | -   | -80 | dBmOP |              |

| Idle ch. noise                 | ICNR   | D to A                  | PCMIN =<br>+0-Code         |       |     | -80 | dBmOP |              |

| AIN to AOUT crosstalk          | XTKA   | 820Hz                   | 0dBm0                      | _     | _   | -65 | dB    |              |

| PCMIN to PCMOUT                | XTKD   | 820Hz                   | 0dBm0                      | _     | _   | -65 | dB    |              |

| PSRR                           | PSRR   | A to A                  | 0.3 to 50kHz               | _     | 40  | -   | dB    |              |

<sup>2)</sup> PCMOUT load condition: 500 Q + 165pF + two LS-TTL Equivalent (In = 0.8mA, In = -150 µA) Threshold level (Vm = 2.4V, Vm = 0.4V)

<sup>3)</sup> Positive value shows SYNC delay from CLOCK.

<sup>4)</sup> tell, by are specified by CLOCK or SYNC which has slower rise time.

<sup>5)</sup> ha specification is valid for the data except MSB.

# HD44270P/CP

## $\mu$ -law (HD44272P/CP, HD44274P/CP, HD44278P/CP)

| Descriptions                   | Symbol | Test condition                     | ns                        | min   | typ | max  | Unit   | Note  |

|--------------------------------|--------|------------------------------------|---------------------------|-------|-----|------|--------|-------|

|                                |        | ·                                  | -45dBm0                   | 23    | _   | _    |        |       |

| Signal to dist.(A to A)        | SDA    | 1020Hz tone                        | -40                       | 28    | _   | _    | dB     | c-wgt |

|                                |        |                                    | -30,-20,<br>-10,0         | 34    |     | _    |        |       |

|                                |        | 102011 - tomo moletino             | - 55dBm0                  | -1.0  | _   | 1.0  |        |       |

| Gain Tracking(A to A)          | GTA    | 1020Hz tone relative<br>to -10dBm0 | -50                       | -0.5  | _   | 0.5  | đВ     |       |

|                                |        | to -10dBm0                         | -40, -30, -20,<br>-10,0,3 | -0.3  | 1   | 0.3  |        |       |

|                                |        |                                    | 0.06kHz                   | 24    |     | _    |        |       |

|                                |        | Relative to 1020Hz<br>0dBm0        | 0.2                       | 0     | 1   | 2.5  |        |       |

| Freq.Response.(A to D)(Loss)   | FRX    |                                    | 0.3 to 3                  | - 0.3 | _   | 0.3  | đВ     |       |

|                                |        |                                    | 3.4                       | 0     | -   | 0.8  |        |       |

|                                |        |                                    | 3.78                      | 6.5   | _   | _    |        |       |

|                                |        | Relative to 1020Hz<br>0dBm0        | 0 to 3kHz                 | - 0.3 | _   | 0.3  |        |       |

| Freq. Response. (D to A)(Loss) | FRR    |                                    | 3.4                       | 0     | _   | 0.8  | dB     |       |

|                                |        |                                    | 3.78                      | 6.5   | _   | -    |        |       |

| Analog input level             | AIL    | 1020Hz 0dBm0                       | Relative to<br>1.227 Vrms | - 0.5 | -   | 0.5  | dB     |       |

| Analog output level            | AOL    | 1020Hz 0dBm0                       | Relative to<br>1.227 Vrms | - 0.5 | _   | 0.5  | dB     |       |

| Idle ch. noise                 | ICNX   | A to D                             | AIN=AGND                  | _     | _   | 16   | dBrnCO |       |

| Idle ch. noise                 | ICNR   | D to A                             | PCMIN =<br>+0-code        | _     | -   | 10   | dBrnCO |       |

| AIN to AOUT crosstalk          | XTKA   | 1020Hz 0dBm0                       |                           | -     | -   | - 65 | dΒ     |       |

| PCMIN to PCMOUT crosstalk      | XTKD   | 1020Hz 0dBm0                       |                           | _     | 1   | - 65 | dB     |       |

| PSRR                           | PSRR   | A to A                             | 0.3 to 50kHz              | _     | 40  | _    | dΒ     |       |

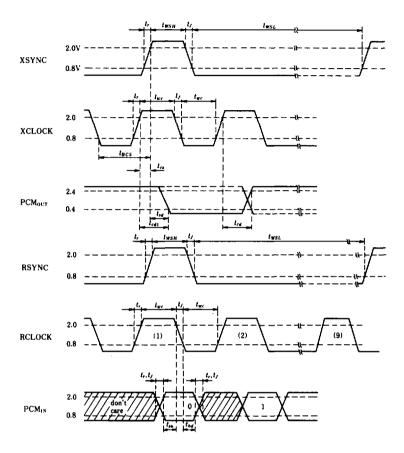

# **TIMING CHART**

# **Notes on Using CODEC LSIs**

This section discusses protection procedures that should be considered when using CODEC devices.

Latchup Protection: Latchup is a thyristor phenomenon, unique to CMOS structures, caused by parasitic pnp or npn transistors. Since all Hitachi CODEC LSIs employ CMOS structure, general latchup protection is useful.

A CODEC has four power supply pins: AGND, DGND, V<sub>DD</sub>, and V<sub>SS</sub>. Power should be applied to these pins in the proper order. Voltage exceeding the absolute maximum ratings may cause damage to the device.

Inserting Boards: Special care should be taken when inserting or replacing a board containing CODECs with the system power on. When the usual slow-starting power supply is turned on, voltages at each part of the board change slowly. Accordingly, a reverse current seldom exceeds the maximum rating. However, when a board is inserted with the power on, a rapid voltage change can occur. This might cause device destruction, thermally dis-connecting VDD or VSS on the device.

In the case of  $V_{\rm DD}$  disconnection, substrate bias is derived from I/O pins (because of the substrate's CMOS characteristics) resulting in unstable operation with the S/N ratio reduced. Thus, hot line insertion is not recommended from the standpoint of reliability. If this is unavoidably required, the following must be considered. Hitachi CODEC HD44230 and 240 series

incorporate an inverse potential prevention circuit to prevent  $V_{SS}$  pin voltage from rising. This circuit can effectively prevent device destruction caused through hot line insertion.

During power up sequence where a +5 V V<sub>DD</sub> pin is set up first, part of the negative supply current is dissipated to temporarily activate the prevention circuit. Thus, ensure that the current capacity is high enough to set up the transition at power up.

When power must be applied to a large number of lines, the current capacity margin must set up -5 V at the V<sub>SS</sub> pin. After the power up sequence is complete, the current flowing in the prevention circuit is cut off. Accordingly, the current of the rated input voltage is specified as a supply current in individual data sheets. In Hitachi CODECs, a sufficient current capacity is preserved at the negative power set up by simultaneously setting up two different types of slow-starter power supplies or by first setting up a -5 V V<sub>SS</sub> pin.

DGND and AGND Connection on a Board: It is usually recommended that bypass capacitors be inserted between DGND and  $V_{DD}$  and between AGND and  $V_{SS}$ . However, CMOS structure is also formed between DGND and  $V_{DD}$ . If DGND and AGND are connected separately on a board, the impedance between  $V_{DD}$  and DGND becomes higher, which increases the possibility of latchup generated by noise during power up. The best way to prevent this is to connect the DGND and  $V_{DD}$  pins together just before the CODEC. If the two lines are separately traced, they can be connected together just before the socket.

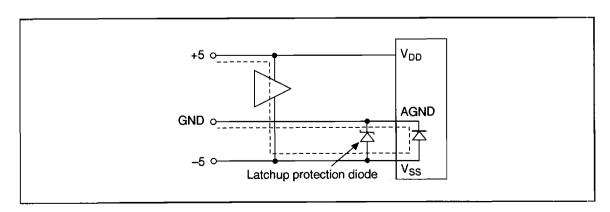

Figure 1 Latchup Protection Diode

## HD44270P/CP

Insertion of Diodes against Inverse Voltage: If devices such as resistors and operational amps are inserted between  $V_{DD}$  and  $V_{SS}$ , current flows in the path of  $V_{DD}$  to  $V_{SS}$  to AGND/DGND through parasitic diodes in the CODEC (figure 1). To eliminate this current, it is recommended that a diode such as a Schottky diode be placed to suppress the voltage between AGND and  $V_{SS}$  to under 0.5 V. The current capacity of the diode should be determined based on the amount of current flowing from external circuits.

Currents Flowing from Other Power Supplies: Power supplies available on the CODEC board include  $\pm 12$  V,  $\pm 15$  V, and -4.8 V. These supplies may overdrive the  $\pm 5$  V CODEC I/O pins. Usually, the current flowing through devices is not large enough to cause latchup, but care should be taken.

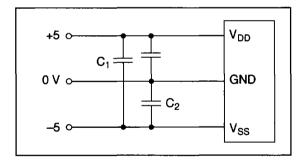

Bypass Capacitors: When bypass capacitors are inserted between different power supplies, the potential may be inversed temporarily depending on the order in which the supplies are turned on (figure 2). The following phenomenon can occur:

1. With capacitors placed between the V<sub>DD</sub>, V<sub>SS</sub>,

Figure 2 Bypass Capacitors

and AGND pins, when  $V_{DD}$  and GND are powered with  $V_{SS}$  open,  $V_{SS}$  potential will rise to  $V_{DD} \times C1/(C1 + C2)$ , which may raise  $V_{SS}$  to a positive potential. However, a fairly large capacitance is required for potential inversion.

2. In an application with a bypass capacitor between a -4.8 V power supply and the GND, when -4.8 volts are applied with GND open, the GND potential may be pulled up to -4.8 V and exceed the V<sub>SS</sub> (-5 V).

The more power supplies are used, the more cases of inverse potential should be considered. Inverse potential can be prevented by providing larger bypass capacitors between  $V_{DD}$  and GND (including AGND and DGND) and between GND and  $V_{SS}$ .

Inserting the CODEC into a Socket: Power should be turned off before the CODEC is inserted into a socket. Insertion with power on may destroy the CODEC because the bypass capacitors have no effect.

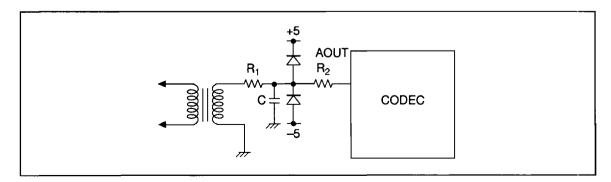

Connecting to a Transformer or Coil: Special care should be taken when connecting a transformer for a audio circuit with the CODEC. A voltage beyond the power supply voltage may be applied to the inputs when:

- Rush currents are caused by intermittent currents through a telephone circuit

- Lightning surge leakage exists between coils

- · Substrate potential has risen

The circuit in figure 3 can effectively prevent this problem. The peak voltage can be suppressed by a

Figure 3 Surge Prevention Circuit

filter consisting of R1 and C (floating capacitance only is sufficient) and clamped by diodes. This prevents AOUT or AIN from being overdriven. Most cases do not require R2.

When long lines are connected to CODEC pins, such as a microphone input and earphone output, these pins should be protected from noise such as external spikes. When piezo elements are used for the microphone and earphone pins, these pins should also be protected from the piezo effect when stress is applied.

**Digital Output:** Digital output pins employ open drain structure, but the substrate (well) is connected to DGND. Accordingly, voltages below DGND (0 V) at these pins may cause latchup. Additionally, loading capacitance and transmission reflection effects should be considered. Since a diode is provided between  $V_{DD}$  and digital outputs, pull-up voltage must not exceed  $V_{DD}$ .