## Advance DATA SHEET

# LC1092AP/BP AC PLASMA DISPLAY COLUMN DRIVERS

#### DESCRIPTION

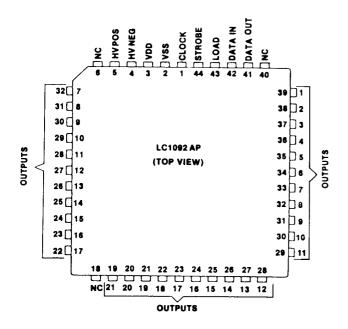

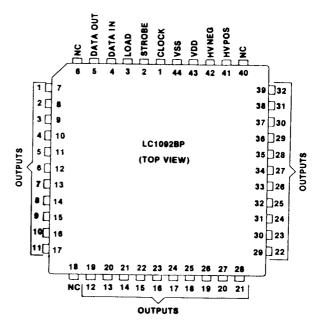

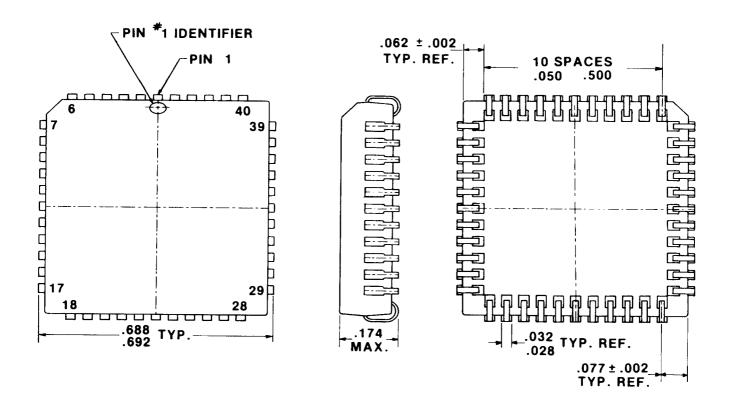

The LC1092AP and LC1092BP are high-voltage CMOS (HV-CMOS) integrated circuits that are assembled in 44-pin plastic J-leaded chip carriers. The LC1092BP pinout alignment is the mirror image of the LC1092AP pinout alignment (see Figures 2 and

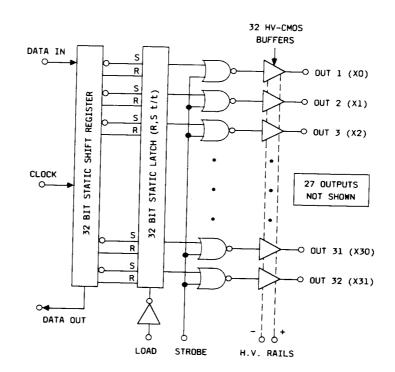

The devices contain a 32-bit shift register which can accept serial data at clock rates up to 10 MHz. A LOAD feature is supplied to allow parallel transfer of the shift register data to a 32-bit latch. Data is transferred on a high-to-low transition of the LOAD signal. The contents of the latch are transferred in parallel to the high-voltage output buffers by means of the STROBE input. These high-voltage buffers will deliver voltage swings of ≤100 volts. Serial data output from the shift register may be used to cascade shift registers. This output is not affected by either the LOAD or STROBE inputs. The LB1092AP/BP can also be operated in a pulsed HV<sub>POS</sub> mode (100-volt swing) with a minimum rise time (10 to 90%) of 0.3  $\mu$ sec and a minimum fall time (10 to 90%) of  $0.5~\mu sec.$

#### **FEATURES**

- 32-BIT SHIFT REGISTER

- 32-BIT LATCH

- 100-VOLT PUSH-PULL CMOS OUTPUTS

- 10 MHz DATA CLOCK RATE

- EACH DEVICE DRIVES 32 LINES

Fig. 1—Functional Diagram

AT&T reserves the right to make changes to the product(s) or circuit(s) described herein without notice. No liability is assumed as a result of their use or application. No rights under any patent accompany the sale of any such product or circuit.

© 1986 AT&T. All Rights Reserved.

**NOVEMBER 1986**

Fig. 2—LC1092AP Package Pinout

Fig. 3—LC1092BP Package Pinout

| MAXIMUM RATINGS (At 25°C unless otherwise specified) |            |

|------------------------------------------------------|------------|

| Ambient Operating Temperature Range                  | 0 to +60°C |

| Storage Temperature Range                            |            |

| Lead Soldering Temperature (t = 10 sec. max.)        |            |

| Supply Voltage (HV <sub>POS</sub> )①                 |            |

| Supply Voltage (HV <sub>NEG</sub> )①                 |            |

| Logic Supply Voltage (VDD)                           |            |

| INPUT Voltage                                        |            |

| Current (Each Driver Output)                         |            |

| Power Dissipation                                    |            |

Stresses in excess of those listed under "Maximum Ratings" may cause permanent damage to the device. This is an absolute stress rating only. Functional operation of the device at these or any other conditions in excess of those indicated in the operational sections of this Data Sheet is not implied. Exposure to maximum rating conditions for extended periods of time may affect device reliability.

1)The difference between HV<sub>POS</sub> and HV<sub>NEG</sub> must never exceed 100 volts. HV<sub>POS</sub> must always be positive with respect to HV<sub>NEG</sub>.

#### PIN DESCRIPTION AND TIMING REQUIREMENTS

| SYMBOL            | NAME/FUNCTION                                                                                                                                                        |  |  |  |  |  |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| CLOCK             | Input for clocking functions. The leading edge of CLOCK must come ≥20 nsec after valid DATA. Clock must remain high for ≥30 nsec.                                    |  |  |  |  |  |  |  |

| DATA IN           | Input for data stream. DATA must be valid for 12 nsec after CLOCK goes high.                                                                                         |  |  |  |  |  |  |  |

| DATA OUT          | Serial data output from the Shift Register may be used to cascade shift registers.                                                                                   |  |  |  |  |  |  |  |

| STR0BE            | STROBE can go low ≥20 nsec after LOAD goes low.                                                                                                                      |  |  |  |  |  |  |  |

| LOAD              | LOAD can go low ≥30 nsec after CLOCK goes high.                                                                                                                      |  |  |  |  |  |  |  |

| NC                | No connection. This terminal should <u>not</u> be used as a tie point for external circuitry.                                                                        |  |  |  |  |  |  |  |

| VDD               | Logic supply voltage. Normal operating voltage is +5.0 V (±0.25 V).                                                                                                  |  |  |  |  |  |  |  |

| VSS               | Logic common (not necessarily system or physical ground).                                                                                                            |  |  |  |  |  |  |  |

| HV <sub>POS</sub> | External power supply. $HV_{POS}$ must always be positive with respect to $HV_{NEG}$ . The difference between $HV_{POS}$ and $HV_{NEG}$ must never exceed 100 volts. |  |  |  |  |  |  |  |

| HV <sub>NEG</sub> | External power supply. $HV_{NEG}$ must always be negative with respect to $HV_{POS}$ . The difference between $HV_{POS}$ and $HV_{NEG}$ must never exceed 100 volts. |  |  |  |  |  |  |  |

| OUT XX            | High-voltage CMOS outputs numbered 1 through 32.                                                                                                                     |  |  |  |  |  |  |  |

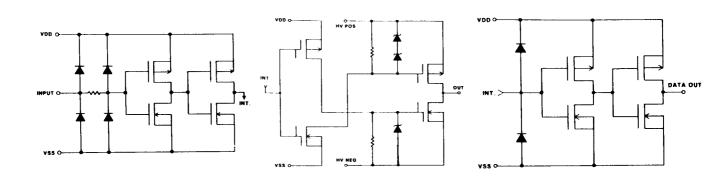

#### SIMPLIFIED INPUT AND OUTPUT DIAGRAMS

Fig. 4—Typical Input

Fig. 5—Typical of All Outputs

Fig. 6—Typical Data Output

### **OUTLINE DRAWINGS** (Dimensions in Inches)

NOTE: The recommended chip carrier socket is Yamaichi #IC 51-0444-400 or equivalent.

#### **ORDERING INFORMATION:**

| DEVICE   | COMCODE   |  |  |  |  |

|----------|-----------|--|--|--|--|

| LC1092AP | 104401492 |  |  |  |  |

| LC1092BP | 104401518 |  |  |  |  |

For additional information contact your AT&T Account Manager, or call:

☐ AT&T Technologies, 555 Union Boulevard, Dept. 50AL203140, Allentown, PA 18103 1-800-372-2447

Printed in United States of America

008199 🗸 – 🛴

DS86-360LBC-RD

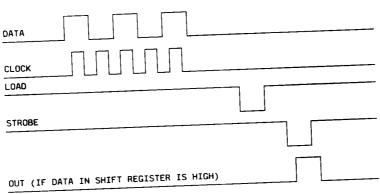

TYPICAL OPERATING SEQUENCE A typical operation sequence (Figure 7) is to clock data into the serial shift register at a clock rate of ≤10 mHz. This data is then transferred in parallel to the 32-bit latch. The information in the latch is transferred to the high-voltage output buffers by means of the STROBE which operates at a rate of ≤16 kHz. A data high input will yield a high-voltage high on the corresponding output, during the time that STROBE is low.

Fig. 7—Typical Operating Sequence Diagram

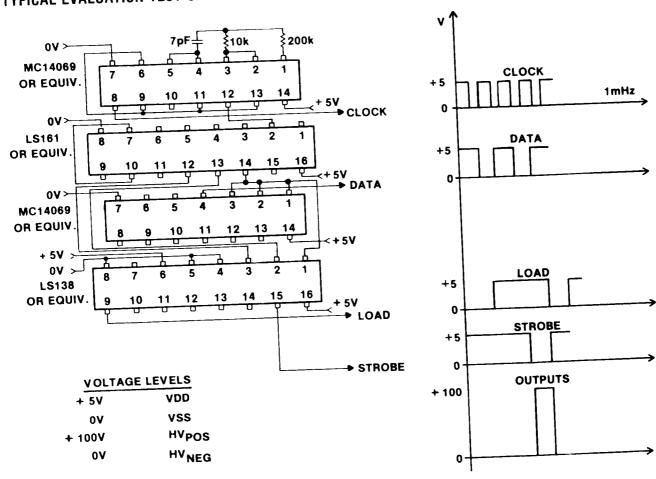

# TYPICAL EVALUATION TEST CIRCUIT (With Unloaded Outputs)

Fig. 8—LC1092A/B Typical Evaluation Test Circuit

### TYPICAL AND RECOMMENDED OPERATING CHARACTERISTICS

(At 25°C unless otherwise specified)

| CHARACTERISTICS                                                                                                                                                                             | MIN.                 | TYP.             | MAX.                     | UNIT                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------------|--------------------------|------------------------------|

| Supply Voltage (HV <sub>POS</sub> )<br>Supply Voltage (HV <sub>NEG</sub> )                                                                                                                  | VDD<br>Gnd           | —<br>Gnd         | 100<br>Gnd               | V                            |

| Logic Supply Voltage (VDD)                                                                                                                                                                  | 4.75                 | 5.00             | 5.25                     | V                            |

| Logic Common Voltage (VSS)                                                                                                                                                                  | Gnd                  | Gnd              | Gnd                      | V                            |

| High-Level Input Voltage                                                                                                                                                                    | VDD-0.5              | 5.0              | VDD+0.5                  | ٧                            |

| Low-Level Input Voltage                                                                                                                                                                     | VSS                  | VSS              | V                        |                              |

| CLOCK Frequency                                                                                                                                                                             | _                    |                  | 10                       | MHz                          |

| CLOCK Pulse Width Duration (Low or High Logic)                                                                                                                                              | 30                   | _                | _                        | nsec                         |

| LOAD Pulse Width Duration                                                                                                                                                                   | 30                   | _                | _                        | nsec                         |

| STROBE Frequency Frequency; 75 pf load on output                                                                                                                                            | _                    | 16               | _                        | kHz                          |

| STROBE Duty Cycle; 75 pf load on output                                                                                                                                                     | _                    | 25               | _                        | %                            |

| Setup Time (See Figure 7) Data Inputs Before CLOCK Transition High Data Inputs After CLOCK Transition High Load Input After CLOCK Transition Low STROBE Input Low After LOAD Transition Low | 20<br>60<br>30<br>30 | _<br>_<br>_<br>_ | -<br>-<br>-              | nsec<br>nsec<br>nsec<br>nsec |

| OUTPUT Rise Time 10% to 90%;<br>0 V to +100 V; Load Capacitance = 35 pF                                                                                                                     | _                    | _                | 0.5                      | μsec                         |

| OUTPUT Fall Time 10% to 90%;<br>+100 V to 0 V; Load Capacitance = 35 pF                                                                                                                     | _                    | _                | 3.0                      | μsec                         |

| Pulsed Mode Supply Voltage (HV <sub>POS</sub> ): Voltage Frequency Supply Voltage (HV <sub>NEG</sub> ): Voltage Frequency                                                                   | VDD<br>—<br>—95<br>— | _<br>_<br>_<br>_ | + 100<br>16<br>Gnd<br>16 | V<br>kHz<br>V<br>kHz         |

#### **FUNCTIONAL TABLE**

Table 1.

| FUNCTION |      | INPUTS |          |        | SHIFT REGISTER |                 | DATA                             |                  |                 | LATCH           | ]                                | OUTP | UTS |        |

|----------|------|--------|----------|--------|----------------|-----------------|----------------------------------|------------------|-----------------|-----------------|----------------------------------|------|-----|--------|

| TONCTION | DATA | CLOCK  | LOAD     | STROBE | R1             | R2              | R3 R32                           | оит              | L1              | L2              | L3 L32                           | Х0   | X1  | X2 X31 |

| DATA IN  | н    | 1      | Н        | н      | Н              | R1 <sub>n</sub> | R2 <sub>n</sub> R31 <sub>n</sub> | R32 <sub>n</sub> | L1 <sub>n</sub> | L2 <sub>n</sub> | L3 <sub>n</sub> L32 <sub>n</sub> | L    | L   | LL     |

|          | L    | 1      | Н        | Н      | L              | R1 <sub>n</sub> | R2 <sub>n</sub> R31 <sub>n</sub> | R32 <sub>n</sub> | L1 <sub>n</sub> | L2 <sub>n</sub> | L3 <sub>n</sub> L32 <sub>n</sub> | L    | L   | L L    |

| LOAD     | Х    | L      | <b>↓</b> | Н      | R1             | R2              | R3 R32                           | R32              | R1              | R2              | R3 R32                           | L    | L   | L L    |

| STROBE   | Х    | L      | Н        | L      | R1             | R2              | R3 R32                           | R32              | L1              | L2              | L3 L32                           | L1   | L2  | L3 L32 |

H = High level.

L = Low level.

X = Don't care.

$<sup>\</sup>uparrow$  = Low-to-high level transition.

<sup>↓ =</sup> High-to-low level transition.

R1...R32 = Levels currently at internal outputs of shift register.

$R1_n \dots R32_n$  = Levels at shift-register internal outputs (R1...R32 respectively) before the most recent clock transition.

L1...L32 = Levels currently at internal outputs of Latch.

$L1_{n}...L32_{n}$  = Levels at Latch internal outputs (L1...L32 respectively) before the most recent Load transition.