### **General Description**

The MAX910/MAX911 are the first high-speed comparators to include an 8-bit DAC with voltage reference to set the input threshold voltage. The MAX910 has a TTL compatible output while the MAX911 output is fully differential and ECL compatible. Comparator propagation delay is 8ns for the MAX910 and only 4ns for the MAX911. For high-speed comparator applications where the threshold must be updated rapidly, such as automatic test equipment (ATE) or process control applications, the MAX910/MAX911 provide a complete, single IC solution which significantly reduces stray capacitance, board space, design time and cost over multi-chip, discrete solutions.

The comparator threshold level, set by the DAC, has 10mV or 20mV pin-selectable resolution (a full-scale range of either 2.56V or 5.12V) when used with the internal reference. An external reference input is also provided.

The MAX910/MAX911 feature separate power and comparator ground pins to eliminate coupling between the comparator output and analog input. Both parts can be powered from either ±5V, or +5V and -5.2V supplies.

### **Applications**

Analog-to-Digital Converters

Voltage-to-Frequency Converters

Threshold Detectors

Window Discriminators

Sampling

**Automatic Test Equipment**

### **Features**

- 8ns Propagation Delay, TTL-Compatible Output (MAX910)

- ♦ 4ns Propagation Delay, ECL-Compatible Output (MAX911)

- **♦ 200mW Power Dissipation**

- ♦ 8-Bit Digitally Programmable Threshold Level

- ♦ Internal +2.56V Voltage Reference

- ♦ 2.56V or 5.12V Full-Scale Range

- ♦ Separate Analog and Digital Supplies

- **♦** Comparator Output Latch Function

### **Ordering Information**

| PART      | TEMP. RANGE  | PIN-PACKAGE           |

|-----------|--------------|-----------------------|

| MAX910ÇAG | 0°C to +70°C | 24 SSOP**             |

| MAX910CNG | 0°C to +70°C | 24 Narrow Plastic DIP |

| MAX910CWG | 0°C to +70°C | 24 Wide SO            |

| MAX910C/D | 0°C to +70°C | Dice*                 |

<sup>\*</sup> Dice are specified at  $T_A = +25^{\circ}C$ , DC parameters only.

## **Typical Operating Circuit**

#### DATA +5V +5V BUS 19 500k Voo Vcc TH CTRL 10k D7-D0 MAXIM 500k MAX910 VEE **REFOUT** -5V RA 11 RB 12 REFIN TH OUT 13 CMP OUT 17 CMP IN 14 GND **GND** GND THRESHOLD OUTPUT 15 RANGE = -2.54V TO +2.56V: 20 PROGRAMMABLE LEVEL DETECTOR

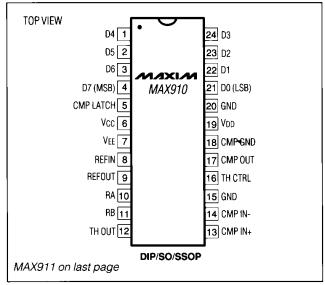

## Pin Configurations

/VI/IXI/VI

Maxim Integrated Products

<sup>\*\*</sup> Contact factory for pricing and availability.

## **ABSOLUTE MAXIMUM RATINGS (Note 1)**

| •                                               | -        |

|-------------------------------------------------|----------|

| Analog Supply Voltage (VCC to VEE)              | +12V     |

| Digital Supply Voltage (VDD to GND)             | +6V      |

| VEE to GND                                      |          |

| CMP GND to GND                                  |          |

| CMP IN+ to CMP IN[VEE - 0.2V] to [VCC           | + 0.2V]  |

| TH CTRL[VEE - 0.2V] to [VCC                     | + 0.2V]  |

| D0-D70.2V to [V <sub>DD</sub>                   | + 0.2V]  |

| REFIN[VEE - 0.2V] to [VCC                       | + 0.2V]  |

| CMP OUT Short-Circuit Duration (MAX910 only)    |          |

| to GNDIn                                        | definite |

| to VCC1                                         | minute   |

| Q and Q Continuous Output Current (MAX911 only) | 50mA     |

| REFOUT Short-Circuit Duration                   |          |

| to GND1                                         | minute   |

| to VCCIn                                        | definite |

|                                                 |          |

| TH OUT Short-Circuit Duration                         |                |

|-------------------------------------------------------|----------------|

| to VEE                                                | 1 minute       |

| to Vcc or GND                                         | Indefinite     |

| REFIN Short-Circuit Duration                          |                |

| to VEE                                                | 1 minute       |

| to VCC or GND                                         |                |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) |                |

| Plastic DIP (derate 8.70mW/°C above +70°C             | C)696mW        |

| SO (derate 11.76mW/°C above +70°C)                    | 941mW          |

| SSOP (derate 8.00mW/°C above +70°C)                   |                |

| Operating Temperature Ranges:                         |                |

| MAX91_C                                               | 0°C to +70°C   |

| Junction Temperature (Tj)                             | 65°C to +160°C |

| Storage Temperature Range                             | 65°C to +150°C |

| Lead Temperature (soldering, 10sec)                   |                |

Note 1: Absolute maximum ratings apply to both packaged parts and dice, unless otherwise noted.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +5V, V_{EE} = -5V, V_{DD} = +5V, T_{A} = +25^{\circ}C, unless otherwise noted.)$

| PARAMETER                          | SYMBOL           | COND                                   | ITIONS                                                        | MIN   | TYP | MAX   | UNITS |

|------------------------------------|------------------|----------------------------------------|---------------------------------------------------------------|-------|-----|-------|-------|

| COMPARATOR                         |                  |                                        |                                                               | I     |     |       |       |

| Input Offset Voltage               | Vos              | V <sub>CM</sub> = 0V (Note 2)          |                                                               |       | 1.0 | 3.0   | mV    |

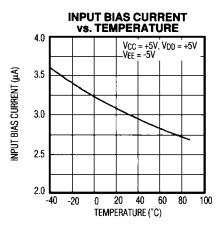

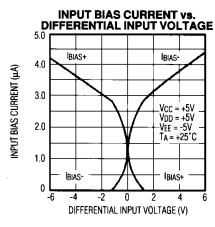

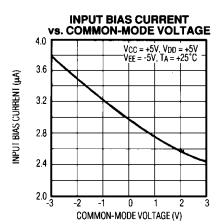

| Input Bias Current                 | IB               | I <sub>IN</sub> + or I <sub>IN</sub> - |                                                               |       | 3   | 6     | μΑ    |

| Input Offset Current               | los              | V <sub>CM</sub> = 0V                   |                                                               |       | 100 | 400   | nA    |

| Wideband Input Voltage Noise       | en               |                                        |                                                               |       | 300 |       | μ٧    |

| Input Common-Mode<br>Voltage Range | Vсм              | (Note 3)                               |                                                               | -3    |     | 3     | V     |

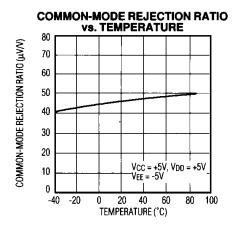

| Common-Mode<br>Rejection Ratio     | CMRR             | -3V < V <sub>CM</sub> < 3V             |                                                               |       | 50  | 150   | μ٧/٧  |

| Power-Supply<br>Rejection Ratio    | PSRR             | (Note 4)                               |                                                               |       | 100 | 250   | μ\/\  |

| Output High Voltage                | Voh              | MAX910                                 | V <sub>IN</sub> > 250mV,<br>I <sub>SOURCE</sub> = 1mA         | 2.4   | 3.5 |       | V     |

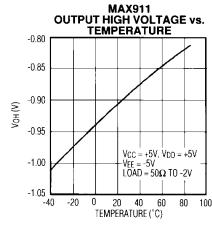

| Output High voitage                | VOH              | MAX911                                 | $V_{IN} > 250 \text{mV},$<br>$R_L = 50 \Omega \text{ to -2V}$ | -0.96 |     | -0.81 | '     |

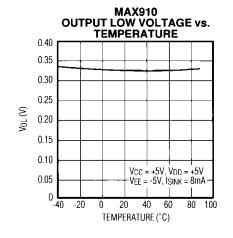

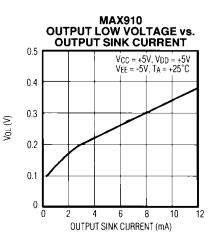

| Output Low Valtage                 | Va.              | MAX910                                 | V <sub>IN</sub> > 250mV,<br> SINK = 8mA                       |       | 0.3 | 0.4   | V     |

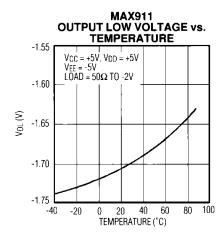

| Output Low Voltage                 | V <sub>OL</sub>  | MAX911                                 | $V_{IN} > 250$ mV,<br>$R_L = 50\Omega$ to -2V                 | -1.85 |     | -1.65 |       |

| CMP LATCH Input<br>Voltage High    | V <sub>L</sub> H |                                        |                                                               |       | 1.4 | 2.0   | V     |

| CMP LATCH Input<br>Voltage Low     | VLL              |                                        |                                                               | 0.8   | 1.4 |       | V     |

| CMP LATCH Input<br>Current High    | П                | V <sub>LH</sub> = 3.0V                 |                                                               |       | 1   | 20    | μА    |

| CMP LATCH Input<br>Current Low     | ILL              | V <sub>LL</sub> = 0.3V                 |                                                               |       | 1   | 20    | μА    |

## **ELECTRICAL CHARACTERISTICS (continued)**

(VCC = +5V, VEE = -5V, VDD = +5V, TA = +25°C, unless otherwise noted.)

| PARAMETER                               | SYMBOL                            | CONDITIONS                               | MIN  | TYP                  | MAX  | UNITS |

|-----------------------------------------|-----------------------------------|------------------------------------------|------|----------------------|------|-------|

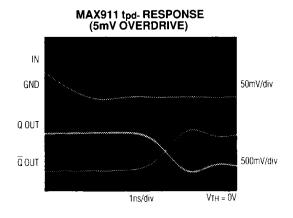

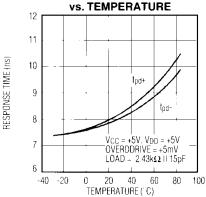

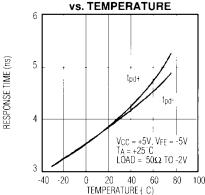

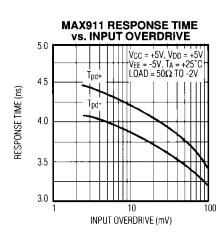

| Input to Output                         | t                                 | MAX910 (Notes 5, 6)                      |      | 8                    | 10   | ns    |

| High Response Time                      | t <sub>pd</sub> +                 | MAX911 (Notes 6, 7)                      |      | 4                    | 6    | 1115  |

| Input to Output_                        | tode                              | MAX910 (Notes 5, 6)                      |      | 8                    | 10   | ns    |

| Low Response Time                       | t <sub>pd</sub> -                 | MAX911 (Notes 6, 7)                      |      | 4                    | 6    | 115   |

| _atch_Disable to Output                 | t <sub>pd+(D)</sub>               | MAX910                                   |      | 5                    |      | ns    |

| High Delay                              | *pa+(D)                           | MAX911                                   |      | 1                    |      | 110   |

| Latch Disable to Output                 | t <sub>pd-(D)</sub>               | MAX910                                   |      | 5                    |      | ns    |

| Low Delay                               | 'pa-(D)                           | MAX911                                   |      | 1                    |      | 113   |

| Latch Setup Time                        | t <sub>S</sub>                    | MAX910                                   |      | 2.0                  |      | ns    |

| Later Setup Time                        | is                                | MAX911                                   |      | 0.5                  |      | 113   |

| Latch Hold Time                         | th                                | MAX910                                   |      | 1.0                  |      | ns    |

| Later Flora Fillie                      | 41                                | MAX911                                   |      | 0.5                  |      | 115   |

| Latch-Disable                           | t <sub>pw(D)</sub>                | MAX910                                   |      | 5                    |      | ns    |

| Pulse Width                             | 'pw(D)                            | MAX911                                   |      | 1                    |      | 113   |

| VOLTAGE REFERENCE                       |                                   |                                          |      |                      |      |       |

| Reference Voltage Output                | VREF                              | (Note 8)                                 | 2.55 | 2.56                 | 2.57 |       |

| D0-D7                                   |                                   |                                          |      |                      |      | _     |

| TTL Input Voltage High                  | VIH                               |                                          |      | 1.4                  | 2.0  | V     |

| TTL Input Voltage Low                   | VIL                               |                                          | 0.8  | 1.4                  |      | V     |

| TTL Input Current High                  | lін                               | V <sub>IH</sub> = 3.0V                   |      | 1                    | 20   | μА    |

| TTL Input Current Low                   | կլ                                | V <sub>IL</sub> = 0.3V                   |      | 1                    | 20   | μА    |

| THRESHOLD VOLTAGE OUTPU                 | ΙΤ                                |                                          |      |                      |      |       |

| Threshold Voltage Range                 | VTH                               | REFIN = 2.56V,<br>TH OUT connected to RB |      | +2.56<br>to<br>-2.54 |      | V     |

| Throughout voltage Hange                | • 111                             | REFIN = 2.56V,<br>TH OUT connected to RA |      | +2.56<br>to<br>+0.01 |      | ·     |

| Threshold Resolution                    | V <sub>TH(R)</sub>                | TH OUT connected to RB                   |      | 20                   |      | mV    |

| Throughout toolidiion                   | * I (N)                           | TH OUT connected to RA 10                |      |                      | 1117 |       |

| Upper Threshold Limit<br>Absolute Error | V <sub>TH+(E)</sub>               | (Note 9)                                 |      | ±1                   | ±3   | mV    |

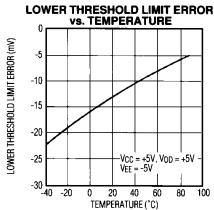

| Lower Threshold Limit<br>Absolute Error | V <sub>TH-(E)</sub>               | (Notes 10, 11)                           |      | ±10                  | ±30  | mV    |

| Wideband Threshold Voltage<br>Noise     | V <sub>TH</sub> (e <sub>n</sub> ) |                                          |      | 800                  |      | μ٧    |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(VCC = +5V, VEE = -5V, VDD = +5V, TA = +25^{\circ}C, unless otherwise noted.)$

| PARAMETER                                   | SYMBOL                            | CONDITIONS                          | MIN | TYP | MAX  | UNITS |

|---------------------------------------------|-----------------------------------|-------------------------------------|-----|-----|------|-------|

| Threshold Voltage Differential Nonlinearity | V <sub>TH(DNL)</sub>              | (Notes 10, 12)                      |     |     | ±10  | mV    |

| Threshold Trim Range                        | V <sub>TH(TR)</sub>               | (Note 13)                           |     |     | ±100 | mV    |

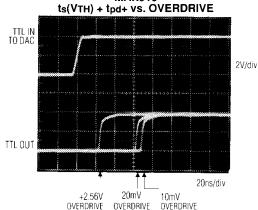

| Threshold Settling Time                     | t <sub>s</sub> (V <sub>TH</sub> ) | To 1/2LSB (Note 14)                 |     | 50  | 75   | ns    |

| POWER REQUIREMENTS                          |                                   | -                                   |     |     |      |       |

| Positive Analog Supply Current              | lcc                               | (Note 4)                            |     | 22  | 30   | mA    |

| Negative Analog Supply Current              | IEE                               | (Note 4)                            |     | 16  | 25   | mA    |

| Digital Supply Current                      | IDD                               | MAX910 only; V <sub>DD</sub> = 5.5V |     | 2   | 5    | mA    |

| Power Dissipation                           | PD                                |                                     |     | 200 | 320  | mW    |

### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +5V, V_{EE} = -5V, V_{DD} = +5V, T_A = 0^{\circ}C$  to  $70^{\circ}C$ , unless otherwise noted.)

| PARAMETER                          | SYMBOL          | COND                                                                   | ITIONS                                         | MIN    | TYP | MAX    | UNITS |

|------------------------------------|-----------------|------------------------------------------------------------------------|------------------------------------------------|--------|-----|--------|-------|

| COMPARATOR                         | •               |                                                                        |                                                | I      |     |        | ı     |

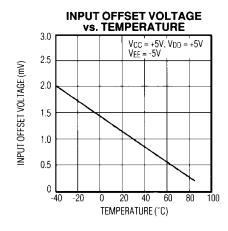

| Input Offset Voltage               | Vos             | V <sub>CM</sub> = 0V (Note 2)                                          |                                                |        | 2.0 | 5.0    | mV    |

| Input Bias Current                 | lΒ              | lin+ or lin-                                                           |                                                |        | 4   | 8      | μΑ    |

| Input Offset Current               | los             | Vcm = 0V                                                               |                                                |        | 150 | 600    | nA    |

| Input Common-Mode<br>Voltage Range | Vсм             | (Note 3)                                                               |                                                | -3     |     | 3      | ٧     |

| Common-Mode Rejection Ratio        | CMRR            | -3V < V <sub>CM</sub> < +3V                                            | -3V < V <sub>CM</sub> < +3V                    |        | 75  | 250    | μV/V  |

| Power-Supply Rejection Ratio       | PSRR            | (Note 4)                                                               |                                                |        | 150 | 400    | μV/V  |

| 111 00 18 1 1 1 1 1 1              |                 | MAX910, V <sub>IN</sub> > 250mV                                        | MAX910, V <sub>IN</sub> > 250mV, ISOURCE = 1mA |        | 3.5 |        |       |

| Output High Voltage                | Voh             | MAX911,                                                                | 0°C                                            | -1.010 |     | -0.850 | ٧     |

|                                    |                 | $V_{IN} > 250 \text{mV},$<br>$R_L = 50 \Omega \text{ to } -2 \text{V}$ | +70°C                                          | -0.900 |     | -0.720 |       |

|                                    |                 | MAX910, VIN > 250mV, ISINK = 8mA                                       |                                                |        | 0.3 | 0.4    |       |

| Output Low Voltage                 | V <sub>OL</sub> | MAX911,                                                                | 0°C                                            | -1.870 |     | -1.660 | V     |

|                                    |                 | $V_{IN} > 250 \text{mV},$<br>$R_L = 50\Omega \text{ to } -2V$          | +70°C                                          | -1.830 |     | -1.620 |       |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +5V, V_{EE} = -5V, V_{DD} = +5V, T_A = 0^{\circ}C$  to  $70^{\circ}C$ , unless otherwise noted.)

| PARAMETER                                      | SYMBOL           | CONDITIONS                         | MIN  | TYP  | MAX   | UNITS |

|------------------------------------------------|------------------|------------------------------------|------|------|-------|-------|

| CMP Latch Input Voltage High                   | V <sub>L</sub> H |                                    |      | 1.4  | 2.0   | V     |

| CMP Latch Input Voltage Low                    | V <sub>LL</sub>  |                                    | 0.8  | 1.4  |       | ٧     |

| CMP Latch Input Current High                   | ILH              | V <sub>LH</sub> = 3.0V             |      | 1    | 20    | μA    |

| CMP Latch Input Current Low                    | ILL              | $V_{LL} = 0.3V$                    |      | 1    | 20    | μA    |

| Input to Output                                | tpd+             | MAX910 (Notes 5, 6)                |      | 10   | 15    | ns    |

| High Response Time                             | ιρατ             | MAX911 (Notes 6, 7)                |      | 5    | 8     | 113   |

| Input to Output                                | tnd              | MAX910 (Notes 5, 6)                |      | 10   | 15    | ns    |

| Low Response Time                              | tpd-             | MAX911 (Notes 6, 7)                |      | 5    | 8     | 115   |

| VOLTAGE REFERENCE                              |                  |                                    |      |      |       |       |

| Reference Voltage Output                       | VREF (E)         | (Note 8)                           | 2.54 | 2.56 | 2.58  | ٧     |

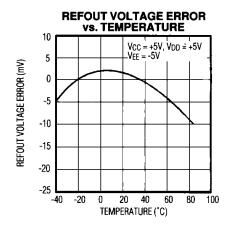

| Reference Voltage Tempco                       | TC VREF          |                                    |      | 0.2  |       | mV/°C |

| D0-D7                                          |                  |                                    |      |      |       |       |

| TTL Input Voltage High                         | ViH              |                                    |      | 1.4  | 2.0   | ٧     |

| TTL Input Voltage Low                          | VIL              |                                    | 0.8  | 1.4  | 41114 | V     |

| TTL Input Current High                         | lıн              | V <sub>IN</sub> = 3.0V             |      | 1    | 20    | μA    |

| TTL Input Current Low                          | Iլլ              | V <sub>IL</sub> = 0.3V             |      | 1    | 20    | μA    |

| THRESHOLD VOLTAGE OUTP                         | UT               | 194414                             |      |      |       |       |

| Upper Threshold Limit<br>Absolute Error        | VTH+(E)          | (Note 9)                           |      |      | ±5    | mV    |

| Lower Threshold Limit<br>Absolute Error        | VTH-(E)          | (Notes 10, 11)                     |      |      | ±30   | mV    |

| Threshold Limit                                | TO) (            | Positive threshold limit           |      | 0.2  |       |       |

| Tempco (Note 10)                               | TCVTH            | Negative threshold limit           |      | 0.2  |       | mV/°C |

| Threshold Voltage<br>Differential Nonlinearity | VTH(DNL)         | (Notes 10, 12)                     |      |      | ±15   | mV    |

| POWER REQUIREMENTS                             | •                |                                    | •    | •    |       |       |

| Positive Analog Supply Current                 | lcc              | (Note 4)                           |      | 22   | 30    | mA    |

| Negative Analog Supply Current                 | IEE              | (Note 4)                           |      | 16   | 25    | mA    |

| Digital Supply Current                         | IDD              | MAX910 only V <sub>DD</sub> = 5.5V |      | 2    | 5     | mA    |

| Power Dissipation                              | PD               |                                    |      | 200  | 320   | mW    |

- Note 2: Specifications are quoted with CMP OUT = +1.4V (TTL threshold) for the MAX910 and Q OUT,  $\overline{Q}$  OUT = -1.3V (ECL threshold) for the MAX911.

- Inferred from the CMRR test.

- Note 4: Tested for +4.75V ≤ V<sub>C</sub> ≤ +5.25V, and -5.5V ≤ V<sub>EE</sub> ≤ +4.75V with V<sub>DD</sub> = +5V.

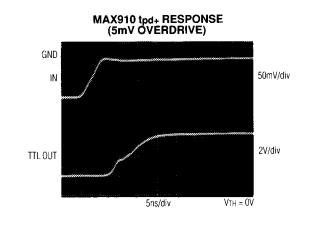

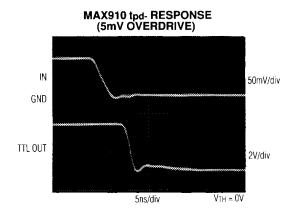

Note 5: Conditions for MAX910 switching specifications are 100mV step input with 5mV of overdrive, 15pF of output load capacitance, and 2mA external pull-up load current.

- Note 6: Parameter is guaranteed by design.

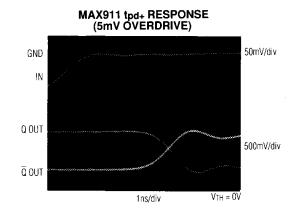

- Note 7: Conditions for MAX911 switching specifications are 100mV step input with 5mV of overdrive, and with both outputs terminated to -2V through  $50\Omega$  load resistors

Note 8: VREF specified while supplying internal DAC current (i.e. REFOUT tied to REFIN).

- **Note 9:** Specified with 2.56V applied to REFIN. Specification denotes maximum  $V_{TH+}$  deviation from 2.56V. **Note 10:** Specified in a 5.10V FS system (i.e. with TH OUT terminated through internal 640 $\Omega$  span resistor, 2.56V applied to REFIN, and with TH CTRL to GND)

- Note 11: V<sub>TH</sub>. limit quoted as a deviation from the nominal value of -2.54V with conditions specified in Note 10. Note 12: Tested for each major carry transition of the input digital code.

- Note 13: V<sub>TH(TR)</sub> specified for lower threshold voltage limit (i.e. with data-bits D0-D7 at logic low). A ±50mV change at TH CTRL

- causes a  $\pm 100$ mV change in V<sub>TH</sub> -. Note 14: Guaranteed by design. Specifications are taken from measurements made with a high-speed test fixture, C<sub>LOAD</sub> = 2pF on TH OUT for both MAX to MIN and MIN to MAX threshold voltage transition and settling to within 10mV (1/2LSB) of the final

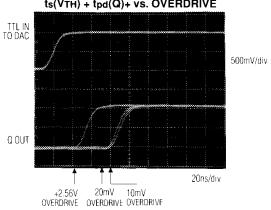

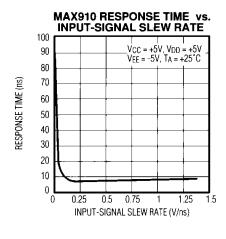

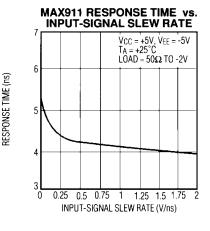

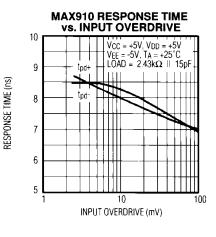

**Typical Operating Characteristics**

$(T_A = +25$ °C, unless otherwise noted.)

500mV/div

## High-Speed, Threshold-Programmable **Voltage Comparators**

ā out

## **Typical Operating Characteristics (continued)**

$(T_A = +25^{\circ}C, unless otherwise noted.)$

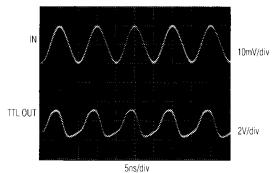

## **COMPARATOR RESPONSE** 10mV/div Q OUT 500mV/div

MAX911 100MHz

5ns/div

### **MAX910**

NOTE: CMP IN- CONNECTS TO GND AND TH OUT CONNECTS TO CMP IN+. THE DAC IS UPDATED, CAUSING TH OUT TO OVERDRIVE THE COMPARATOR INPUT

NOTE: CMP IN- CONNECTS TO GND AND TH OUT CONNECTS TO CMP IN+. THE DAC IS UPDATED, CAUSING TH OUT TO OVERDRIVE THE COMPARATOR INPUT

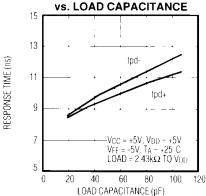

## **MAX910 RESPONSE TIME**

### **MAX910 RESPONSE TIME** vs. LOAD CAPACITANCE

## Typical Operating Characteristics (continued)

# MAX910/MAX911

# High-Speed, Threshold-Programmable Voltage Comparators

## Typical Operating Characteristics (continued)

### **Pin Description**

|               | ,            |                 | Pili Description                                                                                                                                                                                      |

|---------------|--------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX910        | MAX911       | NAME            | FUNCTION                                                                                                                                                                                              |

| 1-4,<br>21-24 | 1-4<br>21-24 | D4-D7,<br>D0-D3 | 8-Bit DAC TTL Logic Inputs                                                                                                                                                                            |

| 5             | 5            | CMP<br>LATCH    | Comparator Latch Input. A TTL logic low latches the comparator output. The comparator remains transparent to input changes when driven high or left floating.                                         |

| 6             | 6            | Vcc             | Analog Positive Supply. Connect to +5V analog supply.                                                                                                                                                 |

| 7             | 7            | VEE             | Analog Negative Supply.<br>Connect to -5V or -5.2V analog<br>supply.                                                                                                                                  |

| 8             | 8            | REFIN           | Reference Input. Connect to REFOUT or External Reference.                                                                                                                                             |

| 9             | Ø            | REFOUT          | +2.56V Reference Output.<br>Connect to REFIN for<br>V <sub>TH</sub> + = +2.56V.                                                                                                                       |

| 10            | 10           | RA              | $320\Omega$ Span Resistor. Connect to TH OUT for 2.55V threshold range and 10mV resolution.                                                                                                           |

| 11            | 11           | RB              | $640\Omega$ Span Resistor. Connect to TH OUT for 5.1V range with 20mV resolution.                                                                                                                     |

| 12            | 12           | TH OUT          | Threshold Output Voltage.<br>Connect to span resistors RA<br>or RB, and to either comparator<br>input.                                                                                                |

| 13            | 13           | CMP IN+         | Comparator Noninverting Input                                                                                                                                                                         |

| 14            | 14           | CMP IN-         | Comparator Inverting Input                                                                                                                                                                            |

| 15, 20        | 15, 20       | GND             | Analog power supply ground; separated from comparator's digital output ground (CMP GND).                                                                                                              |

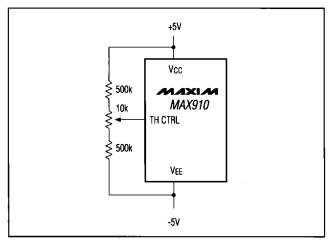

| 16            | 16           | TH<br>CTRL      | Reference Trim Input to the 8-bit DAC. Connect to the wiper of a 10kΩ trimming potentiometer between 500kΩ stop resistors for lower threshold output voltage (V <sub>TH</sub> -) trimming (Figure 1). |

| 17            |              | CMP<br>OUT      | TTL Comparator Output                                                                                                                                                                                 |

|               | 17           | Q OUT           | ECL Comparator Output                                                                                                                                                                                 |

| 18            | 18           | CMP<br>GND      | Comparator Ground. Connect to digital ground.                                                                                                                                                         |

| 19            |              | V <sub>DD</sub> | Positive Digital Supply.<br>Connect to +5V digital supply.                                                                                                                                            |

|               | 19           | Q OUT           | Complementary ECL<br>Comparator Output                                                                                                                                                                |

Figure 1. The lower limit of TH OUT is trimmed up to  $\pm 50$ mV, by connecting a  $10k\Omega$  trim pot between  $500k\Omega$  stop resistors across  $V_{CC}$  and  $V_{EE}$  with the trim pot wiper to TH CTRL.

### **Detailed Description**

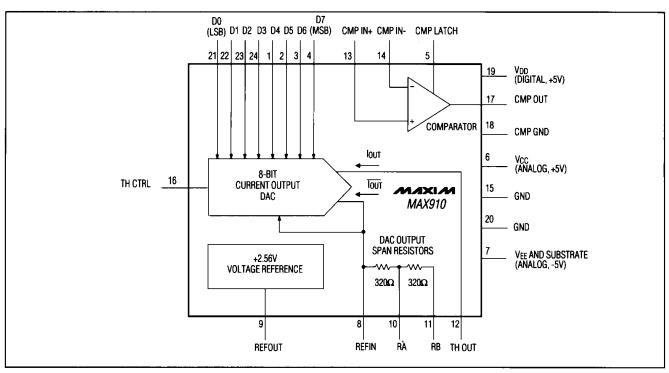

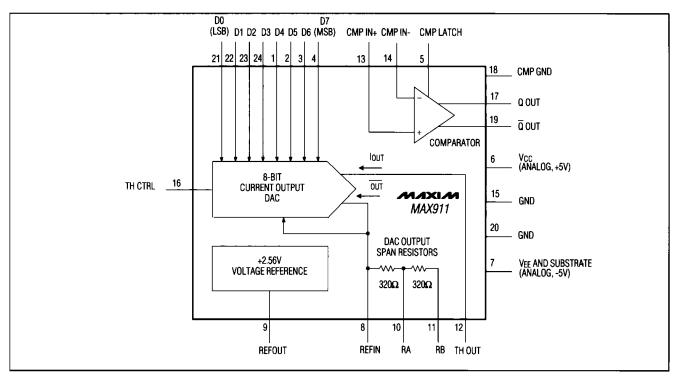

The MAX910 and MAX911 voltage comparators differ in logic compatibility. The MAX910 has a TTL compatible output, while the MAX911 output is fully differential and ECL compatible (Figures 2 and 3). Both comparators have an 8-bit, multiplying-current DAC, internal +2.56V reference, and two span resistors.

### The Comparator

The comparator input common-mode range is specified between ±3V to accommodate a wide range of threshold voltages, although either comparator input can be driven to the VCC or VEE power-supply rails without damage. A TTL compatible latch-enable function (CMP LATCH) is supplied on both the MAX910 and MAX911. The comparator is transparent to changes at the input terminals as long as CMP LATCH is driven high or left floating. As soon as CMP LATCH is taken low, the comparator output latches. The output remains latched until CMP LATCH is again driven high or allowed to float.

The MAX910 TTL comparator, with a propagation delay of 8ns and a fan-out of four, drives low-power Schottky TTL gates and 15pF of parasitic board capacitance without significant speed degradation. The MAX911 has 4ns propagation delay, and comparator output specifications that are directly compatible with the MECL 10k series. For best performance, terminate the differential ECL outputs of the MAX911 with  $50\Omega$  pull-down resistors to a -2V supply. Both the MAX910 and MAX911 respond to 100MHz signals.

Figure 2. MAX910 Functional Diagram

Figure 3. MAX911 Functional Diagram

### Threshold Out (TH OUT)

The complementary outputs of the internal 8-bit DAC sink a full-scale output current of 8mA, which translates to either a 2.56V or a 5.12V range, depending on which span resistor input (RA or RB) connects to TH OUT. The digital code divides the output current between the IOUT and IOUT DAC outputs (Figures 2 and 3). With the digital input code set to all 0s, TH OUT sinks the full-scale current (less 1LSB) from IOUT, and IOUT sinks no current. When the input code is set to all 1s, the reverse is true: REFIN sinks the full-scale output current from IOUT, and TH OUT sinks no current. Intermediate input codes divide the output current between the two DAC outputs accordingly.

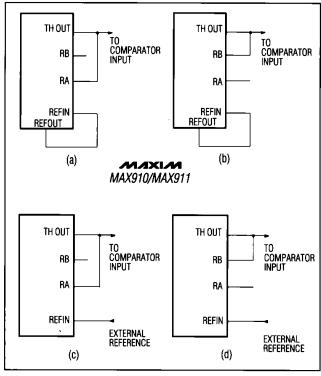

The DAC output current flowing through the DAC output span resistor RA or RB develops the voltage available on TH OUT. Span resistor choice determines the full-scale voltage range and resolution of TH OUT (Table 1). Note that the full-scale output current always flows into REFIN (Pin 8) regardless of the input code. This minimizes glitching on REFIN as the threshold voltage is updated.

Updating the TTL input digital code D0-D7 changes the voltage available on TH OUT.

REFIN must be terminated in a suitable voltage source. Accomplish this by connecting REFIN to REFOUT, or to an external voltage reference. The voltage termination determines the upper end of the threshold range (V<sub>TH+</sub>). Table 1 lists the range and resolution of TH OUT for different pin connections in Figure 4.

### Using an External Reference

For applications requiring higher precision, connect an external reference to REFIN. The voltage applied at REFIN sets VTH- and VTH+. VTH- and VTH+ must not exceed the comparator common-mode input range, and must source at least 10mA.

Choose the external reference and span resistors such that VTH- is at least 2V above VEE. VTH- is determined by REFIN, TH CTRL, and RSPAN (RA, RB):

Figure 4. Configuration for the TH OUT Voltage Ranges and Resolutions Listed in Table 1

$$V_{TH-} = V_{REFIN} - \left[ \left[ \frac{255}{256} \times \frac{R_{SPAN}}{320\Omega} \right] \times \left[ V_{REFIN} - V_{TH} C_{TRL} \right] \right]$$

Where RSPAN =  $320\Omega$  when TH OUT is connected to RA; =  $640\Omega$  when TH OUT is connected to RB.

For example, selecting RSPAN =  $320\Omega$  and delivering +3V to REFIN yields a 0V to +3V threshold range. TH OUT connects to either comparator input.

Table 1. TH OUT Voltage Range and Resolution

| CONNECT REFIN TO: | SPAN<br>RESISTOR (Ω) | VTH+(V) | V <sub>TH-(V)</sub>              | RESOLUTION                          | PIN<br>CONNECTION |

|-------------------|----------------------|---------|----------------------------------|-------------------------------------|-------------------|

| REFOUT (+2.56V)   | RA (320)             | +2.56   | 0.01                             | 1LSB = 10mV                         | Figure 4a         |

| REFOUT (+2.56V)   | RB (640)             | +2.56   | -2.54                            | 1LSB = 20mV                         | Figure 4b         |

| VEXTREF           | RA (320)             | VEXTREF | V <sub>EXTREF</sub> x (1/256)    | 1LSB = VEXTREF/256                  | Figure 4c         |

| VEXTREF           | RB (640)             | VEXTREF | -V <sub>EXTREF</sub> x (254/256) | 1LSB = 2 x V <sub>EXTREF</sub> /256 | Figure 4d         |

**Note:** VEXTREF = External Reference Voltage

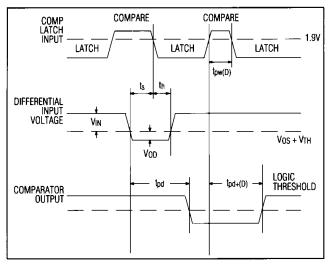

Figure 5. Comparator Timing Diagram

### **Definition of Terms**

- Vos Input Offset Voltage: That voltage which must be applied between the two comparator input terminals to obtain TTL logic threshold (+1.4V) at the comparator output for the MAX910, or ECL logic threshold (-1.3V) at the comparator output for the MAX911.

- Vin Input Voltage Pulse Amplitude; usually set to 100mV for comparator specifications.

- **Vop Input Voltage Overdrive;** usually set to 5mV and in opposite polarity to V<sub>IN</sub> for comparator specifications.

- tpd+ Input to Output High Delay: The propagation delay measured from the time the input signal crosses the input offset voltage to the logic threshold of an output low-to-high transition.

- **tpd- Input to Output Low Delay:** The propagation delay measured from the time the input signal crosses the input offset voltage to the logic threshold of an output high-to-low transition.

- tpd+(D) Latch Disable to Output High Delay: The propagation delay measured from the comparator latch signal crossing the TTL threshold in a low-to-high transition, to the point of the output crossing the logic threshold in a low-to-high transition.

- tpd-(D) Latch Disable to Output Low Delay: The propagation delay measured from the comparator latch signal crossing the TTL threshold in a low-to-high transition, to the point of the output crossing the logic threshold in a high-to-low transition.

- ts Setup Time: The time before the comparator latch signal's negative transition that an input must be present to be acquired and held at the output.

- th Hold Time: The time an input signal must remain unchanged after the negative transition of the comparator latch signal in order to be acquired and held at the output.

- **tpw(D)** Latch-Disable Pulse Width: The time the comparator latch signal must remain high in order to acquire and hold an input signal change.

- **ts(VTH) Threshold Settling Time:** The time required for the threshold voltage to be changed from V<sub>TH</sub>- to V<sub>TH+</sub> or from V<sub>TH+</sub> to V<sub>TH-</sub> and settle to within  $\pm 1/2$ LSB of V<sub>TH+</sub> or V<sub>TH-</sub>.

## Applications Information Board Layout

A printed circuit board with a good, low inductance ground plane is mandatory. Connect analog GND to the ground plane as close to the device as possible. The comparator ground (CMP GND) must be connected to the digital ground plane or bus. Connect the two grounds together at the power supply. Place all decoupling capacitors (small 100nF ceramic type are a good choice) as close as possible to the device power-supply pins. The power return side should be short and straight to the ground plane. Separate positive supplies for analog (VCC) and digital (VDD) are also recommended. Choose decoupling and terminating components with suitable bandwidths.

To avoid unwanted parasitic feedback, keep the comparator input and output trace and lead lengths short. Separate the digital lines driving D0-D7 as far from the analog lines as possible. Solder the device directly to the printed circuit board rather than using a socket to minimize stray capacitance.

Minimize parasitic capacitance between TH OUT, RA, RB, and CMP IN by keeping the connections short. Parasitic capacitance on this node degrades threshold voltage settling time.

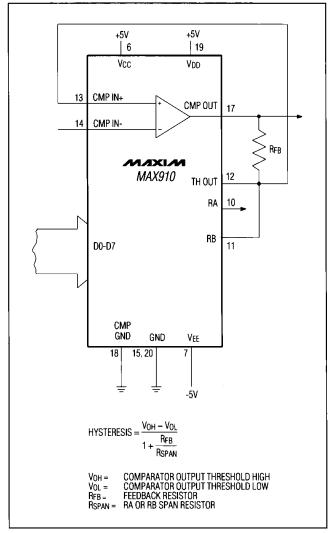

## Typical Application Circuits Adding Hysteresis to the MAX910

For applications requiring fast response to slow-moving inputs, add hysteresis by connecting a resistor from CMP OUT to TH OUT (Figure 6).

$$Hysteresis = \frac{V_{OH} - V_{OL}}{1 + \frac{R_{FB}}{R_{SPAN}}}$$

where VOH = Comparator Output Threshold High

Vol = Comparator Output Threshold Low

RFR = Feedback Resistor

RSPAN =  $320\Omega$  with TH OUT connected to RA

=  $640\Omega$  with TH OUT connected to RB

Figure 6. Adding Hysteresis to the MAX910

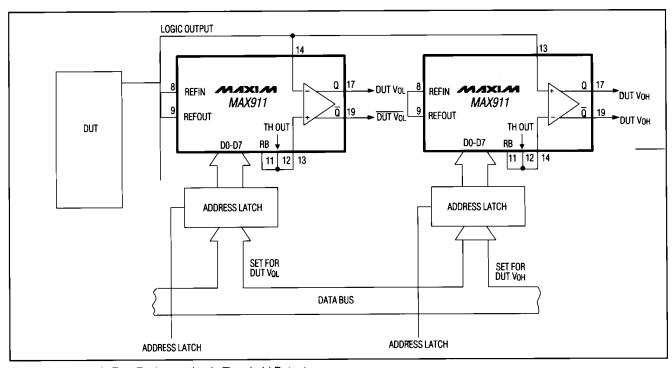

### **Window Comparator Circuit**

Two MAX911s detect the upper and lower threshold limits of a logic output from a device under test (DUT) in an automatic test equipment application (Figure 7). One device is programmed for the upper threshold limit while the other detects the lower limit. Either the MAX910 or MAX911 may be used in this application depending on the propagation delay and output compatibility requirements.

Figure 7. Automatic Test Equipment Logic Threshold Detector

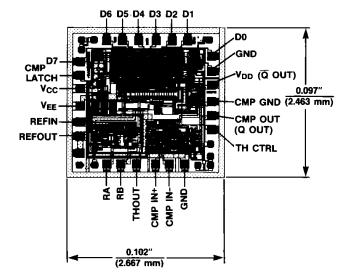

## Pin Configurations (continued)

### **TOP VIEW** 24 D3 D4 1 23 D2 D5 2 22 D1 D6 3 MAX911 21 D0 (LSB) D7 (MSB) 4 CMP LATCH 5 20 GND Vcc [ 19 Q OUT VEE 18 CMP GND REFIN [ 17 Q OUT REFOUT 9 16 TH CTRL 15 GND RA 10 RB 14 CMP IN-11 TH OUT 12 13 CMP IN+ DIP/SO/SSOP

### \_Chip Topography

() ARE FOR MAX911 ONLY. SUBSTRATE CONNECTED TO VEE.

### \_Ordering Information (continued)

| PART      | TEMP. RANGE  | PIN-PACKAGE           |

|-----------|--------------|-----------------------|

| MAX911CAG | 0°C to +70°C | 24 SSOP**             |

| MAX911CNG | 0°C to +70°C | 24 Narrow Plastic DIP |

| MAX911CWG | 0°C to +70°C | 24 Wide SO            |

| MAX911C/D | 0°C to +70°C | Dice*                 |

<sup>\*</sup> Dice are specified at T<sub>A</sub> = +25°C, DC parameters only.

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

<sup>\*\*</sup> Contact factory for pricing and availability.