# **AK5434D**

Dual channel 14bit 30MHz A/D Converter with differential input

#### **Features**

[Power Supply] 3.0V~3.45V Single-Supply

[Operation Temperature]  $-40^{\circ}\text{C} \sim +105^{\circ}\text{C}$

[Package] 30pinVSOP (Pin pitch 0.65mm)

Input range: 4V (Differential input @ Gain 0dB)

Input signal bandwidth: DC  $\sim$  400MHz (typ.) S/H Gain: 0dB/6dB/12dB ADC: 14bit, 30MHz S/(N+D): 69dB (typ.)

(30MHz operation, input signal frequency 14.9MHz@1ch)

Outputs: 14bit parallel data with straight binary

Power consumption: 172mW @typ. (power consumption @Power Down mode: under 1mW)

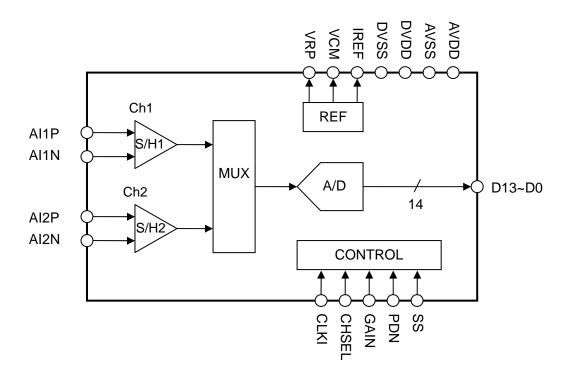

### **Circuit Block Diagram**

MS1515-E-00 -1- 2013/02

| Clock      | Function                                                  |  |

|------------|-----------------------------------------------------------|--|

| S/H1, S/H2 | ample/Hold AMP                                            |  |

| MUX        | witch that selects input signal to A/D from S/H1 and S/H2 |  |

| A/D        | 4bit 30MSPS A/D Converter                                 |  |

| REF        | Reference voltage generator                               |  |

| CONTROL    | Operation control circuit                                 |  |

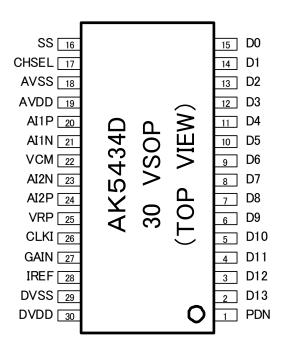

# **Pin Allocation**

# **Pin Description**

| No.   | Name  | I/O | @Power down | Description                                                                                                                                                                       |

|-------|-------|-----|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | PDN   | I   | _           | Power down (H: Normal Operation, L: Power down)                                                                                                                                   |

| 2     | D13   | О   | High-Z      | ADC output data MSB Straight binary code                                                                                                                                          |

| 3     | D12   | О   | High-Z      | ADC output data                                                                                                                                                                   |

| 4     | D11   | О   | High-Z      | ADC output data                                                                                                                                                                   |

| 5     | D10   | О   | High-Z      | ADC output data                                                                                                                                                                   |

| 6     | D9    | О   | High-Z      | ADC output data                                                                                                                                                                   |

| 7     | D8    | О   | High-Z      | ADC output data                                                                                                                                                                   |

| 8     | D7    | О   | High-Z      | ADC output data                                                                                                                                                                   |

| 9     | D6    | О   | High-Z      | ADC output data                                                                                                                                                                   |

| 10    | D5    | О   | High-Z      | ADC output data                                                                                                                                                                   |

| 11    | D4    | О   | High-Z      | ADC output data                                                                                                                                                                   |

| 12    | D3    | О   | High-Z      | ADC output data                                                                                                                                                                   |

| 13    | D2    | О   | High-Z      | ADC output data                                                                                                                                                                   |

| 14    | D1    | О   | High-Z      | ADC output data                                                                                                                                                                   |

| 15    | D0    | О   | High-Z      | ADC output data LSB                                                                                                                                                               |

| 16    | SS    | I   | _           | Sampling timing setting L: Sampling timing is determined by applying Logic to CHSEL-pin. H: The sampling timing is the timing of CHSEL=L. Ch1 and Ch2 are sampled simultaneously. |

| 17    | CHSEL | I   | _           | Ch1/Ch2 select (L:Ch1, H:Ch2)                                                                                                                                                     |

| 18    | AVSS  | PWR | _           | Analog Ground                                                                                                                                                                     |

| 19    | AVDD  | PWR | _           | Analog supply $(3.0V \sim 3.45V)$                                                                                                                                                 |

| 20    | AI1P  | I   | _           | Ch1 differential input P side                                                                                                                                                     |

| 21    | AI1N  | I   | _           | Ch1 differential input N side                                                                                                                                                     |

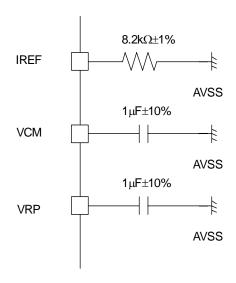

| 22    | VCM   | О   | High-Z      | Common-mode voltage output Connect 1µF between AVSS and this pin.                                                                                                                 |

| 23    | AI2N  | I   | _           | Ch2 differential input N side                                                                                                                                                     |

| 24    | AI2P  | I   | -           | Ch2 differential input P side                                                                                                                                                     |

| 25    | VRP   | О   | L           | ADC Reference-voltage output. Connect 1µF between AVSS and this pin.                                                                                                              |

| 26    | CLKI  | I   | -           | ADC clock input                                                                                                                                                                   |

| 27    | GAIN  | I   | _           | S/H gain setting (L:0dB, M:12dB, H:6dB)                                                                                                                                           |

| 28    | IREF  | О   | High-Z      | bias current output Connect $8.2k\Omega$ between AVSS and this pin.                                                                                                               |

| 29    | DVSS  | PWR | _           | Digital Ground                                                                                                                                                                    |

| 30    | DVDD  | PWR | _           | Digital Power Supply (3.0V~3.45V)                                                                                                                                                 |

| 0.10. | EIO   |     |             | IT DWD. DOWED/CDOLIND                                                                                                                                                             |

(NOTE)IO I: INPUT, O: OUTPUT, PWR: POWER/GROUND

### **Absolute Maximum Ratings**

AVSS, DVSS=0V,All voltages are with respect to ground

| Parameter                            | Symbol       | Min.         | Max.       | Unit   | Note                               |

|--------------------------------------|--------------|--------------|------------|--------|------------------------------------|

| Power Supplies Analog Digial         | AVDD<br>DVDD | -0.3<br>-0.3 | 4.0<br>4.0 | V<br>V |                                    |

| Input Current                        | IIN          | -10          | 10         | mA     | Except AVDD, AVSS, DVDD, DVSS pins |

| Analog Input Voltage Range (Note 1)  | VINA         | -0.3         | AVDD+0.3   | V      |                                    |

| Digital Input Voltage Range (Note 2) | VIND         | -0.3         | DVDD+0.3   | V      |                                    |

| Operating Temperature                | Ta           | -40          | 105        | °C     |                                    |

| Storage Temperature                  | Tstg         | -65          | 150        | °C     |                                    |

(Note 1) AI1P, AI1N, AI2P, AI2N, GAIN, CLKI

(Note 2) CHSEL, SS, PDN

All power supply ground pins (AVSS, DVSS) should be at the same potential.

WARNING: Operation at or beyond these limits may result in permanent damage to the device.

Normal Operating Specifications are not guaranteed at these extremes.

# **Operating Condition**

| Parameter          | Symbol | Min. | Typ. | Max. | Unit | Note |

|--------------------|--------|------|------|------|------|------|

| Supply Voltage     |        |      |      |      |      |      |

| Analog (Core)      | AVDD   | 3.0  | 3.3  | 3.45 | V    |      |

| Digital (Core, IO) | DVDD   | 3.0  | 3.3  | 3.45 | V    |      |

Power supply voltages are values where each ground pin (AVSS=DVSS) is at 0V (Voltage reference)

All power supply ground pins (AVSS, DVSS) should be at the same potential.

MS1515-E-00 -4- 2013/02

### **Electrical Characteristics**

#### ■ Analog Specifications

(AVDD=DVDD=3.3V, S/H gain=0dB, Ta=25°C, CLKI=30MHz, fin=14.9MHz, Signal Level=3.4Vpp-diff)

|                    |        | ii=0db, ia=25 c, cERi=50Wiiz, iii |      |           |           |          |

|--------------------|--------|-----------------------------------|------|-----------|-----------|----------|

| Parameter          | Symbol | Condition                         | min  | Тур       | Max       | Units    |

| DC Characteristics |        |                                   |      |           |           |          |

| Resolution         | RES    |                                   |      |           | 14        | Bits     |

| Integral           | INL    |                                   |      | $\pm 2.8$ | ±10.5     | LSB      |

| Non-Linearity      |        |                                   |      |           |           |          |

| Differential       | DNL    |                                   |      | $\pm 0.8$ | $\pm 4.0$ | LSB      |

| Non-Linearity      |        |                                   |      |           |           |          |

| Offset             | EOC    | AIxP=AIxN=VCM (x=1,2)             |      |           | ±100      | LSB      |

| Gain Error         | GERR   | Gain setting 0dB                  | -10  | 0         | +10       | %FS      |

| Gain               |        | Gain setting 6dB                  | 5.5  | 6         | 6.5       | dB       |

|                    |        | Gain setting 12dB                 | 11.5 | 12        | 12.5      | dB       |

| Input Range        | AINFS  | Gain setting 0dB                  | 3.6  | 4.0       | 4.4       | Vpp-diff |

| Common Voltage     | VCM    |                                   | 1.26 | 1.4       | 1.54      | V        |

| ADC Reference      | VRP    |                                   | 1.8  | 2.0       | 2.2       | V        |

| Voltage            |        |                                   |      |           |           |          |

| -                  | -      | AC Characteristics                |      |           | -         |          |

| S/N                | SNR    |                                   | 68   | 73        |           | dB       |

| S/(N+D)            | SND    |                                   | 64   | 69        |           | dB       |

| S/(N+D) (Note 1)   | SND2   | fin=1MHz                          | 66   | 71        |           | dB       |

| SFDR               | SFDR   |                                   |      | 70        |           | dB       |

| Total Harmonic     |        |                                   | 64   | 70        |           | dBc      |

| Distortion         |        |                                   |      |           |           |          |

| Input Resistance   | RIN    | (Note 4)                          |      | 60        |           | kΩ       |

| (Note 1)           |        |                                   |      |           |           |          |

| Input Capacitance  | CIN    |                                   |      | 5         | 8         | pF       |

| (Note 1)           |        |                                   |      |           |           | _        |

| Input Signal       | BW     | -3dB Level                        |      | 400       |           | MHz      |

| bandwidth (Note 1) |        |                                   |      |           |           |          |

| CMRR               | CMR    | fin=1MHz, common swing -26dB      | 50   | 56        |           | dB       |

| Crosstalk          | CTK    | fin=7.45MHz                       |      | -80       | -70       | dB       |

| Current            | ΙA     | Analog fin=1MHz                   |      | 46        | 68        | mA       |

| Consumption        | ID     | Digital(Note 2) fin=1MHz          |      | 6         | 9         | mA       |

| 1                  | IPD    |                                   |      |           | 0.3       | mA       |

| Current            | IAS    | Analog                            |      |           | 0.1       | mA       |

|                    | IDS    | Digital                           |      |           | 0.1       | mA       |

| power down         |        | (Note 3)                          |      |           |           |          |

| ш                  |        | /                                 | I    |           |           | L        |

<sup>(</sup>Note 1) Design Value

MS1515-E-00 -5- 2013/02

<sup>(</sup>Note 2) CL=10pF are connected to D0~D13 pins.

<sup>(</sup>Note 3) Power down PDN=Low, CLKI=Low fix, Current consumption without no input signal.

<sup>(</sup>Note 4) Equivalent resistance that from VCM operation middle point to differential input pins AI1P/N, AI2P/N. It is in inverse proportion to sampling frequency.

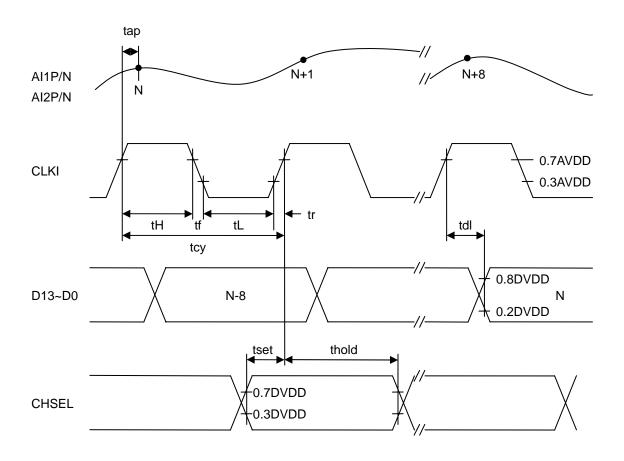

### Switching Characteristics

(AVDD=DVDD=3.0~3.45V, Ta=-40~105°C, CL=10pF)

| Parameter        | Symbol | Conditions | min. | typ. | max. | Unit |

|------------------|--------|------------|------|------|------|------|

| Conversion rate  | fs     |            | 15   |      | 30   | MHz  |

| Clock cycle      | tcy    |            | 33.3 |      | 66.7 | ns   |

| Clock rise time  | tr     | 0.3AVDD    |      | 2    | 15   | ns   |

| Note 1           |        | to 0.7AVDD |      |      |      |      |

| Clock fall time  | tf     | 0.7AVDD    |      | 2    | 15   | ns   |

| Note 1           |        | to 0.3AVDD |      |      |      |      |

| Clock High width | tH     |            | 15   |      |      | ns   |

| Clock Low width  | tL     |            | 15   |      |      | ns   |

| Clock duty       | tduty  |            | 40   | 50   | 60   | %    |

| Pipeline delay   | tpd    |            |      | 8    |      | CLKI |

| Note 2           |        |            |      |      |      |      |

| Aperture delay   | tap    |            |      | 2    | 4    | ns   |

| Note 2           |        |            |      |      |      |      |

| AD output delay  | tdl    |            | 0    | 6    | 20   | ns   |

| CHSEL setup      | tset   |            | 10   |      |      | ns   |

| CHSEL hold       | thold  |            | 10   |      |      | ns   |

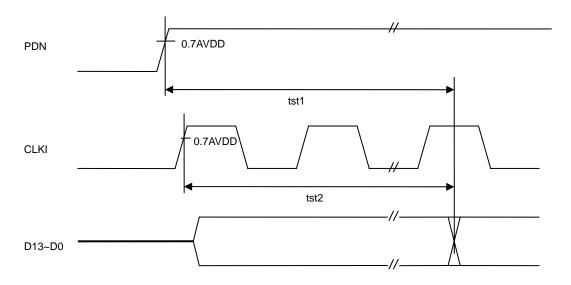

| Start up time 1  | tst1   |            |      | 2    | 5    | ms   |

| Start up time 2  | tst2   |            |      | 2    | 5    | ms   |

Note 1) Clock high width and Low width must be fulfilled.

Note 2) Design Value

# ■ Digital DC Characteristics

(AVDD=DVDD=3.0~3.6V, Ta=-40~105°C)

| Parameter                      | Symbol | Pin            | Min.     | Max.     | Unit | Remark |

|--------------------------------|--------|----------------|----------|----------|------|--------|

| High level input threshold 1   | VIH1   | Note 1         | 0.7×DVDD |          | V    |        |

| Low level input threshold 1    | VIL1   | Note 1         |          | 0.3×DVDD | V    |        |

| High level input threshold 2   | VIH2   | Note 2         | 0.7×AVDD |          | V    |        |

| Low level input threshold 2    | VIL2   | Note 2         |          | 0.3×AVDD | V    |        |

| High level input threshold 3   | VIH3   | GAIN           | 0.8×AVDD |          | V    |        |

| Middle level input threshold 3 | VIM3   | GAIN           | 0.3×AVDD | 0.7×AVDD | V    |        |

| Low level input threshold 3    | VIL3   | GAIN           |          | 0.2×AVDD | V    |        |

| High level output voltage      | VOH    | Note 3, Note 4 | 0.8×DVDD |          | V    |        |

| Low level output voltage       | VOL    | Note 3, Note 5 |          | 0.2×DVDD | V    |        |

| Input leakage current          | ILKG   | Note 1, Note2, |          | ±10      | μΑ   |        |

|                                |        | GAIN           |          |          | -    |        |

| High-Z leakage current         | IOZ    | Note 3         |          | ±10      | μΑ   |        |

Note 1) CHSEL, SS, PDN,

Note 2) CLKI

Note 3) D13~D0

Note 4) IOH = -1mA

Note 5) IOL = 1mA

MS1515-E-00 -7- 2013/02

### **Functional Description**

Power down function

Power Down mode can be activated by applying a logic Level "0" to the PDN-pin. All the data output pins [D13: D0] become Low state.at Power Down mode.

| PDN | Condition       |

|-----|-----------------|

| L   | Power down      |

| Н   | Normal opration |

S/H AMP gain select

The gain of the S/H amplifier can be selected by the input level of GAIN-pin.

| GAIN | Gain | Input full scale |

|------|------|------------------|

| AVSS | 0dB  | 4Vpp-diff        |

| AVDD | 6dB  | 2Vpp-diff        |

| VCM  | 12dB | 1Vpp-diff        |

Sampling timing setting

The sampling timing of two channels can be set with SS-pin.

| SS | Sampling timing                                                 |  |  |  |

|----|-----------------------------------------------------------------|--|--|--|

| L  | S/H1 or S/H2 samples the signal according to CHSEL.             |  |  |  |

| Н  | H At CHSEL=L, S/H1 and S/H2 sample the signal at the same time. |  |  |  |

Sampling channel select

The samples timing can be selected with CHSEL-pin.

Separate sampling (@SS=Low)

| CHSEL | Sampling channel |

|-------|------------------|

| L     | S/H1             |

| Н     | S/H2             |

Simultaneous sampling (@SS=High)

| CHSEL | Sampling channel |

|-------|------------------|

| L     | S/H1 & S/H2      |

| Н     | Not sampled      |

Only at CHSEL=Low, sampling is done at the same timing (SS=High).

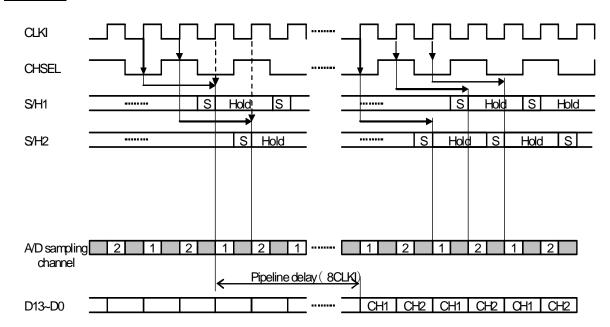

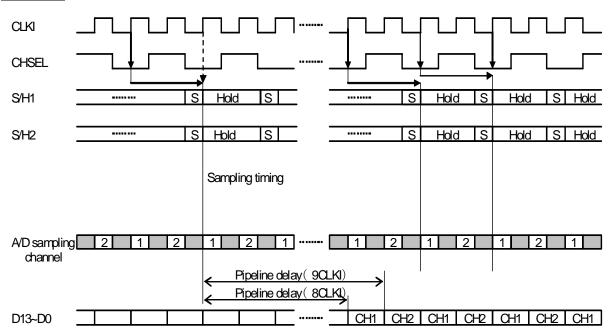

#### ■ Operation timing

#### At SS="L"

#### At SS="H"

MS1515-E-00 -9- 2013/02

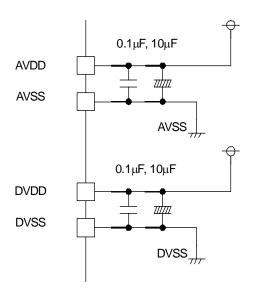

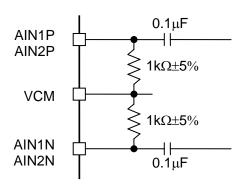

# **External Circuit Examples**

Note) Resisters must be metal-film type.

MS1515-E-00 -10- 2013/02

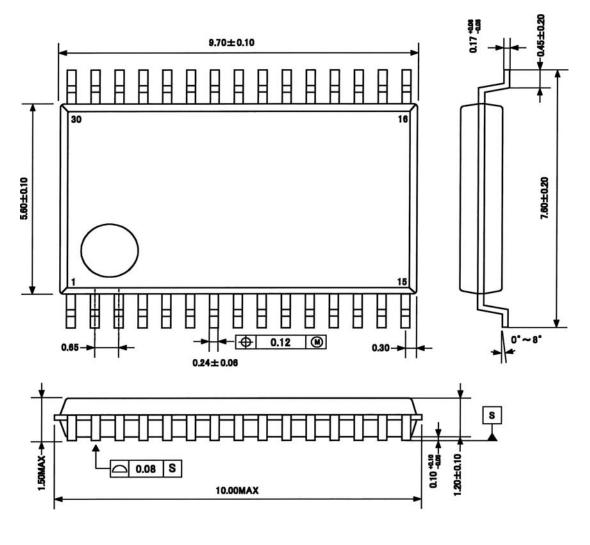

# **Packages**

30-VSOP-0.65

MS1515-E-00 -11- 2013/02

# Marking

Marketing Code: AK5434D

Date Code: XXXXXXX

#### IMPORTANT NOTICE

- These products and their specifications are subject to change without notice. When you consider any use or application of these products, please make inquiries the sales office of Asahi Kasei Microdevices Corporation (AKM) or authorized distributors as to current status of the products.

- Descriptions of external circuits, application circuits, software and other related information contained in this document are provided only to illustrate the operation and application examples of the semiconductor products. You are fully responsible for the incorporation of these external circuits, application circuits, software and other related information in the design of your equipments. AKM assumes no responsibility for any losses incurred by you or third parties arising from the use of these information herein. AKM assumes no liability for infringement of any patent, intellectual property, or other rights in the application or use of such information contained herein.

- Any export of these products, or devices or systems containing them, may require an export license or other official approval under the law and regulations of the country of export pertaining to customs and tariffs, currency exchange, or strategic materials.

- AKM products are neither intended nor authorized for use as critical components<sub>Note1)</sub> in any safety, life support, or other hazard related device or system<sub>Note2)</sub>, and AKM assumes no responsibility for such use, except for the use approved with the express written consent by Representative Director of AKM. As used here:

Note1) A critical component is one whose failure to function or perform may reasonably be expected to result, whether directly or indirectly, in the loss of the safety or effectiveness of the device or system containing it, and which must therefore meet very high standards of performance and reliability.

- Note2) A hazard related device or system is one designed or intended for life support or maintenance of safety or for applications in medicine, aerospace, nuclear energy, or other fields, in which its failure to function or perform may reasonably be expected to result in loss of life or in significant injury or damage to person or property.

- It is the responsibility of the buyer or distributor of AKM products, who distributes, disposes of, or otherwise places the product with a third party, to notify such third party in advance of the above content and conditions, and the buyer or distributor agrees to assume any and all responsibility and liability for and hold AKM harmless from any and all claims arising from the use of said product in the absence of such notification.

MS1515-E-00 -13- 2013/02