## QUAD FORWARD-CONDUCTING BUFFERED P-GATE THYRISTORS

## TISP6NTP2A Programmable Protector

Independent Overvoltage Protection for Two SLICs in Short **Loop Applications:**

- Wide 0 to -90 V Programming Range

- Low 5 mA max. Gate Triggering Current

- High 150 mA min. (85 °C) Holding Current

- Specified 1.2/50 & 0.5/700 Limiting Voltage

- Full -40 °C to 85 °C Temperature Range

### **Rated for Common Impulse Waveforms**

| Voltage Impulse<br>Form | Current Impulse<br>Shape | I <sub>TSP</sub><br>A |  |

|-------------------------|--------------------------|-----------------------|--|

| 10/1000 μs              | 10/1000 μs               | 20                    |  |

| 10/700 μs               | 5/310 μs                 | 25                    |  |

| 1.2/50 µs               | 8/20 μs                  | 75                    |  |

| 2/10 μs                 | 2/10 μs                  | 85                    |  |

SUL Recognized Component

### Description

The TISP6NTP2A has been designed for short loop systems such as:

- WILL (Wireless In the Local Loop)

- FITL (Fibre In The Loop)

- DAML (Digital Added Main Line, Pair Gain)

- SOHO (Small Office Home Office)

- ISDN-TA (Integrated Services Digital Network -Terminal Adaptors)

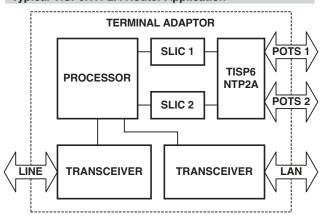

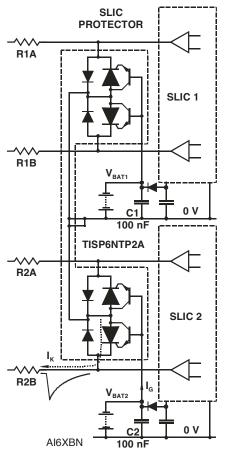

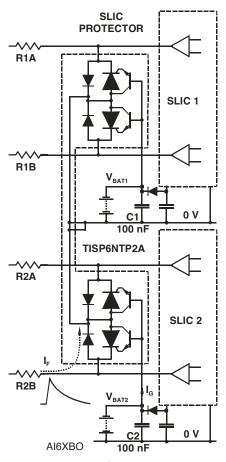

## Typical TISP6NTP2A Router Application

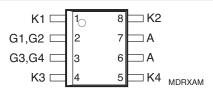

## D Package (Top View)

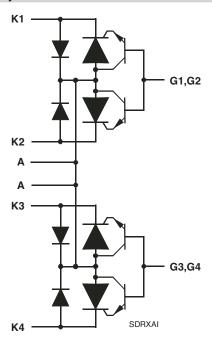

## **Device Symbol**

## **How To Order**

| Device     | Device Package   |               | Order As       |  |  |

|------------|------------------|---------------|----------------|--|--|

| TISP6NTP2A | D, Small-Outline | Tape and Reel | TISP6NTP2ADR-S |  |  |

JUNE 1998 - REVISED JULY 2008

#### **Description (continued)**

These systems often have the need to source two POTS (Plain Old Telephone Service) lines, one for a telephone and the other for a facsimile machine. In a single surface mount package, the TISP6NTP2A protects the two POTS line SLICs (Subscriber Line Interface Circuits) against overvoltages caused by lightning, a.c. power contact and induction.

The TISP6NTP2A has an array of four buffered P-gate forward conducting thyristors with twin commoned gates and a common anode connection. Each thyristor cathode has a separate terminal connection. An antiparallel anode-cathode diode is connected across each thyristor. The buffer transistors reduce the gate supply current.

In use, the cathodes of an TISP6NTP2A thyristor are connected to the four conductors of two POTS lines (see applications information). Each gate is connected to the appropriate negative voltage battery feed of the SLIC driving that line pair. By having separate gates, each SLIC can be protected at a voltage level related to the negative supply voltage of that individual SLIC. The anode of the TISP6NTP2A is connected to the SLIC common.

Positive overvoltages are clipped to common by forward conduction of the TISP6NTP2A antiparallel diode. Negative overvoltages are initially clipped close to the SLIC negative supply by emitter follower action of the TISP6NTP2A buffer transistor. If sufficient clipping current flows, the TISP6NTP2A thyristor will regenerate and switch into a low voltage on-state condition. As the overvoltage subsides, the high holding current of the TISP6NTP2A helps prevent d.c. latchup.

## Absolute Maximum Ratings, TA = 25 °C (Unless Otherwise Noted)

| Rating                                                                                                                         | Symbol           | Value       | Unit |

|--------------------------------------------------------------------------------------------------------------------------------|------------------|-------------|------|

| Repetitive peak off-state voltage, $I_G = 0$ , $-40  ^{\circ}\text{C} \le T_J \le 85  ^{\circ}\text{C}$                        | $V_{DRM}$        | -100        | V    |

| Repetitive peak gate-cathode voltage, $V_{KA} = 0$ , $-40  ^{\circ}\text{C} \le T_{J} \le 85  ^{\circ}\text{C}$                | $V_{GKRM}$       | -90         | V    |

| Non-repetitive peak on-state pulse current, -40 $^{\circ}$ C $\leq$ T <sub>J</sub> $\leq$ 85 $^{\circ}$ C, (see Notes 1 and 2) |                  |             |      |

| 10/1000 μs (Bellcore GR-1089-CORE, Issue 1, November 1994, Section 4)                                                          |                  | 20          |      |

| 0.2/310 μs (I3124, open-circuit voltage wave shape 0.5/700 μs)                                                                 | l                | 25          | Α    |

| 5/310 μs (ITU-T K.20 & K.21, open-circuit voltage wave shape 10/700 μs)                                                        | ITSP             | 25          | _ ^  |

| 8/20 $\mu s$ (IEC 61000-4-5:1995, open-circuit voltage wave shape 1.2/50 $\mu s$ )                                             |                  | 75          |      |

| $2/10~\mu s$ (Bellcore GR-1089-CORE, Issue 1, November 1994, Section 4)                                                        |                  | 85          |      |

| Non-repetitive peak on-state current, 50/60 Hz, -40 °C ≤ T <sub>J</sub> ≤ 85 °C, (see Notes 1 and 2)                           |                  |             |      |

| 100 ms                                                                                                                         |                  | 7           |      |

| 1 s                                                                                                                            | I <sub>TSM</sub> | 2.7         | Α    |

| 5 s                                                                                                                            | . 121/1          | 1.5         | , ,  |

| 300 s                                                                                                                          |                  | 0.45        |      |

| 900 s                                                                                                                          |                  | 0.43        |      |

| Non-repetitive peak gate current, 1/2 μs pulse, cathodes commoned (see Note 1)                                                 | I <sub>GSM</sub> | 25          | Α    |

| Operating free-air temperature range                                                                                           | T <sub>A</sub>   | -40 to +85  | °C   |

| Junction temperature                                                                                                           | T <sub>J</sub>   | -40 to +150 | °C   |

| Storage temperature range                                                                                                      | T <sub>stg</sub> | -65 to +150 | °C   |

- NOTES: 1. Initially, the protector must be in thermal equilibrium with -40 °C  $\leq$  T<sub>J</sub>  $\leq$  85 °C. The surge may be repeated after the device returns to its initial conditions.

- 2. These non-repetitive rated currents are peak values for either polarity. The rated current values may be applied to any cathode-anode terminal pair. Additionally, all cathode-anode terminal pairs may have their rated current values applied simultaneously (in this case the anode terminal current will be four times the rated current value of an individual terminal pair). Above 85 °C, derate linearly to zero at 150 °C lead temperature.

## BOURNS®

## **Recommended Operating Conditions**

|                |                                                                   | Min. | Тур. | Max. | Unit |

|----------------|-------------------------------------------------------------------|------|------|------|------|

| C <sub>G</sub> | Gate decoupling capacitor                                         | 100  | 220  |      | nF   |

| R1, R2         | Series resistor for GR-1089-CORE first-level surge survival       | 40   |      |      |      |

|                | Series resistor for ITU-T recommendation K.20                     | 12   |      |      | Ω    |

|                | Series resistor for ITU-T recommendation K.21                     | 20   |      |      |      |

|                | Series resistor for IEC 61000-4-5:1995, class 5, 1.2/50 or 10/700 | 4    |      |      |      |

## Electrical Characteristics for any Section, $T_A$ = 25 $^{\circ}$ C (Unless Otherwise Noted)

| Parameter         |                                         | Test Conditions                                                              |                        | Min. | Тур. | Max. | Unit |

|-------------------|-----------------------------------------|------------------------------------------------------------------------------|------------------------|------|------|------|------|

| I <sub>D</sub>    | Off-state current                       | $V_D = V_{DRM}$ , $I_G = 0$                                                  | T <sub>J</sub> = 25 °C |      |      | -5   | μΑ   |

| טי ן              | On-state current                        | VD - VDRM, IG - V                                                            | T <sub>J</sub> = 85 °C |      |      | -50  | μΑ   |

|                   |                                         | $I_T = -20 \text{ A}$ , IEC 61000-4-5:1995 combination imp                   | ulse generator,        |      |      | -70  |      |

| V <sub>(BO)</sub> | Breakover voltage                       | $V_{GG} = -50 \text{ V}$                                                     |                        |      |      |      | V    |

|                   |                                         | $I_T = -18 \text{ A}$ , I3124 impulse generator, $V_{GG} = -50 \text{ V}$    |                        |      |      | -70  |      |

| t <sub>(BR)</sub> | Breakdown time                          | $I_T$ = -18 A, I3124 impulse generator, $V_{(BR)}$ < -50 $V_{(BR)}$          | /                      |      |      | 2    | μs   |

| VF                | Forward voltage                         | $I_F = 0.6 \text{ A}, t_W = 500 \mu\text{s}, V_{GG} = -50 \text{ V}$         |                        |      |      | 3    | V    |

| VF                | Torward voltage                         | $I_F = 18 \text{ A}, t_W = 500  \mu\text{s}, V_{GG} = -50 \text{ V}$         |                        |      |      | 5    | V    |

|                   | Peak forward recovery                   | I <sub>F</sub> = 20 A, IEC 61000-4-5:1995 combination impu                   | ılse generator,        |      |      | 15   |      |

| $V_{FRM}$         | voltage                                 | $V_{GG} = -50 \text{ V}$                                                     |                        |      |      |      | V    |

|                   | voltage                                 | $I_F = 18 \text{ A}$ , I3124 impulse generator, $V_{GG} = -50 \text{ V}$     |                        |      |      | 15   |      |

| t <sub>FR</sub>   | Forward recovery time                   | I <sub>F</sub> = 18 A, I3124 impulse generator,                              | $V_{F} > 10 \text{ V}$ |      |      | 2    | μS   |

| чн                | i orward recovery time                  | V <sub>GG</sub> = -50 V                                                      | $V_F > 5 V$            |      |      | 4    | μ5   |

| I <sub>H</sub>    | Holding current                         | $I_T$ = -1 A, di/dt = 1A/ms, $V_{GG}$ = -50 V, $T_J$ = 85 °C                 |                        | -150 |      |      | mA   |

| laa               | Gate reverse current                    | $V_{GG} = V_{GKRM}, V_{AK} = 0$                                              | T <sub>J</sub> = 25 °C |      |      | -5   | μΑ   |

| I <sub>GKS</sub>  | date reverse current                    | VGG − VGKRM, VAK − U                                                         | T <sub>J</sub> = 85 °C |      |      | -50  | μΑ   |

| I <sub>GAT</sub>  | Gate reverse current, on state          | $I_T$ = -0.6 A, $t_W$ = 500 $\mu$ s, $V_{GG}$ = -50 $V$                      |                        |      |      | -1   | mA   |

|                   | Gate reverse current,                   |                                                                              |                        |      |      |      |      |

| I <sub>GAF</sub>  | forward conducting                      | I <sub>F</sub> = 0.6 A, t <sub>w</sub> = 500 μs, V <sub>GG</sub> = -50 V     |                        |      |      | -40  | mA   |

| C/Ai              | state                                   | The start, two seeks, tage seet                                              |                        |      |      |      |      |

| I <sub>GT</sub>   | Gate trigger current                    | $I_T = -5 \text{ A}, t_{p(g)} \ge 20  \mu\text{s}, V_{GG} = -50 \text{ V}$   |                        |      |      | 5    | mA   |

| V <sub>GT</sub>   | Gate trigger voltage                    | $I_T = -5 \text{ A, } t_{p(g)} \ge 20  \mu\text{s, } V_{GG} = -50 \text{ V}$ |                        |      |      | 2.5  | V    |

| C                 | Anode-cathode off-<br>state capacitance | f 1 MH= V 1 V L O (occ Note C)                                               | V <sub>D</sub> = -3 V  |      |      | 100  | pF   |

| C <sub>AK</sub>   |                                         | $f = 1 \text{ MHz}, V_d = 1 \text{ V}, I_G = 0, \text{ (see Note 3)}$        |                        |      |      | 60   | рF   |

NOTE 3: These capacitance measurements employ a three terminal capacitance bridge incorporating a guard circuit. The unmeasured device terminals are a.c. connected to the guard terminal of the bridge.

## **Thermal Characteristics**

| Parameter       |                                         | Test Conditions                                                                 |  | Тур. | Max. | Unit |

|-----------------|-----------------------------------------|---------------------------------------------------------------------------------|--|------|------|------|

| $R_{\theta JA}$ | Junction to free air thermal resistance | $P_{tot} = 0.52 \text{ W}, T_A = 85 \text{ °C}, 5 \text{ cm}^2, \text{FR4 PCB}$ |  |      | 160  | °C/W |

### **Parameter Measurement Information**

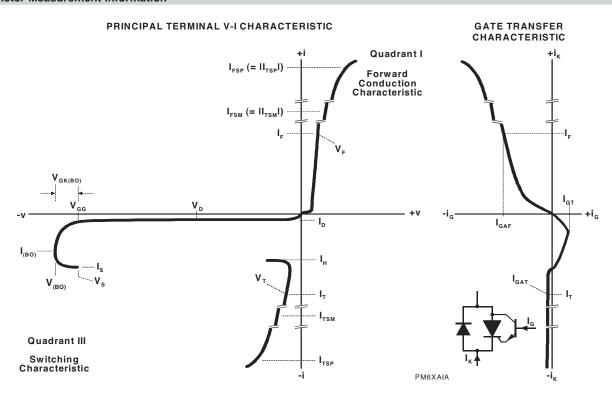

Figure 1. Principal Terminal And Gate Transfer Characteristics

#### **APPLICATIONS INFORMATION**

#### **Operation of Gated Protectors**

Figure 2 and Figure 3 show how the TISP6NTP2A limits overvoltages. The TISP6NTP2A thyristor sections limit negative overvoltages and the diode sections limit positive overvoltages.

Figure 2. Negative Overvoltage Condition

Figure 3. Positive Overvoltage Condition

Negative overvoltages (Figure 2) are initially clipped close to the SLIC negative supply rail value ( $V_{BAT}$ ) by the conduction of the transistor base-emitter and the thyristor gate-cathode junctions. If sufficient current is available from the overvoltage, then the thyristor will crowbar into a low voltage ground referenced on-state condition. As the overvoltage subsides, the high holding current of the crowbar thyristor prevents d.c. latchup. The common gate of each thyristor pair is connected the appropriate SLIC battery feed voltage ( $V_{BAT1}$ ).

The negative protection voltage,  $V_{(BO)}$ , will be the sum of the gate supply  $(V_{BAT})$  and the peak gate (terminal)-cathode voltage  $(V_{GT})$ . Under a.c. overvoltage conditions  $V_{GT}$  will be less than 2.5 V. The integrated transistor buffer in the TISP6NTP2A greatly reduces protectors source and sink current loading on the  $V_{BAT}$  supply. Without the transistor, the thyristor gate current would charge the  $V_{BAT}$  supply. An electronic power supply is not usually designed to be charged like a battery. As a result, the electronic supply would switch off and the thyristor gate current would provide the SLIC supply current. Normally the SLIC current would be less than the gate current, which would cause the supply voltage to increase and destroy the SLIC by a supply overvoltage. The integrated transistor buffer removes this problem.

Fast rising impulses will cause short term overshoots in gate-cathode voltage. The negative protection voltage under impulse conditions will also be increased if there is a long connection between the gate decoupling capacitor and the gate terminal. During the initial rise of a fast impulse, the gate current ( $I_{\text{G}}$ ) is the same as the cathode current ( $I_{\text{K}}$ ). Rates of 60 A/ $\mu$ s can cause inductive voltages of 0.6 V in 2.5 cm of printed wiring track. To minimize this inductive voltage increase of protection voltage, the length of the capacitor to gate terminal tracking should be minimized.

#### **APPLICATIONS INFORMATION**

#### **Operation of Gated Protectors (continued)**

Positive overvoltages (Figure 3) are clipped to ground by forward conduction of the diode section in the TISP6NTP2A. Fast rising impulses will cause short term overshoots in forward voltage (V<sub>FRM</sub>).

### Central Office Application to Bellcore GR-1089-Core Issue 1

The most stressful impulse for first-level surge testing (section 4.5.7) is the 1000 V, 10/1000 impulse. To limit the circuit current to the TISP6NTP2A rating of 20 A requires the total circuit resistance to be  $1000/20 = 50 \Omega$ . Subtracting the generator fictive source impedance of  $10 \Omega$  gives  $40 \Omega$  as the required series resistor value for the TISP6NTP2A (R1A, R1B, R2A and R2B). The various first level impulse current levels are shown in table 1. The maximum 1.2/50 and 2/10 current levels of 56 A are below the TISP6NTP2A ratings of 60 A and 85 A. In table 1, the designation 2x20 means that each conductor has a simultaneous peak current of 20 A and 2x20 = 40 A flows in the anode (ground) connection.

Table 1. First-level Surge Currents

| Waveshape | Open-circuit Voltage<br>V | Short-c ircuit Current<br>A | Generator Resistance $\Omega$ | Wires Tested | Total Series<br>Resistance<br>Ω | I <sub>T</sub> |

|-----------|---------------------------|-----------------------------|-------------------------------|--------------|---------------------------------|----------------|

| 2/10      | 2500                      | 500                         | 5                             | Both         | 22.5                            | 2x56           |

| 1.2/50    | 2500   500   2 + 3/Wire   | 500                         | 0 . 2////                     | Single       | 45                              | 56             |

| 8/20      |                           | Both                        | 28.5                          | 2x53         |                                 |                |

| 10/1000   | 1000                      | 100                         | 10                            | Single       | 50                              | 20             |

| 10/1000   | 1000                      | 10                          | Both                          | 25           | 2x20                            |                |

#### Central Office Application to ITU-T Recommendation K.20

The test level of 1000 V 10/700 delivers a peak short-circuit current level of 25 A, which is equal to the TISP6NTP2A rated value. A series resistor (R1A, R1B, R2A and R2B) is required to ensure coordinated operation with the primary protector at the 4000 V test level. The resistor value will be set by the sparkover voltage of the primary protector. A sparkover voltage of 300 V will give a  $300/25 = 12 \Omega$  series resistor.

## Local Subscribers Line Equipment to ITU-T Recommendation K.21

The test level of 1500 V 10/700 delivers a peak short-circuit current level of 37.5 A. To limit the circuit current to the TISP6NTP2A rating of 25 A requires the total circuit resistance to be  $1500/25 = 60 \Omega$ . Subtracting the generator fictive source impedance of  $40 \Omega$  gives  $20 \Omega$  as the required series resistor value for the TISP6NTP2A. Even at the 1500 V test level, this resistor develops 25x20 = 500 V, which should ensure the coordination with the primary protector sparkover.

#### **APPLICATIONS INFORMATION**

### Indoor POTS Lines to ITU-T Recommendation K.21. K.22 and IEC 61000-4-5: 1995

Internal POTS lines from WILL and ISDN-TA equipment are in a relatively unexposed environment. If these lines are galvanically isolated (floating), the return path for any induced surges can only be through equipment capacitance or insulation breakdown.

The most stressful condition would be when the POTS lines are not galvanically isolated. Such a case is when an ISDN-TA has a common connection between the incoming ISDN line and the internal POTS lines. The ISDN line is likely to be ground referenced and may have primary protection at the subscriber connection. If the primary protection operates, it provides a direct return to ground.

ITU-T recommendation K.22 for a floating 4-conductor T/S bus uses a 1 kV 1.2/50 or 2/10 impulse, capacitively coupled via 8 nF to the bus conductors. Very little circulating current is likely to flow during K.22 testing. If the T/S bus has a ground return, then the testing changes to ITU-T recommendation K.21. The required series resistor values for K.21 and the TISP6NTP2A have been calculated earlier.

In IEC 61000-4-5: 1995 the highest specified test level is class 5. For unshielded symmetrically operated lines, class 5 testing uses a 4000 V combination wave (1.2/50, 8/20) generator to apply a simultaneous impulse to all conductors. For the four conductors of the two POTS lines, the currents are equalized by the use of specified 160  $\Omega$  feed resistors. As the generator fictive source impedance is 2  $\Omega$ , the peak current in each conductor is 4000/(2x4 + 160) = 24 A. This is less than the 60 A TISP6NTP2A rating.

If the lines are long and exit the building, testing is done with a 10/700 generator. In this case the feed resistors are 100  $\Omega$  and the fictive impedance is 15  $\Omega$ . The peak current in each conductor will be 4000/(15x4 + 100) = 25 A. This value is the same as the TISP6NTP2A rating.

As the equipment connected to the POTS line may have uncoordinated protection, it is desirable to provided the ring-tip pair current sharing to the TISP6NTP2A by series resistors (R1A, R1B, R2A and R2B). A value of 4  $\Omega$  should be sufficient to ensure sharing.