#### **GENERAL DESCRIPTION**

The LT9435AC is the P-Channel logic enhancement mode power field effect transistors, using high cell density, DMOS trench technology.

This high density process is especially tailored to minimize on-state resistance.

These devices are particularly suited for low voltage application such as cellular phone, notebook computer power management and other battery powered circuits, and lower power loss that are needed in a

#### **FEATURES**

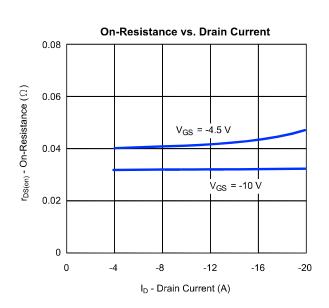

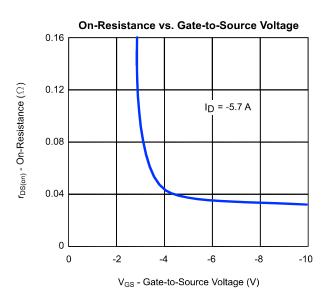

- 1.  $RDS(ON) \leq 40 \text{m} \Omega @VGS = -10V$

- 2.  $RDS(ON) \leq 60m \Omega @VGS = -4.5V$

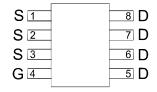

#### PIN CONFIGURATION

(SOP-8) Top View

Ordering Information: LT9435AC (Pb-free)

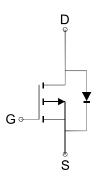

P-Channel MOSFET

#### **Absolute Maximum Ratings** (TA=25°C Unless Otherwise Noted)

| Parameter                               |         | Symbol | 10 secs      | Steady State           | Unit |  |

|-----------------------------------------|---------|--------|--------------|------------------------|------|--|

| Drain-Source Voltage                    |         | VDSS   | -            | V                      |      |  |

| Gate-Source Voltage                     |         | Vgss   | ±20          |                        | V    |  |

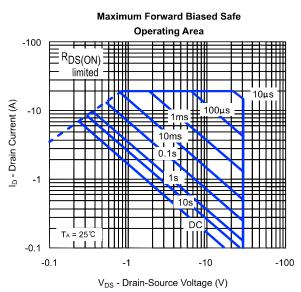

| Continuous Drain Current                | Ta=25°C | lo     | -!           | Α                      |      |  |

| Pulsed Drain Current <sup>1)</sup>      |         | IDM    | -            | Α                      |      |  |

| Maximum Power Dissipation               | Ta=25°C | Po     | 2            | W                      |      |  |

| Operating Junction Temperature          |         | TJ     | -55 1        | $^{\circ}\!\mathbb{C}$ |      |  |

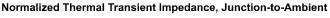

| Junction-to-Case Thermal Resistance     |         | Rejc   | 28           |                        | °C/W |  |

| Junction-to-Ambient Thermal Resistance* |         | Reja   | T≦10 sec     | 34                     | °C/W |  |

|                                         |         |        | Steady State | 62                     | C/VV |  |

<sup>\*</sup>The device mounted on 1in2 FR4 board with 2 oz copper

## **Electrical Characteristics** (TA = 25°C Unless Otherwise Specified)

| Symbol  | Parameter                                     | Limit                                                       | Min  | Тур  | Max  | Unit      |  |  |  |

|---------|-----------------------------------------------|-------------------------------------------------------------|------|------|------|-----------|--|--|--|

| STATIC  |                                               |                                                             |      |      |      |           |  |  |  |

| BVDSS   | Drain-Source Breakdown Voltage                | Vgs=0V, Ip=-250 μ A                                         | -30  |      |      | V         |  |  |  |

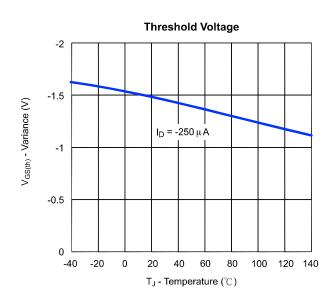

| VGS(th) | Gate Threshold Voltage                        | V <sub>DS</sub> =V <sub>GS</sub> , I <sub>D</sub> =-250 μ A | -1.0 | -2.2 | -3.0 | V         |  |  |  |

| Igss    | Gate Leakage Current                          | V <sub>DS</sub> =0V, V <sub>GS</sub> =±20V                  |      |      | ±100 | nA        |  |  |  |

| IDSS    | Zero Gate Voltage Drain Current               | V <sub>DS</sub> =-24 V <sub>GS</sub> =0V                    |      |      | -1   | $\mu$ A   |  |  |  |

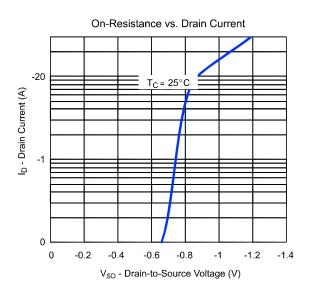

| RDS(ON) | Drain-Source On-State Resistance <sup>a</sup> | Vgs=-10V, ID= -5.3A                                         |      | 31   | 40   | mΩ        |  |  |  |

|         | Diali-Source Oil-State Resistance             | Vgs=-4.5V, Ip= -4.2A                                        |      | 40   | 60   | - 111 2 2 |  |  |  |

| DYNAMIC |                                               | -                                                           | •    | •    | •    |           |  |  |  |

| Rg      | Gate resistance                               | V <sub>DS</sub> =0V, V <sub>GS</sub> =0V, f=1MHz            |      | 5.5  |      | Ω         |  |  |  |

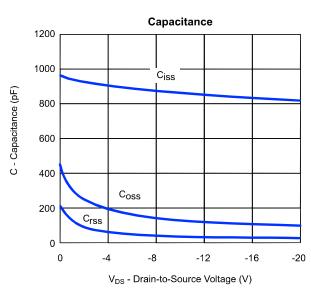

| Ciss    | Input capacitance                             |                                                             |      | 840  | 960  | pF        |  |  |  |

| Coss    | Output Capacitance                            | V <sub>DS</sub> =-15V, V <sub>GS</sub> =0V, f=1.0MHz        |      | 120  |      |           |  |  |  |

| Crss    | Reverse Transfer Capacitance                  |                                                             |      | 35   |      |           |  |  |  |

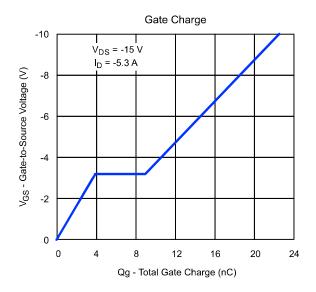

| Qg      | Total Gate Charge                             | \/ 45\/\/ 40\/                                              |      | 21   | 25   | nC        |  |  |  |

| Qgs     | Gate-Source Charge                            | ─ VDS=-15V, VGS=-10V,<br>— ID=-5.3A                         |      | 6    |      |           |  |  |  |

| Qgd     | Gate-Drain Charge                             | ID=-5.3A                                                    |      | 5.4  |      |           |  |  |  |

| td(on)  | Turn-On Delay Time                            | Voc- 15V D15 ()                                             |      | 32   | 40   | - ns      |  |  |  |

| tr      | Turn-On Rise Time                             | V <sub>DD</sub> =-15V, R <sub>L</sub> =15Ω                  |      | 13   | 16   |           |  |  |  |

| td(off) | Turn-Off Delay Time                           | — ID=-1A, VGEN=-10V<br>— RG=6Ω                              |      | 58   | 75   |           |  |  |  |

| tf      | Turn-Off Fall Time                            | 179-077                                                     |      | 6    | 9    |           |  |  |  |

Notes: a. Pulse test: pulse width  $\leq$  300us, duty cycle  $\leq$  2%, Guaranteed by design, not subject to production testing

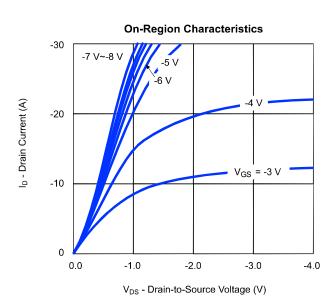

## Typical Characteristics (TJ =25℃ Noted)

## Typical Characteristics (TJ =25℃ Noted)

Square Wave Pulse Duration (sec)

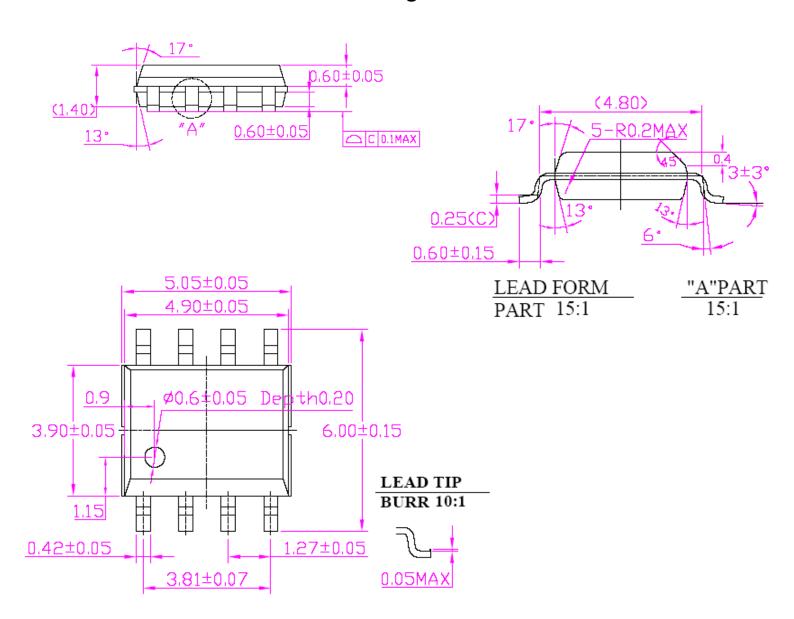

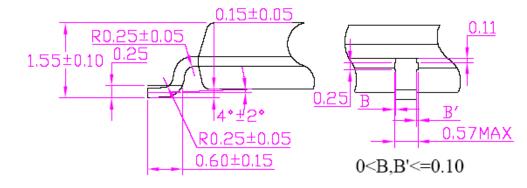

# **SOP-8 Package Outline**

#### NOTES:

- 1. PKG ALL SURFACES ARE Ra0.8-1.2um.

- 2. Mold flash, protrusions or gate burrs shall not exceed 0.15 mm in total (both sides).

## **Important Notice and Disclaimer**

LSC reserves the right to make changes to this document and its products and specifications at any time without notice. Customers should obtain and confirm the latest product information and specifications before final design, purchase or use.

LSC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does LSC assume any liability for application assistance or customer product design. LSC does not warrant or accept any liability with products which are purchased or used for any unintended or unauthorized application.

No license is granted by implication or otherwise under any intellectual property rights of LSC.

LSC products are not authorized for use as critical components in life support devices or systems without express written approval of LSC.