## **Internet Audio Decoder for Flash Memory Media**

**Data Sheet**

#### INTRODUCTION

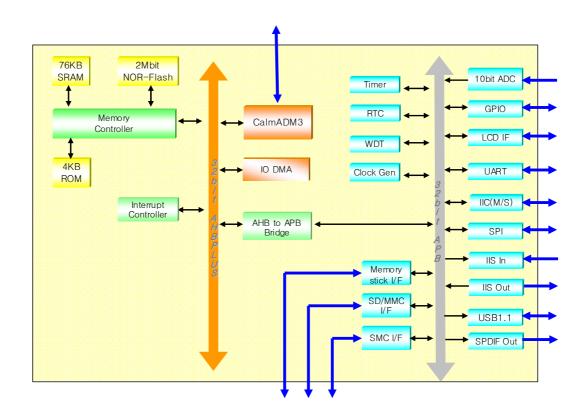

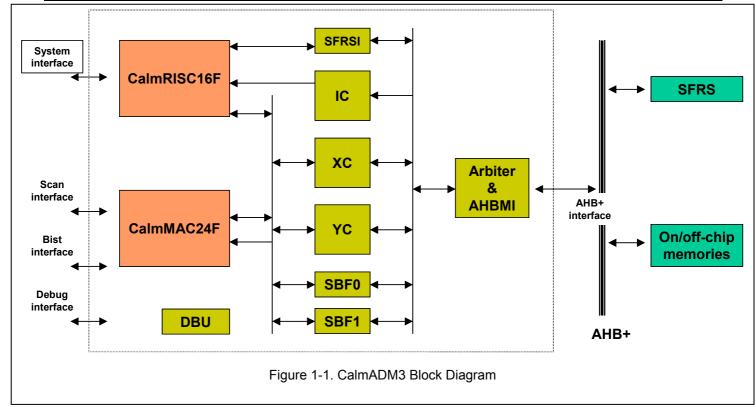

S5L840F is a single chip digital audio player IC supporting various compressed audio format on Flash Memory Media. S5L840F provides 2Mbits of embedded NOR flash memory and 76Kbytes of SRAM requiring no external memory. A 16bit RISC processor (CALMRISC16<sup>TM</sup>) and 24bit MAC(MAC2424<sup>TM</sup>) are provided as a CPU and DSP function.

#### **FEATURES**

Supply voltage range:

- Supply Voltage (Core): 1.8V

- Supply Voltage (IO) : 3.0V

X-tal Oscillator: 32.768 KHz

16bit RISC(CalmRISC16) & 24bit MAC

with 4KB of Instruction Cache

6KB of X Cache

6KB of Y Cache

2Mbit NOR Flash & 76KB SRAM

- IO DMA

- Supports SMC/MMC/SD/Memory Stic

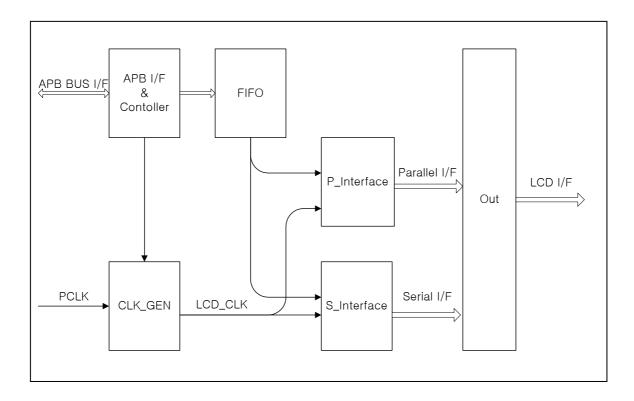

- LCD Controller Interface

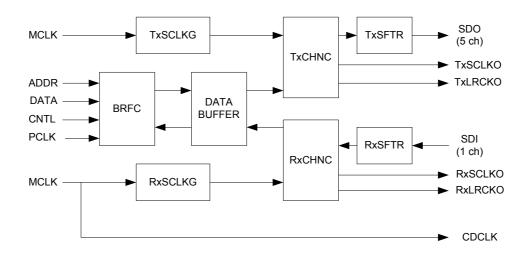

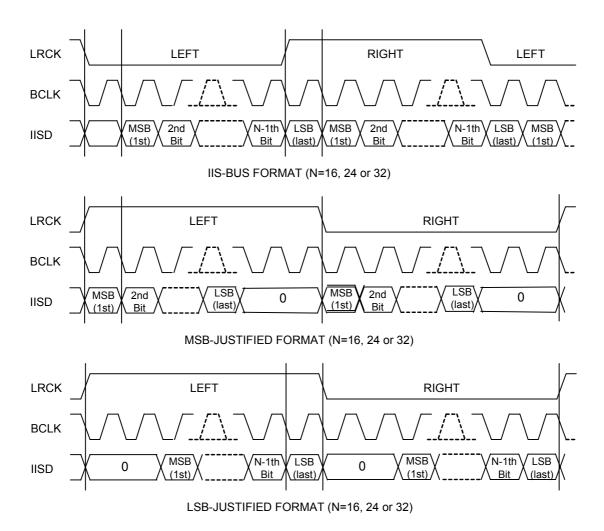

- 2 Channels of IIS

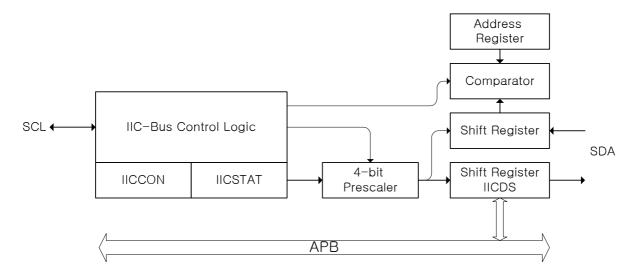

- IIC / SPDIF Output / UART / SPI

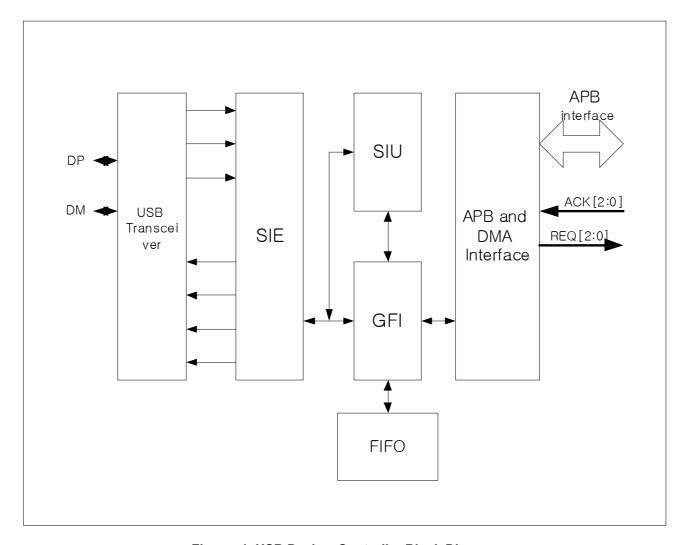

- USB1.1

- 5 channel 10bit ADC

- RTC

- GPIO

#### TYPICAL APPLICATION

MP3/WMA/etc Player

#### ORDERING INFORMATION

| Device  | Package       | Operating Temperature |

|---------|---------------|-----------------------|

| S5L840F | 128-TQFP-1414 | –40 °C − +85 °C       |

### **BLOCK DIAGRAM**

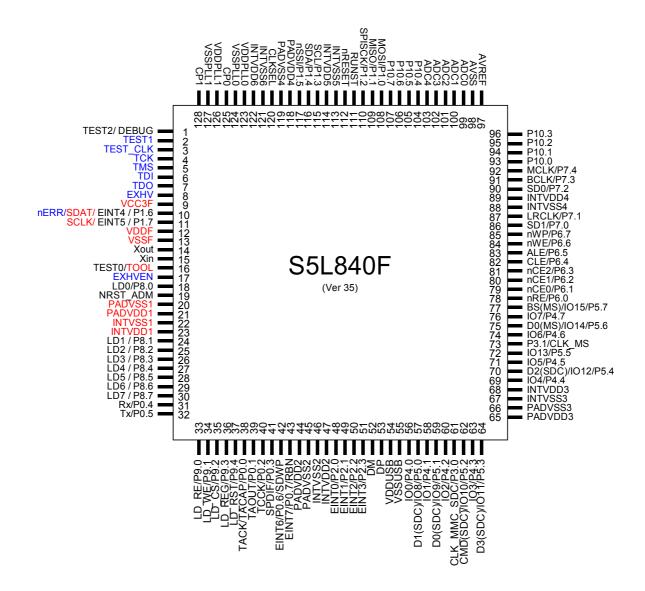

#### PIN CONFIGURATION

## **PIN DESCRIPTION**

| Pin Number | Pin Assignment      | I/O | Pin Description                            |

|------------|---------------------|-----|--------------------------------------------|

| 1          | TEST2/DEBUG         | I   | DEBUG(internal F/F value dump) control     |

| 2          | TEST1               | I   | Test mode                                  |

| 3          | TEST_CLK(for debug) | I   | Test clock                                 |

| 4          | TCK                 | I   | JTAG clock. Pull-Up.                       |

| 5          | TMS                 | I   | JTAG mode selection. Pull-Up.              |

| 6          | TDI                 | I   | JTAG input                                 |

| 7          | TD0                 | 0   | JTAG output                                |

| 8          | EXHV                | В   | Flash high voltage test                    |

| 9          | VCC3F               | Р   | Flash memory internal 3.3V Power.          |

| 10         | nERR/EINT4/P1.6     | В   | UART, GPIO                                 |

| 11         | EINT5/P1.7          | В   | UART, GPIO                                 |

| 12         | VDDF                | Р   | Flash memory internal 1.8V Power.          |

| 13         | VSSF                | Р   | GND for flash core                         |

| 14         | Xout                | 0   | Crystal oscillator signal (~100KHz)        |

| 15         | Xin                 | I   | Crystal oscillator signal (~100KHz)        |

| 16         | TEST0/TOOL_MODE     | I   | BUS/Serial Controller Selection. Pull-Down |

| 17         | EXHVEN              | I   | Flash high volatge test enable. Pull-Down  |

| 18         | LD0/P8.0            | В   | LCD I/F                                    |

| 19         | NTRST_ADM           | I   | Adm reset. Pull-Up.                        |

| 20         | PADVSS1             | Р   | Pad power GND                              |

| 21         | PADVDD1             | Р   | Pad power VDD 3.3V                         |

| 22         | INTVSS1             | Р   | Internal logic GND                         |

| 23         | INTVDD1             | Р   | Internal logic Power VDD 1.8V              |

| 24         | LD1/P8.1            | В   | LCD I/F                                    |

| 25 | LD2/P8.2        | В | LCD I/F                       |

|----|-----------------|---|-------------------------------|

| 26 | LD3/P8.3        | В | LCD I/F                       |

| 27 | LD4/P8.4        | В | LCD I/F                       |

| 28 | LD5/P8.5        | В | LCD I/F                       |

| 29 | LD6/P8.6        | В | LCD I/F                       |

| 30 | LD7/P8.7        | В | LCD I/F                       |

| 31 | Rx/P0.4         | В | INT, GPIO                     |

| 32 | Tx/P0.5         | В | INT, GPIO                     |

| 33 | LD_RE/P9.0      | В | LCD I/F                       |

| 34 | LD_WE/P9.1      | В | LCD I/F                       |

| 35 | LD_CS/P9.2      | В | LCD I/F                       |

| 36 | LD_REG/P9.3     | В | LCD I/F                       |

| 37 | LD_RST/P9.4     | В | LCD I/F                       |

| 38 | TACK/TACAP/P0.0 | В | Timer A, GPIO                 |

| 39 | TAOUT/P0.1      | В | Timer A, GPIO                 |

| 40 | TCCK/P0.2       | В | Timer C, GPIO                 |

| 41 | SPDIF/P0.3      | В | SPDIF, GPIO                   |

| 42 | EINT6/P0.6/SDWP | В | INT, GPIO, SDC_WP             |

| 43 | EINT7/P0.7/RBN  | В | INT, GPIO, RBN(SMC)           |

| 44 | PADVDD2         | Р | Pad power VDD 3.3V            |

| 45 | PADVSS2         | Р | Pad power GND                 |

| 46 | INTVSS2         | Р | Internal logic GND            |

| 47 | INTVDD2         | Р | Internal logic Power VDD 1.8V |

| 48 | EINT0/P2.0      | В | INT, GPIO                     |

| 49 | EINT1/P2.1      | В | INT, GPIO                     |

| 50 | EINT2/P2.2      | В | INT, GPIO                     |

| 51 | EINT3/P2.3         | В | INT, GPIO                      |

|----|--------------------|---|--------------------------------|

| 52 | DM                 | В | USB transceive/receive port    |

| 53 | DP                 | В | USB transceive/receive port    |

| 54 | VDDUSB             | Р | USB Power 3.3V                 |

| 55 | VSSUSB             | Р | USB Ground                     |

| 56 | IO0/P4.0           | В | IO0 for SMC /Debug scan in     |

| 57 | D1(SDC)/IO8/P5.0   | В | IO8 for SMC, D0 for SDC        |

| 58 | IO1/P4.1           | В | IO1 for SMC                    |

| 59 | D0(SDC)/IO9/P5.1   | В | IO9 for SMC, D1 for SDC        |

| 60 | IO2/P4.2           | В | IO2 for SMC                    |

| 61 | CLK_MMC_SDC/P3.0   | В | CLK for MMC/SDC                |

| 62 | CMD(SDC)/IO10/P5.2 | В | IO10 for SMC, CMD/RESP for SDC |

| 63 | IO3/P4.3           | В | IO3 for SMC                    |

| 64 | D3(SDC)/IO11/P5.3  | В | IO11 for SMC, D3 for SDC       |

| 65 | PADVDD3            | Р | Pad power VDD 3.3V             |

| 66 | PADVSS3            | Р | Pad power GND                  |

| 67 | INTVSS3            | Р | Internal logic GND             |

| 68 | INTVDD3            | Р | Internal logic Power VDD 1.8V  |

| 69 | IO4/P4.4           | В | IO4 for SMC                    |

| 70 | D2(SDC)/IO12/P5.4  | В | IO12 for SMC, D2 for SDC       |

| 71 | IO5/P4.5           | В | IO5 for SMC                    |

| 72 | IO13/P5.5          | В | IO13 for SMC                   |

| 73 | P3.1/CLK_MS        | В | GPIO, CLK for MS               |

| 74 | IO6/P4.6           | В | IO6 for SMC                    |

| 75 | D0(MS)/IO14/P5.6   | В | IO14 for SMC, D0 for MS        |

| 76 | IO7/P4.7           | В | IO7 for SMC                    |

| 77  | BS(MS)/IO15/P5.7 | В | IO15 for SMC, BS for MS                    |  |  |  |  |  |

|-----|------------------|---|--------------------------------------------|--|--|--|--|--|

| 78  | nRE/P6.0         | В | SMC control                                |  |  |  |  |  |

| 79  | nCE0/P6.1        | В | SMC control                                |  |  |  |  |  |

| 80  | nCE1/P6.2        | В | SMC control                                |  |  |  |  |  |

| 81  | nCE2/P6.3        | В | SMC control                                |  |  |  |  |  |

| 82  | CLE/P6.4         | В | SMC control                                |  |  |  |  |  |

| 83  | ALE/P6.5         | В | SMC control                                |  |  |  |  |  |

| 84  | nWE/P6.6         | В | SMC control /Debug scan out                |  |  |  |  |  |

| 85  | nWP/P6.7         | В | SMC control                                |  |  |  |  |  |

| 86  | SD1/P7.0         | В | Serial Data In for IIS                     |  |  |  |  |  |

| 87  | LRCLK/P7.1       | В | Left-Right Clock for IIS                   |  |  |  |  |  |

| 88  | INTVSS4          | Р | Internal logic GND                         |  |  |  |  |  |

| 89  | INTVDD4          | Р | Internal logic Power VDD 1.8V              |  |  |  |  |  |

| 90  | SD0/P7.2         | В | Serial Data Out for IIS                    |  |  |  |  |  |

| 91  | BCLK/P7.3        | В | Bit Clock for IIS                          |  |  |  |  |  |

| 92  | MCLK/P7.4        | В | Over-sampling Clock for IIS                |  |  |  |  |  |

| 93  | P10.0            | В | GPIO                                       |  |  |  |  |  |

| 94  | P10.1            | В | GPIO                                       |  |  |  |  |  |

| 95  | P10.2            | В | GPIO                                       |  |  |  |  |  |

| 96  | P10.3            | В | GPIO                                       |  |  |  |  |  |

| 97  | AVREF            | Р | ADC VREF,AVDD33A1,AVDD33A2 연결. 3.3V Power  |  |  |  |  |  |

| 98  | AVSS             | Р | ADC analog GND. avss33a1,avbb33a1,avss33a2 |  |  |  |  |  |

| 99  | ADC0             | I | ADC                                        |  |  |  |  |  |

| 100 | ADC1             | I | ADC                                        |  |  |  |  |  |

| 101 | ADC2             | I | ADC                                        |  |  |  |  |  |

| 102 | ADC3             | I | ADC                                        |  |  |  |  |  |

| 103 | ADC4            | I | ADC                              |

|-----|-----------------|---|----------------------------------|

| 104 | P10.4           | В | GPIO                             |

| 105 | P10.5           | В | GPIO                             |

| 106 | P10.6           | В | GPIO                             |

| 107 | P10.7           | В | GPIO                             |

| 108 | MOSI/P1.0/tclk0 | В | SPI, GPIO, TCLK0(not open)       |

| 109 | MISO/P1.1/tclk1 | В | SPI, GPIO, TCLK1(not open)       |

| 110 | SPISCK/P1.2     | В | SPI, GPIO                        |

| 111 | RUNST           | В | JTAG RUNID / TEST mode select    |

| 112 | nRESET          | I | System RESET. Pull-Up.           |

| 113 | INTVSS5         | Р | Internal logic GND               |

| 114 | INTVDD5         | Р | Internal logic Power VDD 1.8V    |

| 115 | SCL/P1.3        | В | IIC, GPIO                        |

| 116 | SDA/P1.4        | В | IIC, GPIO                        |

| 117 | nSSI/P1.5       | В | SPI, IIC, UART                   |

| 118 | PADVDD4         | Р | Pad power VDD 3.3V               |

| 119 | PADVSS4         | Р | Pad power GND                    |

| 120 | CLKSEL          | Ι | Clock selection signal. Pull-Up. |

| 121 | INTVSS6         | Р | Internal logic GND               |

| 122 | INTVDD6         | Р | Internal logic Power VDD 1.8V    |

| 123 | VDDPLL0         | Р | PLL Power supply VDD 1.8V        |

| 124 | VSSPLL0         | Р | PLL GND                          |

| 125 | CP0             | 0 | Low pass filter circuit for pll0 |

| 126 | VDDPLL1         | Р | PLL Power supply VDD 1.8V        |

| 127 | VSSPLL1         | Р | PLL GND                          |

| 128 | CP1             | 0 | Low pass filter circuit for pll1 |

### **ABSOLUTE MAXIMUM RATINGS**

| Characteristic            | Symbol | Value   | Unit |

|---------------------------|--------|---------|------|

| Supply Voltage            | VDD    | 3.8     | V    |

| Input Voltage             | VIN    | 6.5     | V    |

| Storage Temperature Range | Tstg   | -65–150 | °C   |

#### **ELECTRICAL CHARACTERISTICS**

#### **Recommended Operating Conditions**

| Characteristic              | Symbol | Value                        | Unit |

|-----------------------------|--------|------------------------------|------|

| Supply Voltage              | VDD    | 1.65~1.95(Core), 2.7~3.3(IO) | V    |

| Operating Temperature Range | Topr   | -40–85                       | °C   |

#### **DC Characteristics**

(Ta = 25°C, VDD(IO) = 3.3V, Unless otherwise specified)

| Symbol | Characteristic                                  | Test<br>Conditions   | Min | Тур | Max | Unit |

|--------|-------------------------------------------------|----------------------|-----|-----|-----|------|

| VIH    | High level input voltage                        | _                    | 2.0 | _   | _   | V    |

| VIL    | Low level input voltage                         | _                    | _   | _   | 0.8 | V    |

| VT     | Switching threshold                             |                      |     | 1.4 |     | V    |

| VT+    | Schmitt trigger, positive<br>–going threshold   | CMOS                 |     |     | 2.0 | V    |

| VT-    | Schmitt trigger,<br>negative-going<br>threshold | CMOS                 | 0.8 |     |     | V    |

| VOH    | High level output voltage                       | IOH = -2mA           | 2.4 | -   | _   | V    |

| VOL    | Low level output voltage                        | IOL = 2mA            | _   | _   | 0.4 | V    |

| IOZ    | Tri-state output leakage current                | Vout = Vss or<br>GND | -10 | _   | 10  | μA   |

#### NOTES:

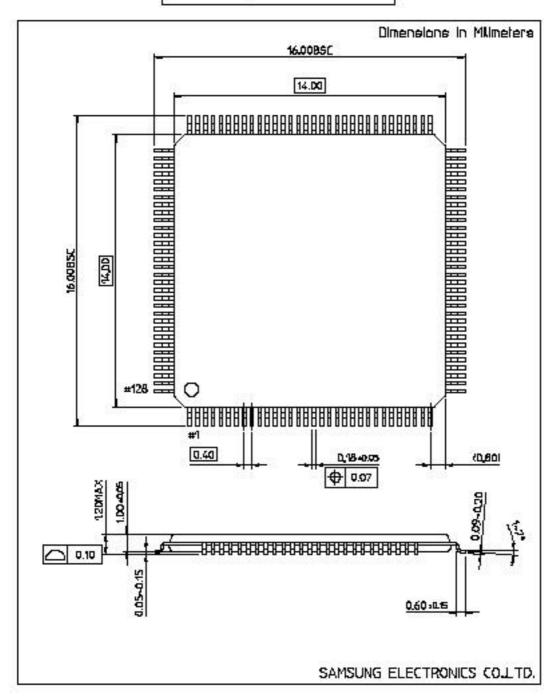

#### **PACKAGE DIMENSIONS**

## 128-TQFP-1414-AN

# Low-Power & High-Performance RISC Core

# CalmRISC16

## **Technical Reference Manual**

MCU Team LSI Division System LSI Business Samsung Electronics Co.

#### 1. Introduction

#### 1.1 Feature

The main features of CalmRISC16, a 16-bit embedded RISC MCU core, are high performance, low power consumption, and efficient coprocessor interface. It can operate up to 100MHz, and consumes 100μA/MHz @3.3V. When operating with MAC2424, a 24-bit fixed point DSP coprocessor, CalmRISC16 can operate up to 80MHz. Through efficient coprocessor interface, CalmRISC16 provides a powerful and flexible MCU+DSP solution. The following gives brief summary of main features of CalmRISC16.

#### ♦ H/W Feature

- Power consumption : 100μA per MHz @3.3V, 0.35μ process

- Maximum frequency: 100MHz @3.3V

- 0.78 mm<sup>2</sup> die size

#### Architecture

- Harvard RISC architecture

- 5-Stage pipeline

#### ◆ Registers

- Sixteen 16-bit general registers

- Eight 6-bit extension registers

- 22-bit Program Counter (PC)

- 16-bit Status Register (SR)

- Seven saved registers for interrupts.

#### ◆ Instruction Set

- 16-bit instruction width for 1-word instructions

- 32-bit instruction width for 2-word instructions

- Load/Store instruction architecture

- Delayed branch support

- C-language/OS support

- Bit operation for I/O process

- ◆ Instruction Execution Time

- One instruction/cycle for basic instructions

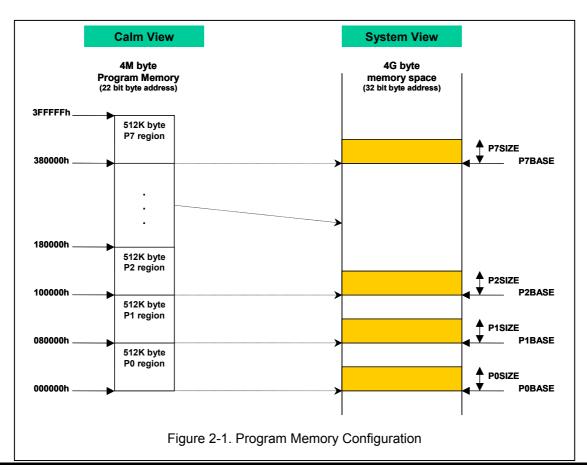

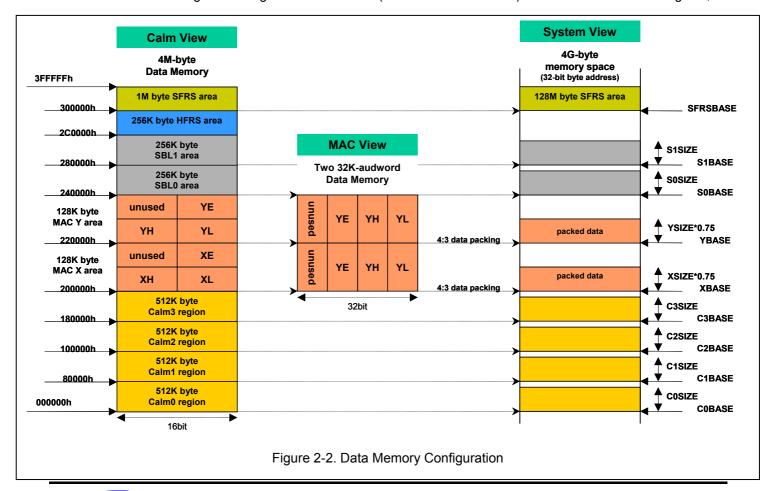

- ♦ Address Space

- 4M byte for Program Memory

- 4M byte for Data Memory

- 2. -

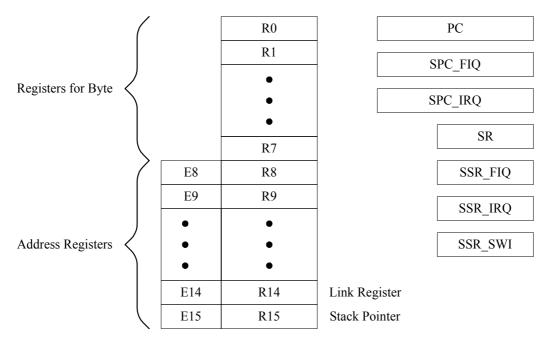

#### 1.2. Registers

In CalmRISC16 there are sixteen 16-bit general registers, eight 6-bit extension registers, a 16-bit Status Register(SR), a program counter (PC), and seven saved registers.

#### General Registers & Extension Registers

The following figure shows the structure of the general registers and the extension registers.

Register Structure in CalmRISC16

The general registers (from R0 to R15) can be either a source register or a destination register for almost all ALU operations, and can be used as an index register for memory load/store instructions (e.g., LDW R3, @[A8+R2]). The 6-bit extension registers (from E8 to E15) are used to form a 22-bit address register (from A8 to A15) by concatenating with a general register (from R8 to R15). The address registers are used to generate 22-bit program and data addresses.

#### Special Registers

The special registers consist of 16-bit SR (Status Register), 22-bit PC (Program Counter), and saved registers for IRQ(interrupt), FIQ(fast interrupt), and SWI(software interrupt). When IRQ interrupt occurs, the most significant 6 bits of the return address are saved in SPCH IRQ, the least significant 16 bits of

The way MCU/DSP should be

the return address are saved in SPCL\_IRQ, and the status register is saved in SSR\_IRQ. When FIQ interrupt occurs, the most significant 6 bits of the return address are saved in SPCH\_FIQ, the least significant 16 bits of the return address are saved in SPCL\_FIQ, and the status register is saved in SSR\_FIQ. When a SWI instruction is executed, the return address is saved in A14 register (E14 concatenated with R14), and the status register is saved in SSR\_SWI. The least significant bit of PC, SPCL\_IRQ and SPCL\_FIQ is read only and its value is always 0.

The 16-bit register SR has the following format.

| 15 |   |   |   |   |   |   | 8 | 7 |    |            |    |   |    |    | 0  |

|----|---|---|---|---|---|---|---|---|----|------------|----|---|----|----|----|

| Т  | _ | - | _ | _ | _ | _ | - | - | PM | <b>Z</b> 1 | Z0 | V | TE | ΙE | FE |

- ◆ FE : FIQ enable bit, FIQ is enabled when FE is set.

- ◆ IE : IRQ enable bit, IRQ is enabled when IE is set.

- ◆ TE: TRQ enable bit, Trace is enabled when TE is set.

- ◆ V : overflow flag, set/clear accordingly when arithmetic instructions are executed.

- ◆ Z0 : zero flag of R6, set when R6 equals zero and used as the branch condition when BNZD instruction with R6 is executed.

- ◆ Z1 : zero flag of R7, set when R7 equals zero and used as the branch condition when BNZD instruction with R7 is executed.

- $\bullet$  PM: privilege mode bit. PM = 1 for privilege mode and PM = 0 for user mode

- ◆ T: true flag, set/clear as a result of an ALU operation.

FE, IE, TE, and PM bits can be modified only when PM = 1 (privilege mode). The only way to change from user mode to privilege mode is via interrupts including SWI instructions. The reserved bit of SR (from bit 7 to bit 14) can be used for other purposes without any notice. Hence programmers should not depend on the value of the reserved bits in their programming. The reserved bits are read as 0 value.

#### 1.3. Pipeline Structure

CalmRISC16 has a 5-stage pipeline architecture. It takes 5 cycles for an instruction to do its operation. In a pipeline architecture, instructions are executed overlapped, hence the throughput is one instruction per cycle. Due to data dependency, control dependency, and 2 word instructions, the throughput is about 1.2 on the average. The following diagram depicts the 5-stage pipeline structure.

| IF ID EA MEN WD |

|-----------------|

|-----------------|

In the first stage, which is called IF (Instruction Fetch) stage, an instruction is fetched from program

memory. In the second stage, which is called ID (Instruction Decoding) stage, the fetched instruction is decoded, and the appropriate operands, if any, for ALU operation are prepared. In the case of branch or jump instructions, the target address is calculated in ID stage. In the third stage, which is called EX (Execution) stage, ALU operation and data address calculation are executed. In the fourth stage, which is called MEM (Memory) stage, data transfer from/to data memory or program memory is executed. In the fifth stage, which is called WB (Write Back) stage, a write-back to register file can be executed. The following figure shows an example of pipeline progress when 3 consecutive instructions are executed.

| I1 : ADD R0, 3  | IF | ID | EX 📍 | MEM <sup>↑</sup>           | WB  |     |    |

|-----------------|----|----|------|----------------------------|-----|-----|----|

| I2 : ADD R1, R0 |    | IF | ID ↓ | EX                         | MEM | WB  |    |

| I3 : LD R2, R0  |    |    | IF   | $_{	ext{ID}}$ $\downarrow$ | EX  | MEM | WB |

In the above example, the instruction I2 needs the result of the instruction I1 before I1 completes. To resolve this problem, the EX stage result of I1 is forwarded to ID stage of I2. Similar forwarding mechanism occurs from MEM stage of I1 to ID stage of I3.

The pipeline cannot progress (called a pipeline stall) due to a data dependency, a control dependency, or a resource conflict.

When a source operand of an ALU instruction is from a register, which is loaded from memory in the previous instruction, 1 cycle of pipeline stall occurs (called load stall). Such load stalls can be avoided by smart reordering of the instruction sequences. CalmRISC16 has 2 classes of branch instructions, those with a delay slot and without a delay slot. Non-delay slot branch instructions incurs a 1 cycle pipeline stall if the branch is taken, due to a control dependency. For branch instructions with a delay slot, no cycle waste is incurred if the delay slot is filled with a useful instruction (or non NOP instruction). Pipeline stalls due to resource conflicts occurs when two different instructions access at the same cycle the same resource such as the data memory and the program memory. LDC (data load from program memory) instruction causes a resource conflict on the program memory. Bit operations such as BITR and BITS (read-modify-write instructions) cause a resource conflict on the data memory.

#### 1.4 Interrupts

In CalmRISC16, there are five interrupts: RESET, FIQ, IRQ, TRQ, SWI. The RESET, FIQ, and IRQ interrupts correspond to external requests. TRQ and SWI interrupts are initiated by an instruction (therefore, in a deterministic way). The following table shows a summary of interrupts.

| Name  | Priority | Address | Description            |

|-------|----------|---------|------------------------|

| RESET | 1        | 000000h | Hardware Reset         |

| FIQ   | 3        | 000002h | Fast Interrupt Request |

- 5 -

| IRQ | 5 | 000004h   | Interrupt Request  |

|-----|---|-----------|--------------------|

| TRQ | 2 | 000006h   | Trace Request      |

| CWI | 4 | 000008h   | Software Intermed  |

| SWI | 4 | ~ 0000feh | Software Interrupt |

When nRES (an input pin CalmRISC16 core) signal is released (transition from 0 to 1), "JMP addr:22" is automatically executed by CalmRISC16. Among the 22-bit address addr:22, the most significant 6 bits are forced to 0, and the least significant 16 bits are the contents of 000000h (i.e., reset vector address) of the program memory. In other words, "JMP {6'h00<sup>1</sup>, PM[000000h]}" instruction is forced to the pipeline. The initial value of PM bit is 1 (that is, in privilege mode) and the initial values of other bits in SR register are 0. All other registers are not initialized (i.e., unknown).

When nFIQ (an input pin CalmRISC16 core) signal is active (transition from 1 to 0), "JMP addr:22" instruction is automatically executed by CalmRISC16. The address of FIQ interrupt service routine is in 000002h (i.e., FIQ vector address) of the program memory (i.e., "JMP {6'h00, PM[000002h]}"). The return address is saved in {SPCH FIQ, SPCL FIQ} register pair, and the SR value is saved in SSR FIQ register. PM bit is set. FE, IE, and TE bits are cleared. When RET FIQ instruction is executed, SR value is restored from SSR FIQ, and the return address is restored into PC from {SPCH FIQ, SPCL FIQ}.

When nIRQ signal (an input pin CalmRISC16 core) is active (transition from 1 to 0), "JMP {6'h00, PM[000004h]}" instruction is forced to the instruction pipeline. The return address is saved in {SPCH IRQ, SPCL IRQ} register pair, and the SR value is saved in SSR IRQ register. PM bit is set. IE and TE bits are cleared. When RET IRQ instruction is executed, SR value is restored from SSR IRQ, and return address is restored to PC from {SPCH IRQ, SPCL IRQ}.

When TE bit is set, TRQ interrupt happens and "JMP {6'h00, PM[000006h]}" instruction is executed right after each instruction is executed. TRQ interrupt uses the saved registers of IRQ(that is, {SPCH IRQ, SPCL IRQ} register pair and SSR IRQ) to save the return address and SR, respectively. PM bit is set. IE, TE bits are cleared.

When "SWI imm:62" instruction is executed, the return address is saved in the register A14, and the value of SR is saved in SSR SWI. Then the program sequence jumps to the address (imm:6 \* 4). PM bit is set. IE and TE bits are cleared. "SWI 0" and "SWI 1" are prohibited because the addresses are reserved for other interrupts. When RET SWI instruction is executed, SR is restored from SSR SWI, and the return address is restored to PC from A14.

- 6 -

### 1.5 Memory Formats

imm:6 is defined as 6-bit immediate number

<sup>&</sup>lt;sup>1</sup> 6'h00 is defined as 00 (or zero) in 6 bits

CalmRISC16 adopts a big endian memory format. In a big endian memory format, the most significant byte of word data is stored at an even address, and the least significant byte is stored at an odd address. For example let us assume that the word data "1234h" is stored at the address 100h. Then the higher byte "12h" is stored at the address 100h, and the lower byte "34h" is stored at the address 101h. When the 22-bit data "123456h" is stored at the address 100h by "LDW @An, Ai" instruction, "00h" is at the address 100h, "12h" is at the address 101h, "34h" is at the address 102h, and "56h" is at the address 103h.

#### 1.6 Signal Description

| Name     | Direction | Description                                                         |

|----------|-----------|---------------------------------------------------------------------|

| PA[20:0] | О         | Program Memory Address, equivalent to PC[21:1]                      |

| PD[15:0] | I         | Program Data                                                        |

| nPMCS    | О         | Program Memory Chip Selection                                       |

| nLDC     | О         | Data load from program memory indicator                             |

| DA[21:0] | О         | Data Memory Address DA[4:0] is shared with SYS and CLD instructions |

| DI[15:0] | I         | Input from Data Memory, Input from coprocessor for CLD instruction. |

| DO[15:0] | О         | Output to Data Memory, Output to coprocessor for CLD instruction.   |

| nDMCSH   | О         | Chip Selection for Higher Byte Data Memory                          |

| nDMCSL   | О         | Chip Selection for Lower Byte Data Memory                           |

| DMWR     | О         | Data Memory Write, 1 means transfer from Core to Memory             |

| nDME     | О         | Data Bus Enable Signal.                                             |

| nRES     | I         | Hardware Reset                                                      |

| nFIQ     | I         | Fast Interrupt Request                                              |

| nIRQ     | I         | Interrupt Request                                                   |

| nEXPACK  | О         | Exception Acknowledge                                               |

| nWAIT    | I         | Wait signal, core is stopped when active.                           |

| nSYSID   | О         | SYS instruction indicator                                           |

| MCLK     | I         | Main Clock Input                                                    |

| ECLK     | О         | Early Clock Output                                                  |

| ICLK     | О         | Clock Output                                                        |

| nCOPID   | О         | Coprocessor instruction indicator                                   |

| nCLDID   | О         | Coprocessor Load instruction indicator                              |

| CLDWR    | О         | Write to Coprocessor indicator                                      |

| COPIR[12:0] | 0 | Instruction to coprocessor, 13-bit immediate field in COP instruction. |

|-------------|---|------------------------------------------------------------------------|

| EC[3:0]     | I | External Conditions from coprocessor or peripherals.                   |

| nBRK        | O | Software break indicator                                               |

| nBKACK      | O | Break Acknowledge                                                      |

| BKMODE[2:0] | О | Break Mode, indicates core state when core breaks.                     |

| BKREQ       | I | Break Request                                                          |

| nGIDIS      | I | Global interrupt disable, when active, all interrupt is disabled.      |

| PDGRANT     | I | Indicates program memory access is permitted.                          |

| PDWAIT      | I | Indicates current program memory access is not complete.               |

| DBGRANT     | I | Indicates data memory access is permitted.                             |

| DBWAIT      | I | Indicates current data memory access is not complete.                  |

| DBREQ       | О | Signal asking for data bus permission.                                 |

| PMODE       | О | Privilege Mode Indicator                                               |

| CGRANT      | О | Indicates that coprocessor may use data bus.                           |

| CSTALL      | I | Coprocessor indicates that coprocessor pipeline stall occurs.          |

| CMW         | I | Coprocessor indicates that coprocessor instruction is multiple word.   |

| nSEQ        | О | Indicates that the next program address is sequential.                 |

| nINCPC      | I | If it is 1, PC value is not incremented when sequential execution.     |

| CCLK        | О | Clock output to coprocessor                                            |

## 2. Instructions

#### 2.1. ALU instructions

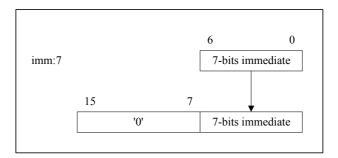

In operations between a 16-bit general register and an immediate value, the immediate value is zero-extended to 16-bit. The following figure shows an example of 7-bit immediate numbers.

In operations between a 22-bit register and an immediate value, the immediate value is zero-extended to

- 8 -

22-bit. In operations between a 22-bit register and a 16-bit register, the 16-bit register is zero-extended to 22-bit. The overflow flag in a 16-bit arithmetic operation is saved to V flag in SR register. ALU instructions are classified into 3 classes as follows.

- ◆ ALUop Register, Immediate

- ◆ ALUop Register, Register

- ◆ ALUop Register

#### ALUop Register, Immediate

#### ADD/ADC/SUB/SBC/AND/OR/XOR/TST/CMP/CMPU Rn, #imm:16

The instructions perform an ALU operation of which source operands are a 16-bit general register Rn and a 16-bit immediate value. In the instructions TST/CMP/CMPU, only T flag is updated accordingly as the result. In the instructions ADD/ADC/SUB/SBC, the value of T flag is the carry flag of the operations, and the value of V flag indicates whether overflow or underflow occurs. In the instructions AND/OR/XOR/TST, the value of T flag indicates whether the result is zero (T=1). "CMP {GT|GE|EQ}, Rn, #imm:16" instructions are for signed comparison operations (GT for greater than, GE for greater than or equal to and EQ for equal to), and "CMPU {GT|GE}, Rn, #imm:16" instructions are for unsigned comparison operations.

#### ADD/SUB An, #imm:16

The immediate value is zero-extended to 22-bit value. No flag update occurs.

#### ADD/SUB Rn, #imm:7

The immediate value is zero-extended to 16-bit value. T flag is updated to the carry of the operation. V flag is updated.

#### AND/OR/XOR/TST R0, #imm:8

The immediate value is zero-extended to 16-bit value. T flag indicates whether the lower 8-bit of the logical operation result is zero.

#### CMP EQ, Rn, #imm:8

The immediate value is zero-extended to 16-bit value. Rn is restricted to R0 to R7. T flag is updated as the result of the instruction.

<sup>&</sup>lt;sup>3</sup> imm:16 is defined as a 16-bit immediate number

MCU Team LSI Division System LSI Business CMP GE, Rn, #imm:6

The immediate value is zero-extended to 16-bit value. The instruction is for signed compare. T flag is

updated as the result of the instruction.

ADD/SUB An, #imm:5

The immediate value is zero-extended to 22-bit value. No flag is updated.

ALUop Register, Register

ADD/SUB/ADC/SBC/AND/OR/XOR/TST/CMP/CMPU Rn, Ri

The instructions perform an ALU operation of which source operands are a pair of 16-bit general registers. In the instructions TST/CMP/CMPU, only T flag is updated as the result. In the instructions ADD/ADC/SUB/SBC, the value of T flag is the carry of the operations, and the value of V flag indicates whether overflow or underflow occurs. In the instructions AND/OR/XOR/TST, the value of T flag indicates whether the result is zero. "CMP {GT|GE|EQ}, Rn, Ri" instructions are for signed comparison,

and "CMPU {GT|GE}, Rn, Ri" instructions are for unsigned comparison.

ADD/SUB An, Ri

16-bit general register Ri is zero-extended to 22-bit value. The result is saved in the 22-bit register An. No

flag update occurs.

CMP EQ, An, Ai

The instruction compares two 22-bit registers.

MUL {SS|SU|US|UU}, Rn, Ri

The general registers Rn and Ri can be one of R0 to R7. The instruction multiplies the lower byte of Rn and the lower byte of Ri, and the 16-bit result is saved in Rn. The optional field, SS, SU, US, and UU, indicates whether the source operands are signed value or unsigned value. The first letter of the two letter qualifiers corresponds to Rn, and the second corresponds to Ri. For example, in the instruction "MUL SU, R0, R1", the 8-bit signed value in the lower byte of R0 and the 8-bit unsigned value in the lower byte of

R1 are multiplied, and the 16-bit result is saved in R0.

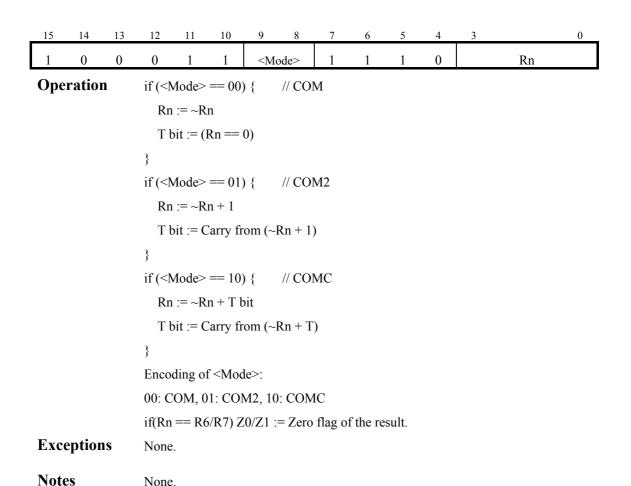

RR/RL/RRC/SR/SRA/SLB/SRB/DT/INCC/DECC/COM/COM2/COMC/EXT Rn

For "DT Rn" (Decrement and Test) and "COM Rn" (Complement) instructions, T flag indicates whether the result is zero. In the instruction of "EXT Rn" (Sign Extend), no flag update occurs. In all other instructions, carry-out of the operation is transferred to T flag. In the instruction of DT, INCC, and DECC,

- 10 -

V flag indicates whether overflow or underflow occurs.

#### 2.2. Load instructions

"Load instructions" move data from register/memory/immediate to register/memory. When the destination is a memory location, only general registers and extension registers can be the source. We can classify "Load instructions" into the following 4 classes.

- LD Register, Register

- ◆ LD Register, Immediate

- ◆ LD Data Memory, Register / LD Register, Data Memory

- ◆ LD Register, Program Memory

#### LD Register, Register

#### LD Rn, Ri / LD An, Ai

The instructions move 16-bit or 22-bit data from the source register to the destination register. When the destination register is R6/R7, the zero flag Z0/Z1 is updated. In all other cases, no flag update occurs.

#### LD Rn, Ei / LD En, Ri

In the instruction "LD Rn, Ei", the 6-bit data in Ei is zero-extended to 16-bit data, and then transferred to Rn. When the destination register is R6/R7, the zero flag Z0/Z1 is updated. In the instruction "LD En, Ri", least significant 6 bits of Ri are transferred to En. Rn/Ri is one of the registers from R0 to R7.

#### LD R0, SPR / LD SPR, R0

#### SPR: SR, SPCL\_FIQ, SPCH\_FIQ, SSR\_FIQ, SPCL\_IRQ, SPCH\_IRQ, SSR\_IRQ, SSR\_SWI

The instructions transfer data between SPR (Special Purpose Registers) and R0. No flag update occurs except the case that the destination register is SR.

#### LD An, PC

The instruction moves the value of (PC+4) to An.

#### LD Register, Data Memory / LD Data Memory, Register

#### LDW Rn, @[SP+edisp:9] / LDW @[SP+edisp:9], Rn

The instructions transfer 16-bit data between a general register Rn and the memory location at the address of (SP+edisp:9). Note SP is another name of A15. edisp:9 is an even positive displacement from 0 to 510.

- 11 -

edisp:9 is encoded into an 8-bit displacement value in the instruction map because the LSB is always 0. When the address is calculated, the 8-bit displacement field is shifted to the left by one bit, and then the result is added to the value of SP. Even if the address might be specified as odd in assembly mnemonic, the LSB of the address should be truncated to zero for word alignment.

#### LDW Rn, @[Ai+edisp:5] / LDW @[Ai+edisp:5], Rn

The instructions transfer 16-bit data between a general register Rn and the memory location at the address of (Ai+edisp:5). edisp:5 is an even positive displacement from 0 to 30. edisp:5 is encoded into an 4-bit displacement value in the instruction map because the LSB is always 0. When the address is calculated, the 4-bit displacement field is shifted to the left by one bit, and then the result is added to the value of Ai. Even if the address might be specified as odd in assembly mnemonic, the LSB of the address should be truncated to zero for word alignment.

#### LDW Rn, @[Ai+disp:16] / LDW @[Ai+disp:16], Rn

The instructions transfer 16-bit data between a general register Rn and the memory location at the address of (Ai+disp:16). disp:16 is an positive displacement from 0 to FFFFh. If the address is odd, the LSB of the address is set to zero for word alignment.

#### LDW Rn, @[Ai+Rj] / LDW @[Ai+Rj], Rn

The instructions transfer 16-bit data between a general register Rn and the memory location at the address of (Ai+Rj). The value of Rj is zero-extended to 22-bit value. If the address is odd, the LSB of the address is set to zero for word alignment.

#### LDW An, @[Ai+edisp:5] / LDW @[Ai+edisp:5], An

The instructions transfer 22-bit data between an address register An and the memory location at the address of (Ai+edisp:5). edisp:5 is an even positive displacement from 0 to 30. edisp:5 is encoded into an 4-bit displacement value in the instruction map because the LSB is always 0. When the address is calculated, the 4-bit displacement field is shifted to the left by one bit, and then the result is added to the value of Ai. Even if the address might be specified as odd in assembly mnemonic, the LSB of the address should be truncated to zero for word alignment.

#### LDW An, @[Ai+disp:16] / LDW @[Ai+disp:16], An

The instructions transfer 22-bit data between an address register An and the memory location at the address of (Ai+disp:16). disp:16 is an positive displacement from 0 to FFFFh. If the address is odd, the LSB of the address is set to zero for word alignment.

- 12 -

#### LDW An, @[Ai+Rj] / LDW @[Ai+Rj], An

The instructions transfer 22-bit data between an address register An and the memory location at the address of (Ai+Rj). The value of Rj is zero-extended to 22-bit value. If the address is odd, the LSB of the address is set to zero for word alignment.

#### PUSH Rn/PUSH Rn, Rm/PUSH An/ PUSH An, Am

The instruction "PUSH Rn" transfers 16-bit data from the register Rn to the memory location at the address of SP, and then increments the value of SP by 2. The register Rn should not be R15. The operation of "PUSH R15" is undefined. The instruction "PUSH Rn, Rm" pushes Rn and then Rm. The registers Rn and Rm should not be the same. The registers Rn and Rm should not be R15. The instruction "PUSH An" pushes Rn and then En. When the extension register En is pushed, the value of En is zero-extended to 16-bit data. The register An should not be A15. The instruction "PUSH An, Am" pushes An and then Am. The registers An and Am should not be the same

#### POP Rn/POP Rn, Rm/POP An/ POP An, Am

The instruction "POP Rn" decrements the value of SP by 2, and then transfers 16-bit data to the register Rn from the memory location at the address of SP. The register Rn should not be R15. The operation of "POP R15" is undefined. The instruction "POP Rn, Rm" pops Rn and then Rm. The registers Rn and Rm should not be the same. The registers Rn and Rm should not be R15. The instruction "POP An" pops En and then Rn. When the extension register En is popped, the least significant 6 bits are transferred to En. The register An should not be A15. The instruction "POP An, Am" pops An and then Am. The registers An and Am should not be the same

#### LDB Rn, @[Ai+disp:4] / LDB @[Ai+disp:4], Rn

The instructions transfer 8-bit data between the general register Rn and the memory location at the address of (Ai+disp:4). disp:4 is a positive displacement from 0 to 15. The general register Rn is one R0 to R7. In the instruction "LDB Rn, @[Ai+disp:4]", the 8-bit data is zero-extended to 16-bit data, and then written into Rn. In the instruction "LDB @[Ai+disp:8], Rn", the least significant byte of Rn is transferred to the memory.

#### LDB Rn, @[Ai+disp:16] / LDB @[Ai+disp:16], Rn

The instructions transfer 8-bit data between the general register Rn and the memory location at the address of (Ai+disp:16). disp:16 is a positive displacement from 0 to FFFFh. The general register Rn is one of R0 to R7. In the instruction "LDB Rn, @[Ai+disp:16]", the 8-bit data is zero-extended to 16-bit data, and then written into Rn. In the instruction "LDB @[Ai+disp:16], Rn", the least significant byte of Rn is transferred to the memory.

- 13 -

#### LDB R0, @[A8+disp:8] / LDB @[A8+disp:8], Rn

The instructions transfer 8-bit data between the general register R0 and the memory location at the address of (A8+disp:8). disp:8 is a positive displacement from 0 to 255. In the instruction "LDB R0, @[A8+disp:8]", the 8-bit data is zero-extended to 16-bit data, and then written into R0. In the instruction "LDB @[A8+disp:8], R0", the least significant byte of R0 is transferred to the memory.

#### LDB Rn, @[Ai+Rj] / LDB @[Ai+Rj], Rn

The instructions transfer 8-bit data between the general register Rn and the memory location at the address of (Ai+Rj). The value of Rj is zero-extended to 22-bit value. The general register Rn is one of the 8 registers from R0 to R7. In the instruction "LDB Rn, @[Ai+Rj]", the 8-bit data is zero-extended to 16-bit data, and then written into R0. In the instruction "LDB @[Ai+Rj], Rn", the least significant byte of Rn is transferred to the memory.

#### LD Register, Program Memory

#### LDC Rn, @Ai

The instruction transfers 16-bit data to Rn from program memory at the address of Ai.

#### LD Register, # immediate

#### LD Rn, #imm:8 / LD Rn, #imm:16 / LD An, #imm:22

The instructions move an immediate data to a register. In the instruction "LD Rn, #imm:8", the immediate value is zero-extended to 16-bit value.

#### 2.3. Branch instructions

CalmRISC16 has 2 classes of branch instructions: with a delay slot and without a delay slot. If a delay slot is filled with a useful instruction (or an instruction which is not NOP), then the performance degradation due to the control dependency can be minimized. However, if the delay slot cannot be used, then it should be NOP instruction, which can increase the program code size. In this case, the corresponding branch instruction without a delay slot can be used to avoid using NOP.

Some instructions are not permitted to be in the delay slot. The prohibited instructions are as follows.

- All 2-word instructions

- All branch and jump instructions including SWI, RETD, RET SWI, RET IRQ, RET

- BREAK instructions

When a prohibited instruction is in the delay slot, the operation of CalmRISC16 is undefined or unpredictable.

- 14 -

#### BSRD eoffset:13

In the instruction, called branch subroutine with a delay slot, the value (PC + 4) is saved into A14 register, the instruction in the delay slot is executed, and then the program sequence is moved to (PC + 2 + eoffset:13), where PC is the address of the instruction "BSRD eoffset:13". The immediate value eoffset:13 is sign-extended to 22-bit and then added to (PC+2). In general, the 13-bit offset field appears as a label in assembly programs. If the instruction in the delay slot reads the value of A14, the value (PC+4) is read. The even offset eoffset:13 is encoded to 12bit signed offset in instruction map by dropping the least significant bit.

#### BRA/BRAD/BRT/BRTD/BRF/BRFD eoffset:11

In the branch instructions, the target address is (PC + 2 + eoffset:11). The immediate value eoffset:11 is sign-extended to 22-bit and then added to (PC+2). The "D" in the mnemonic stands for a delay slot. In general, the 11-bit offset field appears as a label in assembly programs. BRA and BRAD instructions always branch to the target address. BRT and BRTD instructions branch to the target address if T flag is set. BRF and BRFD instructions branch to the target address if T flag is cleared. BRAD/BRTD/BRFD instructions are delay slot branch instructions, therefore the instruction in the delay slot is executed before the branch to the target address or the branch decision is made. The even offset eoffset:11 is encoded to 10-bit signed offset in instruction map by dropping the least significant bit.

#### BRA/BRAD EC:2, eoffset:8

In the branch instructions, the target address is (PC + 2 + eoffset:8). The immediate value eoffset:8 is sign-extended to 22-bit and then added to (PC+2). The EC:2 field indicates one of the 4 external conditions from EC0 to EC3 (input pin signals to CalmRISC16). When the external condition corresponding to EC:2 is set, the program branches to the target address. BRAD has a delay slot. The even offset eoffset:8 is encoded to 7-bit signed offset in instruction map by dropping the least significant bit.

#### BNZD R6/R7, eoffset:8

In the branch instruction, the target address is (PC + 2 + eoffset:8). The immediate value eoffset:8 is sign-extended to 22-bit and then added to (PC+2). "BNZD R6, eoffset:8" instruction branches to the target address if Z0 flag is cleared. "BNZD R7, eoffset:8" instruction branches if Z1 flag is cleared. Before the branch operation, the instruction decrements R6/R7, updates Z0/Z1 flag according to the decrement result, and then executes the instruction in the delay slot. The instruction is used to manage loop counter with just one cycle overhead. In the end of the loop, the value of R6/R7 is -1. When the instruction in the delay slot read the Z0/Z1 flag, the result after the decrement is read. The even offset eoffset:8 is encoded to 7-bit signed offset in instruction map by dropping the least significant bit.

#### JMP/JPT/JPF/JSR addr:22

The target address of the instructions is addr:22. JMP always branches to the target address. JPT branches to the target address if the T flag is set. JPF branches if the T flag is cleared. JSR always branches to the target address with saving the return address (PC+4) into A14. The instructions are 2 word instructions.

#### JMP/JPT/JPF/JSR Ai

The target address of the instructions is the value of Ai. JMP always branches to the target address. JPT branches to the target address if the T flag is set. JPF branches if the T flag is cleared. JSR always branches to the target address with saving the return address (PC+2) into A14.

#### SWI #imm:6/ RET\_SWI/RET\_IRQ/RET\_FIQ

refer to the section for interrupts.

#### RETD

The instruction branches to the address in A14 after the execution of the instruction in the delay slot. When there is no useful instruction adequate to the delay slot, "JMP A14" can be used instead of "RETD".

#### 2.4. Bit Operation

The bit operations manipulate a bit in SR register or in a memory location.

#### BITR/BITS/BITC/BITT @[A8+R1], #imm:3

The source as well as the destination is the 8-bit data in the data memory at the address (A8 + R1). The #imm:3 field chooses a bit position among the 8 bits. BITR resets the bit #imm:3 of the source, and then writes the result to the destination, the same memory location. BITS sets the bit #imm:3 of the source, and then writes the result to the destination. BITC complements the bit #imm:3 of the source, and then writes the result to the destination. BITT does not write any data to the destination. T flag indicates whether the bit #imm:3 of the source is zero. In other words, when the bit #imm:3 of the source is zero, T flag is set. BITR and BITS can be used to implement a semaphore mechanism or lock acquisition/release.

#### CLRSR/SETSR/TSTSR bit

#### bit: FE, IE, TE, Z0, Z1, V, PM

CLRSR instruction clears the corresponding bit of SR. SETSR instruction sets the corresponding bit of SR. TSTSR tests whether the corresponding bit is zero, and stores the result in T flag. For example, when IE flag is zero, "TSTSR IE" instruction sets the T flag. We can clear the T flag by the instruction "CMP GT, R0, R0". We can set the T flag by the instruction "CMP EQ, R0, R0".

- 16 -

#### 2.5. Miscellaneous instructions

#### SYS #imm:5

The instruction activates the output port nSYSID. The #imm:5 is transferred to outside on DA[4:0]. The most significant 17 bits remain unchanged. The instruction is for system command to outside such as power down modes.

#### COP #imm:13

The instruction activates the output port nCOPID. The #imm:13 is transferred to outside on COPIR[12:0]. The instruction is used to transfer instruction to coprocessor. The #imm:13 may be from 200h to 1FFFh.

#### CLD Rn, #imm:5 / CLD #imm:5, Rn

The instruction activates the output port nCOPID, nCLDID, and CLDWR. The least significant 13 bits of the instruction is transferred to outside on COPIR[12:0]. The #imm:5 is transferred to outside on DA[4:0]. The instructions move 16-bit data between Rn and a coprocessor register implied by the #imm:5 field. CLDWR signal indicates whether the data movement is from CalmRISC16 to coprocessor. The register Rn is one 8 registers from R0 to R7.

#### NOP

No operation.

#### BREAK

The software break instruction activates nBRK signal, and holds PA for one cycle. It's for debugging operation.

## 3. CalmRISC16 Instruction Map

|                         | 15 |   |   |   | 8  | 8 7     |              |         |  |  |

|-------------------------|----|---|---|---|----|---------|--------------|---------|--|--|

| ADD Rn, #imm:7          | 0  | 0 | 0 | 0 | Rn | 0       | I            | mm:7    |  |  |

| SUB Rn, #imm:7          | 0  | 0 | 0 | 0 | Rn | 1       | I            | mm:7    |  |  |

| LD Rn, #imm:8           | 0  | 0 | 0 | 1 | Rn |         | Imi          | n:8     |  |  |

| LDW Rn, @[SP + edisp:9] | 0  | 0 | 1 | 0 | Rn |         | Edi          | sp:9    |  |  |

| LDW @[SP + edisp:9], Ri | 0  | 0 | 1 | 1 | Ri |         | Edis         | sp:9    |  |  |

| LDW Rn, @[Ai + edisp:5] | 0  | 1 | 0 | 0 | Rn | 0       | Ai           | Edisp:5 |  |  |

| LDW Rn, @[Ai + Rj]      | 0  | 1 | 0 | 0 | Rn | 1 Ai Rj |              |         |  |  |

| LDW @[An + edisp:5], Ri | 0  | 1 | 0 | 1 | Ri | 0       | 0 An Edisp:5 |         |  |  |

- 17 -

| LDW @[An + Rm], Ri     | 0 | 1 | 0 | 1 |   | F | Ri |   | 1 |   | An |   |   | Rm     |

|------------------------|---|---|---|---|---|---|----|---|---|---|----|---|---|--------|

| LDB Dn, @[Ai + disp:4] | 0 | 1 | 1 | 0 | 0 |   | Dn |   | 0 |   | Ai |   |   | Disp:4 |

| LDB Dn, @[Ai + Rj]     | 0 | 1 | 1 | 0 | 0 |   | Dn |   | 1 |   | Ai |   |   | Rj     |

| LDW An, @[Ai + disp:4] | 0 | 1 | 1 | 0 | 1 |   | An |   | 0 |   | Ai |   |   | Disp:4 |

| LDW An, @[Ai + Rj]     | 0 | 1 | 1 | 0 | 1 |   | An |   | 1 |   | Ai |   |   | Rj     |

| LDB @[An + disp:4], Di | 0 | 1 | 1 | 1 | 0 |   | Di |   | 0 |   | An |   |   | Disp:4 |

| LDB @[An + Rm], Di     | 0 | 1 | 1 | 1 | 0 |   | Di |   | 1 |   | An |   |   | Rm     |

| LDW @[An + disp:4], Ai | 0 | 1 | 1 | 1 | 1 |   | Ai |   | 0 |   | An |   |   | Disp:4 |

| LDW @[An + Rm], Ai     | 0 | 1 | 1 | 1 | 1 |   | Ai |   | 1 |   | An |   |   | Rm     |

| ADD Rn, Ri             | 1 | 0 | 0 | 0 |   | R | ln |   | 0 | 0 | 0  | 0 |   | Ri     |

| SUB Rn, Ri             | 1 | 0 | 0 | 0 |   | R | ın |   | 0 | 0 | 0  | 1 |   | Ri     |

| ADC Rn, Ri             | 1 | 0 | 0 | 0 |   | R | ın |   | 0 | 0 | 1  | 0 |   | Ri     |

| SBC Rn, Ri             | 1 | 0 | 0 | 0 |   | R | ln |   | 0 | 0 | 1  | 1 |   | Ri     |

| AND Rn, Ri             | 1 | 0 | 0 | 0 |   | R | ln |   | 0 | 1 | 0  | 0 |   | Ri     |

| OR Rn, Ri              | 1 | 0 | 0 | 0 |   | R | 'n |   | 0 | 1 | 0  | 1 |   | Ri     |

| XOR Rn, Ri             | 1 | 0 | 0 | 0 |   | R | ln |   | 0 | 1 | 1  | 0 |   | Ri     |

| TST Rn, Ri             | 1 | 0 | 0 | 0 |   | R | ln |   | 0 | 1 | 1  | 1 |   | Ri     |

| CMP GE, Rn, Ri         | 1 | 0 | 0 | 0 |   | R | 'n |   | 1 | 0 | 0  | 0 |   | Ri     |

| CMP GT, Rn, Ri         | 1 | 0 | 0 | 0 |   | R | ln |   | 1 | 0 | 0  | 1 |   | Ri     |

| CMPU GE, Rn, Ri        | 1 | 0 | 0 | 0 |   | R | 'n |   | 1 | 0 | 1  | 0 |   | Ri     |

| CMPU GT, Rn, Ri        | 1 | 0 | 0 | 0 |   | R | ln |   | 1 | 0 | 1  | 1 |   | Ri     |

| CMP EQ, Rn, Ri         | 1 | 0 | 0 | 0 |   | R | ln |   | 1 | 1 | 0  | 0 |   | Ri     |

| LD Rn, Ri              | 1 | 0 | 0 | 0 |   | R | ln |   | 1 | 1 | 0  | 1 |   | Ri     |

| RR Rn                  | 1 | 0 | 0 | 0 | 0 | 0 | 0  | 0 | 1 | 1 | 1  | 0 |   | Rn     |

| RL Rn                  | 1 | 0 | 0 | 0 | 0 | 0 | 0  | 1 | 1 | 1 | 1  | 0 |   | Rn     |

| RRC Rn                 | 1 | 0 | 0 | 0 | 0 | 0 | 1  | 0 | 1 | 1 | 1  | 0 |   | Rn     |

| SRB Rn                 | 1 | 0 | 0 | 0 | 0 | 0 | 1  | 1 | 1 | 1 | 1  | 0 |   | Rn     |

| SR Rn                  | 1 | 0 | 0 | 0 | 0 | 1 | 0  | 0 | 1 | 1 | 1  | 0 |   | Rn     |

| SRA Rn                 | 1 | 0 | 0 | 0 | 0 | 1 | 0  | 1 | 1 | 1 | 1  | 0 |   | Rn     |

| JPF Ai                 | 1 | 0 | 0 | 0 | 0 | 1 | 1  | 0 | 1 | 1 | 1  | 0 | 0 | Ai     |

| JPT Ai                 | 1 | 0 | 0 | 0 | 0 | 1 | 1  | 0 | 1 | 1 | 1  | 0 | 1 | Ai     |

| JMP Ai                 | 1 | 0 | 0 | 0 | 0 | 1 | 1  | 1 | 1 | 1 | 1  | 0 | 0 | Ai     |

| JSR Ai                 | 1 | 0 | 0 | 0 | 0 | 1 | 1  | 1 | 1 | 1 | 1  | 0 | 1 | Ai     |

| SLB Rn                 | 1 | 0 | 0 | 0 | 1 | 0 | 0  | 0 | 1 | 1 | 1  | 0 |   | Rn     |

| DT Rn                  | 1 | 0 | 0 | 0 | 1 | 0 | 0  | 1 | 1 | 1 | 1  | 0 |   | Rn     |

| INCC Rn               | 1 | 0 | 0 | 0 | 1 | 0 | 1  | 0 | 1           | 1 | 1 | 0         |     | Rn   |  |  |

|-----------------------|---|---|---|---|---|---|----|---|-------------|---|---|-----------|-----|------|--|--|

| DECC Rn               | 1 | 0 | 0 | 0 | 1 | 0 | 1  | 1 | 1           | 1 | 1 | 0         |     | Rn   |  |  |

| COM Rn                | 1 | 0 | 0 | 0 | 1 | 1 | 0  | 0 | 1           | 1 | 1 | 0         |     | Rn   |  |  |

| COM2 Rn               | 1 | 0 | 0 | 0 | 1 | 1 | 0  | 1 | 1           | 1 | 1 | 0         |     | Rn   |  |  |

| COMC Rn               | 1 | 0 | 0 | 0 | 1 | 1 | 1  | 0 | 1           | 1 | 1 | 0         |     | Rn   |  |  |

| EXT Rn                | 1 | 0 | 0 | 0 | 1 | 1 | 1  | 1 | 1           | 1 | 1 | 0         |     | Rn   |  |  |

| ADD Rn, #imm:16       | 1 | 0 | 0 | 0 | 0 | 0 | 0  | 0 | 1           | 1 | 1 | 1         |     | Rn   |  |  |

| ADD An, #imm:16       | 1 | 0 | 0 | 0 | 0 | 0 | 0  | 1 | 1           | 1 | 1 | 1         | 0   | An   |  |  |

| SUB An, #imm:16       | 1 | 0 | 0 | 0 | 0 | 0 | 0  | 1 | 1           | 1 | 1 | 1         | 1   | An   |  |  |

| ADC Rn, #imm:16       | 1 | 0 | 0 | 0 | 0 | 0 | 1  | 0 | 1           | 1 | 1 | 1         |     | Rn   |  |  |

| SBC Rn, #imm:16       | 1 | 0 | 0 | 0 | 0 | 0 | 1  | 1 | 1           | 1 | 1 | 1         |     | Rn   |  |  |

| AND Rn, #imm:16       | 1 | 0 | 0 | 0 | 0 | 1 | 0  | 0 | 1           | 1 | 1 | 1         |     | Rn   |  |  |

| OR Rn, #imm:16        | 1 | 0 | 0 | 0 | 0 | 1 | 0  | 1 | 1           | 1 | 1 | 1         |     | Rn   |  |  |

| XOR Rn, #imm:16       | 1 | 0 | 0 | 0 | 0 | 1 | 1  | 0 | 1           | 1 | 1 | 1         |     | Rn   |  |  |

| TST Rn, #imm:16       | 1 | 0 | 0 | 0 | 0 | 1 | 1  | 1 | 1           | 1 | 1 | 1         |     | Rn   |  |  |

| CMP GE, Rn, #imm:16   | 1 | 0 | 0 | 0 | 1 | 0 | 0  | 0 | 1           | 1 | 1 | 1         |     | Rn   |  |  |

| CMP GT, Rn, #imm:16   | 1 | 0 | 0 | 0 | 1 | 0 | 0  | 1 | 1           | 1 | 1 | 1         |     | Rn   |  |  |

| CMPU GE, Rn, #imm:16  | 1 | 0 | 0 | 0 | 1 | 0 | 1  | 0 | 1           | 1 | 1 | 1         |     | Rn   |  |  |

| CMPU GT, Rn, #imm:16  | 1 | 0 | 0 | 0 | 1 | 0 | 1  | 1 | 1           | 1 | 1 | 1         |     | Rn   |  |  |

| CMP EQ, Rn, #imm:16   | 1 | 0 | 0 | 0 | 1 | 1 | 0  | 0 | 1           | 1 | 1 | 1         |     | Rn   |  |  |

| LD Rn, #imm:16        | 1 | 0 | 0 | 0 | 1 | 1 | 0  | 1 | 1           | 1 | 1 | 1         |     | Rn   |  |  |

| Reserved              | 1 | 0 | 0 | 0 | 1 | 1 | 1  |   | 1           | 1 | 1 | 1         |     |      |  |  |

| CMP EQ, Dn, #imm:8    | 1 | 0 | 0 | 1 | 0 |   | Dn |   |             |   |   | Imi       | n:8 |      |  |  |

| AND R0, #imm:8        | 1 | 0 | 0 | 1 | 1 | 0 | 0  | 0 |             |   |   | Imi       | n:8 |      |  |  |

| OR R0, #imm:8         | 1 | 0 | 0 | 1 | 1 | 0 | 0  | 1 |             |   |   | Imi       | n:8 |      |  |  |

| XOR R0, #imm:8        | 1 | 0 | 0 | 1 | 1 | 0 | 1  | 0 |             |   |   | Imi       | n:8 |      |  |  |

| TST R0, #imm:8        | 1 | 0 | 0 | 1 | 1 | 0 | 1  | 1 | Imm:8       |   |   |           |     |      |  |  |

| LDB R0, @[A8+ disp:8] | 1 | 0 | 0 | 1 | 1 | 1 | 0  | 0 | Disp:8      |   |   |           |     |      |  |  |

| LDB @[A8+ disp:8],R0  | 1 | 0 | 0 | 1 | 1 | 1 | 0  | 1 | Disp:8      |   |   |           |     |      |  |  |

| BITR @[A8+R1], bs:3   | 1 | 0 | 0 | 1 | 1 | 1 | 1  | 0 | 0           | 0 | 0 | 0         | 0   | Bs:3 |  |  |

| BITS @[A8+R1], bs:3   | 1 | 0 | 0 | 1 | 1 | 1 | 1  | 0 | 0           | 0 | 0 | 0         | 1   | Bs:3 |  |  |

| BITC @[A8+R1], bs:3   | 1 | 0 | 0 | 1 | 1 | 1 | 1  | 0 | 0           | 0 | 0 | 1         | 0   | Bs:3 |  |  |

| BITT @[A8+R1], bs:3   | 1 | 0 | 0 | 1 | 1 | 1 | 1  | 0 | 0           | 0 | 0 | 1         | 1   | Bs:3 |  |  |

| SYS #imm:5            | 1 | 0 | 0 | 1 | 1 | 1 | 1  | 0 | 0 0 1 Imm:5 |   |   |           |     |      |  |  |

| SWI #imm:6            | 1 | 0 | 0 | 1 | 1 | 1 | 1  | 0 | 0 1 Imm:6   |   |   |           |     |      |  |  |

|                       |   |   |   |   |   |   |    |   |             |   |   | 0 1 Imm:6 |     |      |  |  |

| <u> </u>        |   |   |   | 1 |   |   |   |   |   | 1 | 1 |   |   |   |      | = |

|-----------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|------|---|

| CLRSR bs:3      | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 0 |   | Bs:3 |   |

| SETSR bs:3      | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 1 |   | Bs:3 |   |

| TSTSR bs:3      | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 0 |   | Bs:3 |   |

| NOP             | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0    | 0 |

| BREAK           | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0    | 1 |

| LD R0, SR       | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 1    | 0 |

| LD SR, R0       | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 1    | 1 |

| RET_FIQ         | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 0    | 0 |

| RET_IRQ         | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 0    | 1 |

| RET_SWI         | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1    | 0 |

| RETD            | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1    | 1 |

| LD R0, SPCL_FIQ | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0    | 0 |

| LD R0, SPCH_FIQ | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0    | 1 |

| LD R0, SSR_FIQ  | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 1    | 0 |

| Reserved        | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 1    | 1 |

| LD R0, SPCL_IRQ | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0    | 0 |

| LD R0, SPCH_IRQ | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0    | 1 |

| LD R0, SSR_IRQ  | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1    | 0 |

| Reserved        | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1    | 1 |

| Reserved        | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0    |   |

| LD R0, SSR_SWI  | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1    | 0 |

| Reserved        | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1    | 1 |

| Reserved        | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 |      |   |

| LD SPCL_FIQ, R0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0    | 0 |

| LD SPCH_FIQ, R0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0    | 1 |

| LD SSR_FIQ, R0  | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 1    | 0 |

| Reserved        | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 1    | 1 |

| LD SPCL_IRQ, R0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0    | 0 |

| LD SPCH_IRQ, R0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0    | 1 |

| LD SSR_IRQ, R0  | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1    | 0 |

| Reserved        | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1    | 1 |

| Reserved        | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 0    |   |

| LD SSR_SWI, R0  | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1    | 0 |

| Reserved        | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1    | 1 |

| Reserved        | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 |      |   |

| <u> </u>              |   |   |   | 1 |      |   |    |   |   |   |   |        |       |        |

|-----------------------|---|---|---|---|------|---|----|---|---|---|---|--------|-------|--------|

| Reserved              | 1 | 0 | 0 | 1 | 1    | 1 | 1  | 0 | 1 | 1 | 0 |        | 1     |        |

| Reserved              | 1 | 0 | 0 | 1 | 1    | 1 | 1  | 0 | 1 | 1 | 1 | 0      |       |        |

| LD An, PC             | 1 | 0 | 0 | 1 | 1    | 1 | 1  | 0 | 1 | 1 | 1 | 1      | 0     | An     |

| Reserved              | 1 | 0 | 0 | 1 | 1    | 1 | 1  | 0 | 1 | 1 | 1 | 1      | 1     |        |

| JPF adr:22            | 1 | 0 | 0 | 1 | 1    | 1 | 1  | 1 | 0 | 0 |   | 1      | Adr[2 | 21:16] |

| JPT adr:22            | 1 | 0 | 0 | 1 | 1    | 1 | 1  | 1 | 0 | 1 |   | 1      | Adr[2 | 21:16] |

| JMP adr:22            | 1 | 0 | 0 | 1 | 1    | 1 | 1  | 1 | 1 | 0 |   | 1      | Adr[2 | 21:16] |

| JSR adr:22            | 1 | 0 | 0 | 1 | 1    | 1 | 1  | 1 | 1 | 1 |   | 1      | Adr[2 | 1:16]  |

| LDC Rn, @Ai           | 1 | 0 | 1 | 0 |      | R | ln |   | 0 | 0 | 0 | 0      | 0     | Ai     |

| Reserved              | 1 | 0 | 1 | 0 |      | ı |    |   | 0 | 0 | 0 | 0      | 1     |        |

| LD Dn, Ei             | 1 | 0 | 1 | 0 | 0    |   | Dn |   | 0 | 0 | 0 | 1      | 0     | Ei     |

| LD En, Di             | 1 | 0 | 1 | 0 | 0    |   | Di |   | 0 | 0 | 0 | 1      | 1     | En     |

| CMP EQ, An, Ai        | 1 | 0 | 1 | 0 | 1    |   | An |   | 0 | 0 | 0 | 1      | 0     | Ai     |

| LD An, Ai             | 1 | 0 | 1 | 0 | 1    |   | An |   | 0 | 0 | 0 | 1      | 1     | Ai     |

| LDW Rn, @[Ai+disp:16] | 1 | 0 | 1 | 0 |      | R | n  |   | 0 | 0 | 1 | 0      | 0     | Ai     |

| LDW @[An+disp:16], Ri | 1 | 0 | 1 | 0 |      | R | Ri |   | 0 | 0 | 1 | 0      | 1     | An     |

| LDB Dn, @[Ai+disp:16] | 1 | 0 | 1 | 0 | 0    |   | Dn |   | 0 | 0 | 1 | 1      | 0     | Ai     |

| LDB @[An+disp:16], Di | 1 | 0 | 1 | 0 | 0    |   | Di |   | 0 | 0 | 1 | 1      | 1     | An     |

| LDW An, @[Ai+disp:16] | 1 | 0 | 1 | 0 | 1    |   | An |   | 0 | 0 | 1 | 1 0 Ai |       | Ai     |

| LDW @[An+disp:16], Ai | 1 | 0 | 1 | 0 | 1    |   | Ai |   | 0 | 0 | 1 | 1      | 1     | An     |

| CMP GE, Dn, #imm:6    | 1 | 0 | 1 | 0 | 0    |   | Dn |   | 0 | 1 |   |        | Imi   | m:6    |

| ADD An, #imm:5        | 1 | 0 | 1 | 0 | 1    |   | An |   | 0 | 1 | 0 |        | i     | mm:5   |

| SUB An, #imm:5        | 1 | 0 | 1 | 0 | 1    |   | An |   | 0 | 1 | 1 |        | i     | mm:5   |

| CMP EQ, An, #imm:22   | 1 | 0 | 1 | 0 | 0    |   | An |   | 1 | 0 |   | I      | mm[2  | 21:16] |

| LD An, #imm:22        | 1 | 0 | 1 | 0 | 1    |   | An |   | 1 | 0 |   | I      | mm[2  | 21:16] |

| ADD An, Ri            | 1 | 0 | 1 | 0 | 0    |   | An |   | 1 | 1 | 0 | 0      |       | Ri     |

| SUB An, Ri            | 1 | 0 | 1 | 0 | 1    |   | An |   | 1 | 1 | 0 | 0      |       | Ri     |

| MUL UU, Dn, Di        | 1 | 0 | 1 | 0 | 0    |   | Dn |   | 1 | 1 | 0 | 1      | 0     | Di     |

| MUL US, Dn, Di        | 1 | 0 | 1 | 0 | 0    |   | Dn |   | 1 | 1 | 0 | 1      | 1     | Di     |

| MUL SU, Dn, Di        | 1 | 0 | 1 | 0 | 1    |   | Dn |   | 1 | 1 | 0 | 1      | 0     | Di     |

| MUL SS, Dn, Di        | 1 | 0 | 1 | 0 | 1 Dn |   | 1  | 1 | 0 | 1 | 1 | Di     |       |        |

| POP Rn[, Rm]          | 1 | 0 | 1 | 0 | Rm   |   | 1  | 1 | 1 | 0 | 0 | Rn     |       |        |

| Reserved              | 1 | 0 | 1 | 0 | 0    |   |    |   | 1 | 1 | 1 | 0      | 1     |        |

| POP An[, Am]          | 1 | 0 | 1 | 0 | 1    |   | Am |   | 1 | 1 | 1 | 0      | 1     | An     |

| PUSH Rn[, Rm]         | 1 | 0 | 1 | 0 |      | R | m  |   | 1 | 1 | 1 | 1      | 0     | Rn     |

| Reserved             | 1 | 0 | 1 | 0      | 0 |   |            |    | 1   | 1     | 1     | 1      | 1      |     |

|----------------------|---|---|---|--------|---|---|------------|----|-----|-------|-------|--------|--------|-----|

| PUSH An[, Am]        | 1 | 0 | 1 | 0      | 1 |   | Am         |    | 1   | 1     | 1     | 1      | 1      | An  |

| BSRD eoffset:13      | 1 | 0 | 1 | 1      |   |   |            |    |     | Eoffs | et:13 | 3      |        |     |

| BRA EC:2, eoffset:8  | 1 | 1 | 0 | 0      | 0 | 0 | 0          | EC | C:2 |       |       | Ес     | offset | ::8 |

| Reserved             | 1 | 1 | 0 | 0      | 0 | 0 | 1          |    |     |       |       |        |        |     |

| BRAD EC:2, eoffset:8 | 1 | 1 | 0 | 0      | 0 | 1 | 0          | EC | C:2 |       |       | Ес     | offset | ::8 |

| BNZD H, eoffset:8    | 1 | 1 | 0 | 0      | 0 | 1 | 1          | Н  | 0   |       |       | Ес     | offset | ::8 |

| Reserved             | 1 | 1 | 0 | 0      | 0 | 1 | 1          |    | 1   |       |       |        |        |     |

| BRA eoffset:11       | 1 | 1 | 0 | 0      | 1 | 0 |            |    |     |       | Eoffs | set:11 | l      |     |

| BRAD eoffset:11      | 1 | 1 | 0 | 0      | 1 | 1 |            |    |     |       | Eoffs | set:11 |        |     |

| BRF eoffset:11       | 1 | 1 | 0 | 1      | 0 | 0 |            |    |     |       | Eoffs | set:11 |        |     |

| BRFD eoffset:11      | 1 | 1 | 0 | 1      | 0 | 1 |            |    |     |       | Eoffs | set:11 | l      |     |

| BRT eoffset:11       | 1 | 1 | 0 | 1      | 1 | 0 |            |    |     |       | Eoffs | set:11 | l      |     |

| BRTD eoffset:11      | 1 | 1 | 0 | 1      | 1 | 1 | Eoffset:11 |    |     |       |       |        |        |     |

| CLD Dn, imm:5        | 1 | 1 | 1 | 0      | 0 | 0 | 0          |    | i   | mm:   | 5     |        | 0      | Dn  |

| CLD imm:5, Di        | 1 | 1 | 1 | 0      | 0 | 0 | 0          |    | i   | mm:   | 5     |        | 1      | Di  |

| COP imm:13           | 1 | 1 | 1 | Imm:13 |   |   |            |    |     |       |       |        |        |     |

• An[21:0] : A8  $\sim$  A15, concatenation of En and Rn

$\bullet$  En[5:0] : E8 ~ E15, MS 6-bit of An  $\bullet$  SP : equal to A15

## 4. Quick Reference

| Instruction | op1 | op2     | operation             | flag     |

|-------------|-----|---------|-----------------------|----------|

| ADD         | _   | #imm:7  | op1 <- op1 + op2      | T=C, Z0, |

| SUB         | Rn  | Ri      | op1 <- op1 + ~op2 + 1 | Z1,V     |

|             |     | #imm:8  |                       |          |

| LD          | Rn  | #imm:16 | op1 <- op2            | Z0, Z1   |

|             |     | Ri      |                       |          |

| 1       | i               | <u> </u>      |                                               | † 1    |

|---------|-----------------|---------------|-----------------------------------------------|--------|

|         |                 | @[SP+edisp:9] |                                               |        |

| LDW     | Rn              | @[Ai+edisp:5] | op1 <- op2                                    |        |

| LDW     | Kii             | @[Ai+Rj]      | op1 <- op2                                    | -      |

|         |                 | @[Ai+disp:16] |                                               |        |

|         | @[SP+edisp:9]   |               |                                               |        |

|         | @[An+edisp:5]   |               |                                               |        |

| LDW     | @[An+Rm]        | Ri            | op1 <- op2                                    | -      |

|         | @[Ai+disp:16]   |               |                                               |        |

|         |                 | @[Ai+edisp:5] |                                               |        |

| LDW     | An              | @[Ai+Rj]      | op1 <- op2                                    | -      |

|         |                 | @[Ai+disp:16] |                                               |        |

|         | @[An+edisp:5]   |               |                                               |        |

| LDW     | @[An+Rm]        | Ai            | op1 <- op2                                    | _      |

|         | @[Ai+disp:16]   |               | • •                                           |        |

|         | Of sales        | @[SP+disp:8]  |                                               |        |

|         |                 | @[Ai+disp:4]  |                                               |        |

| LDB     | Dn              | @[Ai+Rj]      | op1<-{8'h0,op2[7:0]}                          | -      |

|         |                 | @[Ai+disp:16] |                                               |        |

| LDB     | R0              | @[A8+disp:8]  | op1<-{8'h0,op2[7:0]}                          | -      |

|         | @[SP+disp:8]    | 0             |                                               |        |

|         | @[An+disp:4]    |               |                                               |        |

| LDB     | @[Ai+Rj]        | Di            | op1 <- op2[7:0]                               | -      |

|         | @[Ai+disp:16]   |               |                                               |        |

| LDB     | @[A8+disp:8]    | R0            | op1 <- op2[7:0]                               | _      |

| ADC     | (e)[110 disp.o] | Ri            | op1 < -op1 + op2 + T                          | T=C,V, |

| SBC     | Rn              | #imm:16       | op1 < op1 + op2 + T $op1 < op1 + op2 + T$     | Z0,Z1  |

| AND     |                 | //IIIII.10    | op1 <- op1 & op2                              | 20,21  |

| OR      | Rn              | Ri            | op1 <- op1   op2                              | T=Z,   |

| XOR     | Kii             | #imm:16       | op1 <- op1 ^ op2                              | Z0,Z1  |

| AOR     |                 | D:            | ορτ <- ορτ ορ2                                |        |

| TST     | Rn              | Ri            | op1 & op2                                     | T=Z    |

| CMD CE  |                 | #imm:16       | on1  2   1 T N                                |        |

| CMP GE  |                 |               | $op1 + \sim op2 + 1$ , $T = \sim N$           |        |

| CMPU GE | n               | Ri            | $op1 + \sim op2 + 1$ , $T = \sim N \& \sim Z$ | T      |

| CMPU GE | Rn              | #imm:16       | $op1 + \sim op2 + 1, T=C$                     | Т      |

| CMPU GT |                 |               | op1 + $\sim$ op2 + 1, T=C& $\sim$ Z           |        |

| CMP EQ  |                 |               | op1 + $\sim$ op2 + 1, T=Z                     |        |

- 23 -

| RR     |          |         | op1 <- {op1[0],op1[15:1]}            | T=op1[0]  |

|--------|----------|---------|--------------------------------------|-----------|

| RL     |          |         | op1 <- {op1[14:0],op1[15]}           | T=op1[15] |

| RRC    |          |         | op1 <- {T,op1[15:1]}                 | T=op1[0]  |

| SRB    | Rn       | -       | op1 <- {8'h00,op1[15:8]}             | T=op1[7]  |

| SR     |          |         | op1 <- {0,op1[15:1]}                 | T=op1[0]  |

| SRA    |          |         | op1 <- {op1[15],op1[15:1]}           | T=op1[0]  |

| SLB    |          |         | op1 <- {op1[7:0],8'h00}              | T= op1[8] |

| 5.5    |          |         |                                      | T=Z,      |

| DT     | Rn       |         | op1 <- op1 + 0xffff                  | Z0,Z1,V   |

|        |          |         | Op1 <- ~op1                          | T=Z,Z0,   |

| COM    | Rn       |         |                                      | Z1        |

| INCC   |          |         | op1 <- op1 + T                       |           |

| DECC   |          |         | op1 < -op1 + 0xffff + T              | T=C,Z0,   |

| COM2   | Rn       |         | op1 <- ~op1 + 1                      | Z1        |

| COMC   |          |         | op1 <- ~op1 + T                      |           |

| EXT    | Rn       |         | op1<-{8{op1[7]},op1[7:0]}            | Z0, Z1    |

| JPF    |          |         | if(T==0) PC <- op1                   |           |

| JPT    | Ai       |         | if(T==1) PC <- op1                   |           |

| JMP    | addr:22  |         | PC <- op1                            | -         |

| JSR    |          |         | A14 <- PC+(2 4), PC<-op1             |           |

|        |          |         | ` · / ·                              | T=C,      |

| ADD    | Rn       | #imm:16 | op1 <- op1 + op2                     | Z0,Z1,V   |

|        |          | #imm:16 |                                      |           |

| ADD    | An       | #imm:5  | op1 <- op1 + op2<br>op1 <- op1 - op2 | _         |

| SUB    | 7111     | Ri      |                                      |           |

| CMP EQ | Dn       | #imm:8  | op1 + ~op2 + 1                       | T=Z       |

| AND    | Dii      | WHITE O | Op1 <- op1 & {8'h00,op2}             |           |

| OR     |          | #imm:8  | op1 <- op1   {8'h00,op2}             |           |

| XOR    | R0       |         | op1 <- op1 \ {8'h00,op2}             | T=Z8      |

| TST    |          |         | op1 & {8'h00,op2}                    |           |

| BITR   |          |         | op1[op2] <- 0                        |           |

| BITS   |          | bs:3    | op1[op2] <- 0                        | T=        |

| BITC   | @[A8+R1] |         | op1[op2] <- \cdot \cop1[op2]         | op1[op2]  |

| BITT   |          |         | op1[op2] <- op1[op2]                 | ορτ[ομ2]  |

| SYS    | #imm:5   |         |                                      |           |

|        |          | -       | DA[4:0] <- op1                       | IE TE     |

| SWI    | #imm:6   | -       | A14 <- PC+2, PC <- op2*4             | IE, TE    |

| 1      | <u> </u>  | <u>+</u> |                                     | <u> </u> |

|--------|-----------|----------|-------------------------------------|----------|

| CLRSR  |           |          | SR[op1] <- 0                        |          |

| SETSR  | bs:3      | -        | SR[op1] <- 1                        | -        |

| TSTSR  |           |          | T <- ~SR[op1]                       |          |

| RETD   | -         | -        | PC <- A14                           | -        |

|        | R0        | SR       | op1 <- op2                          |          |

| LD     |           | SPCL_FIQ |                                     |          |

|        |           | SPCH_FIQ |                                     |          |

|        |           | SSR_FIQ  |                                     |          |

|        |           | SPCL_IRQ |                                     | -        |

|        |           | SPCH_IRQ |                                     |          |

|        |           | SSR_IRQ  |                                     |          |

|        |           | SSR_SWI  |                                     |          |

|        | SR        | _        |                                     |          |

|        | SPCL_FIQ  |          | op1 <- op2                          |          |

|        | SPCH_FIQ  | R0       |                                     |          |

|        | SSR_FIQ   |          |                                     |          |

| LD     | SPCL_IRQ  |          |                                     |          |

|        | SPCH_IRQ  |          |                                     |          |

|        | SSR_IRQ   |          |                                     |          |

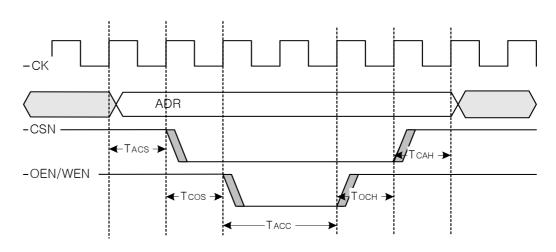

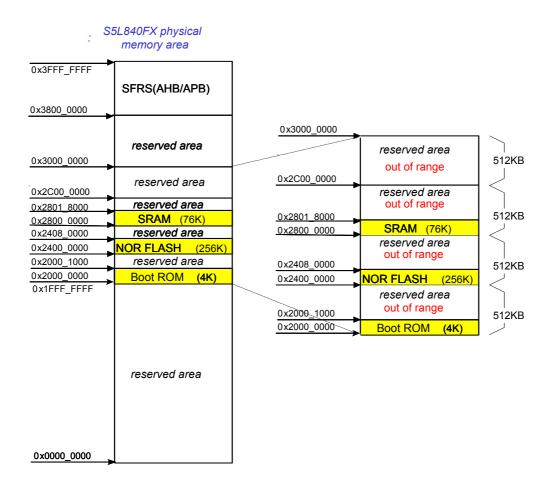

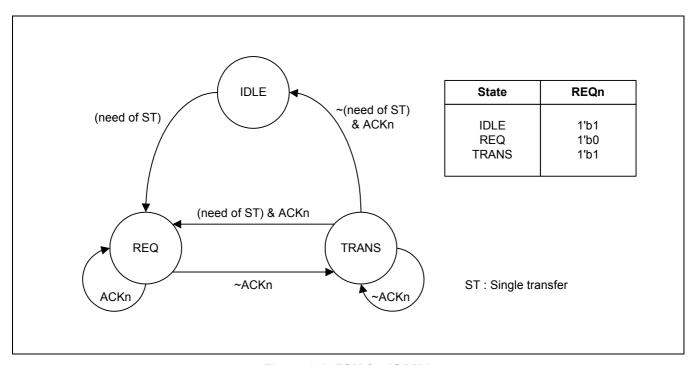

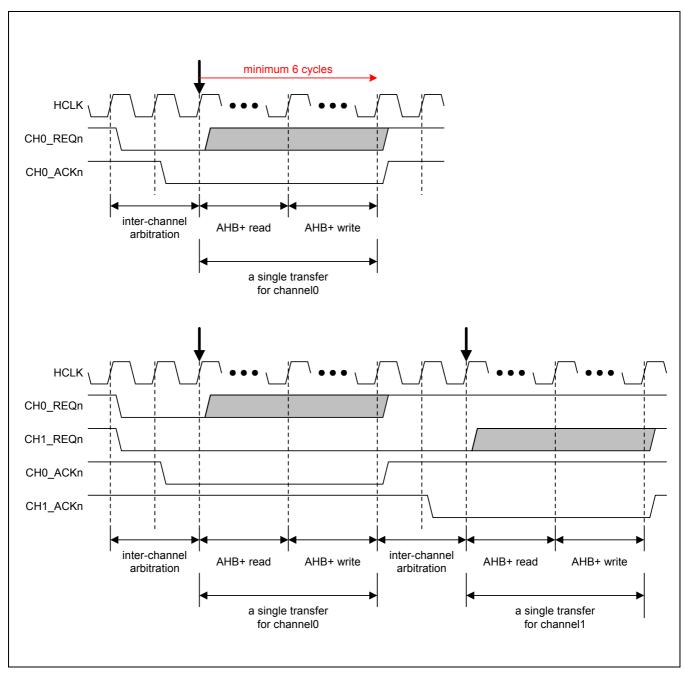

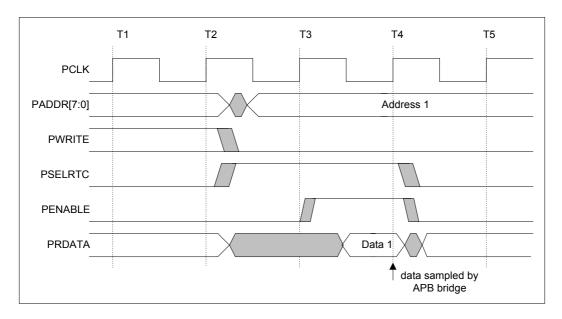

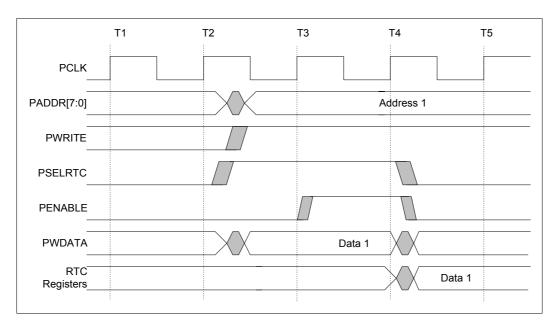

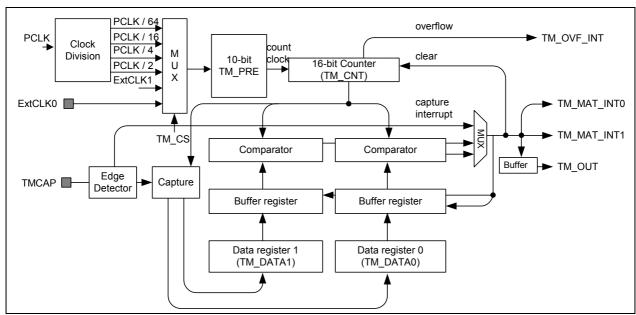

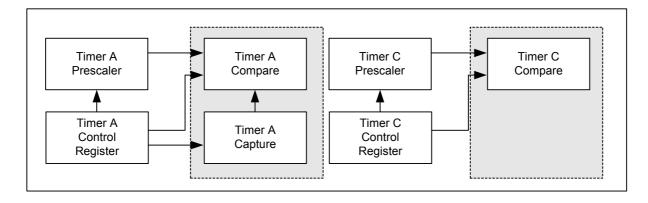

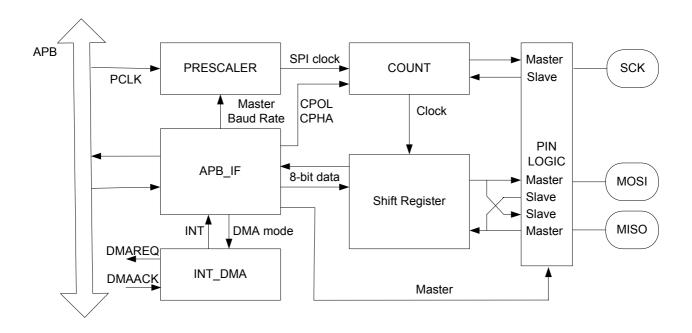

|        | SSR_SWI   |          |                                     |          |