# MR27V1641L

16M-Word × 1-Bit Serial Production Programmed ROM (P2ROM)

#### **GENERAL DESCRIPTION**

The MR27V1641L is a 16 Mbit Production Programmed Read-Only Memory, which is configured as 16,777,216 word × 1-bit. The MR27V1641L supports a simple read operation using a single 3.3V power supply and a Serial Peripheral Interface (SPI) compatible serial bus.

The MR27V1641L have data programmed and have functions tested at LAPIS Semiconductor factory. (Using the DC pins for the programming function is NOT allowed.)

#### **FEATURES**

- $\cdot$  16,777,216-word  $\times$  1-bit configuration

- $\cdot$  +3.0 V to 3.6 V power supply

- · Access time 33 MHz serial clock (FAST-READ)

20 MHz serial clock (READ)

- · Read Identification Instruction

- · Active read current 25 mA MAX (FAST-READ)

20 mA MAX (READ)

- · Standby current 50 µA MAX

- · Serial Clock Input and Data Input/Output

- · Input Data Format

1-byte command code, 3-byte address, 1-byte dummy

(FAST-READ)

1-byte command code, 3-byte address

(READ)

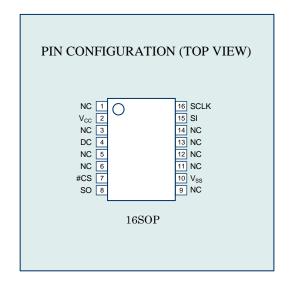

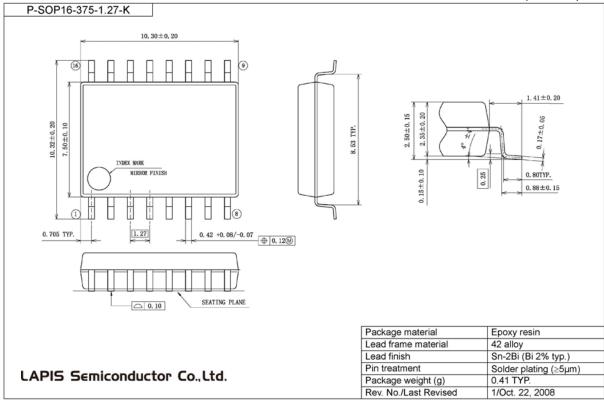

#### **PACKAGES**

· MR27V1641L-xxxMP 16-pin plastic SOP (P-SOP16-375-1.27-K)

#### PIN DESCRIPTIONS

| Pin name        | Functions                                                                                                   |

|-----------------|-------------------------------------------------------------------------------------------------------------|

| #CS             | Chip Select                                                                                                 |

| SI              | Serial Data Input                                                                                           |

| SO              | Serial Data Output                                                                                          |

| SCLK            | Clock Input                                                                                                 |

| V <sub>CC</sub> | Power supply voltage                                                                                        |

| $V_{SS}$        | Ground                                                                                                      |

| DC              | Don't care (0v - Vcc) <for reference=""> Program power supply voltage Vpp under Programming operation</for> |

| NC              | No connection                                                                                               |

## READ COMMAND DEFINITION

| Command | Read Array (byte)                   | Note |

|---------|-------------------------------------|------|

| 1st     | 03[H]                               | 1    |

| 2nd     | AD1                                 | 2    |

| 3rd     | AD2                                 | 2    |

| 4th     | AD3                                 | 2    |

| Action  | N byte read out until #CS goes high | 3    |

- The 1<sup>st</sup> command 03[H] is a Read command

AD1 to AD3 are address input data

- 3. Data output

Details of Command are shown as follows.

| 1-byte command | code |     |     |     |     |     |     |     |

|----------------|------|-----|-----|-----|-----|-----|-----|-----|

| READ:          | 0    | 0   | 0   | 0   | 0   | 0   | 1   | 1   |

| 3-byte address |      |     |     |     |     |     |     |     |

| AD1:           | Χ    | Χ   | X   | A20 | A19 | A18 | A17 | A16 |

| AD2:           | A15  | A14 | A13 | A12 | A11 | A10 | A9  | A8  |

| AD3:           | A7   | A6  | A5  | A4  | A3  | A2  | A1  | A0  |

## Note:

X: Dummy bit

## **FAST-READ COMMAND DEFINITION**

| Command | Read Array (byte)                   | Note |

|---------|-------------------------------------|------|

| 1st     | 0B[H]                               | 1    |

| 2nd     | AD1                                 | 2    |

| 3rd     | AD2                                 | 2    |

| 4th     | AD3                                 | 2    |

| 5th     | X                                   | 3    |

| Action  | N byte read out until #CS goes high | 4    |

## Note:

- The 1<sup>st</sup> command 0B[H] is a Read command

AD1 to AD3 are address input data

X is a dummy cycle

Data output

Details of Command are shown as follows.

| 1-byte command | code |     |     |     |     |     |     |     |

|----------------|------|-----|-----|-----|-----|-----|-----|-----|

| FAST-READ:     | 0    | 0   | 0   | 0   | 1   | 0   | 1   | 1   |

| 3-byte address |      |     |     |     |     |     |     |     |

| AD1:           | Χ    | Χ   | Χ   | A20 | A19 | A18 | A17 | A16 |

| AD2:           | A15  | A14 | A13 | A12 | A11 | A10 | A9  | A8  |

| AD3:           | A7   | A6  | A5  | A4  | А3  | A2  | A1  | A0  |

## Note:

X: Dummy bit

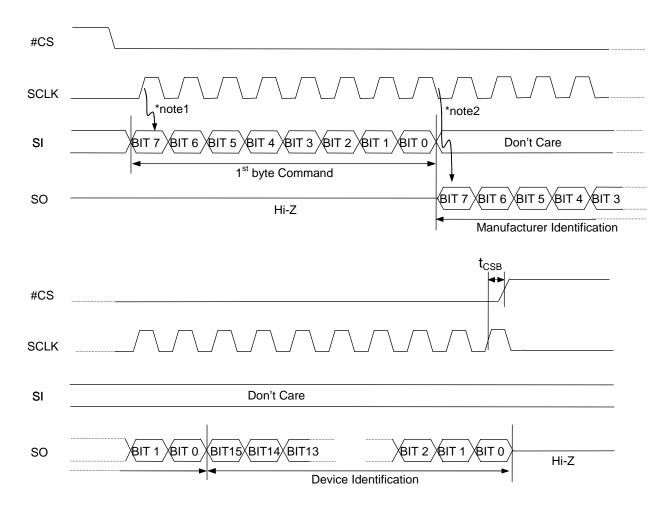

## READ IDENTIFICATION COMMAND DEFINITION

| Command         | Read Array (byte) | Note |

|-----------------|-------------------|------|

| 1 <sup>st</sup> | 9F[H]             | 1    |

| Action          | 3 byte read out   | 2    |

- The 1<sup>st</sup> command 9F[H] is a Read Identification command

Identification output

Details of Command are shown as follows.

| 1-byte command | code |   |   |   |   |   |   |   |

|----------------|------|---|---|---|---|---|---|---|

| RDID           | 1    | 0 | 0 | 1 | 1 | 1 | 1 | 1 |

## **IDENTIFICATION DEFINITION**

| NA                          | Device Identification |          |  |  |

|-----------------------------|-----------------------|----------|--|--|

| Manufacturer Identification | Type                  | Capacity |  |  |

| AE[H]                       | 41[H]                 | 13[H]    |  |  |

## **DEVICE OPERATION**

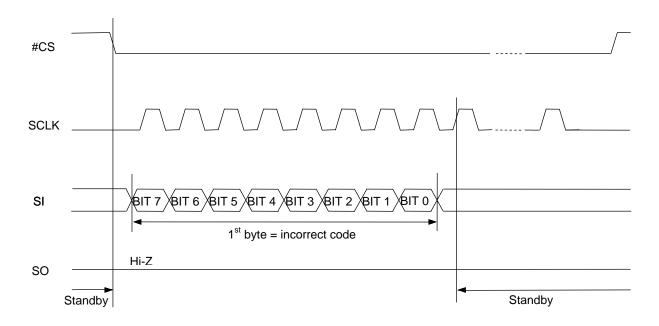

- 1. Command "03h" or "0Bh" makes this LSI become and keep active mode until next #CS High.

- 2. Incorrect command makes this LSI become and keep standby mode until next #CS Low. In standby mode, SO pin is High-Z.

- 3. At Power-up, the device must not be selected (that is #CS must follow the voltage applied on Vcc) until Vcc reaches the operating value.

#### COMMAND DESCRIPTION

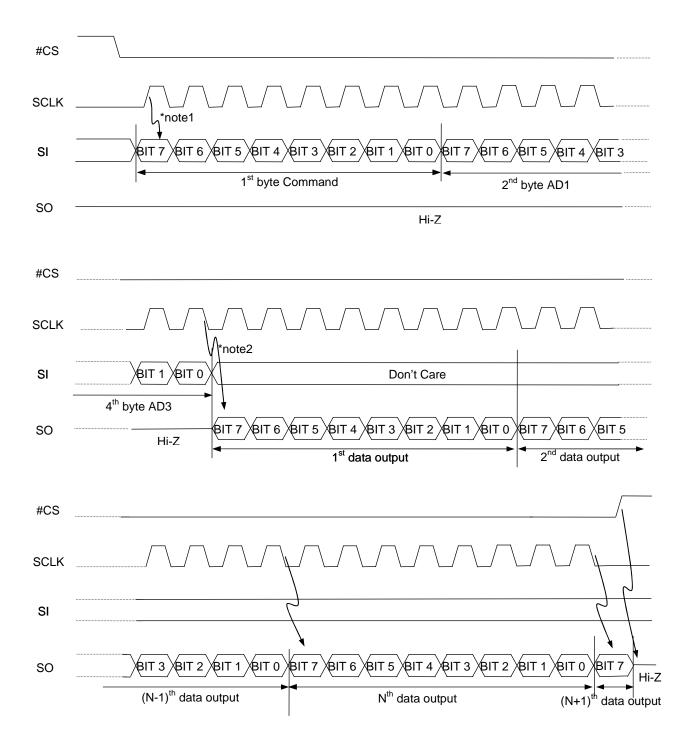

#### 1. Read Array

This command consists of the 4-byte code. The  $1^{st}$  code is a command which decides if the device becomes standby or active mode. The  $1^{st}$  code "03h" activates the device. The  $2^{nd}$  code to the  $4^{th}$  code are address.

#### 2. Fast-Read Array

This command consists of the 5-byte code. The 1<sup>st</sup> code is a command which decides if the device becomes standby or active mode. The 1<sup>st</sup> code "0Bh" activates the device. The 2<sup>nd</sup> code to the 4<sup>th</sup> code are address. The 5<sup>th</sup> code is a dummy cycle.

#### 3. Read Identification Array

This command consists of the 1-byte code. The 1<sup>st</sup> code is a command which decides if the device becomes standby or active mode. The 1<sup>st</sup> code "9Fh" activates the device.

#### 4. Standby

When #CS is high, the device is put in standby mode at the next rising edge of SCLK. Maximum standby current is 50uA. When the above-mentioned 1<sup>st</sup> code is incorrect command, the device is put in standby mode at the next rising edge of SCLK.

#### **DATA SEQUENCE**

The data is serially sent out through SO pin, synchronized with the falling edge of SCLK. Meanwhile input data is also serially read in through SI pin, synchronized with the rising edge of SCLK. The bit sequence for both input and output data are bit7 (MSB) first, bit6, bit5, ..., and bit0(LSB).

#### ADDRESS SEQUENCE

The address assignment is described at the COMMAND DEFINITION on page 2 or 3.

## ABSOLUTE MAXIMUM RATINGS

| Parameter                     | Symbol          | Condition                   | Value                        | Unit |

|-------------------------------|-----------------|-----------------------------|------------------------------|------|

| Storage temperature           | Tstg            | _                           | -55 to 125                   | °C   |

| Input voltage                 | VI              |                             | -0.5 to V <sub>CC</sub> +0.5 | V    |

| Output voltage                | Vo              | relative to V <sub>SS</sub> | -0.5 to V <sub>CC</sub> +0.5 | V    |

| Power supply voltage          | V <sub>CC</sub> |                             | –0.5 to 5                    | V    |

| Power dissipation per package | P <sub>D</sub>  | Ta = 25°C                   | 1.0                          | W    |

| Output short circuit current  | los             | _                           | 10                           | mA   |

## RECOMMENDED OPERATING CONDITIONS

$(Ta = 0 \text{ to } 70^{\circ}C)$

| Parameter                            | Symbol          | Condition                                | Min.   | Тур. | Max.                  | Unit |

|--------------------------------------|-----------------|------------------------------------------|--------|------|-----------------------|------|

| Operating temperature under bias     | Та              |                                          | 0      | ı    | 70                    | °C   |

| V <sub>CC</sub> power supply voltage | V <sub>CC</sub> | $V_{CC} = 3.0 \text{ to } 3.6 \text{ V}$ | 3.0    | 1    | 3.6                   | V    |

| Input "H" level                      | V <sub>IH</sub> |                                          | 2.4    | _    | V <sub>CC</sub> +0.5* | V    |

| Input "L" level                      | V <sub>IL</sub> |                                          | -0.5** |      | 0.6                   | V    |

## Voltage is relative to Vss.

- \* : Vcc+1.5V(Max.) when pulse width of overshoot is less than 10ns.

- \*\*: -1.5V(Min.) when pulse width of undershoot is less than 10ns.

## PIN CAPACITANCE

$(V_{CC} = 3.3 \text{ V}, \text{ Ta} = 25^{\circ}\text{C}, \text{ f} = 1 \text{ MHz})$

| Parameter | Symbol           | Condition   | Min. | Тур. | Max. | Unit |

|-----------|------------------|-------------|------|------|------|------|

| Input     | C <sub>IN1</sub> | $V_I = 0 V$ | _    | _    | 10   |      |

| Output    | C <sub>OUT</sub> | $V_O = 0 V$ | _    | _    | 10   | pF   |

| DC        | C <sub>DC</sub>  | $V_I = 0 V$ | _    | _    | 200  |      |

## **ELECTRICAL CHARACTERISTICS**

#### DC CHARACTERISTICS

$(V_{CC} = 3.3 \text{ V} \pm 0.3 \text{ V}, \text{Ta} = 0 \text{ to } 70^{\circ}\text{C})$

|                                                  |                   |                                             |        | VCC - 0.0 V | ± 0.0 v, ru - | 0 10 10 0) |

|--------------------------------------------------|-------------------|---------------------------------------------|--------|-------------|---------------|------------|

| Parameter                                        | Symbol            | Condition                                   | Min.   | Тур.        | Max.          | Unit       |

| Input leakage current                            | Iμ                | $V_I = 0$ to $V_{CC}$                       | _      | _           | 10            | μΑ         |

| Output leakage current                           | I <sub>LO</sub>   | $V_O = 0$ to $V_{CC}$                       |        | _           | 10            | μΑ         |

| V <sub>CC</sub> power supply current             | I <sub>ccsc</sub> | #CS = V <sub>CC</sub>                       |        | _           | 50            | μΑ         |

| (Standby)                                        | I <sub>CCST</sub> | #CS = V <sub>IH</sub>                       | _      | _           | 1             | mA         |

| V <sub>CC</sub> power supply current (Read)      | I <sub>CC1</sub>  | #CS = V <sub>IL</sub><br>f=20MHz<br>SO=open | _      | _           | 20            | mA         |

| V <sub>CC</sub> power supply current (Fast-Read) | I <sub>CC1F</sub> | #CS = V <sub>IL</sub><br>f=33MHz<br>SO=open | _      | _           | 25            | mA         |

| Input "H" level                                  | V <sub>IH</sub>   | _                                           | 2.4    | _           | Vcc+0.5*      | V          |

| Input "L" level                                  | V <sub>IL</sub>   | _                                           | -0.5** | _           | 0.6           | V          |

| Output "H" level                                 | V <sub>OH</sub>   | I <sub>OH</sub> = -100 μA                   | 2.4    | _           | _             | V          |

| Output "L" level                                 | V <sub>OL</sub>   | I <sub>OL</sub> = 500 μA                    | _      | _           | 0.4           | V          |

## Voltage is relative to Vss.

<sup>\* :</sup> Vcc+1.5V(Max.) when pulse width of overshoot is less than 10ns.

<sup>\*\*: -1.5</sup>V(Min.) when pulse width of undershoot is less than 10ns.

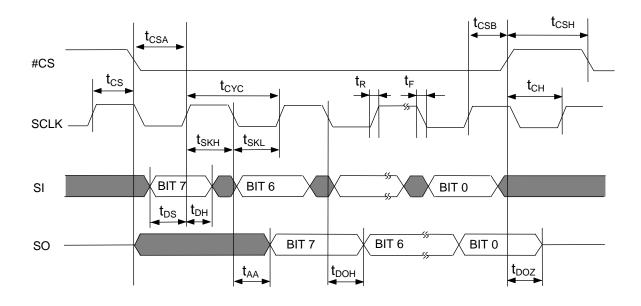

## **AC CHARACTERISTICS**

#### **FAST-READ**

$(V_{CC} = 3.3 \text{ V} \pm 0.3 \text{ V}, \text{Ta} = 0 \text{ to } 70^{\circ}\text{C})$

| Parameter              | Symbol           | Condition | Min. | Max. | Unit |

|------------------------|------------------|-----------|------|------|------|

| Clock frequency        | tsclk            | _         | _    | 33   | MHz  |

| Clock high time        | t <sub>SKH</sub> | _         | 14   | _    | ns   |

| Clock low time         | t <sub>SKL</sub> | _         | 14   | _    | ns   |

| Input signal Rise time | t <sub>R</sub>   | _         | _    | 3    | ns   |

| Input signal Fall time | t <sub>F</sub>   |           |      | 3    | ns   |

| #CS lead clock time    | t <sub>CSA</sub> |           | 10   | _    | ns   |

| #CS setup time         | t <sub>CS</sub>  | _         | 5    | _    | ns   |

| #CS lag clock time     | t <sub>CSB</sub> |           | 5    | _    | ns   |

| #CS hold time          | t <sub>CH</sub>  |           | 5    | _    | ns   |

| #CS high time          | tcsH             |           | 80   | _    | ns   |

| SI setup time          | t <sub>DS</sub>  | _         | 2    | _    | ns   |

| SI hold time           | t <sub>DH</sub>  |           | 10   | _    | ns   |

| Access time            | t <sub>AA</sub>  |           |      | 14   | ns   |

| SO hold time           | t <sub>DOH</sub> |           | 0    | _    | ns   |

| SO floating time       | t <sub>DOZ</sub> |           |      | 15   | ns   |

## READ

$(V_{CC} = 3.3 \text{ V} \pm 0.3 \text{ V}, \text{Ta} = 0 \text{ to } 70^{\circ}\text{C})$

|                        | T                 |           | (VCC = 3.3 V ± 0.3 V, TA = 0 to 70 C) |      |      |

|------------------------|-------------------|-----------|---------------------------------------|------|------|

| Parameter              | Symbol            | Condition | Min.                                  | Max. | Unit |

| Clock frequency        | t <sub>SCLK</sub> | _         | _                                     | 20   | MHz  |

| Clock high time        | tskh              | _         | 20                                    | _    | ns   |

| Clock low time         | t <sub>SKL</sub>  | _         | 20                                    | _    | ns   |

| Input signal Rise time | t <sub>R</sub>    | _         | _                                     | 3    | ns   |

| Input signal Fall time | t <sub>F</sub>    | _         | _                                     | 3    | ns   |

| #CS lead clock time    | t <sub>CSA</sub>  | _         | 10                                    | _    | ns   |

| #CS setup time         | t <sub>CS</sub>   | _         | 5                                     | _    | ns   |

| #CS lag clock time     | t <sub>CSB</sub>  | _         | 5                                     | _    | ns   |

| #CS hold time          | t <sub>CH</sub>   | _         | 5                                     | _    | ns   |

| #CS high time          | t <sub>CSH</sub>  | _         | 80                                    | _    | ns   |

| SI setup time          | t <sub>DS</sub>   | _         | 2                                     | _    | ns   |

| SI hold time           | t <sub>DH</sub>   | _         | 10                                    | _    | ns   |

| Access time            | t <sub>AA</sub>   | _         | _                                     | 14   | ns   |

| SO hold time           | t <sub>DOH</sub>  | _         | 0                                     |      | ns   |

| SO floating time       | t <sub>DOZ</sub>  | _         | _                                     | 15   | ns   |

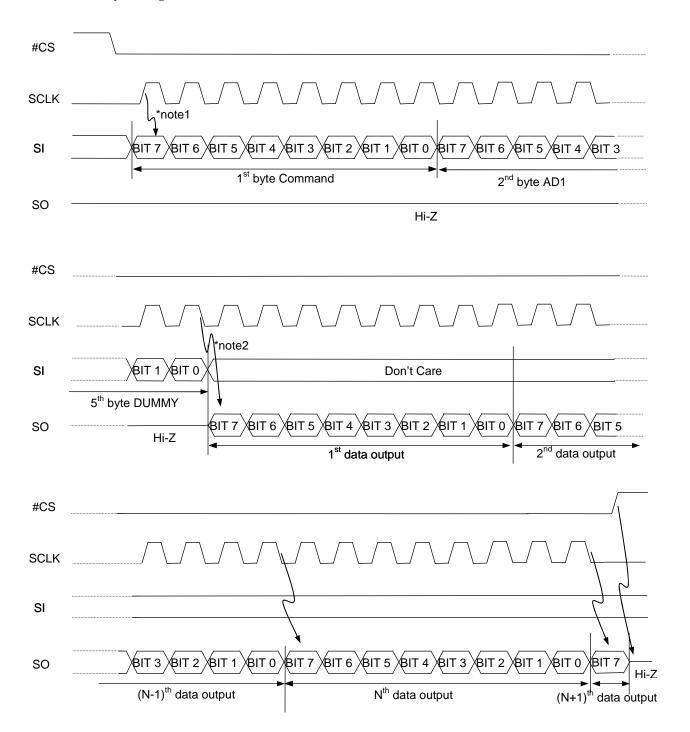

## TIMING CHART (READ CYCLE)

## **Serial Data Input/Output Timing**

## **Standby Timing**

Incorrect command makes this LSI become and keep standby mode until next #CS rising edge. In standby mode, SO pin is High-Z.

## **Read Array Timing Waveform**

#### Note:

- 1. Input data are latched at SCLK-rising edge.

- 2. Data-output starts at SCLK-falling edge in bit0 of the 4<sup>th</sup> byte.

#### **Fast Read Array Timing Waveform**

## Note:

- 1. Input data are latched at SCLK-rising edge.

- 2. Data-output starts at SCLK-falling edge in bit0 of the 5th byte.

## **Read Identification Timing Waveform**

#### Note:

- 1. Input data are latched at SCLK-rising edge.

- 2. Data-output starts at SCLK-falling edge in bit0 of the 1st byte.

#### PACKAGE DIMENSIONS

## Notes for Mounting the Surface Mount Type Package

The surface mount type packages are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact ROHM's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

## **REVISION HISTORY**

| Document<br>No.     | Date          | Page                |                    |                                                                                                                                                                                                                                                   |  |

|---------------------|---------------|---------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                     |               | Previous<br>Edition | Current<br>Edition | Description                                                                                                                                                                                                                                       |  |

| FEDR27V1641L-02-01  | Oct. 28, 2005 | ı                   | ı                  | Final edition 1                                                                                                                                                                                                                                   |  |

| FEDR27V1641L-02-02  | Oct. 31, 2006 | 1, 7, 8             | 1, 7, 8            | serial clock (FAST-READ) 33MHz> 30MHz                                                                                                                                                                                                             |  |

|                     |               | 1                   | 1                  | Don't care (H or L or Open)> Don't care (0v - Vcc)                                                                                                                                                                                                |  |

|                     |               | 5                   | 5                  | device operatioN added 3.                                                                                                                                                                                                                         |  |

|                     |               | 6                   | 6                  | Pin Capacitance C <sub>IN1</sub> Max 12pF> 10pF<br>C <sub>OUT</sub> Max 12pF> 10pF                                                                                                                                                                |  |

|                     |               | 8                   | 8                  | FAST-READ  t <sub>SKH</sub> Min. 12ns> 14ns  t <sub>SKL</sub> Min. 12ns> 14ns  FAST-READ & READ  t <sub>R</sub> Min. 0.1 V/ns> Max. 3ns  t <sub>F</sub> Min. 0.1 V/ns> Max. 3ns  t <sub>AA</sub> Max. 15ns> 14ns  t <sub>DOZ</sub> Max. 8ns> 15ns |  |

| FEDR27V1641L-02-03  | Mar. 16, 2007 | 2                   | 2                  | 3-byte address (0 to 3FFF[H])> 3-byte address                                                                                                                                                                                                     |  |

|                     |               | 3                   | 3                  | 3-byte address (0 to 3FFF[H])> 3-byte address                                                                                                                                                                                                     |  |

|                     |               | 13                  | 13                 | Replaced package diagram                                                                                                                                                                                                                          |  |

| FEDR27V1641L-002-03 | Oct. 1, 2008  | -                   | -                  | Changed company logo and name to OKI SEMICONDUCTOR                                                                                                                                                                                                |  |

| FEDR27V1641L-002-04 | Apr. 1, 2009  | 1, 7, 8             | 1, 7, 8            | serial clock (FAST-READ) 30MHz> 33MHz                                                                                                                                                                                                             |  |

#### **NOTICE**

No copying or reproduction of this document, in part or in whole, is permitted without the consent of LAPIS Semiconductor Co., Ltd.

The content specified herein is subject to change for improvement without notice.

The content specified herein is for the purpose of introducing LAPIS Semiconductor's products (hereinafter "Products"). If you wish to use any such Product, please be sure to refer to the specifications, which can be obtained from LAPIS Semiconductor upon request.

Examples of application circuits, circuit constants and any other information contained herein illustrate the standard usage and operations of the Products. The peripheral conditions must be taken into account when designing circuits for mass production.

Great care was taken in ensuring the accuracy of the information specified in this document. However, should you incur any damage arising from any inaccuracy or misprint of such information, LAPIS Semiconductor shall bear no responsibility for such damage.

The technical information specified herein is intended only to show the typical functions of and examples of application circuits for the Products. LAPIS Semiconductor does not grant you, explicitly or implicitly, any license to use or exercise intellectual property or other rights held by LAPIS Semiconductor and other parties. LAPIS Semiconductor shall bear no responsibility whatsoever for any dispute arising from the use of such technical information.

The Products specified in this document are intended to be used with general-use electronic equipment or devices (such as audio visual equipment, office-automation equipment, communication devices, electronic appliances and amusement devices).

The Products specified in this document are not designed to be radiation tolerant.

While LAPIS Semiconductor always makes efforts to enhance the quality and reliability of its Products, a Product may fail or malfunction for a variety of reasons.

Please be sure to implement in your equipment using the Products safety measures to guard against the possibility of physical injury, fire or any other damage caused in the event of the failure of any Product, such as derating, redundancy, fire control and fail-safe designs. LAPIS Semiconductor shall bear no responsibility whatsoever for your use of any Product outside of the prescribed scope or not in accordance with the instruction manual.

The Products are not designed or manufactured to be used with any equipment, device or system which requires an extremely high level of reliability the failure or malfunction of which may result in a direct threat to human life or create a risk of human injury (such as a medical instrument, transportation equipment, aerospace machinery, nuclear-reactor controller, fuel-controller or other safety device). LAPIS Semiconductor shall bear no responsibility in any way for use of any of the Products for the above special purposes. If a Product is intended to be used for any such special purpose, please contact a ROHM sales representative before purchasing.

If you intend to export or ship overseas any Product or technology specified herein that may be controlled under the Foreign Exchange and the Foreign Trade Law, you will be required to obtain a license or permit under the Law.

Copyright 2009 - 2011 LAPIS Semiconductor Co., Ltd.