# 4-/8-Channel Wideband Video Multiplexers

## **Features**

- Wide Bandwidth: 500 MHz

- Very Low Crosstalk: −97 dB @ 5 MHz

- On-Board TTL-Compatible Latches with Readback

- Optional Negative Supply

- Low r<sub>DS(on)</sub>: 45 Ω

## **Benefits**

- Improved System Bandwidth

- Improved Channel Off-Isolation

- Simplified Logic Interfacing

- Allows Bipolar Signal Swings

- Reduced Insertion Loss

- Allows Differential Signal Switching

## **Applications**

- Wideband Signal Routing and Multiplexing

- Video Switchers

- ATE Systems

- Infrared Imaging

## **Description**

The DG534 is a digitally selectable 4-channel or dual 2-channel multiplexer. The DG538 is an 8-channel or dual 4-channel multiplexer. On-chip TTL-compatible address decoding logic and latches with data readback are included to simplify the interface to a microprocessor data bus. The low on-resistance and low capacitance of the these devices make them ideal for wideband data multiplexing and video and audio signal routing in channel selectors and crosspoint arrays. An optional negative supply pin allows the handling of bipolar signals without dc biasing.

The DG534/DG538 are built on a D/CMOS process that combines n-channel DMOS switching FETs with low-power CMOS control logic, drivers and latches. The low-capacitance DMOS FETs are in a "T" configuration to achieve extremely high levels of off isolation. Crosstalk is reduced to -97 dB at 5 MHz by including a ground line between each adjacent signal path.

The DG534A/DG538A are recommended for new designs.

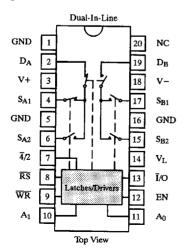

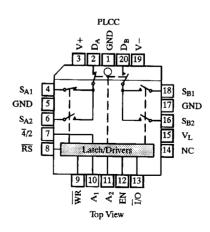

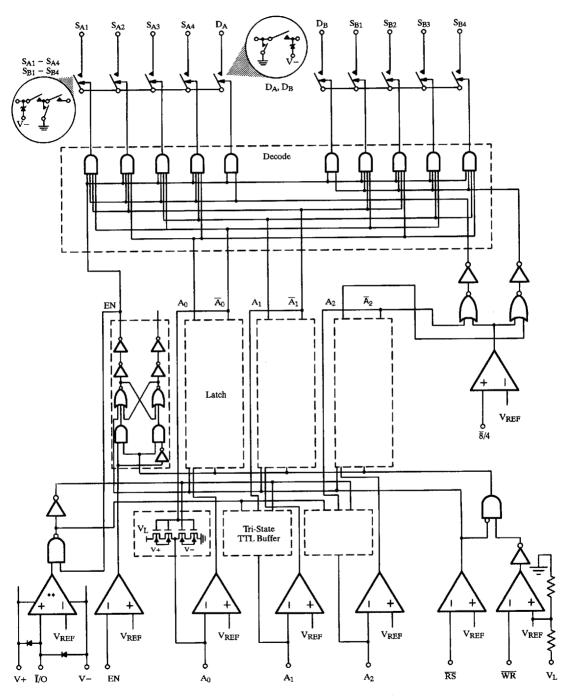

# **Functional Block Diagrams and Pin Configurations**

## DG534DJ

### DG534DN

# Not Recommended for New Designs

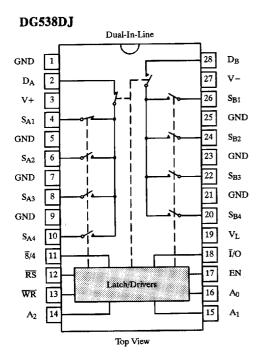

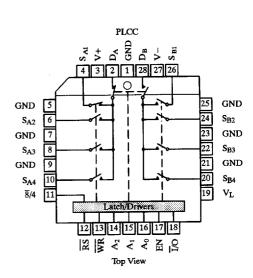

# Functional Block Diagrams and Pin Configurations (Cont'd)

## DG538DN

# **Truth Tables and Ordering Information**

Ordering Information - DG534

| 31g          |                    |             |  |  |  |  |  |

|--------------|--------------------|-------------|--|--|--|--|--|

| Temp Range   | Package            | Part Number |  |  |  |  |  |

| 40 . 0505    | 20-Pin Plastic DIP | DG534DJ     |  |  |  |  |  |

| -40 to 85°C  | 20-Pin PLCC        | DG534DN     |  |  |  |  |  |

| 55. 10500    | 20-Pin Sidebraze   | DG534AP     |  |  |  |  |  |

| −55 to 125°C | 20-Fin Sidebraze   | DG534AP/883 |  |  |  |  |  |

Truth Table - DG534

| 1000 |                |                |    |    |    |                                         |                 |                     |             |  |

|------|----------------|----------------|----|----|----|-----------------------------------------|-----------------|---------------------|-------------|--|

| ī/O  | A <sub>1</sub> | A <sub>0</sub> | EN | WR | RS | 4/2ª                                    |                 | On Swi              | tch         |  |

| х    | х              | х              | х  | 5  | 1  | 1                                       | Main            | tains previous s    | tate        |  |

| x    | Х              | X              | Х  | X  | 0  | X                                       | None            | (latches cleared    | i)          |  |

| х    | Х              | X              | 0  | 0  | 1  | X                                       | None            |                     |             |  |

| 0    | 0              | 0              | 1  | 0  | 1  | 0                                       | S <sub>A1</sub> | May be              |             |  |

| 0    | 0              | 1              | 1  | 0  | 1  | 0                                       | S <sub>A2</sub> |                     | Latches     |  |

| 0    | 1              | 0              | 1  | 0  | 1  | 0                                       | S <sub>B1</sub> |                     | Transparent |  |

| 0    | 1              | 1              | 1  | 0  | 1  | 0                                       | S <sub>B2</sub> | externany           |             |  |

| 0    | Х              | 0              | 1  | 0  | 1  | 1                                       | S <sub>A1</sub> | and S <sub>B1</sub> | ]           |  |

| 0    | X              | 1              | 1  | 0  | 1  | 1 1 S <sub>A2</sub> and S <sub>B2</sub> |                 |                     |             |  |

| 1    |                | Note l         | ,  | 1  | 1  | Note c                                  |                 |                     |             |  |

Logic "0" =  $V_{AL} \le 0.8 \text{ V}$ Logic "1" =  $V_{AH} \ge 2 \text{ V}$

X = Don't Care

### Notes:

- Connect D<sub>A</sub> and D<sub>B</sub> together externally for single-ended operation.

- With I/O high, An pin becomes output and reflects latch contents. See timing diagrams for more detail.

- c. 4/2 can be either "1" or "0" but should not change during these operations.

# Truth Tables and Ordering Information (Cont'd)

Ordering Information - DG538

| Temp Range   | Package            | Part Number |

|--------------|--------------------|-------------|

| −40 to 85°C  | 28-Pin Plastic DIP | DG538DJ     |

| -40 10 65 C  | 28-Pin PLCC        | DG538DN     |

| −55 to 125°C | 28-Pin Sidebraze   | DG538AP     |

| 33 10 123 C  | 20-1 in Sideoraze  | DG538AP/883 |

Truth Table - DG538

| Ĩ/O | A <sub>2</sub> | A <sub>1</sub> | $\mathbf{A}_0$ | EN | WR | RS | 8/4ª   |                   | On Swi                               | tch                    |  |  |  |

|-----|----------------|----------------|----------------|----|----|----|--------|-------------------|--------------------------------------|------------------------|--|--|--|

| _X  | X              | х              | х              | х  | 5  | 1  | 1      |                   | tains previous                       |                        |  |  |  |

| X   | X              | Х              | X              | X  | X  | 0  | Х      | None              | (latches cleare                      | ed)                    |  |  |  |

| Х   | X              | X              | X              | 0  | 0  | 1  | Х      | None              | :                                    |                        |  |  |  |

| 0   | 0              | 0              | 0              | 1  | 0  | 1  | 0      | S <sub>A1</sub>   |                                      | †                      |  |  |  |

| 0   | 0              | 0              | 1              | 1  | 0  | 1  | 0      | S <sub>A2</sub>   |                                      |                        |  |  |  |

| 0   | 0              | 1              | 0              | 1  | 0  | 1  | 0      | S <sub>A3</sub>   | D <sub>A</sub> and D <sub>B</sub>    |                        |  |  |  |

| 0   | 0              | 1              | 1              | 1  | 0  | 1  | 0      | S <sub>A4</sub>   | should be                            |                        |  |  |  |

| 0   | 1              | 0              | 0              | 1  | 0  | 1  | 0      | S <sub>B1</sub>   | should be<br>connected<br>externally |                        |  |  |  |

| 0   | 1              | 0              | 1              | 1  | 0  | 1  | 0      | S <sub>B2</sub>   | externally                           | Latches<br>Transparent |  |  |  |

| 0   | 1              | 1              | 0              | 1  | 0  | 1  | 0      | S <sub>B3</sub>   | 1                                    | ranoparont             |  |  |  |

| 0   | 1              | 1              | 1              | 1  | 0  | 1  | 0      | S <sub>B4</sub>   | 1                                    | l                      |  |  |  |

| 0   | X              | 0              | 0              | 1  | 0  | 1  | 1      | S <sub>A1</sub> a | nd S <sub>B1</sub>                   | 1                      |  |  |  |

| 0   | X              | 0              | 1              | 1  | 0  | 1  | 1      | S <sub>A2</sub> a | nd S <sub>B2</sub>                   | 1                      |  |  |  |

| 0   | X              | 1              | 0              | 1  | 0  | 1  | 1      | S <sub>A3</sub> a | nd S <sub>B3</sub>                   | 1                      |  |  |  |

| 0   | X              | 1              | 1              | 1  | 0  | 1  | 1      | S <sub>A4</sub> a | nd S <sub>B4</sub>                   |                        |  |  |  |

| 1   |                | Not            | e b            |    | 1  | 1  | Note c |                   |                                      | -                      |  |  |  |

Logic "0" =  $V_{AL} \le 0.8 \text{ V}$ Logic "1" =  $V_{AH} \ge 2 \text{ V}$ X = Don't Care

#### Notes:

- a. Connect DA and DB together externally for single-ended operation.

- With I/O high, An pin becomes output and reflects latch contents. See timing diagrams for more detail.

- c.  $\frac{8}{4}$  can be either "1" or "0" but should not change during these operations.

# **Absolute Maximum Ratings**

| V+ to GND0.3 V to +21 V                           |

|---------------------------------------------------|

| V+ to V0.3 V to +21 V                             |

| V- to GND                                         |

| $V_L \dots 0 V \text{ to } (V+) + 0.3 V$          |

| Digital Inputs $(V-)$ -0.3 V to $(V+)$ + 0.3 V    |

| or 20 mA, whichever occurs first                  |

| $V_{S}, V_{D}$ $(V-)$ -0.3 $V$ to $(V-)$ + 14 $V$ |

| or 20 mA, whichever occurs first                  |

| Current (any terminal) Continuous 20 mA           |

| Current(S or D) Pulsed I ms 10% Duty 40 mA        |

| Storage Temperature     | (A Suffix)65 to 150°C<br>(D Suffix)65 to 125°C |

|-------------------------|------------------------------------------------|

| Power Dissipation (Pack | rage) <sup>a</sup>                             |

| Plastic DIPb            | 625 mW                                         |

| PLCC <sup>c</sup>       | 450 mW                                         |

| Sidebrazed              | 1200 mW                                        |

### Notes:

- a. All leads soldered or welded to PC board.

- b. Derate 8.3 mW/°C above 75°C.

- c. Derate 6 mW/°C above 75°C.

- d. Derate 16 mW/°C above 75°C.

# **DG534/538**

# Specifications<sup>a</sup>

|                                      |                       | Test Conditions<br>Unless Otherwise Specified                                                                    |                   |              |                  | A Suffix<br>-55 to 125°C |                  | <b>D Suffix</b><br>-40 to 85°C |            |    |

|--------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------|-------------------|--------------|------------------|--------------------------|------------------|--------------------------------|------------|----|

| Parameter                            | Symbol                | $V + = 15 \text{ V}, V - = -3 \text{ V}, V_{\text{I}}$<br>$\overline{WR} = 0.8 \text{ V}, \overline{RS}, EN = 3$ | Temp <sup>b</sup> | Турс         | Min <sup>d</sup> | Max <sup>d</sup>         | Min <sup>d</sup> | Max <sup>d</sup>               | Unit       |    |

| Analog Switch                        |                       |                                                                                                                  |                   |              |                  |                          |                  |                                | 99.00      |    |

| Analog Signal Range <sup>g</sup>     | V <sub>ANALOG</sub>   | V-=-5V                                                                                                           |                   | Full         |                  | -5                       | 8                | -5                             | 8          | V  |

| Drain-Source<br>On-Resistance        | r <sub>DS(on)</sub>   | $I_S = -10 \text{ mA}, V_S = 0$<br>$V_{AIL} = 0.8 \text{ V}, V_{AIH} = 2$                                        | v<br>v            | Room<br>Full | 45               |                          | 90<br>120        |                                | 90<br>120  | Ω  |

| Resistance Match<br>Between Channels | $\Delta r_{DS(on)}$   | Sequence Each Switch                                                                                             | On                | Room         |                  |                          | 9                |                                | 9          |    |

| Source Off<br>Leakage Current        | I <sub>S(off)</sub>   | $V_S = 8 \text{ V}, V_D = 0 \text{ V}, EN =$                                                                     | 0.8 V             | Room<br>Full | 0.05             | -5<br>-50                | 5<br>50          | -5<br>-50                      | 5<br>50    |    |

| Drain Off<br>Leakage Current         | $I_{D(off)}$          | $V_S = 0 \text{ V}, V_D = 8 \text{ V}, EN =$                                                                     | 0.8 V             | Room<br>Full | 0.1              | -20<br>-500              | 20<br>500        | -20<br>-100                    | 20<br>100  | nA |

| Drain On<br>Leakage Current          | $I_{D(on)}$           | $V_{S} = V_{D} = 8 V$                                                                                            |                   | Room<br>Full | 0.1              | -20<br>-1000             | 20<br>1000       | -20<br>-200                    | 20<br>200  |    |

| Digital Control                      |                       |                                                                                                                  |                   |              |                  |                          |                  |                                |            |    |

| Input Voltage High                   | VAIH                  |                                                                                                                  |                   | Full         |                  | 2                        |                  | 2                              |            | v  |

| Input Voltage Low                    | VAIL                  |                                                                                                                  | Full              |              |                  | 0.8                      |                  | 0.8                            | <u>L'</u>  |    |

| Address Input Current                | I <sub>AI</sub>       | $V_{AI} = 0 \text{ V, or } 2 \text{ V or } 5$                                                                    | Room<br>Full      | -0.1         | -1<br>-10        | 1<br>10                  | -1<br>-10        | 1<br>10                        |            |    |

|                                      | Lo                    | $V_{AO} = 2.7 \text{ V}$                                                                                         | Room              | -300         |                  |                          |                  |                                | μΑ         |    |

| Address Output Current               | $I_{AO}$              | $V_{AO} = 0.4 \text{ V}$                                                                                         | Room              | 300          |                  |                          | <u> </u>         |                                | <u>L</u>   |    |

| Dynamic Characteristic               |                       |                                                                                                                  |                   |              |                  |                          |                  |                                |            |    |

| On State Input                       |                       |                                                                                                                  | PLCC              | Room         | 28               |                          | 40               |                                | 40         |    |

| Capacitanceg                         | $C_{S(on)}$           |                                                                                                                  | DIP               | Room         | 31               |                          | 45               | ļ                              | 45         | 1  |

| Off State Input                      | C <sub>S(off)</sub>   |                                                                                                                  | PLCC              | Room         | 3                |                          | 5                |                                | 4          | pF |

| Capacitance <sup>8</sup>             | ~3(0II)               |                                                                                                                  | DIP               | Room         | 4                | <u> </u>                 |                  | ļ                              | 5          |    |

| Off State Output                     | C <sub>D(off)</sub>   |                                                                                                                  | PLCC              | Room         | 6                |                          | 10               | -                              | 10         |    |

| Capacitanceg                         |                       |                                                                                                                  | DIP               | Room         | 170              | <del>  -</del>           | 300              | <del> </del>                   | 300        | ┼─ |

| Transition Time                      | t <sub>TRANS</sub>    |                                                                                                                  |                   | Full         | 1,0              |                          | 500              |                                | 500        |    |

| Break-Before-Make<br>Interval        | topen                 |                                                                                                                  |                   | Room<br>Full | 80               | 50<br>25                 |                  | 50<br>25                       |            | ns |

| EN, WR Turn On Time                  | ton                   |                                                                                                                  |                   | Room<br>Full | 180              |                          | 300<br>500       |                                | 300<br>500 |    |

| EN, Turn Off Time                    | toff                  |                                                                                                                  |                   | Room<br>Fuli | 95               |                          | 175<br>300       |                                | 175<br>300 |    |

| Charge Injection                     | Qi                    |                                                                                                                  |                   | Room         | -70              |                          |                  |                                |            | pC |

| Chip Disabled Crosstalk <sup>f</sup> | X <sub>TALK(CD)</sub> | $R_L = 75 \Omega, f = 5 MHz$ $EN = 0.8 V$                                                                        | PLCC<br>DIP       | Room<br>Room | -75<br>-65       |                          | _                |                                | <u> </u>   | -  |

|                                      |                       | $R_{IN} = 10 \Omega$ , $R_L = 10 k\Omega$                                                                        | PLCC              | Room         | -97              | †                        |                  | 1                              |            | ┥  |

| _                                    |                       | f = 5  MHz                                                                                                       | DIP               | Room         | -87              | 1                        | 1                | 1                              |            | dB |

| Adjacent Input Crosstalkf            | X <sub>TALK(AI)</sub> | $R_{\rm IN} = 75 \Omega, R_{\rm L} = 75 \Omega$                                                                  | PLCC              | Room         | -80              |                          |                  |                                |            |    |

|                                      |                       | f = 5  MHz                                                                                                       | DIP               | Room         | -70              | <del> </del>             |                  |                                |            |    |

# Specifications<sup>a</sup>

|                                                                 |                         | Test Conditions<br>Unless Otherwise Specified                                                                          |                   |              |                  | A Suffix<br>-55 to 125°C |             | D Suffix<br>-40 to 85°C |      |      |

|-----------------------------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------|-------------------|--------------|------------------|--------------------------|-------------|-------------------------|------|------|

| Parameter                                                       | Symbol                  | V + = 15  V, V - = -3  V, V<br>$\overline{\text{WR}} = 0.8 \text{ V}, \overline{\text{RS}}, \text{EN} = 0.8 \text{ V}$ | Temp <sup>b</sup> | Турс         | Min <sup>d</sup> | Max <sup>d</sup>         | Mind        | Max <sup>d</sup>        | Unit |      |

| Dynamic Characteristic                                          | cs (Cont'd)             |                                                                                                                        |                   |              |                  |                          |             |                         |      |      |

|                                                                 | X <sub>TALK(AH)</sub>   | $R_{IN} = 10 \Omega, R_{L} = 10 k\Omega$                                                                               | PLCC              | Room         | -77              |                          |             |                         |      |      |

| All Hostile Crosstalk                                           |                         | f = 5 MHz                                                                                                              | DIP               | Room         | -72              |                          |             |                         |      |      |

|                                                                 | IALA(AR)                | $R_{\rm IN} = 75 \Omega$ , $R_{\rm L} = 75 \Omega$                                                                     | PLCC              | Room         | -77              |                          |             |                         |      |      |

|                                                                 | ļ                       | f = 5 MHz                                                                                                              | DIP               | Room         | -72              |                          |             |                         |      | dB   |

| Differential Crosstalk                                          | X <sub>TALK(DIFF)</sub> | $R_{IN} = 10 \Omega, R_L = 10$<br>f = 5  MHz                                                                           | kΩ                | Room         | -84              |                          |             |                         | _    |      |

|                                                                 | ATALK(DIFF)             | $R_{IN} = R_L = 75 \Omega$ $f = 5 \text{ MHz}$                                                                         |                   | Room         | -84              |                          |             |                         |      |      |

| Bandwidth                                                       | BW                      | $R_{\rm L} = 50  \Omega$                                                                                               | Room              | 500          |                  |                          |             |                         | MHz  |      |

| Power Supplies                                                  |                         |                                                                                                                        |                   |              | <b>10</b>        |                          |             |                         |      |      |

| Positive Supply Current                                         | I+                      | Any One Channel Selecte                                                                                                | Room<br>Full      | 0.6          |                  | 2<br>5                   |             | 2<br>5                  |      |      |

| Negative Supply Current                                         | I-                      | Address Inputs at GND                                                                                                  | or V+             | Room<br>Full | 0.6              | -1.8<br>-2               |             | -1.8<br>-2              |      | mA.  |

| Functional Check of                                             | V+ to V-                |                                                                                                                        | Full              |              | 10               | 21                       | 10          | 21                      | v    |      |

| Maximum Operating<br>Supply Voltage Range                       | V- to GND               | Functional Test Only                                                                                                   | Full              |              | -5.5             | 0                        | -5.5        | 0                       |      |      |

| Supply Voltage Range                                            | V+ to GND               |                                                                                                                        |                   | Full         |                  | 10                       | 21          | 10                      | 21   | !    |

| Logic Supply Current                                            | $I_L$                   |                                                                                                                        |                   | Full         | 150              |                          | 500         |                         | 500  | μА   |

| Timing                                                          |                         |                                                                                                                        |                   |              |                  |                          |             |                         |      | 1000 |

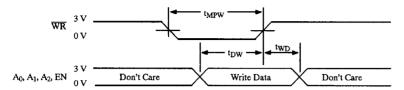

| Reset to Write                                                  | t <sub>RW</sub>         |                                                                                                                        |                   | Full         |                  | 50                       |             | 50                      |      |      |

| WR, RS<br>Minimum Pulse Width                                   | t <sub>MPW</sub>        |                                                                                                                        |                   | Full         |                  | 200                      |             | 200                     |      |      |

| A <sub>0</sub> , A <sub>1</sub> , EN<br>Data Valid to Strobe    | t <sub>DW</sub>         |                                                                                                                        |                   | Full         |                  | 100                      |             | 100                     |      |      |

| A <sub>0</sub> , A <sub>1</sub> , EN<br>Data Valid after Strobe | t <sub>WD</sub>         | See Figure 1                                                                                                           |                   | Fuil         |                  | 50                       |             | 50                      |      | ns   |

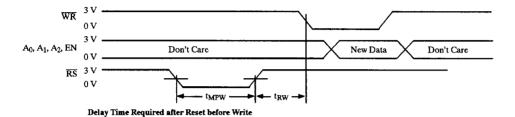

| Address Bus Tri-Statee                                          | t <sub>AZ</sub>         |                                                                                                                        | Room              | 25           |                  |                          |             |                         |      |      |

| Address Bus Output                                              | t <sub>AO</sub>         |                                                                                                                        |                   | Room         | 95               |                          | <del></del> | <del></del>             |      |      |

| Address Bus Input                                               | t <sub>Al</sub>         |                                                                                                                        | <u> </u>          | Room         | 110              |                          |             |                         |      |      |

### Notes:

- Refer to PROCESS OPTION FLOWCHART (Section 5 of the 1994 Data Book or FaxBack number 7103).

- b. Room = 25°C, Full = as determined by the operating temperature suffix.

c. Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

- The algebraic convention whereby the most negative value is a minimum and the most positive a maximum, is used in this data sheet.

- Defined by system bus requirements.

- Each individual pin shown as GND must be grounded.

- Guaranteed by design, not subject to production test.

# DG534/538

# Siliconix A Member of the TEMIC Group

# **Control Circuitry**

\* Decode section includes delay circuitry in AND gating to ensure proper break-before-make operation.

\*\* Typical all digital inputs.

## **Output Timing Requirements**

Writing Data to Device

<sup>\*</sup> Enable must be latched high to read data, otherwise BUS is high Z.  $V-\leq -3$  V required for readback functionality.

Figure 1.

# **Applications**

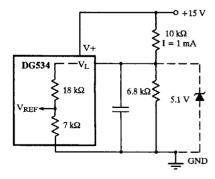

To protect against latchup  $V_L$  must not exceed V+ by more than 0.3 V. This is easily achieved by generating  $V_L$  from V+ using a Zener or a resistor divider network as shown in Figure 2. When an external  $V_L$  is available the alternative

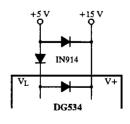

simple protection circuit shown in Figure 3 should be used to prevent triggering the parasitic SCR during power up. The DG53XA does not require these protection diodes.

Figure 2.  $V_L$  Generated from V+

Figure 3. External Diodes Prevent Latchup

**Not Recommended for New Designs**

**8254735 0019248 833**