# 27C011 PAGE-ADDRESSED 1M (8 x 16K x 8) EPROM

- Paged Organization

- Reduced Physical Address

Requirement

- Compatible with 28-Pin JEDEC EPROMs

- Single-Trace Modification for Retrofitting 27128-Based Designs

- No-Hardware-Change Upgrades

- Drop-In 27513 Replacement

- Fast Programming

- Quick-Pulse Programming<sup>TM</sup>

Algorithm

- Programming Time as Fast as

- Automatic Page Clear

- Resets to Page 0 on Power-Up and On Demand with RST Signal

- **■** High-Performance

- 200 ns Access Time

- Low 30 mA Active Power

- Standard EPROM Features

- TTL Compatibility

- Two Line Control

- inteligent Identifier<sup>TM</sup> for Automated Programming

- Smallest Megabit DIP Package

- 28-Pin DIP, Minimal Footprint without Address/Data Multiplexing

The Intel 27C011 is a 5V-only, 1,048,576-bit Erasable Programmable Read Only Memory. It is organized as 8 pages of 16K 8-bit words. Its pin-compatibility with byte-wide JEDEC EPROMs allows retrofitting existing designs to the greater storage capacity afforded by the page-addressed organization. Its 16 K-byte physical address space requirement allows the 27C011 to be utilized in address-constrained system designs.

When a 28-pin DIP socket is configured for 27C64 or 27C128 EPROMs, it is easily retrofitted to the 27C011. By adding a WRITE ENABLE signal to pin 27 (DIP) (unused on 27C64 and 27C128), the 27C011 can be used in an existing design. Thus, the 27C011 enables product enhancements via additional feature sets and firmware-intensive performance upgrades.

The page-addressed organization allows the use of 28-pin DIP packages, the smallest megabit EPROM footprint with applicability to all microprocessors. This provides very efficient circuit board layouts.

The 27C011 is part of a multi-product megabit EPROM family. The other members are standard-addressed byte-wide and word-wide versions, the 27C010 and 27C210, respectively. The 27C010 is organized as 128K x 8 in a 32-pin DIP package which is pin-compatible with JEDEC-standard 28-pin 512K EPROMs. The 27C210 is packaged in a 40-pin DIP with a 64K x 16 organization.

The 27C011 has an automatic page clear circuit for ease of use of its paged organization. The page-select latch is automatically cleared to the lowest order page upon system power-up. The 27C011 also contains many industry-standard features such as two-line output control for simple interfacing and the in

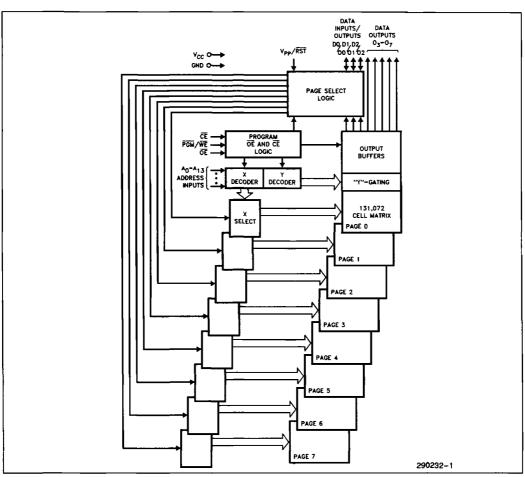

Figure 1. Block Diagram

| 27C513<br>27513                | 27C128<br>27128A |

|--------------------------------|------------------|

| RST                            | V <sub>PP</sub>  |

| A <sub>12</sub>                | A <sub>12</sub>  |

| A <sub>7</sub>                 | A <sub>7</sub>   |

| A <sub>6</sub>                 | A <sub>6</sub>   |

| A <sub>5</sub>                 | A <sub>5</sub>   |

| A <sub>4</sub>                 | A4               |

| A <sub>3</sub>                 | A <sub>3</sub>   |

| A <sub>2</sub>                 | A <sub>2</sub>   |

| A <sub>1</sub>                 | A <sub>1</sub>   |

| A <sub>O</sub>                 | A <sub>0</sub>   |

| $D_0/O_0$                      | 00               |

| D <sub>1</sub> /O <sub>1</sub> | O <sub>1</sub>   |

| O <sub>2</sub>                 | O <sub>2</sub>   |

| GND                            | GND              |

| 27C011                                                                                                                                                                                                                                                                                   |                                     |                                                                      |                                                                                                                                                                                                                   |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| V <sub>PP</sub> /RST D<br>A <sub>12</sub> D<br>A <sub>5</sub> D<br>A <sub>5</sub> D<br>A <sub>4</sub> D<br>A <sub>5</sub> D<br>A <sub>7</sub> D<br>A <sub>9</sub> D<br>D <sub>0</sub> /O <sub>0</sub> D<br>D <sub>1</sub> /O <sub>1</sub> D<br>D <sub>2</sub> /O <sub>2</sub> D<br>GND D | 1 2 3 4 4 5 5 6 6 7 8 9 10 11 12 13 | 27<br>26<br>25<br>24<br>23<br>22<br>21<br>20<br>19<br>18<br>17<br>16 | □ V <sub>CC</sub> □ PGM/WE □ A <sub>13</sub> □ A <sub>8</sub> □ A <sub>9</sub> □ A <sub>11</sub> □ ŌĒ □ A <sub>10</sub> □ CĒ □ O <sub>7</sub> □ O <sub>6</sub> □ O <sub>5</sub> □ O <sub>4</sub> □ O <sub>3</sub> |  |  |  |  |

|                                                                                                                                                                                                                                                                                          |                                     | _                                                                    | 0232-2                                                                                                                                                                                                            |  |  |  |  |

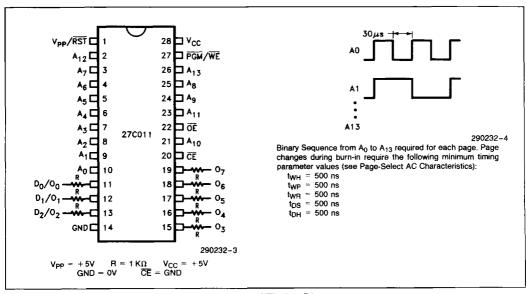

Figure 2. Pin Configuration

| 27C128<br>27128A      | 27C513<br>27513       |

|-----------------------|-----------------------|

| V <sub>CC</sub>       | V <sub>CC</sub><br>WE |

| A <sub>13</sub>       | A <sub>13</sub>       |

| A <sub>8</sub>        | A <sub>8</sub>        |

| A <sub>9</sub>        | A <sub>9</sub>        |

| <u>A<sub>11</sub></u> | _A <sub>11</sub>      |

| ŌĒ                    | OE/V <sub>PP</sub>    |

| <u>A10</u>            | A <sub>10</sub>       |

| CE                    | CE                    |

| 07                    | O <sub>7</sub>        |

| O <sub>6</sub>        | O <sub>6</sub>        |

| O <sub>5</sub>        | O <sub>5</sub>        |

| 04                    | O <sub>4</sub>        |

| Ωn                    | l On                  |

| Din | Names |  |

|-----|-------|--|

| PID | Names |  |

| A <sub>0</sub> -A <sub>13</sub> | Addresses                        |

|---------------------------------|----------------------------------|

| CE                              | Chip Enable                      |

| ŌĒ                              | Output Enable                    |

| WE                              | Page-Select Write Enable         |

| 03-07                           | Outputs                          |

| D <sub>X</sub> /O <sub>X</sub>  | input/Outputs $(X = 0, 1, or 2)$ |

| V <sub>PP</sub> /RST            | V <sub>PP</sub> /Page Reset      |

| NC                              | No Internal Connection           |

| D.U.                            | Don't Use                        |

## EXTENDED TEMPERATURE (EXPRESS) EPROMs

The Intel EXPRESS EPROM family is a series of electrically programmable read only memories which have received additional processing to enhance product characteristics. EXPRESS processing is available for several densities of EPROM, allowing the choice of appropriate memory size to match system applications. EXPRESS EPROM products are available with 168 ±8 hour, 125°C dynamic burn-in using Intel's standard bias configuration. This process exceeds or meets most industry specifications of burn-in. The standard EXPRESS EPROM operating temperature range is 0°C to 70°C. Extended operating temperature range (-40°C to +85°C) EX-PRESS products are available. Like all Intel EPROMs, the EXPRESS EPROM family is inspected to 0.1% electrical AQL. This may allow the user to reduce or eliminate incoming inspection testing.

#### **EXPRESS EPROM PRODUCT FAMILY**

#### PRODUCT DEFINITIONS

| Туре | Operating<br>Temperature | Burn-In<br>125°C (hr) |

|------|--------------------------|-----------------------|

| Q    | 0°C to +70°C             | 168 ±8                |

#### **EXPRESS OPTIONS**

#### 27C011 VERSIONS

| Packaging Options |         |  |  |  |

|-------------------|---------|--|--|--|

| Speed Versions    | Cerdip  |  |  |  |

| -200V10           | Q, T, L |  |  |  |

**Burn-In Bias and Timing Diagrams**

#### **ABSOLUTE MAXIMUM RATINGS\***

| Operating Temperature During Read0°C to +70°C                                             |

|-------------------------------------------------------------------------------------------|

| Temperature Under Bias 10°C to +80°C                                                      |

| Storage Temperature65°C to +125°C                                                         |

| All Input or Output Voltages with Respect to Ground0.6V to +6.5V                          |

| Voltage on A <sub>9</sub> with Respect to Ground0.6V to +13.0V                            |

| $V_{PP}$ Supply Voltage with Respect to Ground During Programming $\dots -0.6V$ to $+14V$ |

| $V_{CC}$ Supply Voltage with Respect to Ground 0.6V to $+7.0V$                            |

NOTICE: This data sheet contains information on products in the sampling and initial production phases of development. The specifications are subject to change without notice.

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

#### **READ OPERATION**

#### DC CHARACTERISTICS TTL and NMOS inputs, 0°C ≤ TA ≤ +70°C, VCC ± 10%

| Symbol           | Parameter                         | Notes | Min                    | Typ(3) | Max                   | Units | Test Condition                                          |

|------------------|-----------------------------------|-------|------------------------|--------|-----------------------|-------|---------------------------------------------------------|

| ILI              | Input Load Current                |       |                        | 0.01   | 1.0                   | μΑ    | V <sub>IN</sub> = 0V to 5.5V                            |

| ILO              | Output Leakage Current            |       |                        |        | ± 10                  | μА    | $V_{OUT} = 0V \text{ to } 5.5V$                         |

| ILRST            | V <sub>PP</sub> /RST Load Current | 9     |                        |        | 500                   | μΑ    | V <sub>PP</sub> /RST ≤ V <sub>CC</sub>                  |

| I <sub>SB</sub>  | V <sub>CC</sub> Current Standby   |       |                        |        | 1.0                   | mA    | CE = V <sub>IH</sub>                                    |

| lcc <sub>1</sub> | V <sub>CC</sub> Current Active    | 5     |                        |        | 30                    | mA    | $\overline{CE} = V_{IL}$<br>f = 5 MHz, $I_{OUT} = 0$ mA |

| I <sub>PP1</sub> | V <sub>PP</sub> Current Read      | 7     |                        |        | 10                    | μΑ    | V <sub>PP</sub> = V <sub>CC</sub>                       |

| VIL              | Input Low Voltage (±10% Supply)   | 1     | -0.5                   |        | 0.8                   | V     |                                                         |

| VIH              | Input High Voltage (±10% Supply)  |       | 2.0                    |        | V <sub>CC</sub> + 0.5 | ٧     | <del></del>                                             |

| VOL              | Output Low Voltage                |       |                        |        | 0.45                  | ٧     | I <sub>OL</sub> = 2.1 mA                                |

| V <sub>OH</sub>  | Output High Voltage               |       | 2.4                    |        |                       | ٧     | $I_{OH} = -400 \mu\text{A}$                             |

| $V_{CLR}$        | Page Latch Clear-V <sub>CC</sub>  |       |                        | 3.5    | 4.0                   | ٧     |                                                         |

| los              | Output Short Circuit Current      | 6     |                        |        | 100                   | mA    |                                                         |

| V <sub>PP</sub>  | V <sub>PP</sub> Read Voltage      | 8     | V <sub>CC</sub> - 0.7V |        | Vcc                   | V     |                                                         |

#### NOTES:

- 1. Minimum DC input voltage is -0.5V. During transitions, the inputs may undershoot to -2.0V for periods less than 20 ns. Maximum DC voltage on output pins is  $V_{CC} + 0.5$ V which may overshoot to  $V_{CC} + 2$ V for periods less than 20 ns.

- 2. Operating temperature is for commercial product defined by this specification. Extended temperature options are available in EXPRESS and Automotive versions.

- 3. Typical limits are at  $V_{CC} = 5V$ ,  $T_A = +25$ °C.

- 4.  $\overrightarrow{CE}$  is  $V_{CC} \pm 0.2V$ . All other inputs can have any value within spec.

- 5. Maximum current value is with outputs O<sub>0</sub> to O<sub>7</sub> unloaded.

- Output shorted for no more than one second. No more than one output shorted at a time. I<sub>OS</sub> is sampled but not 100% tested.

- 7. Maximum active power usage is the sum of  $I_{PP}$  and  $I_{CC}$ . The maximum current value is with no loading on outputs  $O_0$  to  $O_7$ .

- 8. V<sub>PP</sub> may be one diode voltage drop below V<sub>CC</sub>. It may be connected directly to V<sub>CC</sub>. Also, V<sub>CC</sub> must be applied simultaneously or before V<sub>PP</sub> and removed simultaneously or after V<sub>PP</sub>.

- 9. Vpp/RST should be at a TTL VIH level except during programming or during page 0 reset.

#### **READ OPERATION (Continued)**

#### **DC CHARACTERISTICS CMOS Inputs**

| Symbol           | Parameter                           | Notes | Min                  | Typ(3) | Max                  | Units | Test Condition                                             |

|------------------|-------------------------------------|-------|----------------------|--------|----------------------|-------|------------------------------------------------------------|

| l <sub>Ll</sub>  | Input Load Current                  |       |                      | 0.01   | 1.0                  | μΑ    | $V_{IN} = 0V \text{ to } 5.5V$                             |

| lLO              | Output Leakage Current              |       |                      |        | ±10                  | μА    | V <sub>OUT</sub> = 0V to 5.5V                              |

| I <sub>SB</sub>  | V <sub>CC</sub> Current Standby     | 4     | -                    |        | 100                  | μΑ    | CE = V <sub>CC</sub>                                       |

| lcc1             | V <sub>CC</sub> Current Active      | 5     |                      |        | 30                   | mA    | CE = V <sub>IL</sub><br>f = 5 MHz, I <sub>OUT</sub> = 0 mA |

| l <sub>PP1</sub> | V <sub>PP</sub> Current Read        | 7     |                      |        | 10                   | μΑ    | $V_{PP} = V_{CC}$                                          |

| V <sub>IL</sub>  | Input Low Voltage<br>(±10% Supply)  |       | -0.5                 |        | 0.8                  | ٧     |                                                            |

| V <sub>IH</sub>  | Input High Voltage<br>(±10% Supply) |       | 0.7 V <sub>CC</sub>  |        | V <sub>CC</sub> +0.5 | ٧     |                                                            |

| VOL              | Output Low Voltage                  |       |                      |        | 0.4                  | ٧     | I <sub>OL</sub> = 2.1 mA                                   |

| V <sub>OH</sub>  | Output High Voltage                 |       | V <sub>CC</sub> -0.8 |        |                      | ٧     | $I_{OH} = -400 \mu\text{A}$                                |

| los              | Output Short Circuit Current        | 6     |                      |        | 100                  | mA    |                                                            |

#### NOTES:

- 1. Minimum DC input voltage is -0.5V. During transitions, the inputs may undershoot to -2.0V for periods less than 20 ns. Maximum DC voltage on output pins is V<sub>CC</sub> + 0.5V which may overshoot to V<sub>CC</sub> + 2V for periods less than 20 ns.

- 2. Operating temperature is for commercial product defined by this specification. Extended temperature options are available in EXPRESS and Automotive versions.

- 3. Typical limits are at  $V_{CC} = 5V$ ,  $T_A = +25^{\circ}C$ . 4. CE is  $V_{CC} \pm 0.2V$ . All other inputs can have any value within spec.

- 5. Maximum current value is with outputs O<sub>0</sub> to O<sub>7</sub> unloaded.

- 6. Output shorted for no more than one second. No more than one output shorted at a time. IOS is sampled, not 100%

- 7. Maximum active power usage is the sum of IPP and ICC. The maximum current value is with no loading on outputs O0 to

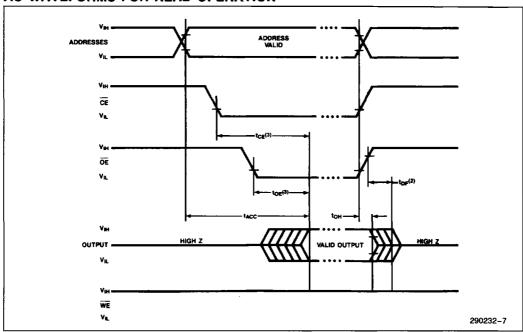

#### AC CHARACTERISTICS(1) O°C ≤ TA ≤ +70°C

| Versions            | V <sub>CC</sub> ± 10%                                            | 27C011 | Harita |       |  |

|---------------------|------------------------------------------------------------------|--------|--------|-------|--|

| Symbol              | Characteristics                                                  | Min    | Max    | Units |  |

| tACC                | Address to Output Delay                                          |        | 200    | ns    |  |

| tCE                 | CE to Output Delay                                               |        | 200    | ns    |  |

| t <sub>OE</sub>     | OE to Output Delay                                               |        | 70     | ns    |  |

| t <sub>DF</sub> (2) | ŌĒ High to Output Float                                          | 0      | 60     | ns    |  |

| t <sub>OH</sub> (2) | Output Hold from Addresses CE or OE,<br>Whichever Occurred First | 0      |        | ns    |  |

- 1. See AC Waveforms for Read Operation for timing measurements.

- 2. Sampled, not 100% tested.

#### **AC CONDITIONS OF TEST**

| Input Rise and Fall Times (10% to 90%) 10 ns |                |  |  |

|----------------------------------------------|----------------|--|--|

| Input Pulse Levels                           | 0.45V to 2.4V  |  |  |

| Input Timing Reference Level                 | .0.8V and 2.0V |  |  |

| Output Timing Reference Level                | .0.8V and 2.0V |  |  |

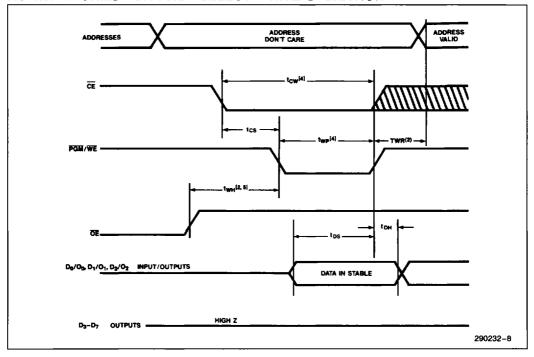

#### PAGE-SELECT WRITE AND PAGE-RESET OPERATION

### AC CHARACTERISTICS $0^{\circ}C \le T_A \le +70^{\circ}C$

| Symbol           | Parameter                      | Lir | nits |       | Test                 |  |

|------------------|--------------------------------|-----|------|-------|----------------------|--|

|                  |                                | Min | Max  | Units | Conditions           |  |

| t <sub>CW</sub>  | CE to End of Write             | 100 |      | ns    | ŌĒ = V <sub>IH</sub> |  |

| t <sub>WP</sub>  | Write Pulse Width              | 50  |      | ns    | ŌĒ = V <sub>IH</sub> |  |

| t <sub>WR</sub>  | Write Recovery Time            | 20  |      | ns    |                      |  |

| t <sub>DS</sub>  | Data Setup Time                | 50  |      | ns    | OE = VIH             |  |

| t <sub>DH</sub>  | Data Hold Time                 | 20  |      | ns    | OE = VIH             |  |

| t <sub>CS</sub>  | CE to Write Setup Time         | 0   |      | ns    | OE = VIH             |  |

| t <sub>WH</sub>  | WE Low from OE High Delay Time | 55  |      | ns    |                      |  |

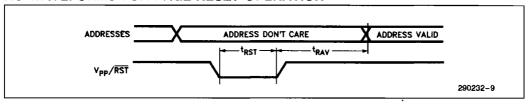

| t <sub>RST</sub> | Reset Low Time                 | 100 |      | ns    |                      |  |

| t <sub>RAV</sub> | Reset to Address Valid         | 150 |      | ns    | -                    |  |

### CAPACITANCE(1) TA = +25°C, f = 1 MHz

| Symbol                | Parameter                        | Typ(1) | Max | Units | Conditions     |

|-----------------------|----------------------------------|--------|-----|-------|----------------|

| C <sub>IN</sub>       | Input Capacitance                | 4      | 8   | pF    | $V_{IN} = 0V$  |

| C <sub>OUT</sub>      | Output Capacitance               | 8      | 12  | pF    | $V_{OUT} = 0V$ |

| C <sub>VPP</sub> /RST | V <sub>PP</sub> /RST Capacitance | 18     | 25  | pF    | $V_{IN} = 0V$  |

<sup>1.</sup> Sampled. Not 100% tested.

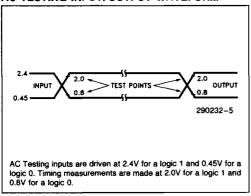

#### AC TESTING INPUT/OUTPUT WAVEFORM

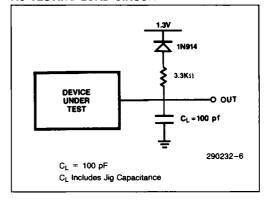

#### **AC TESTING LOAD CIRCUIT**

#### **AC WAVEFORMS FOR READ OPERATION**

#### AC WAVEFORMS FOR PAGE-SELECT WRITE OPERATION

#### AC WAVEFORMS FOR PAGE-RESET OPERATION

- Typical values are for T<sub>A</sub> = +25°C and nominal supply voltages.

This parameter is only sampled and is not 100% tested.

- OE may be delayed up to t<sub>CE</sub>-t<sub>OE</sub> after the falling edge of CE without impact on t<sub>CE</sub>.

Write may be terminated by either CE or WE, providing that the minimum t<sub>CW</sub> requirement is met before bringing WE high or that the minimum two requirement is met before bringing CE high.

- 5. OE must be high during write cycle.

#### **DEVICE OPERATION**

The modes of operation of the 27C011 are listed in Table 1. A single 5V power supply is required in the read mode. All inputs are TTL levels except for VPP and 12V on Ag for inteligent Identifier.

**Table 1. Operating Modes**

| Pins                    | CE              | ŌĒ              | PGM/<br>WE      | A <sub>9</sub>     | A <sub>0</sub>  | V <sub>PP</sub> /RST | V <sub>CC</sub>     | Outputs          | input/<br>Outputs    |

|-------------------------|-----------------|-----------------|-----------------|--------------------|-----------------|----------------------|---------------------|------------------|----------------------|

| Read                    | VIL             | VIL             | V <sub>IH</sub> | χ(1)               | ×               | V <sub>IH</sub>      | 5.0V                | Dout             | D <sub>OUT</sub>     |

| Output Disable          | VIL             | VIH             | V <sub>IH</sub> | Х                  | х               | V <sub>IH</sub>      | 5.0V                | High Z           | High Z               |

| Standby                 | V <sub>IH</sub> | Х               | ×               | Х                  | х               | V <sub>IH</sub>      | 5.0V                | High Z           | High Z               |

| Programming             | VIL             | ViH             | VIL             | Х                  | Х               | V <sub>PP</sub> (3)  | V <sub>CC</sub> (3) | D <sub>IN</sub>  | D <sub>IN</sub>      |

| Verify                  | VIL             | Ϋ <sub>IL</sub> | V <sub>IH</sub> | Х                  | Х               | V <sub>PP</sub> (3)  | V <sub>CC</sub> (3) | D <sub>OUT</sub> | D <sub>OUT</sub>     |

| Program Inhibit         | V <sub>IH</sub> | х               | V <sub>IH</sub> | Х                  | X               | V <sub>PP</sub> (3)  | V <sub>CC</sub> (3) | High Z           | High Z               |

| Page-Select Write       | VIL             | V <sub>IH</sub> | V <sub>IL</sub> | Х                  | Х               | V <sub>IH</sub>      | V <sub>CC</sub> (5) | (Note 7)         | Page D <sub>IN</sub> |

| Page-Reset              | х               | х               | Х               | Х                  | х               | V <sub>iL</sub>      | Vcc                 | (Note 7)         | Х                    |

| inteligent Manufacturer | VIL             | VIL             | V <sub>IH</sub> | V <sub>H</sub> (6) | VIL             | VIH                  | 5.0V                | 89H              | 89H                  |

| Identifier —Device      | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>H</sub> (6) | V <sub>IH</sub> | V <sub>IH</sub>      | 5.0V                | 31H              | 31H                  |

#### NOTES:

- 1. X can be VIH or VIL.

- 2. Addresses are don't care for page selection. See Table 2 for DIN values.

- 3. See Table 3 for V<sub>CC</sub> and V<sub>PP</sub>.

- 4. A1-A8, A10-A13, = VIL.

- 5. Page 0 is automatically selected at power-up (V<sub>CC</sub> < 4.0V).

- 6.  $V_H = 12.0V \pm 0.5\%$ .

- 7. State of outputs depends on state of CE and OE. See Outputs State for Read, Output Disable, and Standby Modes.

#### **Read Mode**

The 27C011 has three control functions, two of which must be logically active in order to obtain data at the outputs. Chip Enable ( $\overline{\text{CE}}$ ) is the power control and should be used for device selection. Output Enable ( $\overline{\text{OE}}$ ) is the output control and should be used to gate data from the output pins, independent of device selection. Assuming that addresses are stable, the address access time ( $t_{ACC}$ ) is equal to the delay from  $\overline{\text{CE}}$  to output ( $t_{CE}$ ). Data is available at the outputs after a delay of  $t_{OE}$  from the falling edge of  $\overline{\text{OE}}$ , assuming that  $\overline{\text{CE}}$  has been low and addresses have been stable for at least  $t_{ACC}$ – $t_{OE}$ .  $\overline{\text{WE}}$  is held high during read operations.

#### Standby Mode

EPROMs can be placed in standby mode which reduces the maximum current of the device by applying a TTL-high signal to the CE input. When in standby mode, the outputs are in a high impedance state, independent of the OE and WE inputs.

#### **Page-Select Write Mode**

The 27C011 is addressed by first selecting one of eight 16 K-byte pages. Individual bytes are then selected by normal random access within the 16 K-byte page using the proper combination of  $A_0-A_{13}$  address inputs. By applying a TTL low signal to the  $\overline{WE}$  input with  $\overline{CE}$  low and  $\overline{OE}$  high, the desired page is latched in according to the combination of  $D_0/O_0$ ,  $D_1/O_1$  and  $D_2/O_2$ . Address inputs are "don't care" during page selection.

Care should be taken in organizing software programs such that the number of page changes is minimized. This allows maximum system performance. Also, the processor's program counter status must be considered when page changes occur in the middle of an opcode sequence. After a page-select write, the program counter will be incremented to the next location (or further in pipelined systems) in the new page relative to that of the page-select write opcode in the previous page.

**Table 2. Page Selection Data**

| input/Output   |                                |                                |                                |  |

|----------------|--------------------------------|--------------------------------|--------------------------------|--|

| Page Selection | D <sub>2</sub> /O <sub>2</sub> | D <sub>1</sub> /O <sub>1</sub> | D <sub>0</sub> /O <sub>0</sub> |  |

| Select Page 0  | V <sub>IL</sub>                | V <sub>IL</sub>                | V <sub>IL</sub>                |  |

| Select Page 1  | Vi∟                            | ViL                            | ViH                            |  |

| Select Page 2  | V <sub>IL</sub>                | ViH                            | ViL                            |  |

| Select Page 3  | V <sub>IL</sub>                | ViH                            | ViH                            |  |

| Select Page 4  | VIH                            | V <sub>IL</sub>                | ViL                            |  |

| Select Page 5  | VIH                            | ViL                            | ViH                            |  |

| Select Page 6  | ViH                            | V <sub>IH</sub>                | V <sub>IL</sub>                |  |

| Select Page 7  | ViH                            | V <sub>IH</sub>                | ViH                            |  |

#### Page Reset

The 27C011 has an automatic page latch clear circuit to ensure consistent page selection during system bootstrapping. The page latch is automatically cleared to page 0 upon power-up. As the  $V_{CC}$  supply voltage ramps up, the page latch is cleared. After  $V_{CC}$  exceeds the 4.0V maximum page latch clear voltage ( $V_{CLR}$ ), the latch clear circuit is disabled. This ensures an adequate safety margin (500 mV of system noise below the worst case -10%  $V_{CC}$  supply condition) against spurious page latch clearing.

The 27C011 also has a page reset pin:  $V_{PP}/\overline{RST}$ . This pin should be tied to an active low reset line. These 27C011s will be reset to page 0 when this line is brought to TTL Low  $(V_{IL})$ .

#### Two Line Control

Because EPROMs are usually used in larger memory arrays, Intel has provided 2 output control lines which accommodate this multiple memory connection. The two control lines for read operation allow for

- a) the lowest possible memory power dissipation, and

- b) complete assurance that output bus contention will not occur.

To use these two control lines most efficiently,  $\overline{CE}$  should be decoded and used as the primary device selecting function, while  $\overline{OE}$  should be made a common connection to all devices in the array and connected to the  $\overline{READ}$  line from the system control bus. This assures that all deselected memory devices are in their low power standby mode and that the output pins are active only when data is desired from a particular memory device.

Similarly,  $\overline{CE}$  deselects other 27C011s or RAMs during page select write operation while  $\overline{WE}$  is in common with other devices in the array.  $\overline{WE}$  is connected to the  $\overline{WRITE}$  system control line.

#### SYSTEM CONSIDERATIONS

The power switching characteristics of EPROMs require careful decoupling of the devices. The supply current,  $I_{CC}$ , has three segments that are of interest to the system designer—the standby current level, the active current level, and the transient current peaks that are produced by the falling and rising edges of Chip Enable. The magnitude of these transient current peaks is dependent on the output capacitive and inductive loading of the device. The as-

sociated transient voltage peaks can be suppressed by complying with Intel's Two-Line Control and by properly selected decoupling capacitors. It is recommended that a 0.1 µF ceramic capacitor be used on every device between V<sub>CC</sub> and GND. This should be a high frequency capacitor of low inherent inductance and should be placed as close to the device as possible. In addition, a 4.7 µF bulk electrolytic capacitor should be used between V<sub>CC</sub> and GND for every eight devices. The bulk capacitor should be located near where the power supply is connected to the array. The purpose of the bulk capacitor is to overcome the voltage droop caused by the inductive effects of PC board traces. This inductive effect should be further minimized through special layout considerations such as larger traces and gridding. In particular, the VSS (Ground) plane should be as stable as possible.

#### PROGRAMMING

Caution: Exceeding 14.0V on V<sub>PP</sub> will permanently damage the 27C011.

Initially, and after each erasure, all bits of the EPROM are in the "1" state. Data is introduced by selectively programming "0s" into the desired bit locations. Although only "0s" will be programmed, both "1s" and "0s" can be present in the data word. The only way to change a "0" to a "1" is by ultraviolet light erasure.

The 27C011 is in the programming mode when the V<sub>PP</sub> input is at its programming voltage and CE is at TTL-low. The data to be programmed is applied 8 bits in parallel to the data output pins. The levels required for the address and data inputs are TTL.

#### Program Inhibit

Programming of multiple 27C011s in parallel with different data is easily accomplished by using the Program Inhibit mode. A high-level CE input inhibits the other 27C011s from being programmed.

Except for  $\overline{CE}$ , all inputs of the parallel 27C011s may be common. A TTL low-level pulse applied to the  $\overline{PGM/WE}$  input with  $V_{PP}$  at its programming voltage will program the selected 27C011.

#### Verify

A verify (read) should be performed on the programmed bits to determine that they have been correctly programmed. The verify is performed with  $\overline{\text{OE}}$  and  $\overline{\text{CE}}$  at  $V_{\text{IL}}$  and  $V_{\text{CC}}$  is at its programming voltage

Data should be verified  $t_{DV}$  after the falling edge of  $\overline{CF}$ .

#### inteligent Identifier™ Mode

The int<sub>e</sub>ligent Identifier Mode allows the reading out of a binary code from an EPROM that will identify its manufacturer and type. This mode is intended for use by programming equipment for the purpose of automatically matching the device to be programmed with its corresponding programming algorithm. This mode is functional in the 25°C  $\pm 5^{\circ}$ C ambient temperature range that is required when programming the device.

To activate this mode, the programming equipment must force 11.5V to 12.5V on address line A9 of the EPROM. Two identifier bytes may then be sequenced from the device outputs by toggling address line A0 from  $V_{IL}$  to  $V_{IH}$ . All other address lines must be held at  $V_{IL}$  during the int<sub>e</sub>ligent Identifier Mode.

Byte 0 (A0 =  $V_{IL}$ ) represents the manufacturer code and byte 1 (A0 =  $V_{IH}$ ) the device identifier code. These two identifier bytes are given in Table 1.

## ERASURE CHARACTERISTICS (FOR CERDIP EPROMs)

The erasure characteristics are such that erasure begins to occur upon exposure to light with wavelengths shorter than approximately 4000 Angstroms (Å). It should be noted that sunlight and certain types of fluorescent lamps have wavelengths in the 3000–4000 Å range. Data show that constant exposure to room level fluorescent lighting could erase the EPROM in approximately 3 years, while it would take approximately 1 week to cause erasure when exposed to direct sunlight. If the device is to be exposed to these types of lighting conditions for extended periods of time, opaque labels should be placed over the window to prevent unintentional erasure.

The recommended erasure procedure is exposure to shortwave ultraviolet light which has a wavelength of 2537 Angstroms (Å). The integrated dose (i.e., UV intensity x exposure time) for erasure should be a minimum of 15 Wsec/cm². The erasure time with this dosage is approximately 15 to 20 minutes using an ultraviolet lamp with a 12000  $\mu$ W/cm² power rating. The EPROM should be placed within 1 inch of the lamp tubes during erasure. The maximum integrated dose an EPROM can be exposed to without damage is 7258 Wsec/cm² (1 week @ 12000  $\mu$ W/cm²). Exposure of the device to high intensity UV light for long periods may cause permanent damage.

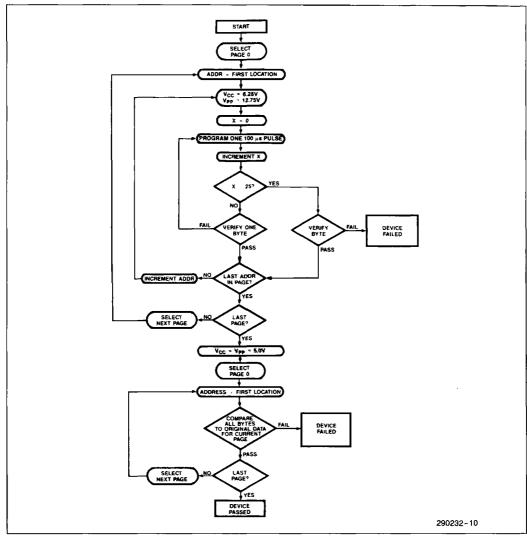

Figure 4. 27C011 Quick-Pulse Programming Flowchart

### **Quick Pulse Programming Algorithm**

Intel's 27C011 EPROM is programmed using the Quick-Pulse Programming algorithm, developed by Intel to substantially reduce the throughput time in the production programming environment. This algorithm allows these devices to be programmed as fast as fourteen seconds, almost a hundred fold improvement over previous algorithms. Actual programming time is a function of the PROM programmer being used.

The Quick-Pulse Programming algorithm uses initial pulses of 100 microseconds followed by a byte veri-

fication to determine when the address byte has been successfully programmed. Up to 25 100  $\mu$ s pulses per byte are provided before a failure is recognized. A flowchart of the Quick-Pulse Programming algorithm is shown in Figure 4.

For the Quick-Pulse Programming algorithm, the entire sequence of programming pulses and byte verifications is performed at  $V_{CC} = 6.25V$  and  $V_{PP}$  at 12.75V. When programming of the EPROM has been completed, all bytes should be compared to the original data with  $V_{CC} = V_{PP} = 5.0V$ .

### DC PROGRAMMING CHARACTERISTICS $T_A = 25^{\circ}C \pm 5^{\circ}C$

#### Table 3

| Combal               | Bananatan                                                 |      | Limits | Test Conditions |                                      |

|----------------------|-----------------------------------------------------------|------|--------|-----------------|--------------------------------------|

| Symbol               | Parameter                                                 | Min  | Max    | Units           | (Note 1)                             |

| ILI                  | Input Current (All Inputs)                                |      | 1      | μΑ              | $V_{IN} = V_{IL} \text{ or } V_{IH}$ |

| V <sub>IL</sub>      | Input Low Level (All Inputs)                              | -0.1 | 0.8    | ٧               |                                      |

| V <sub>IH</sub>      | Input High Level                                          | 2.4  | 6.5    | ٧               |                                      |

| V <sub>OL</sub>      | Output Low Voltage During Verify                          |      | 0.45   | ٧               | I <sub>OL</sub> = 2.1 mA             |

| V <sub>OH</sub>      | Output High Voltage During Verify                         | 3.5  |        | V               | $I_{OH} = -2.5 \mu A$                |

| l <sub>CC2</sub> (3) | V <sub>CC</sub> Supply Current (Program and Verify)       |      | 40     | mA              |                                      |

| I <sub>PP2</sub>     | V <sub>PP</sub> Supply Current (Program)                  |      | 50     | mA              | CE = VIL                             |

| V <sub>ID</sub>      | A <sub>9</sub> int <sub>e</sub> ligent Identifier Voltage | 11.5 | 12.5   | V               |                                      |

| V <sub>PP</sub>      | Quick-Pulse Programming Algorithm                         | 12.5 | 13.0   | V               |                                      |

| V <sub>CC</sub>      | Quick-Pulse Programming Algorithm                         | 6.0  | 6.5    | V               |                                      |

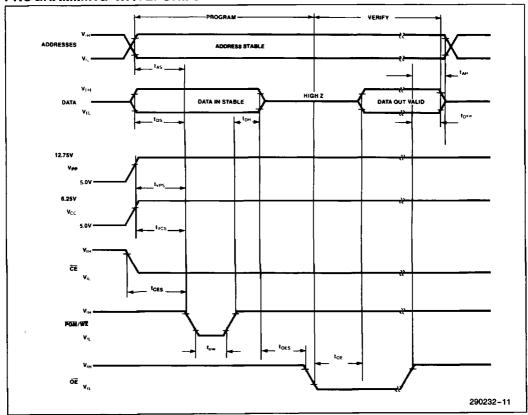

#### **AC PROGRAMMING CHARACTERISTICS**

$T_A = 25^{\circ}C \pm 5^{\circ}C$  (See Table 3 for  $V_{CC}$  and  $V_{PP}$  voltages.)

| Symbol           | Parameter                     |     | Li  | mits | Conditions* |                         |

|------------------|-------------------------------|-----|-----|------|-------------|-------------------------|

|                  | i di dilicici                 | Min | Тур | Max  | Units       | (Note 1)                |

| t <sub>AS</sub>  | Address Setup Time            | 2   |     |      | μs          |                         |

| t <sub>OES</sub> | OE Setup Time                 | 2   |     |      | μs          |                         |

| t <sub>DS</sub>  | Data Setup Time               | 2   |     |      | μs          |                         |

| t <sub>AH</sub>  | Address Hold Time             | 0   |     |      | μs          |                         |

| t <sub>DH</sub>  | Data Hold Time                | 2   |     |      | μs          |                         |

| t <sub>DFP</sub> | OE High to Output Float Delay | 0   |     | 130  | ns          | (Note 2)                |

| t <sub>VPS</sub> | V <sub>PP</sub> Setup Time    | 2   |     |      | μs          |                         |

| t <sub>VCS</sub> | V <sub>CC</sub> Setup Time    | 2   |     |      | μs          |                         |

| t <sub>CES</sub> | CE Setup Time                 | 2   |     |      | μs          |                         |

| t <sub>PW</sub>  | PGM Program Pulse Width       | 95  | 100 | 105  | μs          | Quick-Pulse Programming |

| toE              | Data Valid from OE            |     |     | 150  | ns          |                         |

#### \*AC CONDITIONS OF TEST

| Input Rise and Fall Times (10% to 90° | %)20 ns        |

|---------------------------------------|----------------|

| Input Pulse Levels                    | .0.45V to 2.4V |

| Input Timing Reference Level          | .0.8V and 2.0V |

| Output Timing Reference Level         | .0.8V and 2.0V |

#### NOTES:

- 1.  $V_{CC}$  must be applied simultaneously or before  $V_{PP}$  and removed simultaneously or after  $V_{PP}$ .

- This parameter is only sampled and is not 100% tested. Output Float is defined as the point where data is no longer driven—see timing diagram.

- 3. The maximum current value is with outputs  $O_0 O_7$  unloaded.

#### PROGRAMMING WAVEFORMS

- 1. The Input Timing Reference Level is 0.8V for a V<sub>IL</sub> and 2.0V for a V<sub>IH</sub>.

2. tog and togp are characteristics of the device but must be accommodated by the programmer.

3. The proper page to be programmed must be selected by a page-select write operation prior to programming each of the four 16 Kbyte pages. See Page Select Write AC and DC Characteristics for information on page selection operations.

#### **REVISION HISTORY**

| Number | Description             |

|--------|-------------------------|

| 002    | Remove 150 speed option |