Model SY0006 Date: August 1, 2000

PRELIMINARY

#### INTRODUCTION

The SY0006 is an accurate time and frequency source that has been designed as a module level subsystem. The module is designed to work within ATM, SONET, SDH, and wireless systems where synchronization is vital. The SY0006 is an excellent synchronization solution for timing, jitter and wander topics specified within ITU-T Recommendations G.812, ETSI -ETS 300 462-4, and Bellcore GR-1244-CORE. The SY0006 is designed for Stratum 4 applications.

#### FEATURES

A synchronization solution for timing, jitter and wander concerns in a single module.

Complies with ITU-T Recommendations G.812 and ETSI-ETS 300 462-4 and Bellcore GR-1244-CORE for Stratum 4 applications.

Supports four modes of operation: Locked to Reference 1, Locked to Reference 2, Holdover and Free-run.

Accepts reference inputs from two independent sources from 8 kHz to 77.76 MHz.

Provides two outputs up to 77.76 MHz.

Loop filtering utilizing application specific software in the digital signal processor (DSP).

Continuously monitors and evaluate input reference signals.

Creates a history buffer for Holdover mode operation.

Manual or Automatic selection between timing modes.

Alarm and status signal.

Host interface and JTAG port.

Small dimensions of 2.0 x 2.0 x 0.75 inch.

#### APPLICATION

The SY0006 performs clock regeneration as a Synchronous Equipment Clock (SEC), or STRATUM 4 in ATM, SDH, PDH, and SONET networks. It is designed for manufacturers of network equipment, especially Access Switches, Core Switches, Cross Connects, Digital Multiplexers-Exchangers, and SDH/SONET equipment. The unit is also suitable for PCS, WLL, and Wireless Base Stations. Wherever a Timing unit with high performance specifications is required, the SY0006 can be integrated into the network system and provide all necessary frequencies and interfaces. The input stage can receive two different input reference signals at various rates from 4 kHz to 77.76 MHz. An optional application can be achieved by integrating the SY0006 with a low cost GPS receiver and locking it to the GPS 1 pps output signal.

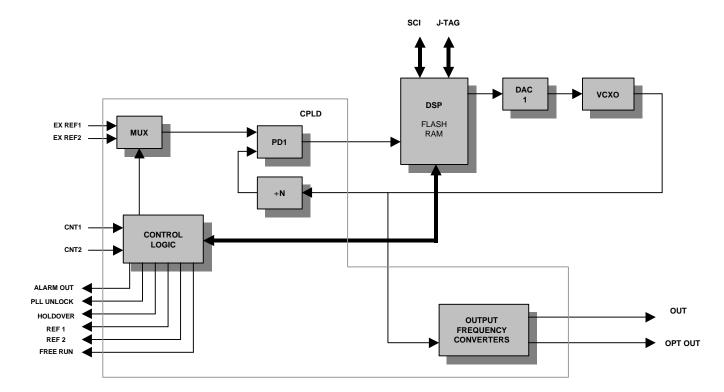

Figure 1. - The functional block diagram of SY0006

#### DESCRIPTION

The SY0006 synchronization module is a Digital PLL (DPLL), which utilizes application specific software in the digital signal processor (DSP). The DSP is complemented by fast hardware logic (CPLD) where all multiplexers, counters, dividers, phase detectors, output frequency converters and other control logic circuits are completely implemented. The functional block diagram with maximum configuration is shown in figure 1. Depending on the application, the user can specify an appropriate configuration to fit their system requirements. The basic configuration utilizes one DPLL with a VCXO as on-board oscillator, shown in figure 1 as the shaded boxes. The VCXO is driven by a digital-to-analog converter (DAC1) and provides the accurate and stable signal with less power consumption. The output frequency converters scale the output frequency from the oscillator. For other configurations, please contact Raltron.

## ✓ The module operates in the following four timing modes:

#### Free-run

In this mode the unit is unlocked to either of the inputs. The accuracy of the output frequencies in this mode is ±32ppm. Free-run mode is typically used when a master clock source is required, not valid history of data for the Holdover mode, or immediately following system power-up before network synchronization is achieved. In the Free-run Mode, the SY0006 provides timing and synchronization signals that are based on the accuracy of onboard oscillators only, and are not synchronized to the reference signals.

## Holdover

In this mode the module has lost its reference inputs and is utilizing stored timing data, called history, to control the output frequency. Holdover Mode is typically used while network synchronization is temporarily disrupted. In Holdover Mode, the SY0006 provides timing, based on data from the history buffer, while unlocked to an external reference signal. The history data is determined while the device is locked to an external reference signal. The stability of the output signal in holdover mode depends primarily on the stability of on-board oscillator and

environment effects where the clock is mounted. The SY0006 uses a VCXO as an on-board oscillator but other types of oscillators are available.

#### Locked to Ref.1

In this mode the output of the module is phase locked to input reference 1.

#### Locked to Ref.2

In this mode the output of the module is phase locked to input reference 2.

The REF1 or REF2 Modes are typically used when a slave clock source is synchronized to the network. In these modes, the SY0006 provides timing signals, which are synchronized, to one of two references inputs (REF1 or REF2). The input reference signals may have a variety of nominal frequencies, which is typically specified by the end user. When the modes are selected the unit goes through a reference evaluation, and then a frequency acquisition, and finally to phase locking.

### Input References

The SY0006 module accepts two input references EX REF1 and EX REF2. End users can specify the frequencies within a range of 8 kHz to 77.76 MHz. The input reference signals are HCMOS/TTL levels with timing characteristic in according to Bellcore GR-1244-core 3.2.1.R3-1 or equivalent standards. Please note that the end user must specify the two input frequencies at the time of order.

## Output Signals

The SY0006 module provides two output signals OUT and OPT OUT. The outputs are generated by the internal oscillator and scaled by the output frequency converters. The performance of the module significantly depends on the internal oscillator and special care was taken to define its specification. A Voltage Controlled Crystal Oscillator (VCXO) is used as the internal oscillator. The frequency of the oscillator is specified according to the network application where the SY0006 will be used. The frequency converters divide signal from the oscillator to the specified frequencies.

## Specifications

|                               |                                | 2" (D) x 2" (W) x 0.75" (H)      | Hermetically Sealed Metal box     |

|-------------------------------|--------------------------------|----------------------------------|-----------------------------------|

| General Specifications        | Mechanical                     | 1.85" (D) x 1.85" (W) x 0.7" (H) | Metal Box                         |

|                               |                                | 1.8" (D) x 1.8" (W) x 0.55" (H)  | Module on PCB                     |

|                               | Power Supply                   | 5VDC                             | Regulated                         |

|                               | Current Supply                 | 300mA max.                       |                                   |

|                               | Operating Temperature          | -20°C to 70°C                    | Other ranges available on request |

|                               | Storage Temperature            | -40° to 85°C                     |                                   |

|                               | Humidity                       | 5% to 95% non-condensing         |                                   |

|                               | Internal Oscillators           | VCXO                             |                                   |

| Input Signals                 | Number of Inputs               | 2                                |                                   |

|                               | Input reference frequency      | 8kHz to 77.76MHz                 | User selectable                   |

|                               | Signal Level                   | HCMOS/TTL Compatible             |                                   |

|                               | Time Reference characteristics |                                  | Bellcore: GR-1244-core 3.2.1.R3-1 |

|                               | Number of Outputs              | 2                                |                                   |

| Output Signal                 | Output 1                       | 8kHz to 77.76MHz                 | User define                       |

| Output Signal                 | Output 2                       | 8kHz to 77.76MHz                 | User define                       |

|                               | Signal Level                   | HCMOS                            | Depend of the frequency output    |

| Signal Quality<br>Performance | Jitter Tolerance               |                                  | Bellcore: GR-1244-core 4.2        |

|                               |                                |                                  | ITU-T: G.812                      |

|                               | Phase Transient Tolerance      |                                  | Bellcore: GR-1244-core 4.4        |

|                               | Wander Generation              |                                  | Bellcore: GR-1244-core 5.3        |

|                               | Wander Generation              |                                  | ITU-T: G.812                      |

| Frequency Output              | Free run accuracy              | ±32ppm                           | GR-1244-core 5.1                  |

| Performance                   |                                |                                  | ITU-T: G.812                      |

|                               | Holdover frequency stability   | N.A.                             |                                   |

|                               | Initial Offset                 | N.A.                             | Bellcore: GR-1244-core 5.2        |

|                               | miliai Olisei                  | N.A.                             | ITU-T: G.812                      |

|                               | Temperature                    | N.A.                             |                                   |

|                               | Drift                          | N.A                              | Bellcore: GR-1244-core 5.2        |

|                               |                                |                                  | ITU-T: G.812                      |

|                               | DPLL bandwidth                 | 3Hz                              |                                   |

|                               | Lock Time                      | <10sec                           | GR-1244-core 3.7                  |

|                               | Lock accuracy                  | ±1x10 <sup>-11</sup>             |                                   |

## Pin Assignment

On the picture below it is shown the pin-out for the SY0006. The design is done in such a way that is can support basically any other pin-out without changes in the hardware. For other pin-out requirement please contact the Raltron.

| +5V      | O 18 | 1 0 | HOLDOVER   |

|----------|------|-----|------------|

| EX REF1  | O 17 | 2 O | REF 1      |

| GND      | O 16 | з О | REF2       |

| EX REF 2 | O 15 | 4 O | FREERUN    |

| GND      | O 14 | 5 O | GND        |

| OPT OUT  | O 13 | 6 O | ALARM OUT  |

| GND      | O 12 | 7 O | CNT 1      |

| OUT      | O 11 | 8 O | CNT 2      |

| GND      | O 10 | 9 O | PLL UNLOCK |

|          |      |     |            |

|          |      |     |            |

Figure 4 - Bottom view

| Pin #         | Name       | Description                                                                                                                      |  |  |

|---------------|------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1             | HOLDOVER   | Holdover Signal -> the output is high when the unit is in holdover mode                                                          |  |  |

| 2             | REF 1      | Reference 1 Signal -> the output is high when the unit is using the reference 1                                                  |  |  |

| 3             | REF 2      | Reference 2 Signal -> the output is high when the unit is using the reference 2                                                  |  |  |

| 4             | FREERUN    | Free-run Signal -> the output is high when the unit is in the free run mode                                                      |  |  |

| 6             | ALARM OUT  | Alarm signal -> the output is high when there is an alarm in the module, alarm condition is during free-run mode, holdover mode, |  |  |

| 7             | CNT 1      | Control Input 1 -> the external input for selecting mode of the unit – see table.                                                |  |  |

| 8             | CNT 2      | Control Input 2 -> the external input for selecting mode of the unit – see table.                                                |  |  |

| 9             | PLL UNLOCK | PLL Unlocked Signal -> the output is high when the unit is not locked to any of the references                                   |  |  |

| 5,10,12,14,16 | GND        | Ground                                                                                                                           |  |  |

| 18            | +5V        | Positive Voltage Supply                                                                                                          |  |  |

| 11            | OUT        | Synchronized Output -> the output of the synchronized signal, for frequency range see table below.                               |  |  |

| 13            | OPT OUT    | Optional Output -> the secondary output of the synchronized signal, for frequency range see table below.                         |  |  |

| 17            | EX REF 1   | External Reference 1 Input -> the input signal from reference 1                                                                  |  |  |

| 15            | EX REF 2   | External Reference 2 Input -> the input signal from reference 2                                                                  |  |  |

For other pin-out configurations contact the factory!

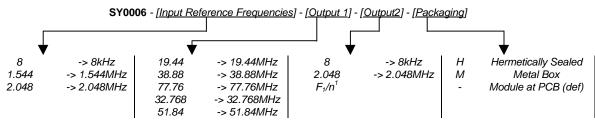

# Ordering Information

For other frequencies contact the factory!

Example: SY0006-8-19.44-8

<sup>1)</sup>  $F_1/n$  -> is frequency of the output 1 divided by any integer number;

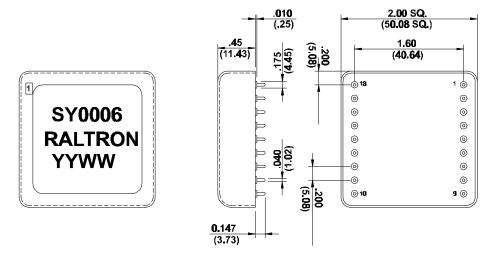

#### Mechanical dimensions

Figure 5 - The mechanical dimensions.

Figure 5 shows the mechanical dimension of the SY0006 module. The module can be supplied in three different types of packaging:

- Hermetically sealed metal box

- Metal box

- Module without packaging

The dimensions shown on the picture are valid for first and second type of packaging, the actual dimensions for the third type are 1.8 x 1.8 x 0.55" keeping the pin-out dimensions the same for all of three. The label on the module shows part number, factory name, week and year of production.