# 32Kx32 Monolithic Flow Through Synchronous SRAM ADVANCED\*

#### **FEATURES**

- Fast Access Times of 10 and 11ns

- Fast OE Access Time of 7ns

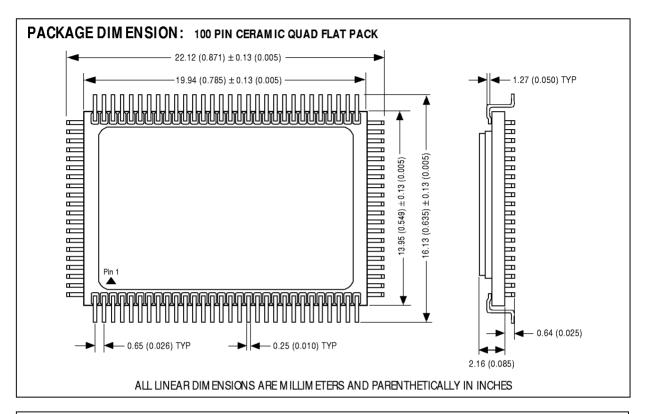

- Packaging:

- 100-pin Ceramic Quad Hatpack, CQFP. Footprint compatible with standard 100 lead TQFP package.

- Single  $+3.3V \pm 5\%$  Power Supply

- 5V-Tolerant Common Data I/O

- Individual Byte Write Control and Global Write

- How through Data Bus

- Industrial and Military Temperature Ranges

- Write Pass-through Capability

- Clock Controlled, Registered, Address, Data and Control

- Internally Self-timed Write Cycle

- Burst Control Pin (Interleaved or Linear Burst)

- Snooze Mode for Reduced Power Standby

- High 30pF Output Drive Capability at Rated Access Time

- \* This data sheet describes a product that may or may not be under development and is subject to change or cancellation without notice.

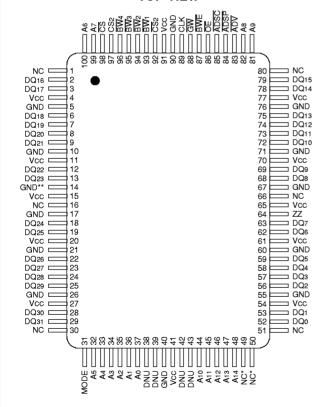

# FIG. 1 PIN CONFIGURATION FOR WMY32K32V-XTQX TOP VIEW

- Pin 49 is reserved for A<sub>15</sub>, pin 50 for A<sub>16</sub>.

- \*\* Pin 14 does not have to be directly connected to GND as long as the input voltage is ≤ V<sub>IL</sub>.

## PIN DESCRIPTION

| DQ0-31              | Data Inputs/Outputs                      |  |  |  |  |  |

|---------------------|------------------------------------------|--|--|--|--|--|

| A0-14               | Address Inputs                           |  |  |  |  |  |

| BW 1-4              | Byte Writes                              |  |  |  |  |  |

| CLK                 | Clock                                    |  |  |  |  |  |

| CS, CS <sub>2</sub> | Synchronous Chip Selects                 |  |  |  |  |  |

| ŌĒ                  | Output Enable                            |  |  |  |  |  |

| ADV                 | Synchronous Address Advance              |  |  |  |  |  |

| ADSP                | Synchronous Address Status<br>Processor  |  |  |  |  |  |

| ADSC                | Synchronous Address Status<br>Controller |  |  |  |  |  |

| ZZ                  | Snooze Enable                            |  |  |  |  |  |

| BWE                 | Byte Write Enable                        |  |  |  |  |  |

| Ġ₩                  | Global Write                             |  |  |  |  |  |

| MODE                | Burst Sequence Mode                      |  |  |  |  |  |

| Vcc                 | +3.3V Power Supply                       |  |  |  |  |  |

| GND                 | Ground                                   |  |  |  |  |  |

| NC                  | Not Connected                            |  |  |  |  |  |

| DNU                 | o Not Use                                |  |  |  |  |  |

## **GENERAL DESCRIPTION**

The device integrates a 32Kx32 SRAM Core with advanced synchronous peripheral circuitry and a 2-bit burst counter. All synchronous input passes through registers controlled by a positive-edge-triggered Signal Clock Input (CLK). The synchronous inputs include all Addresses, all Data Inputs, active low Chip Select  $(\overline{CS})$ , two additional chip selects for easy depth expansion (CS2,  $\overline{CS}$ 2), Burst Control Inputs  $(\overline{ADSC}, \overline{ADSP}, \overline{ADV})$ , Byte Write Enables  $(\overline{BW}_{1-4})$ , and Global Write  $(\overline{GW})$ .

Asynchronous inputs include the Output Enable  $(\overline{OE})$ , Clock (CLK) and Snooze Enable (ZZ). There is a Burst Mode pin (MODE) that selects between interleaved and linear burst modes. The Data Out (Q), enabled by  $\overline{OE}$  is also asynchronous. W RITE cycles can be from 1 to 4 bytes wide as controlled by the write control inputs.

Burst operation can be initiated with either ADSP or ADSC input pins. Subsequent burst addresses can be internally generated as controlled by the Burst Advance pin (ADV).

Address and write control are registered on-chip to simplify WRITE cycles. This allows self-timed WRITE cycles. Individual byte enables allow individual bytes to be written.

GW Low causes all Bytes to be written.

The device operates from a 3.3V power supply and all inputs and outputs are TTL-compatible.

#### TRUTH TABLE

| CS | ŪS₂ | CS <sub>2</sub> | ZZ | ADSP | ADSC | ADV | WRITE | ŌĒ | CLK | DQ     | Address Used     | Operation                    |

|----|-----|-----------------|----|------|------|-----|-------|----|-----|--------|------------------|------------------------------|

| Н  | Х   | Χ               | L  | Х    | L    | Х   | Х     | Χ  | L→H | High-Z | N/A              | Deselected Cycle, Power-down |

| L  | Х   | L               | L  | L    | Х    | Х   | Х     | Х  | L→H | High-Z | N/A              | Deselected Cycle, Power-down |

| L  | Н   | Χ               | L  | L    | Х    | Х   | Х     | Χ  | L→H | High-Z | N/A              | Deselected Cycle, Power-down |

| L  | Х   | L               | L  | Н    | L    | Х   | Х     | Х  | L→H | High-Z | N/A              | Deselected Cycle, Power-down |

| L  | Н   | Χ               | L  | Н    | L    | Х   | Х     | Χ  | L→H | High-Z | N/A              | Deselected Cycle, Power-down |

| Χ  | Х   | Χ               | Н  | Х    | Х    | Х   | Х     | Χ  | Х   | High-Z | N/A              | SNOOZE MODE, Power-down      |

| L  | L   | H               | L  | L    | Χ    | Χ   | Х     | L  | L→H | Q      | External Address | READ Cycle, Begin Burst      |

| L  | L   | H               | Ш  | L    | Χ    | Χ   | Х     | Н  | L→H | High-Z | External Address | READ Cycle, Begin Burst      |

| L  | L   | Η               | L  | Н    | L    | Х   | L     | Χ  | L→H | D      | External Address | WRITE Cycle, Begin Burst     |

| L  | L   | Н               | L  | Н    | L    | Х   | Н     | L  | L→H | Q      | External Address | READ Cycle, Begin Burst      |

| L  | L   | Н               | L  | Н    | L    | Х   | Н     | Н  | L→H | High-Z | External Address | READ Cycle, Begin Burst      |

| Х  | Х   | Χ               | L  | Н    | Н    | L   | Н     | L  | L→H | Q      | Next Address     | READ Cycle, Continue Burst   |

| Х  | Х   | Χ               | L  | Н    | Н    | L   | Н     | Н  | L→H | High-Z | Next Address     | READ Cycle, Continue Burst   |

| Н  | Х   | Χ               | L  | Х    | Н    | L   | Н     | L  | L→H | Q      | Next Address     | READ Cycle, Continue Burst   |

| Н  | Х   | Χ               | L  | Х    | Н    | L   | Н     | Н  | L→H | High-Z | Next Address     | READ Cycle, Continue Burst   |

| Х  | Х   | Χ               | L  | Н    | Н    | L   | L     | Χ  | L→H | D      | Next Address     | WRITE Cycle, Continue Burst  |

| Н  | Х   | Χ               | L  | Х    | Н    | L   | L     | Χ  | L→H | D      | Next Address     | WRITE Cycle, Continue Burst  |

| Х  | Х   | Χ               | L  | Н    | Н    | Н   | Н     | L  | L→H | Q      | Current Address  | READ Cycle, Suspend Burst    |

| Х  | Х   | Χ               | L  | Н    | Н    | Н   | Н     | Н  | L→H | High-Z | Current Address  | READ Cycle, Suspend Burst    |

| Н  | Х   | Χ               | L  | Х    | Н    | Н   | Н     | L  | L→H | Q      | Current Address  | READ Cycle, Suspend Burst    |

| Н  | Х   | Χ               | L  | Х    | Н    | Н   | Н     | Н  | L→H | High-Z | Current Address  | READ Cycle, Suspend Burst    |

| Х  | Х   | Χ               | L  | Н    | Н    | Н   | L     | Χ  | L→H | D      | Current Address  | WRITE Cycle, Suspend Burst   |

| Н  | Х   | Х               | L  | Х    | Н    | Н   | L     | Х  | L→H | D      | Current Address  | WRITE Cycle, Suspend Burst   |

#### NOTES:

- 1. X means "don't care." H means logic HIGH. L means logic LOW. WRITE = L means any one or more byte write enable signals (BW<sub>1</sub>, BW<sub>2</sub>, BW<sub>3</sub> or BW<sub>4</sub>) and BWE are LOW or GW is LOW. WRITE = H means all byte write enable signals and GW are HIGH.

- 2. BW1 enables WRITEs to Byte 1 (DQo-7). BW2 enables WRITEs to Byte 2 (DQs-15). BW3 enables WRITEs to Byte 3 (DQ16-23). BW4 enables WRITEs to Byte 1 (DQ04-31).

- 3. All inputs except  $\overline{OE}$  and ZZ must meet setup and hold times around the rising edge (LOW to HIGH) of CLK.

- 4. Wait states are inserted by suspending burst.

- 5. For a WRITE operation following a READ operation,  $\overline{\text{CE}}$  must be HIGH before the input data setup time and held HIGH throughout the input data hold time.

- 6. This device contains circuitry that will ensure the outputs will be in High-Z during power-up.

- 7. ADSP LOW always initiates an internal READ at the L→H edge CLK. A WRITE is performed by setting one or more byte write enable signals and BWE LOW or GW LOW for subsequent L→H edge of CLK.