#### Philips Components-Signetics

|               | <u> </u>              |

|---------------|-----------------------|

| Document No.  |                       |

| ECN No.       |                       |

| Date of Issue | June 1989             |

| Status        | Product Specification |

| Memory Produ  | cts                   |

# PCF8581/8581C 128 $\times$ 8-bit EEPROM with I<sup>2</sup>C-bus interface

#### GENERAL DESCRIPTION

The PCF8581 and PCF8581C are low-power CMOS EEPROMs with standard and wide operating voltage:

4.5 to 5.5 V (PCF8581); 2.5 to 6.0 V (PCF8581C).

In the following text, the generic term "PCF8581" is used to refer to both types in all packages except where specified.

The PCF8581 is organized as 128 words by 8-bits.

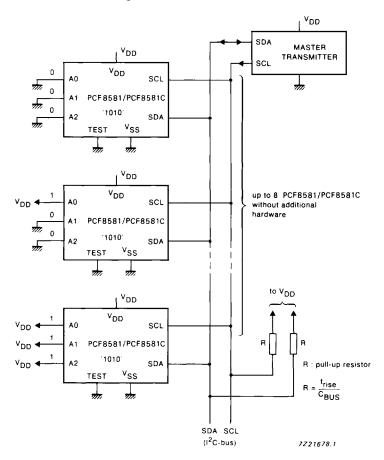

Addresses and data are transferred serially via a two-line bidirectional bus (I<sup>2</sup>C). The built-in word address register is incremented automatically after each written or read data byte. All bytes can be read in a single operation. Up to eight bytes can be written in one operation, reducing the total write time per byte. Three address pins A0, A1 and A2 are used to define the hardware address, allowing the use of up to eight devices connected to the bus without additional hardware.

#### **Features**

- Operating supply voltage: 4.5 to 5.5 V (PCF8581); 2.5 to 6.0 V (PCF8581C)

- Integrated voltage multiplier and timer for writing (no external components required)

- · Automatic erase before write

- Low standby current max, 10 μA

- Eight-byte page write mode

- Serial input/output bus (I<sup>2</sup>C)

- Address by 3 hardware address pins

- Automatic word address incrementing

- Designed for 10 000 write cycles per byte minimum

- 10 years minimum non-volatile data retention

- Infinite number of read cycles

- Pin and address compatibility to PCF8570, PCF8571 and PCF8582

PCF8581P/PCF8581CP: 8-lead DIL; plastic (SOT97).

PCF8581T/PCF8581CT: 8-lead mini-pack (SO-8L; SOT176C).

# 128 × 8-bit EEPROM with I<sup>2</sup>C-bus interface

## PCF8581/8581C

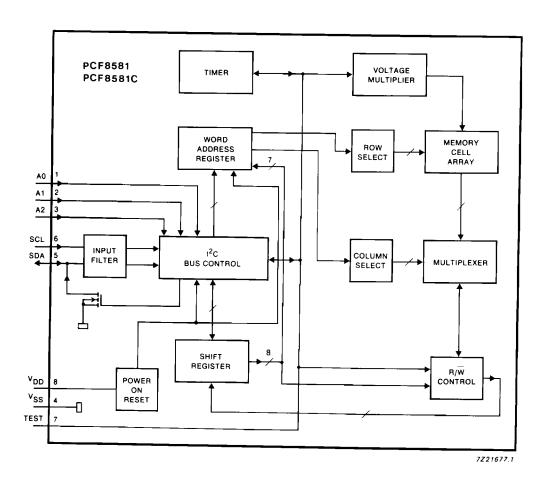

Fig.1 Block diagram.

# 128 × 8-bit EEPROM with I<sup>2</sup>C-bus interface

PCF8581/8581C

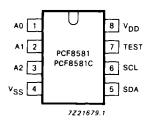

| PINNIN | <b>I</b> G |                                                               |

|--------|------------|---------------------------------------------------------------|

| 1      | A0         |                                                               |

| 2      | A1 }       | hardware address inputs                                       |

| 3      | A2         |                                                               |

| 4      | $V_{SS}$   | negative supply                                               |

| 5      | SDA        | serial data input/output   I <sup>2</sup> C-bus               |

| 6      | SCL        | serial clock input                                            |

| 7      | TEST       | test output can be connected to VSS, VDD or left open-circuit |

| 8      | $v_{DD}$   | positive supply                                               |

Fig.2 Pinning diagram.

#### **RATINGS**

Limiting values in accordance with the Absolute Maximum System (IEC 134)

| parameter                           | symbol           | min. | max.                 | unit |

|-------------------------------------|------------------|------|----------------------|------|

| Supply voltage range (pin 8)        | V <sub>DD</sub>  | -0.3 | 7.0                  | V    |

| Voltage range on any input*         | l v <sub>i</sub> | -0.8 | V <sub>DD</sub> +0.8 | V    |

| DC input current (any input)        | ± 11             | _    | 10                   | mA   |

| DC output current (any output)      | ± 10             | _    | 10                   | mA   |

| Total power dissipation             | P <sub>tot</sub> | _    | 150                  | mW   |

| Power dissipation per output        | P                | _    | 50                   | mW   |

| Storage temperature range           | T <sub>stg</sub> | -65  | + 150                | °C   |

| Operating ambient temperature range | T <sub>amb</sub> | -40  | + 85                 | °C   |

<sup>\*</sup> Measured via a 500  $\Omega$  resistor.

# 128 × 8-bit EEPROM with I<sup>2</sup>C-bus interface

PCF8581/8581C

#### **CHARACTERISTICS**

$V_{DD}$  = 2.5 to 6 V (PCF8581C) 4.5 to 5.5 V (PCF8581);  $V_{SS}$  = 0 V;  $T_{amb}$  = -40 to +85 °C unless otherwise specified

| parameter                                              | conditions                                                                | symbol            | min.               | typ.         | max.               | unit           |

|--------------------------------------------------------|---------------------------------------------------------------------------|-------------------|--------------------|--------------|--------------------|----------------|

| Supply                                                 | • • •                                                                     |                   | <del> </del>       |              |                    |                |

| Supply voltage range<br>PCF8581A<br>PCF8581            |                                                                           | V <sub>DD</sub>   | 2.5<br>4.5         | _            | 6.0<br>5.5         | V              |

| Supply current<br>standby<br>operating<br>during write | f <sub>SCL</sub> = 0 Hz<br>f <sub>SCL</sub> = 100 kHz<br>see bus protocol | IDD<br>IDD<br>IDD | -<br>  -<br>  -    | <br> -<br> - | 10<br>400<br>1000  | μΑ<br>μΑ<br>μΑ |

| Inputs                                                 |                                                                           |                   |                    |              |                    |                |

| A0, A1, A2, SCL, SDA                                   |                                                                           |                   |                    |              |                    |                |

| Input voltage LOW                                      |                                                                           | VIL               | _                  | _            | 0.3V <sub>DD</sub> | v              |

| Input voltage HIGH                                     |                                                                           | VIH               | 0.7V <sub>DD</sub> | _            | _                  | v              |

| Input leakage current                                  | pin at V <sub>SS</sub> or V <sub>DD</sub>                                 | ILI               | _                  |              | 1                  | μΑ             |

| Input capacitance                                      | pin at V <sub>SS</sub>                                                    | CI                | -                  | _            | 7                  | p <b>F</b>     |

| Outputs                                                |                                                                           |                   |                    |              |                    |                |

| SDA                                                    |                                                                           |                   |                    |              |                    |                |

| Output current LOW TEST                                | pin at 0.4 V                                                              | lor               | 3                  | _            | _                  | mA             |

| Output leakage current                                 | pin at V <sub>SS</sub> or V <sub>DD</sub>                                 | lLO               | _                  | _            | 1                  | μΑ             |

| Erase/write data                                       |                                                                           |                   |                    |              |                    |                |

| Write time                                             |                                                                           | twr               | 6                  | _            | 12                 | ms             |

| Data retention time                                    |                                                                           | t <sub>RET</sub>  | 10                 | _            | _                  | years          |

Purchase of Philips' I<sup>2</sup>C components conveys a license under the Philips' I<sup>2</sup>C patent to use the components in the I<sup>2</sup>C-system provided the system conforms to the I<sup>2</sup>C specifications defined by Philips.

84

June 1989

#### PCF8581/8581C

#### CHARACTERISTICS OF THE 12C-BUS

The I<sup>2</sup>C-bus is for two-way, 2-line communication between different ICs or modules. The two lines are a serial data line (SDA) and a serial clock line (SCL). Both lines must be connected to a positive supply via a pull-up resistor when connected to the output stages of a device. Data transfer may be initiated only when the bus is not busy.

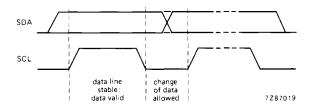

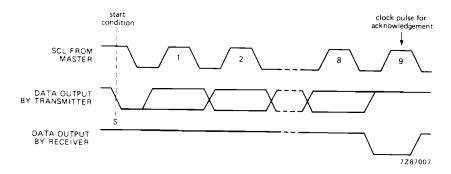

#### Bit transfer

One data bit is transferred during each clock pulse. The data on the SDA line must remain stable during the HIGH period of the clock pulse as changes in the data line at this time will be interpreted as control signals.

Fig. 3 Bit transfer.

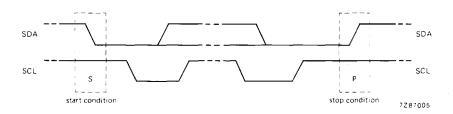

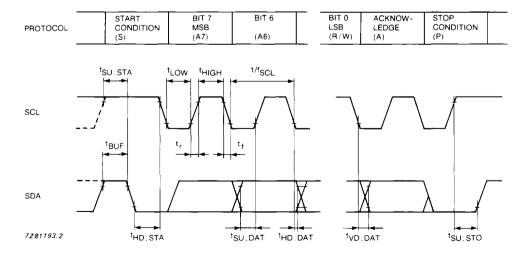

#### Start and stop conditions

Both data and clock lines remain HIGH when the bus is not busy. A HIGH-to-LOW transition of the data line, while the clock is HIGH is defined as the start condition (S). A LOW-to-HIGH transition of the data line while the clock is HIGH is defined as the stop condition (P).

Fig. 4 Definition of start and stop conditions.

PCF8581/8581C

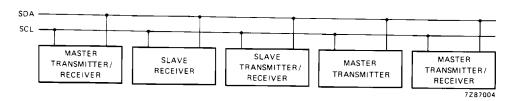

#### System configuration

A device generating a message is a "transmitter", a device receiving a message is the "receiver". The device that controls the message is the "master" and the devices which are controlled by the master are the "slaves".

Fig. 5 System configuration.

#### Acknowledge

The number of data bytes transferred between the start and stop conditions from transmitter to receiver is not limited. Each byte of eigth bits is followed by one acknowledge bit. The acknowledge bit is a HIGH level put on the bus by the transmitter whereas the master generates an extra acknowledge related clock pulse. A slave receiver which is addressed must generate an acknowledge after the reception of each byte. Also a master must generate an acknowledge after the reception of each byte that has been clocked out of the slave transmitter. The device that acknowledges has to pull down the SDA line during the acknowledge clock pulse, so that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse, set-up and hold times must be taken into account. A master receiver must signal an end of data to the transmitter by **not** generating an acknowledge on the last byte that has been clocked out of the slave. In this event the transmitter must leave the data line HIGH to enable the master to generate a stop condition.

Fig. 6 Acknowledgement on the I2C-bus.

## PCF8581/8581C

## **Timing specifications**

All the timing values are valid within the operating supply voltage and ambient temperature range and refer to  $V_{IL}$  and  $V_{IH}$  with an input voltage swing of  $V_{SS}$  to  $V_{DD}$ .

| parameter                    | symbol               | min. | typ. | max. | unit |

|------------------------------|----------------------|------|------|------|------|

| SCL clock frequency          | fSCL                 | _    | _    | 100  | kHz  |

| Tolerable spike width on bus | tsw                  | _    | _    | 100  | ns   |

| Bus free time                | tBUF                 | 4.7  | _    | _    | μs   |

| Start condition set-up time  | <sup>t</sup> SU; STA | 4.7  | _    | _    | μs   |

| Start condition hold time    | tHD; STA             | 4.0  | _    | _    | μs   |

| SCL LOW time                 | tLOW                 | 4.7  | _    | _    | μs   |

| SCL HIGH time                | tHIGH                | 4.0  | _    | _    | μs   |

| SCL and SDA rise time        | t <sub>r</sub>       | -    | _    | 1.0  | μs   |

| SCL and SDA fall time        | tf                   | -    | -    | 0.3  | μs   |

| Data set-up time             | tSU; DAT             | 250  | _    | _    | ns   |

| Data hold time               | tHD; DAT             | 0    | _    | _    | ns   |

| SCL LOW to data out valid    | tVD; DAT             | _    | _    | 3.4  | μs   |

| Stop condition set-up time   | tSU; STO             | 4.0  | _    | _    | μs   |

Fig. 7 I<sup>2</sup>C-bus timing diagram.

PCF8581/8581C

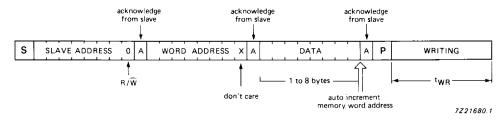

#### **Bus protocol**

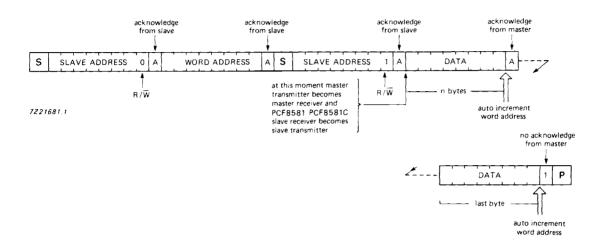

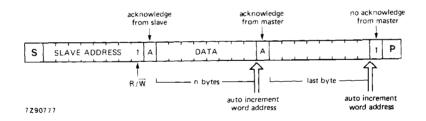

Before any data is transmitted on the I<sup>2</sup>C-bus, the device which should respond is addressed first. The addressing is always done with the first byte transmitted after the start procedure. The I<sup>2</sup>C-bus configuration for PCF8581 WRITE cycle is shown in Fig. 8 and READ cycle in Figs 10 and 11.

#### Writing

Fig. 8 Master transmits to slave receiver (WRITE mode).

After the word address, one to eight data bytes can be sent. The address is automatically incremented, but the four highest address bits (row) are internally latched. Therefore all bytes are written in the same row.

An example of writing eight bytes with word address X0000000 and six bytes with word address X0010101 is shown in Fig. 9. Where X = don't care.

| word address | row    | bytes |     |      |      |      |        |        |     |      |

|--------------|--------|-------|-----|------|------|------|--------|--------|-----|------|

| X0000000     | 0      | 1 →   | 2   | 3    | 4    | 5 →  | 6 →    | 7      | 8   |      |

| X0000001     | 1      |       |     |      |      |      |        |        |     |      |

| X0010101     | 2      | 4     | 5 → | 6    |      |      | 1>     | 2 →    | 3 → | 1    |

| X0011101     | 3      |       |     |      |      |      |        |        |     | 1    |

|              |        |       |     |      |      |      |        |        |     |      |

|              | ١.     | <br>  | 1   | <br> | <br> | <br> | 1<br>1 | l<br>i | 1   | <br> |

|              | column | 0     | 1   | 2    | 3    | 4    | 5      | 6      | 7   |      |

Fig. 9 Writing eight and six bytes with different word addresses.

To transmit eight bytes in sequential order, begin with the lowest address bits 000. The data is written after a stop is detected. The data is only written if complete bytes have been received and acknowledged. Writing takes a time two (6 to 12 ms) during which the device will not respond to its slave address. Note that to write the next row, a new write operation is required (start, slave address, row address, data, stop).

#### LIFE SUPPORT APPLICATIONS

Faselec's product is not designed for use in life support appliances, devices or systems where malfunction of above product can reasonably be expected to result in a personal injury. Faselec's customers using or selling Faselec's PCF8581/81C for use in life support applications do so at their own risk and agree to fully indemnify Faselec for any damages resulting from such improper use or sale.

## PCF8581/8581C

#### Reading

Fig. 10 Master reads after setting word address (WRITE word address; READ data).

Fig. 11 Master reads slave immediately after first byte (READ mode).

An unlimited number of data bytes can be read in one operation. The address is automatically incremented. If a read without setting the word address is performed after a write operation, the address pointer may point at a byte in the row after the previously written row. This occurs if, during writing, the three lowest address bits (column) rolled over.

## PCF8581/8581C

#### APPLICATION INFORMATION

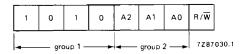

The PCF8581 slave address has a fixed combination 1010 as group 1, while group 2 is fully programmable (see Fig. 12).

Fig. 12 PCF8581 address.

Fig. 13 Application diagram.

#### Note

A0, A1 and A2 inputs must be connected to  $V_{\mbox{DD}}$  or  $V_{\mbox{SS}}$  but not left open-circuit.