# SMART POWER H-BRIDGE MOTOR DRIVES

#### **DESCRIPTION**

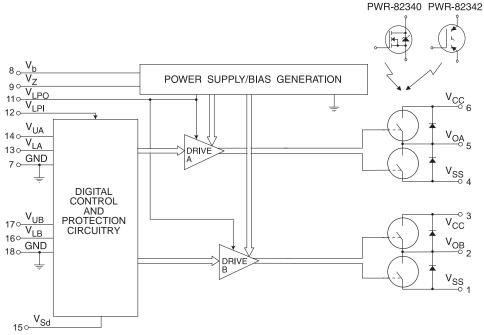

The PWR-82340 and PWR-82342 are 30 A H-bridge motor drive hybrids. The PWR-82340 has a 200 V rating and uses MOSFETs in the output stage while the PWR-82342 has a 500 V rating and an IGBT output stage. Both types have individual fast recovery diodes internally connected across the output drive transistors to clamp inductive flyback. This new series of Smart Power Motor Drives has CMOS Schmitt Trigger inputs for high noise immunity. High- and low-side input logic signals are XOR'd in each phase to prevent simultaneous turn-on of in-line transistors, thus eliminating a shootthru condition. The internal logic controls the high- and low-side gate drives for each phase and can operate from +5 to +15 V logic levels. The internal power supply provides a constant voltage source to the floating high side gate drives. This provides constant output performance for switching frequencies from DC to 50 kHz.

#### **APPLICATIONS**

Packaged in small cases, these hybrids are an excellent choice for high performance, high reliability motor drives for military and aerospace servo-amps and speed controls. Among the many applications are robotics; electromechanical valve assemblies; actuator systems for flight control surfaces on military and commercial aircraft; antenna and radar positioning; fan and blower motors for environmental conditioning; thrust and vector position control of mini subs, drones, and RPV's; compressor motors for cryogenic coolers; and high-power inverters. The PWR-82340/342 hybrids are ideal for harsh military environments where shock, vibration, and temperature extremes are evident, such as missile applications where fin actuator systems control missile direction. The PWR-82340 and PWR-82342 operate over the -55°C to +125°C temperature range and are available with military processing.

#### **FEATURES**

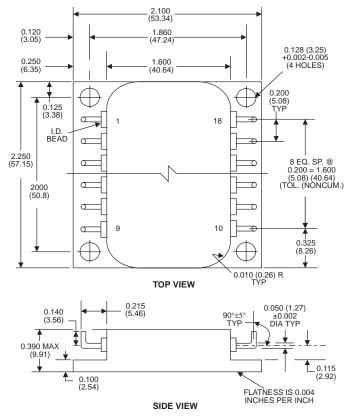

- Small Size (2.25" x 2.1" x 0.39")

- 200 V and 500 V Capability

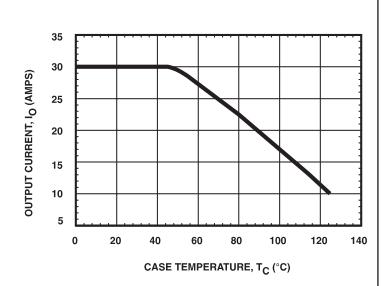

- 30 A Current Capability

- High-Efficiency MOSFET or IGBT Drive Stage

- Direct Drive from PWM

- Drives Brushless DC or Brush Motors

- Four Quadrant Operation

- 0.85 °C/W θ j-c Max

- Military Processing Available

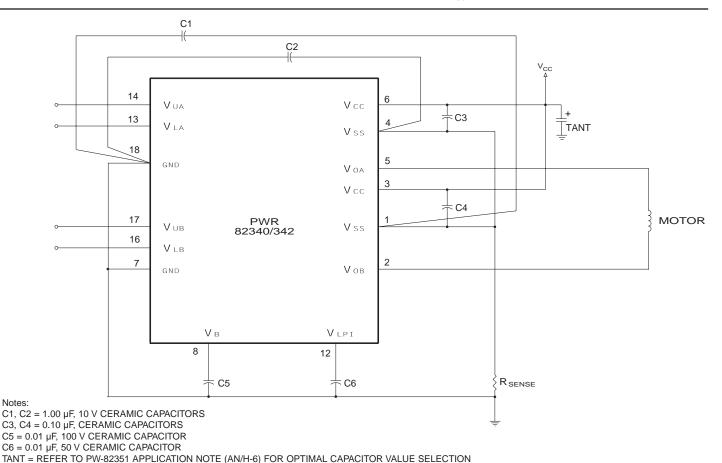

NOTE: Pins 3 and 6 are internally connected; Pins 7 and 18 are internally connected.

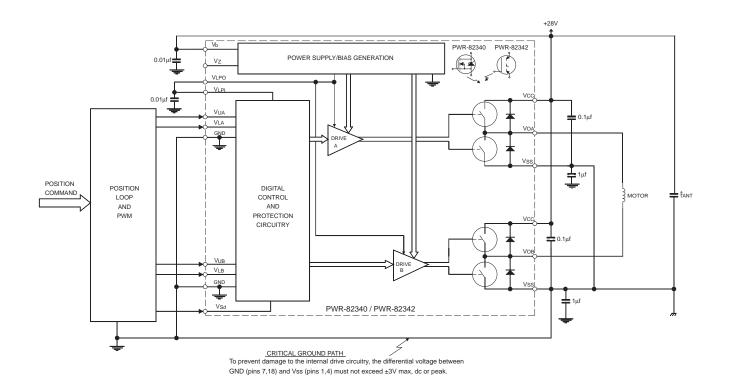

FIGURE 1. PWR-82340/342 BLOCK DIAGRAM

| TABLE 1. PWR-82340 AND PWR-82342 ABSOLUTE MAXIMUM RATINGS $T_{c}$ = +25°C unless otherwise specified) |                                               |                        |                        |        |  |  |  |

|-------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------------|------------------------|--------|--|--|--|

| PARAMETER                                                                                             | SYMBOL                                        | PWR-82340 VALUE        | PWR-82342 VALUE        | UNITS  |  |  |  |

| SUPPLY VOLTAGE                                                                                        | V <sub>CC</sub>                               | 200                    | 500                    | V      |  |  |  |

| BIAS VOLTAGE                                                                                          | V <sub>b</sub>                                | 50                     | 50                     | V      |  |  |  |

| LOGIC POWER-IN VOLTAGE                                                                                | $V_{LPI}$                                     | 18                     | 18                     | V      |  |  |  |

| INPUT LOGIC VOLTAGE                                                                                   | V <sub>U</sub> V <sub>L</sub> V <sub>Sd</sub> | V <sub>LPI</sub> + 0.5 | V <sub>LPI</sub> + 0.5 | V      |  |  |  |

| OUTPUT CURRENT<br>CONTINUOUS<br>PULSED                                                                | I <sub>o</sub><br>I <sub>op</sub>             | 30<br>50               | 30<br>50               | A<br>A |  |  |  |

| OPERATING FREQUENCY                                                                                   | f <sub>O</sub>                                | 50                     | 25                     | kHz    |  |  |  |

| CASE OPERATING TEMPERATURE                                                                            | T <sub>C</sub>                                | -55 to +125            | -55 to +125            | °C     |  |  |  |

| CASE STORAGE TEMPERATURE                                                                              | T <sub>CS</sub>                               | -55 to +150            | -55 to +150            | °C     |  |  |  |

# TABLE 2. PWR-82340 AND PWR-82342 SPECIFICATIONS $T_C = +25^{\circ}C$ unless otherwise specified)

|                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                       |                                                                                                                                                                          | PWR-82340  |     | PWR-82342                                                            |            |     |                                                                    |                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----|----------------------------------------------------------------------|------------|-----|--------------------------------------------------------------------|--------------------------------------------------------------|

| PARAMETERS                                                                                                                                                                                                                                                                                                                                                                 | SYMBOL                                                                                                                | TEST CONDITIONS                                                                                                                                                          | MIN        | TYP | MAX                                                                  | MIN        | TYP | MAX                                                                | UNIT                                                         |

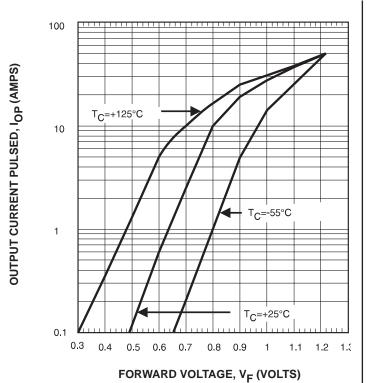

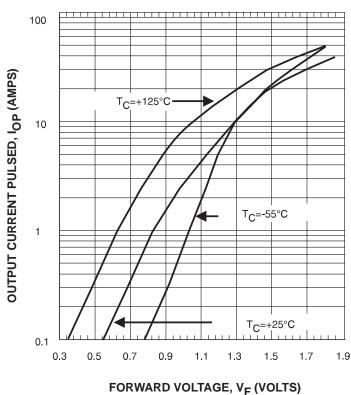

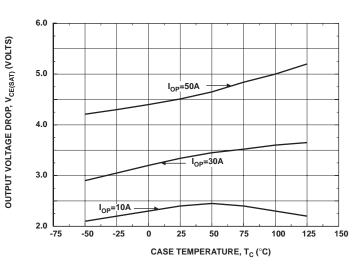

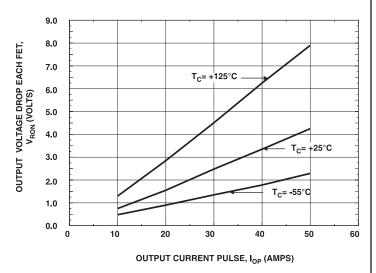

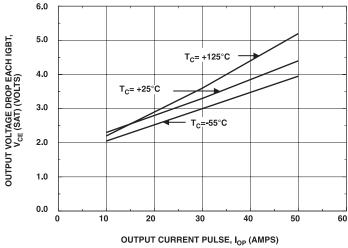

| OUTPUT Output Current Continuous (see FIGURES 19 and 15) Supply Voltage Output On Resistance (each FET)(see FIGURE 14A) Output Voltage Drop (each IGBT)(see FIGURES 14B) Instant Forward Voltage (flyback diode)(see FIGURE 13) Reverse Recovery Time (flyback diode) Reverse Leakage Current at T <sub>C</sub> = +25°C Reverse Leakage Current at T <sub>C</sub> = +125°C | I <sub>O</sub> V <sub>CC</sub> Ron V <sub>CE</sub> (SAT) V <sub>F</sub> t <sub>rr</sub> I <sub>r</sub> I <sub>r</sub> | see note 1<br>$I_0 = 30 \text{ A}$<br>$I_0 = 30 \text{ A}$<br>$I_p = 30 \text{ A}$ (see note 2)<br>$I_f = 1 \text{ A}$ , $I_r = 1 \text{ A}$<br>see note 3<br>see note 3 |            | 140 | 30<br>200<br>0.1<br>1.15<br>50<br>10                                 |            | 270 | 30<br>500<br>3.8<br>1.70<br>50<br>10                               | A<br>V<br>ohm<br>V<br>V<br>nsec<br>μA<br>mA                  |

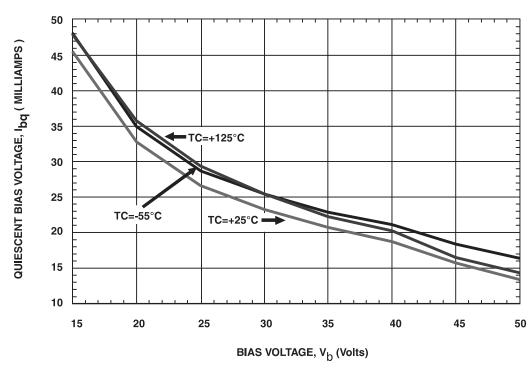

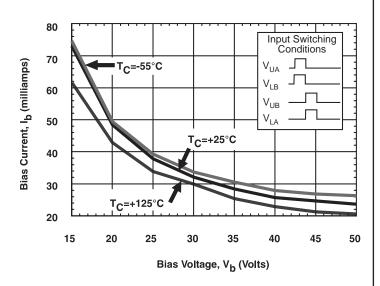

| BIAS SUPPLY Input Bias Voltage (T <sub>C</sub> = -55 to +125°C) Quiescent Bias Current (see note 4)(see FIGURE 16) Bias Current (T <sub>C</sub> = -55 to +125°C) (see FIGURES 17 and 18) Inrush Current (T <sub>C</sub> = -55 to +125°C) Logic Power Input Current                                                                                                         | V <sub>b</sub><br>Ibq<br>I <sub>b</sub><br>Iir<br>I <sub>LPI</sub>                                                    | $V = 28 \text{ V}$ $V_b = 28 \text{ V(see note 5)}$ $V_b = 28 \text{ V}$ $\text{see note 6}$                                                                             | 14<br>30   | 27  | 50<br>40<br>1.4<br>2                                                 | 15<br>24   | 27  | 50<br>35<br>1.4<br>2                                               | V<br>mA<br>mA                                                |

| INPUT SIGNALS (see FIGURE 7) Positive Trigger Threshold Voltage  Negative Trigger Threshold Voltage                                                                                                                                                                                                                                                                        | V <sub>P</sub>                                                                                                        | Pin Connections Pin 11 and 12 connected Pin 11 and 12 connected                                                                                                          | 6.8<br>4.0 |     | 10<br>7                                                              | 6.8<br>4.0 |     | 10<br>7                                                            | V                                                            |

| Positive Trigger Threshold Voltage<br>Negative Trigger Threshold Voltage                                                                                                                                                                                                                                                                                                   | V <sub>P</sub><br>V <sub>N</sub>                                                                                      | see note 6<br>see note 6                                                                                                                                                 | 2.2<br>0.9 |     | 3<br>2                                                               | 2.2<br>0.9 |     | 3<br>2                                                             | V<br>V                                                       |

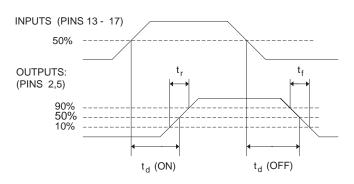

| SWITCHING CHARACTERISTICS (see FIGURE 2) Upper Drive: Turn-on propagation delay Turn-off propagation delay Shut down propagation delay Turn-on rise time Turn-off fall time Lower Drive: Turn-on propagation delay Turn-off propagation delay Shut down propagation delay Shut down propagation delay (see FIGURE 9) Turn-on rise time Turn-off fall time                  | td (on) td (off) tsa tr tf td (on) td (off) tsa tr tf                                                                 | Test 1 Conditions Pin 11 and 12 connected +15 V logic I <sub>O</sub> = 30 A peak PWR-82340 V <sub>CC</sub> = 140 V PWR-82342 V <sub>CC</sub> = 270 V                     |            |     | 840<br>1020<br>800<br>125<br>125<br>850<br>1000<br>800<br>125<br>125 |            |     | 810<br>860<br>810<br>100<br>150<br>800<br>870<br>770<br>100<br>150 | nsec<br>nsec<br>nsec<br>nsec<br>nsec<br>nsec<br>nsec<br>nsec |

| SWITCHING CHARACTERISTICS (see FIGURE 2) Upper Drive: Turn-on propagation delay Turn-off propagation delay Shut down propagation delay Turn-on rise time Turn-off fall time                                                                                                                                                                                                | td (on) td (off) tSd tr tf                                                                                            | Test 2 Conditions see note 6 +5 V logic l <sub>0</sub> = 30 A peak PWR-82340 V <sub>CC</sub> = 140 V PWR-82342 V <sub>CC</sub> = 270 V                                   |            |     | 1090<br>1315<br>1100<br>125<br>125                                   |            |     | 1050<br>1150<br>850<br>100<br>150                                  | nsec<br>nsec<br>nsec<br>nsec<br>nsec                         |

## PWR-82340/82342 Errata Sheet

This errata sheet replaces the section on INPUT SIGNALS in Table 2 on page 2.

#### TABLE 2. PWR-82340/82342 SPECIFICATION

(T<sub>C</sub> = +25°C Unless Otherwise Specified)

|                                    | PWR-823340 |                         |     |     | PWR-823342 |     |     |      |      |

|------------------------------------|------------|-------------------------|-----|-----|------------|-----|-----|------|------|

| PARAMETER                          | SYMBOL     | TEST CONDITIONS         | MIN | TYP | MAX        | MIN | TYP | MAX  | UNIT |

| INPUT SIGNALS (See Figure 7)       |            | Pin Connections         |     |     |            |     |     |      |      |

| Positive Trigger Threshold Voltage | $V_{P}$    | Pin 11 and 12 connected |     |     | 12.9       |     |     | 12.9 | V    |

| Negative Trigger Threshold Voltage | $V_N$      | Pin 11 and 12 connected | 2.1 |     |            | 2.1 |     |      | V    |

| Hysteresis Voltage                 | $V_{H}$    | Pin 11 and 12 connected | 1.6 |     | 10.8       | 1.6 |     | 10.8 | V    |

| Positive Trigger Threshold Voltage | $V_P$      | See note 6              |     |     | 4.3        |     |     | 4.3  | V    |

| Negative Trigger Threshold Voltage | $V_N$      | See note 6              | 0.9 |     |            | 0.9 |     |      | V    |

| Hysteresis Voltage                 | $V_{H}$    | See note 6              | 0.3 |     | 3.6        | 0.3 |     | 3.6  | V    |

| TABLE 2. PWR-82340 AND PWR-82342 SPECIFICATIONS (CONTINUED)  (T <sub>C</sub> = 25°C unless otherwise specified)                                                                        |                                                        |                                                                                                                                        |                   |           |                                    |                   |     |                                   |                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------|------------------------------------|-------------------|-----|-----------------------------------|--------------------------------------|

|                                                                                                                                                                                        | PWR 82340                                              |                                                                                                                                        |                   | PWR 82342 |                                    |                   |     |                                   |                                      |

| PARAMETERS                                                                                                                                                                             | SYMBOL                                                 | TEST CONDITIONS                                                                                                                        | MIN               | TYP       | MAX                                | MIN               | TYP | MAX                               | UNIT                                 |

| SWITCHING CHARACTERISTICS (continued) LowerDrive: Turn-on propagation delay Turn-off propagation delay Shut-down propagation delay (see FIGURE 9) Turn-on Rise Time Turn-off Fall Time | td(on) td(off) tsd tr tf                               | Test 2 Conditions  see note 6 +5V logic I <sub>O</sub> = 30 A peak PWR-82340 V <sub>CC</sub> = 140 V PWR-82342 V <sub>CC</sub> = 270 V |                   |           | 1125<br>1290<br>1100<br>125<br>125 |                   |     | 1050<br>1150<br>850<br>100<br>150 | nsec<br>nsec<br>nsec<br>nsec<br>nsec |

| DEAD TIME                                                                                                                                                                              | t <sub>dt</sub>                                        |                                                                                                                                        | 400               |           |                                    | 500               |     |                                   | nsec                                 |

| MINIMUM PULSE WIDTH                                                                                                                                                                    | t <sub>pw</sub>                                        |                                                                                                                                        | 150               |           |                                    | 175               |     |                                   | nsec                                 |

| THERMAL  Maximum Thermal Resistance  Maximum Lead Soldering Temp.  Junction Temperature Range  Case Operating Temperature  Case Storage Temperature                                    | θj-c<br>Ts<br>Tj<br>T <sub>CO</sub><br>T <sub>CS</sub> | each transistor<br>see note 7                                                                                                          | -55<br>-55<br>-55 |           | 0.85<br>250<br>150<br>125<br>150   | -55<br>-55<br>-55 |     | 0.85<br>250<br>150<br>125<br>150  | ာ့ သို့<br>သို့ သို့                 |

| WEIGHT                                                                                                                                                                                 |                                                        |                                                                                                                                        |                   |           | 3.88<br>(110)                      |                   |     | 3.88<br>(110)                     | oz<br>(g)                            |

Notes: 1. For Hi-Rel applications, derating per MIL-S-19500 should be observed. (Derate V<sub>cc</sub> to 70%.)

#### **INTRODUCTION**

The PWR-82340 and PWR-82342 are 30 A motor drive hybrids rated at 200 V and 500 V respectively. The PWR-82340 uses a MOSFET output stage and the PWR-82342 has an IGBT output stage for high speed, high current, and high efficiency operation. The PWR-82342 also offers high voltage performance of an IGBT for use in 270 V systems. These motor drives are ideal for use in high performance motion control systems, servo amplifiers, and motor speed control designs. Furthermore, Multiaxis systems requiring multiple drive stages can benefit from the small size of these power drives.

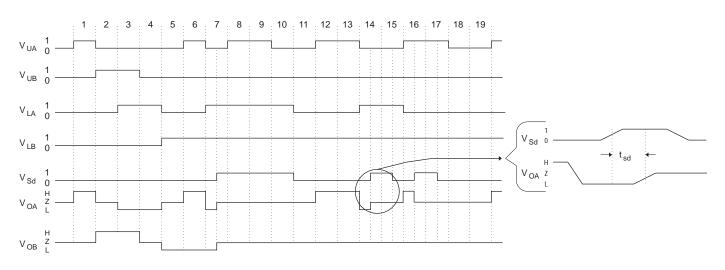

The PWR-82340/342 can be driven directly from a PWM, DSP, or a custom ASIC that supplies digital signals to control the

(Reference TABLE 2 also.)

FIGURE 2. INPUT/OUTPUT TIMING RELATIONSHIPS

upper and lower transistors of each phase. These highly integrated drive stages have Schmitt trigger digital inputs that control the high and low side of each phase. Digital protection of each phase eliminates an in-line firing condition by preventing simultaneous turn-on of both the upper and lower transistors. The logic controls the high- and low-side gate drivers. Operation from +5 to +15 V logic levels can be programmed by applying the appropriate voltage to pin 12 (V<sub>LPI</sub>). The PWR-82340/342 has a ground referenced low-side gate drive. An internal DC-DC converter supplies a floating output to each of the two high-side drives. This provides a continuous high-side gate drive even during a motor stall. Pin 11 (V<sub>LPO</sub>) supplies a +15 V output, which can be used to power the internal logic when system usage requires +15 V logic. The high- and low-side gate drivers control the Nchannel MOSFET or IGBT output stage. The MOSFETs used in the PWR-82340 allow output switching up to 50 kHz, while the high-speed IGBTs in the PWR-82342 can switch at 25 kHz. A flyback diode parallels each output transistor and controls the regenerative energy produced by the motor. These fast recovery diodes have faster reverse switching times than the intrinsic body diode of the MOSFETs used in the PWR-82340. They also protect the IGBTs used in the PWR-82342 from exceeding their Emitter-to-Collector breakdown voltage. Use of a copper case and solder attachment of the output transistors achieves a low thermal resistance of 0.85°C/W maximum. Care should be taken to adequately heatsink these motor drives to maintain a case temperature of +125°C. Junction temperatures should not exceed +150°C. The PWR-82340/342 does not have internal short circuit or overcurrent protection which, if required, must be added externally to the hybrid.

<sup>2.</sup> Pulse width  $\leq$  300  $\mu$ s, duty cycle  $\leq$  2%.

<sup>3.</sup> For PWR-82340  $V_{CC}$  = 140 V,  $V_{U}$ ,  $V_{L}$  = logic '0' and for PWR-82342  $V_{CC}$  = 350 V,  $V_{U}$ ,  $V_{L}$  = logic '0.'

<sup>4.</sup>  $V_U$ ,  $V_L$  = logic '0' on pins 13 to 17.

<sup>5.</sup> For PWR-82340  $f_O$  = 30 kHz and for PWR-82342  $f_O$  = 10 kHz.

<sup>6.</sup> Pin 12 connected to external +5 V supply.

<sup>7.</sup> Solder 1/8" from case for 5 seconds maximum.

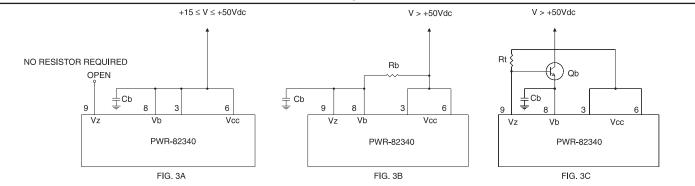

#### **BIAS VOLTAGES**

The PWR-82340 and PWR-82342 motor drive hybrids only require a single power supply for operation. The hybrid generates two independent, floating supplies, which eliminates the need for external bias voltages for each phase.

In order for the internal power supply to generate these voltages, the input bias voltage ( $V_b$ ) must be from +15 to +50 Vdc. In most avionic systems this can be accomplished by connecting the  $V_b$  pin to the MIL-STD-704D, +28 Volt bus. See FIGURE 3A.

If the system bus voltage is greater than +50 Vdc (and a lower voltage is not available), then the  $V_b$  pin and  $V_z$  pin can be tied

together with an external power resistor  $(R_b)$  and connected from these pins to the system power bus. See FIGURE 3B.

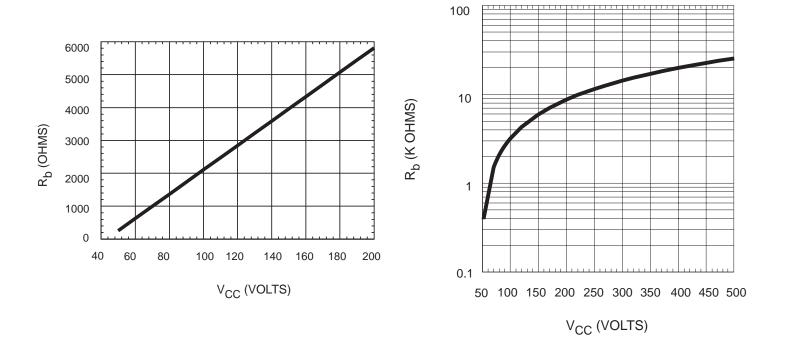

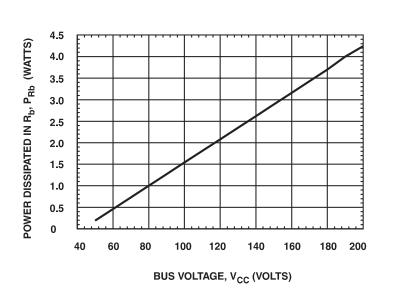

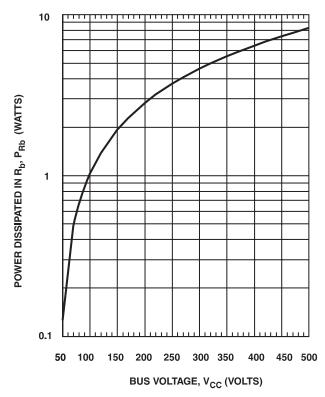

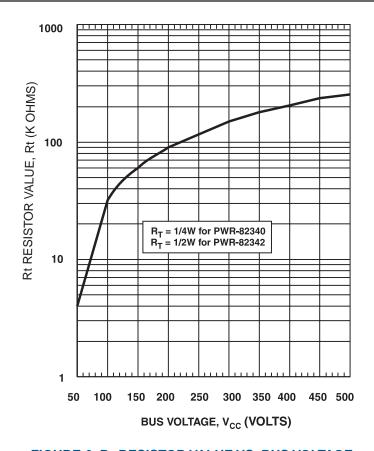

See FIGURES 4 and 5 for bias resistor characteristics.

If additional power dissipation in  $R_b$  is a concern, FIGURE 3C shows a more efficient design, using a low-power resistor ( $R_0$ ) and an additional transistor. To determine the proper resistor to use, refer to FIGURE 6.

If there is another voltage available in the system in the +15 to +50 VDC range, then this voltage can be directly connected to the  $V_b$  pin of the hybrid. In any case, a 0.01  $\mu$ f decoupling capacitor ( $C_b$ ) must be connected between  $V_b$  (pin 8) and GND.

FIGURE 3. CONNECTION TO BUS VOLTAGE TO DEVELOP PROPER INPUT BIAS VOLTAGE

FIGURE 4A. PWR-82340

FIGURE 4B. PWR-82342

FIGURE 4. BIAS RESISTOR VALUE VS. BUS VOLTAGE

FIGURE 5A. PWR-82340

FIGURE 5B. PWR-82342

FIGURE 5. POWER DISSIPATED IN BIAS RESISTOR (Rb) VS. BUS VOLTAGE

FIGURE 6.  $R_T$  RESISTOR VALUE VS. BUS VOLTAGE

#### **DIGITALLY CONTROLLED INPUTS**

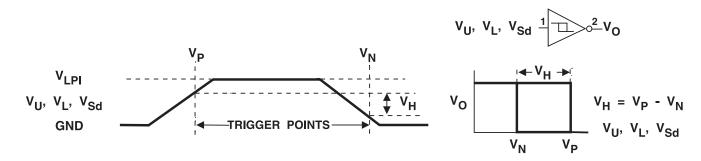

The PWR-82340 and PWR-82342 use Schmitt triggered digital inputs (with hysteresis) to ensure high noise immunity. The trigger switches at different points for positive and negative going signals. Hysteresis voltage ( $V_H$ ) is the difference between the positive going voltage ( $V_P$ ) and the negative going voltage ( $V_N$ ) (see FIGURE 7). The digital inputs have programmable logic levels, which allows the hybrid to be used with different types of control logic with an input voltage range of +5 to +15 V, such as TTL or CMOS logic. The PWR-82340 and PWR-82342 internal power supply generates a +15 Vdc ( $V_{LPO}$ ) on pin 11. This output can only be used to power the internal digital circuitry within the hybrid. **Do not use this +15 V output to power any circuitry**

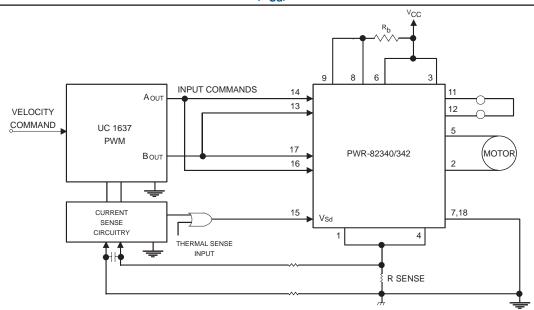

external to the hybrid. Pin 12 is the logic power input ( $V_{LPI}$ ) for the digital circuitry inside the hybrid. A 0.01 uF, 50 V ceramic capacitor must be placed between this pin (12) and GND as close to the hybrid as possible. When using 15 V control circuitry, the logic power input (pin 12) can be connected directly to the logic power output (pin 11) of the hybrid. There is no need for an additional external power supply. When using 5 V control logic, an external +5 VDC supply must be connected between pin 12 of the hybrid, and GND — leave Pin 11 open (N/C). The control circuitry can be as simple as a PWM, or as sophisticated as a microprocessor or custom ASIC, depending on the system requirements. The Block Diagram in FIGURE 8 shows a typical interface of the PWR-82340 and PWR-82342 with a motor and control logic in a Servo-Amp System.

FIGURE 7. HYSTERESIS DEFINITION AND CHARACTERISTICS

FIGURE 8. PWR-82340/342 TYPICAL INTERFACE WITH A MOTOR AND PWM

#### SHUT-DOWN INPUT (V<sub>Sd</sub>)

Pin 15 ( $V_{Sd}$ ) provides a digital shut-down input, which allows the user to completely turn off both the upper and lower output transistors in both phases. Application of a logic '1' to the  $V_{Sd}$  input will latch the Digital Control/Protection circuitry thereby turning off all output transistors. The Digital Control/Protection circuitry remains latched in the off state and will not respond to signals on the  $V_L$  or  $V_U$  inputs while the  $V_{Sd}$  has a logic '1' applied. When the user or the sense circuitry (as in FIGURE 10) returns the  $V_{Sd}$  input to a logic '0,' and then the user sets the  $V_L$  and  $V_U$  inputs to a logic '0' the output of the Digital Control/Protection circuitry will clear the internal latch. When the next rising edge (see FIGURE 9) occurs on the  $V_L$  or  $V_U$  digital inputs, the output transistors will respond to the corresponding digital input. This feature can be used with external current limit or temperature sense circuitry to disable the drive if a fault condition occurs (see FIGURE 10).

#### INTERNAL PROTECTION CIRCUITRY

The hybrid contains digital protection circuitry, which prevents inline transistors from conducting simultaneously. This, in effect, would short circuit the power supply and would damage the output stage of the hybrid. The circuitry allows only proper input signal patterns to cause output conduction. FIGURE 9 and TABLE 3 (see page 13) show these timing relationships. If an improper input requested that the upper and lower transistors of the same phase conduct together, the output would be a high impedance until removal of the illegal code from the input of the PWR- 82340 or PWR-82342. A dead time of 500 nsec minimum should still be maintained between the signals at the  $\rm V_U$  and  $\rm V_L$  pins; this ensures the complete turn off of any transistor before turning on its associated in-line transistor.

FIGURE 9. SHUT-DOWN (V<sub>Sd</sub>) TIMING RELATIONSHIPS

FIGURE 10. FUNCTIONAL SHUT-DOWN INPUT USED WITH CURRENT-SENSING CIRCUITRY

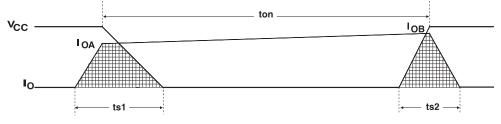

#### **PWR-82340 POWER DISSIPATION (SEE FIGURE 11)**

There are three major contributors to power dissipation in the motor driver: conduction losses, switching losses, and flyback diode losses.

V<sub>CC</sub> = 140 V(Bus Voltage)

$I_{OA} = 20 \text{ A} \text{ (see FIGURE 11)}; I_{OB} = 30 \text{ A}; \text{ (see FIGURE 11)}$

$t_{on}$  = 20  $\mu$ s (see FIGURE 11); T = 40  $\mu$ s (period)

Ron = 0.1  $\Omega$  (on resistance see TABLE 2,  $I_0$  = 30 A,  $T_c$  = 25 °C)

$t_{\rm S1}$  = 250 ns (see FIGURE 11);  $t_{\rm S2}$  = 250 ns (see FIGURE 11)

$f_0 = 25 \text{ kHz(switching frequency)}$

$V_f$  is the diode forward voltage, Table 2,  $I_o = 30 \text{ A}$ ,  $T_c = 25 \text{ °C}$

$V_{f}(avg) = 1.15 V$

If is the diode forward current

#### 1. Conduction Losses (P<sub>C</sub>)

$$P_C = I(t)^2 \times R_{on} = I \text{ motor rms}^2 \times R_{on}$$

I motor rms =

$$\sqrt{\left(I_{OB}^2 - I_{OB}(I_{OB} - I_{OA}) + \frac{(I_{OB} - I_{OA})^2}{3}\right)\left(\frac{t_{on}}{T}\right)}$$

I motor rms =

$$\sqrt{\left(30^2 - 30 (30 - 20) + \frac{(30 - 20)^2}{3}\right)\left(\frac{20}{40}\right)}$$

$$P_C$$

= (17.80 A)<sup>2</sup> x (0.1 Ω)

$P_C$  = 31.68 Watts

### 2. Switching Losses (P<sub>S</sub>)

$$P_S = \{V_{CC} [I_{OA} (t_{s1}) + I_{OB} (t_{s2})] f_o\} / 2$$

$P_S = \{140 [20 (250 ns) + 30 (250 ns)] 25k\} / 2$

$P_S = 21.88 \text{ Watts}$

#### 3. Flyback diode Losses (P<sub>df</sub>)

$$P_{df} = I_f \text{ (avg) x } V_f \text{ (avg)}$$

$$I_f \text{ (avg)} = [(I_{OB} + I_{OA})/2] / 2 = [(30 + 20)/2] / 2 = 12.5 \text{ A}$$

$$P_{df} = 12.5 A \times 1.15 V$$

$$P_{df} = 14.38 \text{ Watts}$$

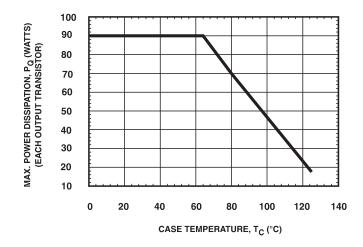

To calculate the maximum power dissipation of the output transistor as a function of the case temperature use the following equation. (Reference FIGURE 20 to ensure you don't exceed the maximum allowable power dissipation of each transistor.)

$$P_{Q} = P_{C} + P_{S}$$

To calculate Total Power dissipated in the hybrid use:

$$P_{Total} = \sum_{i=1}^{n} [P_{ci} + P_{si} + P_{dfi}]$$

where  $i = each$  transistor or diode.

#### **PWR-82342 POWER DISSIPATION (SEE FIGURE 11)**

There are three major contributors to power dissipation in the motor driver: conduction losses, switching losses, and flyback diode losses.

V<sub>CC</sub> = 270 V(Bus Voltage)

$I_{OA} = 20 \text{ A} \text{ (see FIGURE 11)}; I_{OB} = 30 \text{ A}; \text{ (see FIGURE 11)}$

$t_{on} = 50 \mu s$  (see FIGURE 11);  $T = 100 \mu s$  (period)

$V_{CE(SAT)} = 3.8 \text{ V} \text{ (see TABLE 2, } I_0 = 30 \text{ A, } T_c = 25 \text{ °C)}$

$t_{s1} = 300$  ns (see FIGURE 11);  $t_{s2} = 300$  ns (see FIGURE 11)

$f_0 = 10 \text{ kHz(switching frequency)}$

$V_f$  is the diode forward voltage, TABLE 2,  $I_o = 30 \text{ A}$ ,  $T_c = 25 \text{ }^{\circ}\text{C}$

$V_{f(avg)} = 1.70 V$

If is the diode forward current

#### 1. Conduction Losses (P<sub>C</sub>)

$$P_C = I(t)^2 \times V_{CE(SAT)} = I_{AVG} \times V_{CE(SAT)}$$

$$I_{AVG} = \left(\frac{(I_{OB} + I_{OA})}{2}\right) \left(\frac{t_{on}}{T}\right)$$

$$IAVG = \left(\frac{(30+20)}{2}\right) \left(\frac{50}{100}\right)$$

$$P_C = (12.5 \text{ A}) \text{ x } (3.8 \text{ V})$$

$P_C = 47.50 \text{ Watts}$

#### 2. Switching Losses (P<sub>S</sub>)

$P_S = \{V_{CC} [I_{OA} (t_{s1}) + I_{OB} (t_{s2})]f_o\} / 2$

$P_S = \{270 [20 (300ns) + 30 (300ns)]10k\} / 2$

$P_S = 20.25 \text{ Watts}$

#### 3. Flyback diode Losses (P<sub>df</sub>)

$P_{df} = I_s \text{ (avg) } x V_f \text{ (avg)}$

$I_f$  (avg) = [( $I_{OB} + I_{OA}$ ) / 2] / 2 = [(30 + 20) / 2] / 2 = 12.5 A

$P_{df} = 12.5 A \times 1.70 V$

$P_{df} = 21.25 \text{ Watts}$

To calculate the maximum power dissipation of the output transistor as a function of the case temperature use the following equation. (Reference FIGURE 20 to ensure you don't exceed the maximum allowable power dissipation of each transistor.)

$$P_0 = P_C + P_S$$

To calculate Total Power dissipated in the hybrid use:

$$P_{Total} = \sum_{i=1}^{4} [P_{ci} + P_{si} + P_{dfi}]$$

where  $i =$  each transistor or diode.

FIGURE 11. OUTPUT CHARACTERISTICS

#### **GROUND CONNECTIONS**

#### LAYOUT AND EXTERNAL COMPONENTS

Important Information - The following information regarding layout guidelines and required external components is critical to the proper operation of these motor drives.

External connections can be easily made to the hybrid by any of the following methods:

- · Solder a wire around each pin.

- · Use a printed circuit board with a cutout that will enable the printed circuit board to slide over the pins.

Permanent damage will result to the motor drive if the user does not make the following recommended ground connections that will ensure the proper operation of the hybrid.

The V<sub>b</sub> and logic grounds are on pins 7 and 18 (GND). The Vss connections for the output stage are on pins 1 and 4 (V<sub>ss</sub>). To prevent damage to the internal drive circuitry, the differential voltage between GND (pins 7, 18) and V<sub>ss</sub> (pins 1, 4) must not exceed ±3 V max, dc or peak. This includes the combined voltage drop of the associated ground paths and the voltage drop across  $\mathbf{R}_{\text{sense}}$  (see FIGURE 12). For example, a value for  $R_{sense}$  of 0.025  $\Omega$  will give a voltage drop of 1.25 V at 50 A and allow enough margin for the voltage drop in the ground conductors. Locate R<sub>sense</sub> 1" - 2" maximum from the hybrid. It is critical that all ground connections be as short, and of lowest impedance, as the system allows.

C1 and C2 are 1 µF, 10 V ceramic capacitors that provide a low ac impedance between each V<sub>ss</sub> pin and GND. You must use one capacitor for each V<sub>ss</sub> pin-to-GND connection (total of two capacitors in all). These capacitors are independent of the type of drive scheme used. Since placement of these capacitors is critical, place these capacitors across the hybrid, if possible. Please note, on FIGURE 12, that C1 and C2 must go directly from terminal to terminal on the hybrid — do not daisy chain along the ground return.

C3 and C4 are the 0.1 µf ceramic bypass capacitors that suppress high frequency spiking. The voltage rating should be 2x the maximum system voltage. These capacitors should be located as close to the hybrid as possible.

Care must be taken to control the regenerative energy produced by the motor in order to prevent excessive voltage spiking on the V<sub>cc</sub> line. Accomplish this by placing a capacitor or clamping diode between  $V_{cc}$  and the high power ground return.

FIGURE 13A. PWR-82340 TYPICAL FORWARD VOLTAGE DROP OF FLYBACK DIODES

FIGURE 13B. PWR-82342 TYPICAL FORWARD VOLTAGE DROP OF FLYBACK DIODES

FIGURE 14A. PWR-82340 TYPICAL ON RESISTANCE VARIATION WITH TEMPERATURE

FIGURE 14B. PWR-82342 TYPICAL VCE(SAT)

VARIATION WITH TEMPERATURE

FIGURE 15A. PWR-82340 TYPICAL OUTPUT ON VOLTAGE DROP VERSUS OUTPUT CURRENT

FIGURE 15B. PWR-82342 TYPICAL OUTPUT ON VOLTAGE DROP VERSUS OUTPUT CURRENT

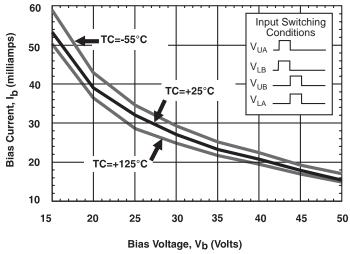

FIGURE 16. PWR-82340/342 TYPICAL QUIESCENT BIAS CURRENT VERSUS BIAS VOLTAGE

FIGURE 17A. PWR-82340 TYPICAL BIAS CURRENT VERSUS BIAS VOLTAGE AT F0 = 30 KHZ

FIGURE 17B. PWR-82342 TYPICAL BIAS CURRENT VERSUS BIAS VOLTAGE AT F<sub>0</sub> = 10 KHZ

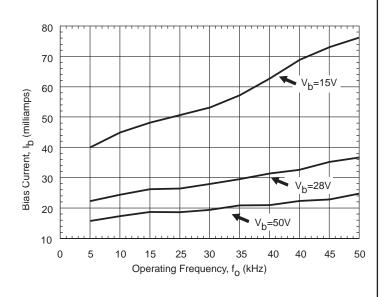

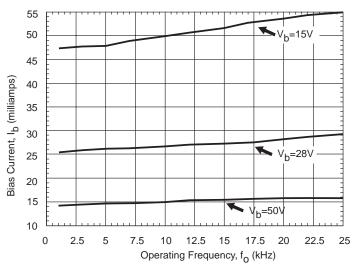

FIGURE 18A. PWR-82340 BIAS CURRENT VERSUS OPERATING FREQUENCY

FIGURE 18B. PWR-82342 BIAS CURRENT VERSUS OPERATING FREQUENCY

#### **MOUNTING**

The package bolts to part of the chassis or even the motor assembly itself, depending on system requirements. In applications where this isn't convenient, the hybrid can be mounted to its own heatsink. The heat transfer in a hybrid is from semiconductor junction to the bottom of the hybrid case. The flatness and maximum temperature of this mounting surface are critical to proper performance and reliability, because this is the only method of dissipating the power created in the hybrid. Use a mounting surface flatness of 0.004 inches/inch maximum. This interface can be improved with the use of a thermal compound or pad. The heatsink should be designed to insure that the case temperature does not exceeded +125°C.

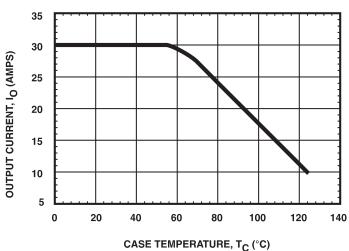

**FIGURE 19A. PWR-82340 MAXIMUM ALLOWABLE CONTINUOUS OUTPUT CURRENT VERSUS CASE TEMPERATURE**

FIGURE 19B. PWR-82342 MAXIMUM ALLOWABLE CONTINUOUS OUTPUT **CURRENT VERSUS CASE TEMPERATURE**

FIGURE 20. PWR-82340 AND PWR-82342 MAXIMUM ALLOWABLE POWER DISSIPATION OF EACH OUTPUT TRANSISTOR VERSUS CASE **TEMPERATURE**

| TABLE 3. INPUT-OUTPUT TRUTH TABLE    |                                      |                                      |                                      |                                 |                            |                                      |  |  |

|--------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|---------------------------------|----------------------------|--------------------------------------|--|--|

|                                      | OUTPUTS                              |                                      |                                      |                                 |                            |                                      |  |  |

| UPP                                  | ERS                                  | LOW                                  | ERS                                  | CON                             | TROL                       | COIPOIS                              |  |  |

| V <sub>UA</sub>                      | V <sub>UB</sub>                      | V <sub>LA</sub>                      | V <sub>LB</sub>                      | VSd                             | V <sub>OA</sub>            | V <sub>OB</sub>                      |  |  |

| 0<br>0<br>1<br>1<br>1<br>X<br>0<br>X | 0<br>1<br>0<br>1<br>X<br>1<br>0<br>X | 1<br>1<br>0<br>0<br>1<br>X<br>0<br>X | 1<br>0<br>1<br>0<br>X<br>1<br>0<br>X | 0<br>0<br>0<br>0<br>0<br>0<br>0 | L<br>H<br>H<br>Z<br>X<br>Z | L<br>H<br>L<br>H<br>X<br>Z<br>Z<br>Z |  |  |

|                                      | H = hig                              |                                      |                                      | level, X                        |                            | vant,                                |  |  |

NOTE: Dimensions in inches (mm).

FIGURE 21. PWR-82340 AND PWR-82342 MECHANICAL OUTLINE

| TABLE 4. PIN ASSIGNMENTS |                 |     |                 |  |  |  |  |  |

|--------------------------|-----------------|-----|-----------------|--|--|--|--|--|

| PIN                      | FUNCTION        | PIN | FUNCTION        |  |  |  |  |  |

| 1                        | V <sub>SS</sub> | 18  | GND             |  |  |  |  |  |

| 2                        | V <sub>OB</sub> | 17  | V <sub>UB</sub> |  |  |  |  |  |

| 3                        | V <sub>cc</sub> | 16  | $V_{LB}$        |  |  |  |  |  |

| 4                        | V <sub>SS</sub> | 15  | VSd             |  |  |  |  |  |

| 5                        | V <sub>OA</sub> | 14  | $V_{UA}$        |  |  |  |  |  |

| 6                        | V <sub>CC</sub> | 13  | $V_{LA}$        |  |  |  |  |  |

| 7                        | GND             | 12  | $V_{LPI}$       |  |  |  |  |  |

| 8                        | V <sub>b</sub>  | 11  | $V_{LPO}$       |  |  |  |  |  |

| 9                        | V <sub>Z</sub>  | 10  | N/C             |  |  |  |  |  |

Note: Pins 3 and 6 are internally connected; Pins 7 and 18 are internally connected.

# **NOTES**

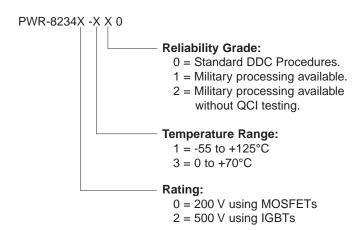

#### **ORDERING INFORMATION**

The information provided in this data sheet is believed to be accurate; however, no responsibility is assumed by Data Device Corporation for its use, and no license or rights are granted by implication or otherwise in connection therewith.

Specifications are subject to change without notice.

105 Wilbur Place, Bohemia, New York 11716-2482

For Technical Support - 1-800-DDC-5757 ext. 7420

Headquarters - Tel: (631) 567-5600 ext. 7420, Fax: (631) 567-7358

**Southeast -** Tel: (703) 450-7900, Fax: (703) 450-6610 **West Coast -** Tel: (714) 895-9777, Fax: (714) 895-4988 **Europe -** Tel: +44-(0)1635-811140, Fax: +44-(0)1635-32264 **Asia/Pacific -** Tel: +81-(0)3-3814-7688, Fax: +81-(0)3-3814-7689

World Wide Web - http://www.ddc-web.com

G-06/99-500 PRINTED IN THE U.S.A.