# **CLF11 Series Compact Linear Flash Memory Card** 8, 16 and 32 MB (Intel Strata Flash)

#### **GENERAL DESCRIPTION**

The CLF11 Series Compact Flash memory cards offer a low cost linear Flash solid state storage solution for code and data storage, high performance disk emulation, mobile PC and embedded applications.

CLF11 series cards offer memory capacities from 8MB to 32MB, with 256kB (2x128kB) block erase size.

It is based on Intel MLC, Strata Flash memories. Cards are based on the J3 families of memory components: built with: 28F128J3, 28F640J3, 28F320J3

These flash devices support the Common Flash Interface (CFI) programming algorithm, a standard that allows system level software to evaluate the flash configuration, electrical characteristic, programming parameters and supported functions. CFI is intended to support future upgrades with universal programming algorithms, so there is no longer a need for continued programming software modification and updates. Systems should be able to recognize and support all devices to allow universal expansion/upgrade path.

The symmetrically blocked architecture and single supply (universal 3.3V or 5V for CLF11 cards) operation provides a cost effective, high performance, nonvolatile storage solution. The Compact Flash Card form factor offers an industry standard pinout and mechanical outline, allowing density upgrades without system design changes.

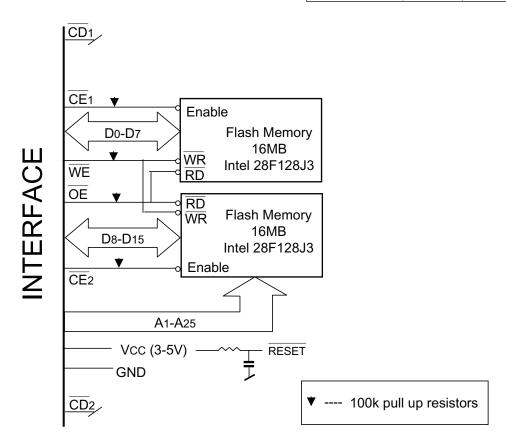

The CLF11 series is designed as a simple x16 linear array of Flash devices. Two Flash devices provide the lower and upper bytes for the 16 bit access. (See Functional Truth Table on page 5)

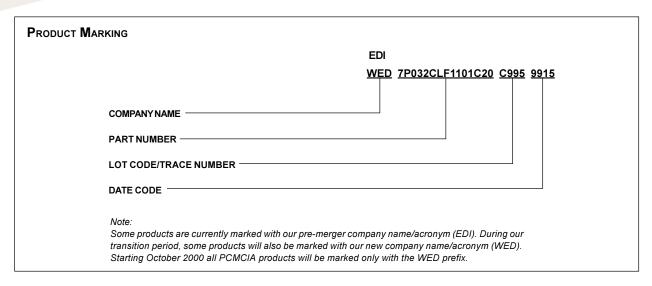

WEDC's standard cards are shipped with blank housings . Please contact WEDC sales representative for further information on Custom artwork.

#### **FFATURES**

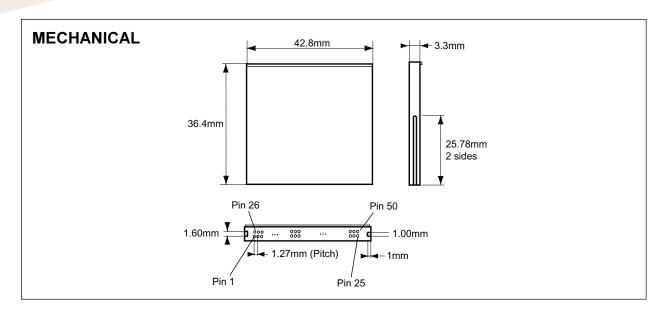

- Small Form Factor: CF compatible

- 36.4 x 42.8 x 3.3 mm

- Low cost Linear Flash Card

- Single Supply Operation

- 5V or 3.3V (Note 1)

- Fast Read Performance

- 200ns Maximum Access Time

- Based on MLC J3 Strata Flash Components

- Common Flash Interface (CFI) compliant

- Erase sector size: 2x 128kB

- High Performance Random Writes

- 6µs Typical per Byte Write Time, using 32Byte Write buffer

- Automated Write and Erase Algorithms

- High Write/Erase Endurance: 100,000 Write/Erase Cycles

- Low Power Consumption

- 150µA Standby Current

- 75mA Max Byte Write Current

#### Note 1:

CLF11 supports wide, universal operating voltage: 3V to 5V.

That means the card will work in 3.3V systems as well as in 5V systems. This feature may allow easy exchange of data between multiple and different systems and provide easy upgrade / expansion path.

## **CLF BLOCK DIAGRAM**

#### MANUFACTURER AND DEVICE ID CODES

| Device       | Manuf ID | Device ID |  |

|--------------|----------|-----------|--|

| Int 28F128J3 | 89h      | 18h       |  |

| Int 28F640J3 | 89h      | 17h       |  |

| Int 28F320J3 | 89h      | 16h       |  |

FIG 1. BLOCK DIAGRAM FOR 32MB CARD

- 1. A25..23 pulled down by 100kW resistors

- 2. Open for FVF0x; GND for FVF1x (3.3V operation)

Other configurations available: 8MB, 16MB, 16 bit only access, etc. Please contact sales department for more information

# For information regarding modes of operation, commands, and programming details for the memory components, please consult the Intel StrataFlash J3 data sheet.

http://developer.intel.com/design/flcomp/datashts/290667.htm

Writing commands to the CUI enables reading of device data, query, identifier codes, inspection and clearing of the status register, and, when V<sub>PEN</sub> = V<sub>PENH</sub>, block erasure, program, and lock-bit configuration.

The Block Erase command requires appropriate command data and an address within the block to be erased. The Byte/Word Program command requires the command and address of the location to be written. Set Block Lock-Bit commands require the command and block within the device to be locked. The Clear Block Lock-Bits command requires the command and address within the device.

The CUI does not occupy an addressable memory location. It is written when the device is enabled and WE is active. The address and data needed to execute a command are latched on the rising edge of WE or the first edge of CE1 or CE2 that disables the card. Standard microprocessor write timings are used.

#### **PINOUT**

| Pin | Signal name     | I/O | Function       | Active |

|-----|-----------------|-----|----------------|--------|

| 1   | GND             |     | Ground         |        |

| 2   | DQ3             | I/O | Data bit 3     |        |

| 3   | DQ4             | I/O | Data bit 4     |        |

| 4   | DQ5             | I/O | Data bit 5     |        |

| 5   | DQ6             | I/O | Data bit 6     |        |

| 6   | DQ7             | I/O | Data bit 7     |        |

| 7   | CE <sub>1</sub> | I   | Card enable 1  | LOW    |

| 8   | A11             | I   | Address bit 10 |        |

| 9   | ŌĒ              | I   | Output enable  | LOW    |

| 10  | A10             | I   | Address bit 11 |        |

| 11  | A9              | - 1 | Address bit 9  |        |

| 12  | A8              | 1   | Address bit 8  |        |

| 13  | Vcc             |     | Supply Voltage |        |

| 14  | <b>A</b> 7      | I   | Address bit 7  |        |

| 15  | A <sub>6</sub>  | I   | Address bit 6  |        |

| 16  | <b>A</b> 5      | I   | Address bit 5  |        |

| 17  | A4              | - 1 | Address bit 4  |        |

| 18  | Аз              | 1   | Address bit 3  |        |

| 19  | A <sub>2</sub>  | 1   | Address bit 2  |        |

| 20  | A <sub>1</sub>  | 1   | Address bit 1  |        |

| 21  | DQ₀             | I/O | Data bit 0     |        |

| 22  | DQ1             | I/O | Data bit 1     |        |

| 23  | DQ2             | I/O | Data bit 2     |        |

| 24  | A12             | I   | Address bit 12 |        |

| 25  | CD <sub>2</sub> | 0   | Card Detect 2  | LOW    |

| Pin | Signal name      | I/O | Function       | Active |

|-----|------------------|-----|----------------|--------|

| 26  | CD <sub>1</sub>  | 0   | Card Detect 1  | LOW    |

| 27  | DQ11             | I/O | Data bit 11    |        |

| 28  | DQ <sub>12</sub> | I/O | Data bit 12    |        |

| 29  | DQ13             | I/O | Data bit 13    |        |

| 30  | DQ14             | I/O | Data bit 14    |        |

| 31  | DQ15             | I   | Data bit 15    |        |

| 32  | CE <sub>2</sub>  | I   | Card enable 2  | LOW    |

| 33  | A22              | I   | Address bit 22 |        |

| 34  | A21              | ı   | Address bit 21 |        |

| 35  | A20              | ı   | Address bit 20 |        |

| 36  | WE               | I   | Write Enable   | LOW    |

| 37  | A24              | I   | Address bit 24 |        |

| 38  | Vcc              |     | Supply Voltage |        |

| 39  | <b>A</b> 19      | I   | Address bit 19 |        |

| 40  | <b>A</b> 18      | I   | Address bit 18 |        |

| 41  | A23              | I   | Address bit 23 |        |

| 42  | <b>A</b> 17      | I   | Address bit 17 |        |

| 43  | <b>A</b> 16      | - 1 | Address bit 16 |        |

| 44  | <b>A</b> 15      | 1   | Address bit 15 |        |

| 45  | A14              | I   | Address bit 14 |        |

| 46  | <b>A</b> 13      | ı   | Address bit 13 |        |

| 47  | DQ8              | I/O | Data bit 8     |        |

| 48  | DQ9              | I/O | Data bit 9     |        |

| 49  | DQ10             | 0   | Data bit 10    |        |

| 50  | GND              |     | Ground         | LOW    |

16 bit operation; using 2 independent Low and High byte enables: single byte access ability

#### CARD SIGNAL DESCRIPTION

| Symbol                            | Туре             | Name and Function                                                                                                                                                                                                                                               |

|-----------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1 - A25                          | INPUT            | ADDRESS INPUTS: An through A25 enable direct addressing of up to 64MB of memory on the card                                                                                                                                                                     |

| DQ0 - DQ15                        | INPUT/<br>OUTPUT | DATA INPUT/OUTPUT: DQ <sub>0</sub> THROUGH DQ <sub>15</sub> constitute the bi-directional databus. DQ <sub>0</sub> - DQ <sub>7</sub> constitute the lower (even) byte and DQ <sub>8</sub> - DQ <sub>15</sub> the upper (odd) byte. DQ <sub>15</sub> is the MSB. |

| CE <sub>1</sub>                   | INPUT            | CARD ENABLE 1: CE1 enables card accesses (See below the Functional Truth Table).                                                                                                                                                                                |

| ŌĒ                                | INPUT            | OUTPUT ENABLE: Active low signal enabling read data from the memory card.                                                                                                                                                                                       |

| WE                                | INPUT            | WRITE ENABLE: Active low signal gating write data to the memory card.                                                                                                                                                                                           |

| CD <sub>1</sub> , CD <sub>2</sub> | OUTPUT           | CARD DETECT 1 and 2: Provide card insertion detection. These signals are connected to ground internally on the memory card. The host socket interface circuitry shall supply 10K-ohm or larger pull-up resistors on these signal pins.                          |

| Vcc                               |                  | CARD POWER SUPPLY: (5.0V for FVF0x or 3V to 5V for FVF1x)                                                                                                                                                                                                       |

| GND                               |                  | GROUND:                                                                                                                                                                                                                                                         |

### FUNCTIONAL TRUTH TABLE

| Function Mode                               | CE <sub>2</sub> | CE <sub>1</sub> | ŌĒ | WE | D15-D8       | D7-D0         |

|---------------------------------------------|-----------------|-----------------|----|----|--------------|---------------|

| Standby Mode                                | Н               | Н               | Х  | Х  | High-Z       | High-Z        |

| Output Desible                              | L               | L               | Н  | Н  | High-Z       | High-Z        |

| Read Function<br>LOW Byte Access (8 bits)   | Н               | L               | L  | Н  | High-Z       | Even-Byte Out |

| Read Function<br>HIGH Byte Access (8 bits)  | L               | Н               | L  | Н  | Odd-Byte Out | High-Z        |

| Read Function<br>Word Access (16 bits)      | L               | L               | L  | Н  | Odd-Byte Out | Even-Byte Out |

| WRITE function<br>LOW Byte Access (8 bits)  | Н               | L               | Н  | L  | ×            | Even-Byte In  |

| WRITE function<br>HIGH Byte Access (8 bits) | L               | Н               | Н  | L  | Odd-Byte In  | ×             |

| WRITE function<br>Word Access (16 bits)     | L               | L               | Н  | L  | Odd-Byte In  | Even-Byte In  |

#### COMMAND DEFINITIONS TABLE

(THE COMMAND DEFINITIONS FOR STRATA FLASH MEMORY)

|                       |          | 1 <sup>st</sup> Bus Cycle |      |            | 2 <sup>nd</sup> Bus Cycle |      |      |

|-----------------------|----------|---------------------------|------|------------|---------------------------|------|------|

| Command Code Sequence | Bus Cyc. | Bus Opr                   | Addr | Data       | Bus Opr                   | Addr | Data |

| Read Array            | 1        | WR                        | Х    | FFh        |                           |      |      |

| Read Identifier Codes | 2        | WR                        | X    | 90h        | RD                        | IA   | ID   |

| Read Status Register  | 2        | WR                        | Х    | 70h        | RD                        | Х    | SRD  |

| Clear Status Register | 1        | WR                        | Х    | 50h        |                           |      |      |

| Block Erase           | 2        | WR                        | BA   | 20h        | WR                        | BA   | D0h  |

| Word/Byte Write       | 2        | WR                        | WA   | 40h or 10h | WR                        | WA   | WD   |

| Erase/Write Suspend   | 1        | WR                        | Х    | B0h        |                           |      |      |

| Erase/Write Resume    | 1        | WR                        | Х    | D0h        |                           |      |      |

#### ABSOLUTE MAXIMUM RATINGS (1)

| Operating Temperature TA (ambient) |                   |

|------------------------------------|-------------------|

| Commercial                         | 0°C to +70 °C     |

| Industrial                         | -40°C to +85 °C   |

| Storage Temperature                | 55°C to +110 °C   |

| Voltage on any pin relative to Vss | -0.5V to Vcc+0.5V |

#### Notes:

1. Stress greater than those listed under "Absolute Maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation at these or any other conditions greater than those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### **DC CHARACTERISTICS** VCC SUPPLY VOLTAGE 3V - 5V

| Symbol | Parameter                       | Notes                       | Тур      | Max      | Units | Test Conditions                                                                           |

|--------|---------------------------------|-----------------------------|----------|----------|-------|-------------------------------------------------------------------------------------------|

| Iccr   | Vcc Read Current<br>16 bit mode | Vcc = 3.3V<br>Vcc = 5.0V    | 35<br>45 | 55<br>65 | mA    | Vcc = Vcc MAX<br>tcycle = 200ns                                                           |

| Iccw   | Vcc Program Current             | Vcc = 3.3V<br>Vcc = 5.0V    | 35<br>40 | 60<br>70 | mA    | 1 device active                                                                           |

| Icce   | Vcc Erase Current               | Vcc = 3.3V<br>Vcc = 5.0V    | 35<br>40 | 70<br>80 | mA    | 1 device active                                                                           |

| IccsL  | Vcc Sleep Current               | Per 2 devices               | 160      | 250      | μA    | Vcc = 3.3V<br>Control Signals = Vcc<br>Reset = Viн (active)                               |

| lccs   | Vcc Standby Current             | Per 2 devices<br>TTL inputs |          | 300      | μА    | Vcc = 3.3V<br>Control Signals = V <sub>I</sub> H<br>Reset = V <sub>I</sub> L (not active) |

Notes:

CMOS Test Conditions: VIL = Vss ± 0.2V, VIH = Vcc ± 0.2V

# **Compact Linear Flash**

#### VCC SUPPLY VOLTAGE 3V - 5V

| Symbol | Parameter                            | Notes | Min | Max     | Units | Test Conditions                   |

|--------|--------------------------------------|-------|-----|---------|-------|-----------------------------------|

| liL    | Input Leakage Current                | 1, 2  |     | ±20     | μΑ    | Vcc = VccMAX Vin =Vcc or Vss      |

| ILO    | Output Leakage Current               | 1     |     | ±20     | μА    | Vcc = VccMAX<br>Vout = Vcc or Vss |

| VIL    | Input Low Voltage                    | 1     | 0   | 0.8     | V     |                                   |

| VIH    | Input High Voltage                   | 1     | 2.0 | Vcc+0.5 | V     |                                   |

| Vol    | Output Low Voltage                   | 1     |     | 0.4     | V     | IoL = 2mA                         |

| Vон    | Output High Voltage                  | 1     | 2.4 | 3.2     | V     | Iон = -2.0mA                      |

| VLKO   | Vcc Erase/Program<br>Lockout Voltage |       | 1   | 2.0     | V     |                                   |

#### Notes:

- 1. Values are the same for all card densities.

- 2. Exceptions: Leakage currents on CE1, OE and WE will be < 500 µA when VIN = GND due to internal pull-up resistors. Leakage currents on RST will be <150µA when V<sub>IN</sub>=V<sub>CC</sub> due to internal pull-down resistor.

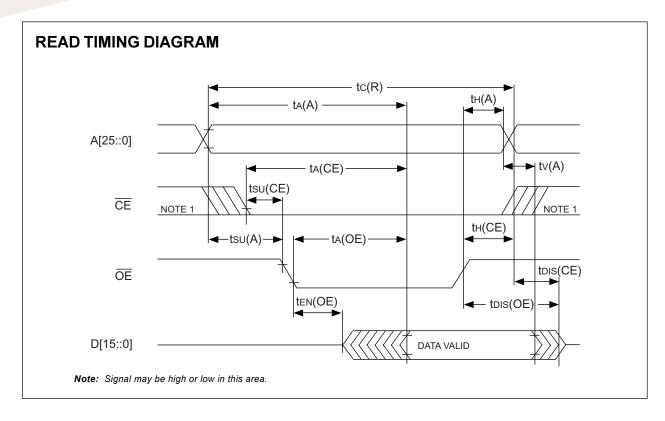

#### **AC CHARACTERISTICS** READ TIMING PARAMETERS (1)

|                       |                                               | 200 | Ons |      |

|-----------------------|-----------------------------------------------|-----|-----|------|

| SYMBOL(PCMCIA)        | Parameter                                     | Min | Max | Unit |

| tc(R)                 | Read Cycle Time                               | 200 |     | ns   |

| t <sub>a</sub> (A)    | Address Access Time                           |     | 200 | ns   |

| t <sub>a</sub> (CE)   | Card Enable Access Time                       |     | 200 | ns   |

| t <sub>a</sub> (OE)   | Output Enable Access Time                     |     | 100 | ns   |

| t <sub>su</sub> (A)   | Address Setup Time                            |     | 20  | ns   |

| t <sub>su</sub> (CE)  | Card Enable Setup Time                        |     | 0   | ns   |

| th(A)                 | Address Hold Time                             |     | 20  | ns   |

| t <sub>h</sub> (CE)   | Card Enable Hold Time                         |     | 20  | ns   |

| t <sub>v</sub> (A)    | Output Hold from Address Change               |     | 0   | ns   |

| t <sub>dis</sub> (CE) | Output Disable Time from CE                   |     | 90  | ns   |

| t <sub>dis</sub> (OE) | Output Disable Time from OE                   |     | 90  | ns   |

| t <sub>en</sub> (CE)  | Output Enable Time from CE                    | 5   |     | ns   |

| t <sub>en</sub> (CE)  | Output Enable Time from OE                    | 5   |     | ns   |

| trec(RST)             | Power Down recovery to Output Delay. Vcc = 5V |     | 500 | ns   |

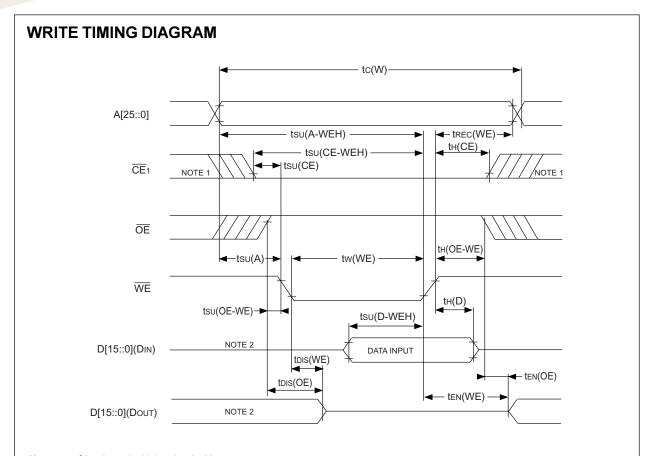

#### WRITE TIMING PARAMETERS

|              |                                | 200 | 200ns |      |

|--------------|--------------------------------|-----|-------|------|

| SYM (PCMCIA) | Parameter                      | Min | Max   | Unit |

| tcW          | Write Cycle Time               | 200 |       | ns   |

| tw(WE)       | Write Pulse Width              | 120 |       | ns   |

| ts∪(A)       | Address Setup Time             | 20  |       | ns   |

| ts∪(A-WEH)   | Address Setup Time for WE      | 140 |       | ns   |

| tsu(CE-WEH)  | Card Enable Setup Time for WE  | 140 |       | ns   |

| tsu(D-WEH)   | Data Setup Time for WE         | 60  |       | ns   |

| tH(D)        | Data Hold Time                 | 30  |       | ns   |

| trec(WE)     | Write Recover Time             | 30  |       | ns   |

| tois(WE)     | Output Disable Time from WE    |     | 90    | ns   |

| tois(OE)     | Output Disable Time from OE    |     | 90    | ns   |

| ten(WE)      | Output Enable Time from WE     | 5   |       | ns   |

| ten(OE)      | Output Enable Time from OE     | 5   |       | ns   |

| tsu(OE-WE)   | Output Enable Setup from WE    | 10  |       | ns   |

| tн(OE-WE)    | Output Enable Hold from WE     | 10  |       | ns   |

| tsu(CE)      | Card Enable Setup Time from OE | 0   |       | ns   |

| tн(CE)       | Card Enable Hold Time          | 20  |       | ns   |

#### Notes: 1. Signal may be high or low in this area.

2. When the data I/O pins are in the output state, no signals shall be applied to the data pins (D15 - D0) by the host system.

#### DATA WRITE AND ERASE PERFORMANCE<sup>(1,2,3)</sup> **CLF11: Vcc = 3V-5V**

| Parameter                                                     | Notes       | Min | Typ <sup>(1)</sup> | Max | Units |

|---------------------------------------------------------------|-------------|-----|--------------------|-----|-------|

| Write Buffer Byte program time(time to prog. 32Bytes/16Words) | - J3 device |     | 200                |     | μs    |

| Byte Program time - Using Word/Byte prog command              | - J3 device |     | 180                |     | μs    |

| Block Program Time128kB written using Write to Buffer         | - J3 device |     | 0.8                |     | sec   |

| Block Erase Time                                              | - J3 device |     | 0.7                |     | sec   |

#### Notes:

- 1. Typical: Nominal voltages and  $T_A = 25$ °C.

- 2. Excludes system overhead.

- 3. Valid for all speed options.

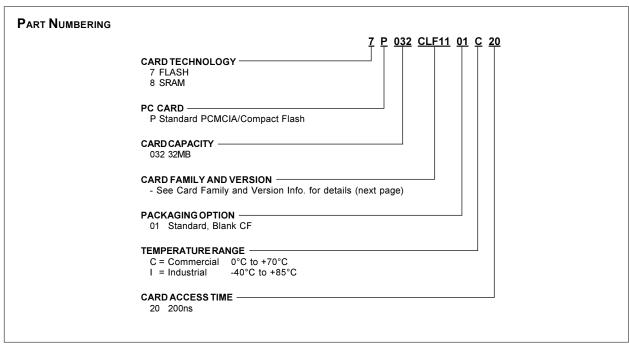

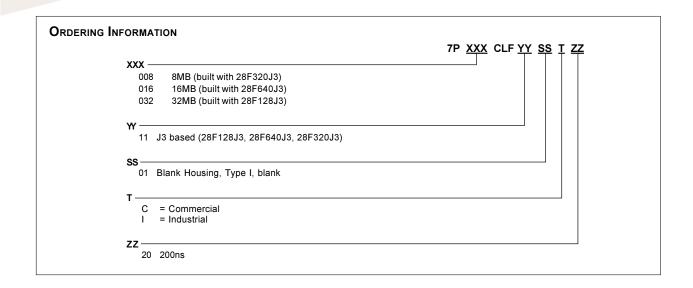

#### PART NUMBER TABLE - COMMON OPTIONS

#### INTEL STRATA FLASH BASED CARDS

| WEDC Part Number | Density | Speed | Flash Component |

|------------------|---------|-------|-----------------|

| 7P016CLF1101C20  | 8MB     | 200ns | 28F320J3        |

| 7P032CLF1101C20  | 16MB    | 200ns | 28F640J3        |

| 7P064CLF1101C20  | 32MB    | 200ns | 28F128J3        |

| 7P016CLF1101I20  | 8MB     | 200ns | 28F320J3        |

| 7P032CLF1101I20  | 16MB    | 200ns | 28F640J3        |

| 7P064CLF1101I20  | 32MB    | 200ns | 28F128J3        |

#### Notes:

<sup>1.</sup> Other options, including density, architecture and speed are available, please contact your WEDC sales representative with your request.

## **Document Title**

Compact Linear Flash Memory Card - CLF11 Series

# **Revision History**

| Rev level | <u>Description</u>                         | <u>Date</u>    |

|-----------|--------------------------------------------|----------------|

| rev 0     | Initial release                            | February, 2001 |

| rev 1     | Add separate enable for LOW and HIGH bytes | February, 2001 |

| rev 2     | Final release                              | October, 2001  |

| rev 3     | Industrial temp. added                     | May, 2003      |