# **LR38620**

### **DESCRIPTION**

The LR38620 is a CMOS timing generator IC which generates timing pulses for driving 4 200 k-pixel CCD area sensor and processing pulses.

### **FEATURES**

- Designed for 1/1.8-type 4 200 k-pixel CCD area sensor

- Frequency of driving horizontal CCD : 24.54545 MHz

- In monitoring mode, it can be obtained 30 fields/s

- External shutter control function with serial data input is possible

- +3.3 V and +4.5 V power supplies

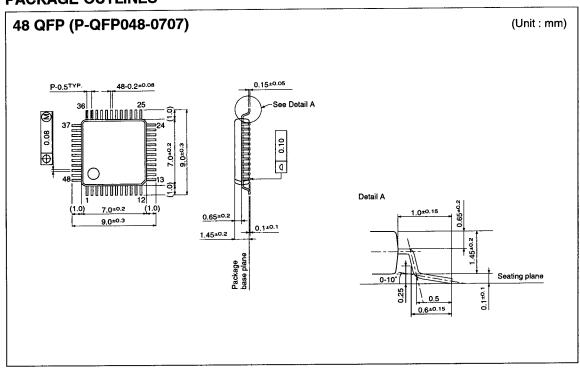

- Package : 48-pin QFP (P-QFP048-0707) 0.5 mm pin-pitch

# Timing Generator IC for 4 200 k-pixel CCD

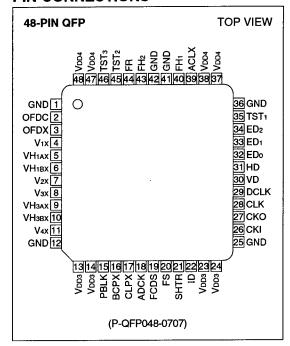

## PIN CONNECTIONS

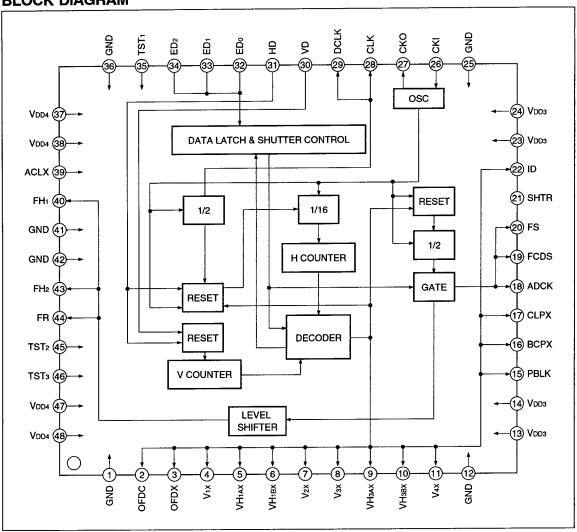

# **BLOCK DIAGRAM**

# **PIN DESCRIPTION**

| C 114   | DESCRIPTION        |                  |          |                            |                                                         |    |                                                      |                                        |  |

|---------|--------------------|------------------|----------|----------------------------|---------------------------------------------------------|----|------------------------------------------------------|----------------------------------------|--|

| PIN NO. | SYMBOL             | IO SYMBOL        | POLARITY | PIN NAME                   | DESCRIPTION                                             |    |                                                      |                                        |  |

| 1       | GND                | _                | -        | Ground                     | A grounding pin.                                        |    |                                                      |                                        |  |

| 2       | OFDC               | O3MR1            | Л        | Control pulse output       | A pulse to control OFD voltage.                         |    |                                                      |                                        |  |

|         |                    | OSIVINI          | JL       | for OFD voltage            |                                                         |    |                                                      |                                        |  |

|         |                    |                  |          |                            | A pulse that sweeps the charge of the photo-diode for   |    |                                                      |                                        |  |

| 3       | OFDX               | O3MR1            | ٦٢       | OFD pulse output           | the electronic shutter. Connect to OFD pin of the CCD   |    |                                                      |                                        |  |

| ١       | OFDX               | OSIVIITI         | IJ       | Of D pulse output          | through the vertical driver IC and DC offset circuit.   |    |                                                      |                                        |  |

|         |                    |                  |          |                            | Held at H level in normal mode.                         |    |                                                      |                                        |  |

| 4       | V <sub>1</sub> X   | O3MR1            | J_       | Vertical transfer          | A vertical transfer pulse for the CCD.                  |    |                                                      |                                        |  |

| 4       | VIX                | OSIVINI          | J [      | pulse output 1             | Connect to V1x pin of vertical driver IC.               |    |                                                      |                                        |  |

|         |                    |                  |          | Readout pulse              | A pulse that transfers the charge of the photo-diode to |    |                                                      |                                        |  |

| 5       | VH <sub>1</sub> AX | O3MR1            | l T      | output 1A                  | the vertical shift register.                            |    |                                                      |                                        |  |

|         |                    |                  |          | output 1A                  | Connect to VH1AX pin of vertical driver IC.             |    |                                                      |                                        |  |

|         |                    |                  |          | Readout pulse              | A pulse that transfers the charge of the photo-diode to |    |                                                      |                                        |  |

| 6       | VH <sub>1</sub> BX | O3MR1            | J        | output 1B                  | the vertical shift register.                            |    |                                                      |                                        |  |

|         |                    |                  |          | output 15                  | Connect to VH1BX pin of vertical driver IC.             |    |                                                      |                                        |  |

| 7       | V <sub>2</sub> X   | O3MR1            |          | Vertical transfer          | A vertical transfer pulse for the CCD.                  |    |                                                      |                                        |  |

|         | VZX                |                  | ] ]      | pulse output 2             | Connect to V2x pin of vertical driver IC.               |    |                                                      |                                        |  |

|         | Vov                | O3MR1            | П        | Vertical transfer          | A vertical transfer pulse for the CCD.                  |    |                                                      |                                        |  |

| 8       | Vзx                |                  |          | pulse output 3             | Connect to V3x pin of vertical driver IC.               |    |                                                      |                                        |  |

|         | VНзах              | O3MR1            |          | Readout pulse output 3A    | A pulse that transfers the charge of the photo-diode to |    |                                                      |                                        |  |

| 9       |                    |                  | 1        |                            | the vertical shift register.                            |    |                                                      |                                        |  |

|         |                    |                  |          |                            | Connect to VH3AX pin of vertical driver IC.             |    |                                                      |                                        |  |

|         |                    | labx O3MR1       |          | Readout pulse<br>output 3B | A pulse that transfers the charge of the photo-diode to |    |                                                      |                                        |  |

| 10      | VНзвх              |                  | 1        |                            | the vertical shift register.                            |    |                                                      |                                        |  |

|         |                    |                  |          |                            | Connect to VH3BX pin of vertical driver IC.             |    |                                                      |                                        |  |

| 11      | VAY OSMB           | V <sub>4</sub> X | O2MD4    | /4X O3MR1                  | VAY O3MB1                                               | ][ | Vertical transfer                                    | A vertical transfer pulse for the CCD. |  |

|         | V4X                | OSIVIITI         | Ш        | pulse output 4             | Connect to V <sub>4</sub> x pin of vertical driver IC.  |    |                                                      |                                        |  |

| 12      | GND                | _                |          | Ground                     | A grounding pin.                                        |    |                                                      |                                        |  |

| 13      | V <sub>DD3</sub>   | _                | -        | Power supply               | Supply of +3.3 V power.                                 |    |                                                      |                                        |  |

| 14      | V <sub>DD3</sub>   | -                |          | Power supply               | Supply of +3.3 V power.                                 |    |                                                      |                                        |  |

| İ       |                    |                  | 1        |                            | A pulse for pre-blanking. This pulse is controlled by   |    |                                                      |                                        |  |

|         |                    |                  |          | Pre-blanking pulse output  | serial data BLKCNT.                                     |    |                                                      |                                        |  |

|         | PBLK               |                  | J        |                            | BLKCNT = H; This pulse stays low during the             |    |                                                      |                                        |  |

| 15      |                    | O3MR1            |          |                            | absence of effective pixels within the                  |    |                                                      |                                        |  |

| '3      |                    |                  |          |                            | vertical blanking or during the                         |    |                                                      |                                        |  |

|         |                    |                  |          |                            | sweepout signal.                                        |    |                                                      |                                        |  |

|         |                    |                  |          |                            | BLKCNT = L; Continuous pulse                            |    |                                                      |                                        |  |

|         |                    |                  |          |                            |                                                         |    | The output phase of PBLK is selected by serial data. |                                        |  |

| PIN NO. | SYMBOL                | IO SYMBOL  | DOI ARITY                  | PIN NAME                                                    | DESCRIPTION                                                  |  |  |  |  |  |  |  |  |  |  |                                          |

|---------|-----------------------|------------|----------------------------|-------------------------------------------------------------|--------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|------------------------------------------|

| PIN NO. | STIVIDOL              | IO 3 HIBOL | POLAIIIII                  | I III IIAIIIE                                               | A pulse to clamp the optical black signal.                   |  |  |  |  |  |  |  |  |  |  |                                          |

|         |                       |            |                            |                                                             | This pulse is controlled by serial data BCPCNT.              |  |  |  |  |  |  |  |  |  |  |                                          |

|         |                       |            |                            |                                                             | BCPCNT = H; This pulse stays high during the                 |  |  |  |  |  |  |  |  |  |  |                                          |

|         |                       |            |                            | Optical black clamp                                         | absence of effective pixels within the                       |  |  |  |  |  |  |  |  |  |  |                                          |

| 16      | BCPX                  | O3MR1      |                            | pulse output                                                | vertical blanking or during the                              |  |  |  |  |  |  |  |  |  |  |                                          |

|         |                       | 1          |                            | puise output                                                | sweepout signal.                                             |  |  |  |  |  |  |  |  |  |  |                                          |

|         |                       |            |                            |                                                             | BCPCNT = L; This pulse stays high during the                 |  |  |  |  |  |  |  |  |  |  |                                          |

|         |                       |            |                            |                                                             | sweepout signal.                                             |  |  |  |  |  |  |  |  |  |  |                                          |

|         | ····                  |            |                            |                                                             | A pulse to clamp the dummy outputs of the CCD signal.        |  |  |  |  |  |  |  |  |  |  |                                          |

| 17      | CLPX                  | O3MR1      | J                          | Clamp pulse output                                          | This pulse stays high during the sweepout period.            |  |  |  |  |  |  |  |  |  |  |                                          |

|         |                       |            |                            |                                                             | An output pin for AD converter. The output phase of          |  |  |  |  |  |  |  |  |  |  |                                          |

| 18      | ADCK                  | O6M32      | $\prod$                    | AD clock output                                             | ADCK is selected by serial data in 90° steps.                |  |  |  |  |  |  |  |  |  |  |                                          |

|         |                       |            | n                          |                                                             | A pulse to clamp the feed-through level for the CCD.         |  |  |  |  |  |  |  |  |  |  |                                          |

| 19      | FCDS                  | O6M32      |                            | CDS pulse output 1                                          | The output phase and output polarity of FCDS are             |  |  |  |  |  |  |  |  |  |  |                                          |

| '       | 1 000                 | COMOZ      | 1                          | OBO pales calpar.                                           | selected by serial data.                                     |  |  |  |  |  |  |  |  |  |  |                                          |

|         |                       |            | П                          |                                                             | A pulse to sample-hold the signal for the CCD.               |  |  |  |  |  |  |  |  |  |  |                                          |

| 20      | FS                    | O6M32      |                            | CDS pulse output 2                                          | The output phase and output polarity of FS are selected      |  |  |  |  |  |  |  |  |  |  |                                          |

| 20      |                       |            | l                          | OBO paiso caipa. 2                                          | by serial data.                                              |  |  |  |  |  |  |  |  |  |  |                                          |

| 21      | SHTR                  | O3MR1      | П                          | Frigger output A trigger pulse for effective signal period. |                                                              |  |  |  |  |  |  |  |  |  |  |                                          |

|         |                       |            |                            | Line index pulse                                            | The pulse is used in the color separator.                    |  |  |  |  |  |  |  |  |  |  |                                          |

| 22      | ID                    | O3MR1      | l II                       | output                                                      | The signal switches between high and low at every line.      |  |  |  |  |  |  |  |  |  |  |                                          |

| 23      | V <sub>DD3</sub>      | _          | _                          | Power supply                                                | Supply of +3.3 V power.                                      |  |  |  |  |  |  |  |  |  |  |                                          |

| 24      | V <sub>DD3</sub>      | _          | _                          | Power supply                                                | Supply of +3.3 V power.                                      |  |  |  |  |  |  |  |  |  |  |                                          |

| 25      | GND                   | l _        | _                          | Ground                                                      | A grounding pin.                                             |  |  |  |  |  |  |  |  |  |  |                                          |

|         |                       | 0000       |                            |                                                             | An input pin for reference clock oscillation.                |  |  |  |  |  |  |  |  |  |  |                                          |

| 26      | CKI                   | OSCI3      | _                          | Clock input                                                 | The frequency is 49.0909 MHz.                                |  |  |  |  |  |  |  |  |  |  |                                          |

|         | 01/0                  |            |                            |                                                             |                                                              |  |  |  |  |  |  |  |  |  |  | An output pin for reference oscillation. |

| 27      | ско                   | OSCO3      | <b>-</b>                   | Clock output                                                | The output is the inverse of CKI (pin 26).                   |  |  |  |  |  |  |  |  |  |  |                                          |

|         | 01.14                 | 001400     | nι                         | Ol- alc autaut                                              | An output pin to generate HD and VD pulses.                  |  |  |  |  |  |  |  |  |  |  |                                          |

| 28      | CLK                   | O6M32      | N.                         | Clock output                                                | The frequency is 24.54545 MHz.                               |  |  |  |  |  |  |  |  |  |  |                                          |

|         |                       |            |                            |                                                             | An output pin for DSP IC. The frequency is 24.54545 MHz.     |  |  |  |  |  |  |  |  |  |  |                                          |

| 29      | DCLK                  | O6M32      | $\mathbb{I}$               | Clock output                                                | The output phase of DCLK is selected by serial data in       |  |  |  |  |  |  |  |  |  |  |                                          |

|         |                       |            |                            |                                                             | 90° steps.                                                   |  |  |  |  |  |  |  |  |  |  |                                          |

| 30      | VD                    | IC3        | 15                         | Vertical reference                                          | An input pin for reference of vertical pulse.                |  |  |  |  |  |  |  |  |  |  |                                          |

| 30      | VD                    | 103        |                            | pulse input                                                 | Connect to VD pin of DSP IC.                                 |  |  |  |  |  |  |  |  |  |  |                                          |

| 31      | HD                    | IC3        |                            | Horizontal drive                                            | An input pin for reference of horizontal pulse.              |  |  |  |  |  |  |  |  |  |  |                                          |

| 31      | ا ا<br>               | 103        | U                          | pulse input                                                 | Connect to HD pin of DSP IC.                                 |  |  |  |  |  |  |  |  |  |  |                                          |

| 32      | 32 ED <sub>0</sub> IC |            | 1                          | Strobe pulse input                                          | An input pin for the strobe pulse, to control the functions  |  |  |  |  |  |  |  |  |  |  |                                          |

|         |                       | 15555      | ICSD3 - Strobe pulse input |                                                             | of LR38620. For details, see "Serial Data Control".          |  |  |  |  |  |  |  |  |  |  |                                          |

|         |                       |            |                            | Shift register clock                                        | An input pin for the clock of the shift register, to control |  |  |  |  |  |  |  |  |  |  |                                          |

| 33      | ED <sub>1</sub>       | 1 ICSD3    | _                          | input                                                       | the functions of LR38620. For details, see "Serial Data      |  |  |  |  |  |  |  |  |  |  |                                          |

|         |                       |            |                            | •                                                           | Control".                                                    |  |  |  |  |  |  |  |  |  |  |                                          |

| PIN NO. | SYMBOL           | IO SYMBOL | POLARITY | PIN NAME                             | DESCRIPTION                                                                                                                    |  |  |  |

|---------|------------------|-----------|----------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 34      | ED <sub>2</sub>  | ICSD3     | 1        | Shift register data input            | An input pin for the data of the shift register, to control the functions of LR38620. For details, see "Serial Data Control".  |  |  |  |

| 35      | TST <sub>1</sub> | ICD3      | _        | Test pin 1                           | A test pin. Set open or to L level in normal mode.                                                                             |  |  |  |

| 36      | GND              | -         | -        | Ground                               | A grounding pin.                                                                                                               |  |  |  |

| 37      | VDD4             | _         | -        | Power supply                         | Supply of +4.5 V power.                                                                                                        |  |  |  |

| 38      | VDD4             |           | _        | Power supply                         | Supply of +4.5 V power.                                                                                                        |  |  |  |

| 39      | ACLX             | ICU4      | -        | All clear input                      | An input pin for resetting all internal circuit at power-on.  Connect to VDD3 through the diode and GND through the capacitor. |  |  |  |

| 40      | FH <sub>1</sub>  | O8M43     | N        | Horizontal transfer pulse output 1   | A horizontal transfer pulse for the CCD.  Connect to ∲H1 pin of the CCD.                                                       |  |  |  |

| 41      | GND              | -         | _        | Ground                               | A grounding pin.                                                                                                               |  |  |  |

| 42      | GND              | -         | _        | Ground                               | A grounding pin.                                                                                                               |  |  |  |

| 43      | FH <sub>2</sub>  | O8M43     | N        | Horizontal transfer pulse output 2   | A horizontal transfer pulse for the CCD.  Connect to                                                                           |  |  |  |

| 44      | FR               | O8M43 _   |          | Reset pulse output                   | A pulse to reset the charge of output circuit. The output phase of FR is selected by serial data.                              |  |  |  |

| 45      | TST2             | ICD4      | _        | Test pin 2                           | A test pin. Set open or to L level in normal mode.                                                                             |  |  |  |

| 46      | TSTз             | ICD4      | 1        | Test pin 3                           | A test pin. Set open or to L level in normal mode.                                                                             |  |  |  |

| 47      | VDD4             | -         | -        | Power supply Supply of +4.5 V power. |                                                                                                                                |  |  |  |

| 48      | V <sub>DD4</sub> | _         | _        | Power supply                         | Supply of +4.5 V power.                                                                                                        |  |  |  |

IC3 : Input pin (CMOS level)

ICD3 : Input pin (CMOS level with pull-down resistor)

ICSD3 : Input pin (CMOS schmitt-trigger level with pull-

down resistor)

ICD4 : Input pin (CMOS level with pull-down resistor)

ICU4 : Input pin (CMOS level with pull-up resistor)

O3MR1 : Output pin (output high level is VDD3.)

O6M32 : Output pin (output high level is VDD3.)

O8M43 : Output pin (output high level is VDD4.)

OSCI3 : Input pin for oscillation

OSCO3 : Output pin for oscillation

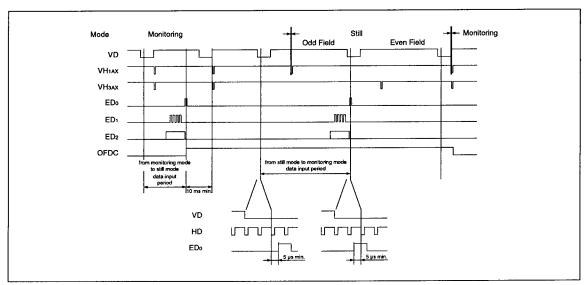

# Serial Data Control SERIAL DATA INPUT TIMING

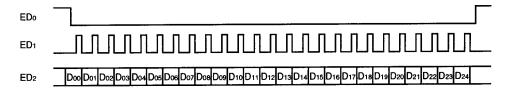

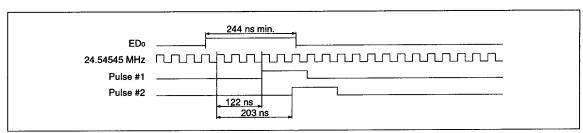

ED2 is shifted by the rising edge of ED1, and is latched by the pulse #1 which is generated after 122 to 162 ns delay from the rising edge of ED0. (See **Fig. 2**.)

The latched serial data are divided into two types by the data of Doo, and are relatched by the pulse #2 which is generated after 203 to 243 ns delay from the rising edge of EDo. (See **Fig. 1**.)

INMD is effective at the start of #3 horizontal line, and shutter control data are effective at the start of #11 horizontal line in monitoring mode and #93 horizontal line in still mode, and other data are effective at pulse #2.

EDo should be at low level during data inputs of ED1 and ED2 or while ACLX is at low level.

Fig. 1 Data Latch Timing

Fig. 2 Input Pulse Timing of EDo, ED1 and ED2

SHARP LR38620

# **SERIAL DATA INPUTS**

Doo = L

| DATA    | NAME             | FUNCTION DATA = L DATA = H        |                        | AT ACLX = L       |       |  |

|---------|------------------|-----------------------------------|------------------------|-------------------|-------|--|

|         | 0D)/- 0D)/-      | Integration time control in field | -                      |                   | All L |  |

| D01-D09 | SDV0-SDV8        | period step by horizontal period. |                        |                   |       |  |

| D10-D15 | SDHo-SDH5        | Dummy Fix to L level              |                        | All L             |       |  |

| D16     | SDF <sub>0</sub> | 1tion time control by field       |                        |                   |       |  |

| D17     | SDF1             | Integration time control by field |                        | All L             |       |  |

| D18     | SDF2             | period.                           |                        |                   |       |  |

| D19     | SMD              | Electronic shutter mode control – |                        | L                 |       |  |

| D20     | PWSA             | Power save control                | Normal                 | Normal Power save |       |  |

| D21     | INMD             | Integration mode control          | Monitoring             | Still             | L     |  |

| D22     | Dummy            | Dummy                             | Fix to L level         |                   | L     |  |

| D23     | Dummy            | Dummy                             | Fix to L level         |                   | L     |  |

| D24     | VHCNT            | VH1AX to VH3BX control            | Output Held at H level |                   | L     |  |

Doo = H

| DATA | NAME   | FUNCTION                               | DATA = L   | DATA = H      | AT ACLX = L |  |

|------|--------|----------------------------------------|------------|---------------|-------------|--|

| D01  | ML1    |                                        | <u>_</u>   |               | All L       |  |

| D02  | ML2    |                                        |            | , <u>-</u>    |             |  |

| D03  | MR1    |                                        |            |               |             |  |

| D04  | MR2    |                                        |            | All L         |             |  |

| D05  | MR3    |                                        |            |               |             |  |

| D06  | MC1    | 1                                      |            |               |             |  |

| D07  | MC2    |                                        |            | All L         |             |  |

| D08  | МСЗ    | Phase control                          |            |               |             |  |

| D09  | MS1    | Priase Control                         |            |               |             |  |

| D10  | MS2    |                                        | -          | All L         |             |  |

| D11  | MS3    |                                        |            |               |             |  |

| D12  | MD1    |                                        |            |               |             |  |

| D13  | MD2    |                                        | -          | All L         |             |  |

| D14  | MD3    |                                        |            |               |             |  |

| D15  | MA1    |                                        |            | All L         |             |  |

| D16  | MA2    |                                        |            | All L         |             |  |

| D17  | Dummy  |                                        |            |               | All L       |  |

| D18  | Dummy  | Dummy                                  | Fix to     |               |             |  |

| D19  | Dummy  |                                        |            |               |             |  |

| D20  | MP1    | Phase control                          | _          |               | All L       |  |

| D21  | MP2    | Friase control                         |            | All L         |             |  |

| D22  | PLCH   | Polarity control of FCDS and FS pulses | Negative   | Positive      | L           |  |

| D23  | BLKCNT | PBLK control                           | Continuous | Discontinuous | L           |  |

| D24  | BCPCNT | BCPX control                           | Continuous | Discontinuous | L           |  |

# **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER             | SYMBOL     | RATING                 | UNIT |

|-----------------------|------------|------------------------|------|

| Supply voltage        | VDD3, VDD4 | -0.3 to +5.5           | V    |

|                       | Vıз        | -0.3 to VDD3 + 0.3     | V    |

| Input voltage         | VI4        | -0.3 to VDD4 + 0.3     | V    |

|                       | Voз        | Vo3 -0.3 to VDD3 + 0.3 |      |

| Output voltage        | V04        | -0.3 to VDD4 + 0.3     | V    |

| Operating temperature | TOPR       | -20 to +70             | ,c   |

| Storage temperature   | Тѕтс       | -55 to +150            | .c   |

## **ELECTRICAL CHARACTERISTICS**

# **DC Characteristics**

$(VDD3 = 3.3\pm10\%, VDD4 = 4.5\pm10\%, TOPR = -20 to +70°C)$

| DC Characteristics    |           | $(VDD3 = 3.3\pm10\%, VDD4 = 4.3\pm10\%, TOPR = -20.10 + 70.0$ |            |        |      |      |      |  |

|-----------------------|-----------|---------------------------------------------------------------|------------|--------|------|------|------|--|

| PARAMETER             | SYMBOL    | CONDITIONS                                                    | MIN.       | TYP. M | AX.  | UNIT | NOTE |  |

| Input "Low" voltage   | VIL3-1    |                                                               |            | 0.2    | VDD3 | ٧    | 1, 2 |  |

| Input "High" voltage  | VIH3-1    |                                                               | 0.8VDD3    |        |      | ٧    | 1, 2 |  |

| Input "Low" voltage   | VIL3-2    |                                                               | 0.2VDD3    |        |      | ٧    |      |  |

| Input "High" voltage  | VIH3-2    | Schmitt-buffer                                                |            | 0.75   | VDD3 | ٧    | 3    |  |

| Hysteresis voltage    | VT+ - VT- |                                                               | 0.14VDD3   |        |      | ٧    |      |  |

| Input "Low" voltage   | VIL4      |                                                               |            | 0.2    | VDD4 | ٧    | 4 5  |  |

| Input "High" voltage  | VIH4      |                                                               | 0.8VDD4    |        |      | ٧    | 4, 5 |  |

| Input "Low" current   |           | VI = 0 V                                                      |            | 1      | .0   | μΑ   | 1    |  |

| Input "High" current  |           | VI = VDD3                                                     |            | 1      | .0   | μΑ   | '    |  |

| Input "Low" current   |           | Vi = 0 V                                                      |            | 3      | .0   | μΑ   | 2 2  |  |

| Input "High" current  | liH3-2    | Vi = VDD3                                                     | 8.0        | 10     | 00   | μΑ   | 2, 3 |  |

| Input "Low" current   |           | VI = 0 V                                                      | 20         | 30     | 00   | μΑ   | 4    |  |

| Input "High" current  |           | VI = VDD4                                                     |            | 5      | .0   | μΑ   |      |  |

| Input "Low" current   | liL4-2    | Vi = 0 V                                                      |            | 5      | .0   | μA   | 5    |  |

| Input "High" current  | IIH4-2    | VI = VDD4                                                     | 20         | 30     | 00   | μΑ   | ] 3  |  |

| Output "Low" voltage  | VOL3-1    | loL = 3 mA                                                    |            | 0      | .4   | ٧    | 6    |  |

| Output "High" voltage | Vонз-1    | lон = −2.5 mA                                                 | VDD3 - 0.5 |        |      | ٧    |      |  |

| Output "Low" voltage  | VOL3-2    | IoL = 12 mA                                                   |            | 0      | .4   | V    | 7    |  |

| Output "High" voltage | Vонз-2    | lон = −10 mA                                                  | VDD3 - 0.5 |        |      | ٧    |      |  |

| Output "Low" voltage  | VOL4      | loL = 20 mA                                                   |            | 0      | .4   | V    | 8    |  |

| Output "High" voltage | VoH4      | lон = −20 mA                                                  | VDD4 - 0.5 |        |      | V    |      |  |

## **NOTES:**

- 1. Applied to inputs (IC3, OSCI3).

- 2. Applied to input (ICD3).

- 3. Applied to input (ICSD3).

- 4. Applied to input (ICU4).

- 5. Applied to input (ICD4).

- Applied to outputs (OSCO3, O3MR1). (Output (OSCO3) measures on condition that input (OSCI3) level is 0 V or VDD3.)

- 7. Applied to output (O6M32).

- 8. Applied to output (O8M43).

# **PACKAGE OUTLINES**

## SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE.

Suggested applications (if any) are for standard use; See Important Restrictions for limitations on special applications. See Limited Warranty for SHARP's product warranty. The Limited Warranty is in lieu, and exclusive of, all other warranties, express or implied. ALL EXPRESS AND IMPLIED WARRANTIES, INCLUDING THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR USE AND FITNESS FOR A PARTICULAR PURPOSE, ARE SPECIFICALLY EXCLUDED. In no event will SHARP be liable, or in any way responsible, for any incidental or consequential economic or property damage.

# HARP

### **NORTH AMERICA**

SHARP Microelectronics of the Americas 5700 NW Pacific Rim Blvd. Camas, WA 98607, U.S.A. Phone: (1) 360-834-2500 Fax: (1) 360-834-8903 Fast Info: (1) 800-833-9437 www.sharpsma.com

#### **TAIWAN**

SHARP Electronic Components (Taiwan) Corporation 8F-A, No. 16, Sec. 4, Nanking E. Rd. Taipei, Taiwan, Republic of China Phone: (886) 2-2577-7341 Fax: (886) 2-2577-7326/2-2577-7328

### **CHINA**

SHARP Microelectronics of China (Shanghai) Co., Ltd. 28 Xin Jin Qiao Road King Tower 16F Pudong Shanghai, 201206 P.R. China Phone: (86) 21-5854-7710/21-5834-6056 Fax: (86) 21-5854-4340/21-5834-6057 **Head Office:** No. 360, Bashen Road,

Xin Development Bldg. 22 Waigaogiao Free Trade Zone Shanghai 200131 P.R. China

Email: smc@china.global.sharp.co.jp

### **EUROPE**

SHARP Microelectronics Europe Division of Sharp Electronics (Europe) GmbH Sonninstrasse 3 20097 Hamburg, Germany Phone: (49) 40-2376-2286 Fax: (49) 40-2376-2232 www.sharpsme.com

#### **SINGAPORE**

SHARP Electronics (Singapore) PTE., Ltd. 438A, Alexandra Road, #05-01/02 Alexandra Technopark, Singapore 119967 Phone: (65) 271-3566 Fax: (65) 271-3855

### HONG KONG

SHARP-ROXY (Hong Kong) Ltd. 3rd Business Division. 17/F, Admiralty Centre, Tower 1 18 Harcourt Road, Hong Kong Phone: (852) 28229311 Fax: (852) 28660779 www.sharp.com.hk **Shenzhen Representative Office:** Room 13B1, Tower C, Electronics Science & Technology Building Shen Nan Zhong Road Shenzhen, P.R. China Phone: (86) 755-3273731 Fax: (86) 755-3273735

### **JAPAN**

SHARP Corporation Electronic Components & Devices 22-22 Nagaike-cho, Abeno-Ku Osaka 545-8522, Japan Phone: (81) 6-6621-1221 Fax: (81) 6117-725300/6117-725301

www.sharp-world.com

### **KOREA**

SHARP Electronic Components (Korea) Corporation RM 501 Geosung B/D, 541 Dohwa-dong, Mapo-ku Seoul 121-701, Korea Phone: (82) 2-711-5813 ~ 8 Fax: (82) 2-711-5819