Dear customers,

About the change in the name such as "Oki Electric Industry Co. Ltd." and "OKI" in documents to OKI Semiconductor Co., Ltd.

The semiconductor business of Oki Electric Industry Co., Ltd. was succeeded to OKI Semiconductor Co., Ltd. on October 1, 2008. Therefore, please accept that although the terms and marks of "Oki Electric Industry Co., Ltd.", "Oki Electric", and "OKI" remain in the documents, they all have been changed to "OKI Semiconductor Co., Ltd.". It is a change of the company name, the company trademark, and the logo, etc., and NOT a content change in documents.

October 1, 2008 OKI Semiconductor Co., Ltd.

# OKI SEMICONDUCTOR CO., LTD.

550-1 Higashiasakawa-cho, Hachioji-shi, Tokyo 193-8550, Japan http://www.okisemi.com/en/

# **OKI** Semiconductor

### This version: Nov. 1997 Previous version: Mar. 1996

# **MSM6648**

#### **100-DOT COMMON DRIVER**

#### **GENERAL DESCRIPTION**

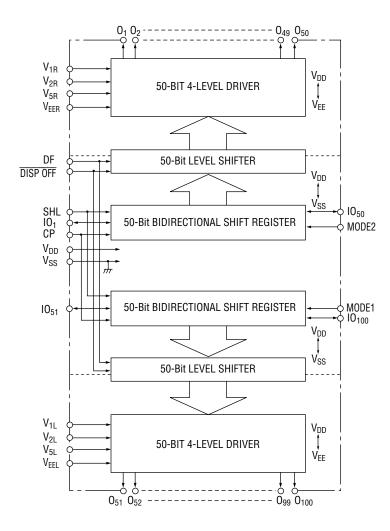

The MSM6648 is a dot matrix LCD common driver. Fabricated in CMOS technology, the device consists of two 50-bit bidirectional shift registers, two 50-bit level shifters, and two 50-bit 4-level drivers.

The MSM6648 is equipped with 100 LCD output pins. By connecting more than two MSM6648s in cascade, this LSI is applicable to a wide LCD panel.

#### **FEATURES**

Logic supply voltage

LCD drive voltage

Applicable LCD duty

2.7 to 5.5 V

18 to 28 V

1/64 to 1/240

- Suitable for bath panel sizes of  $400 (200 \times 2)$  and  $480 (240 \times 2)$  in common numbers by the use of intermediate data input and 10-bit bypass function.

- Structure:

Tape Carrier Package (TCP) mounting with 35 mm wide film

(Product name: MSM6648AV-Z-01)

Sn-plated

# **BLOCK DIAGRAM**

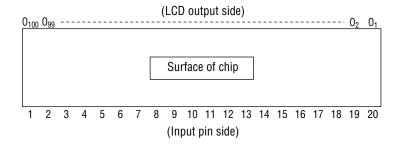

# **PIN CONFIGURATION (TOP VIEW)**

| Pin | Symbol            | Pin | Symbol           |

|-----|-------------------|-----|------------------|

| 1   | V <sub>1L</sub>   | 11  | IO <sub>50</sub> |

| 2   | V <sub>2L</sub>   | 12  | V <sub>SS</sub>  |

| 3   | V <sub>5L</sub>   | 13  | DF               |

| 4   | V <sub>EEL</sub>  | 14  | CP               |

| 5   | MODE1             | 15  | 101              |

| 6   | IO <sub>100</sub> | 16  | MODE2            |

| 7   | DISP OFF          | 17  | V <sub>EER</sub> |

| 8   | $V_{DD}$          | 18  | V <sub>5R</sub>  |

| 9   | SHL               | 19  | V <sub>2R</sub>  |

| 10  | IO <sub>51</sub>  | 20  | V <sub>1R</sub>  |

#### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                | Symbol                              | Condition | Rating                        | Unit |

|--------------------------|-------------------------------------|-----------|-------------------------------|------|

| Power Supply Voltage (1) | $V_{DD}$                            | Ta = 25°C | -0.3 to +6.5                  | V    |

| Power Supply Voltage (2) | V <sub>DD</sub> -V <sub>EE</sub> *1 | Ta = 25°C | 0 to 30                       | V    |

| Input Voltage            | VI                                  | Ta = 25°C | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Storage Temperature      | T <sub>STG</sub>                    | _         | −30 to +85                    | °C   |

<sup>\*1</sup>  $V_1 > V_2 > V_5 > V_{EE}$ ,  $V_{DD} \ge V_1 > V_2 \ge V_{DD} - 10V$ ,  $V_{EE} + 10V \ge V_5 > V_{EE}$  $V_1 = V_{1L} = V_{1R}$ ,  $V_2 = V_{2L} = V_{2R}$ ,  $V_5 = V_{5L} = V_{5R}$ ,  $V_{EE} = V_{EEL} = V_{EER}$

#### RECOMMENDED OPERATING CONDITIONS

| Parameter                | Symbol                               | Condition        | Range      | Unit |  |

|--------------------------|--------------------------------------|------------------|------------|------|--|

| Power Supply Voltage (1) | $V_{DD}$                             | _                | 2.7 to 5.5 | V    |  |

| Power Supply Voltage (2) | V V *1                               | No load          | 14 to 28   | V    |  |

|                          | V <sub>DD</sub> – V <sub>EE</sub> *1 | During LCD drive | 18 to 28   | V    |  |

| Operating Temperature    | Тор                                  | _                | -20 to +75 | °C   |  |

\*1

$$V_1 > V_2 > V_5 > V_{EE}$$

,  $V_{DD} \ge V_1 > V_2 \ge V_{DD} - 7V$ ,  $V_{EE} + 7V \ge V_5 > V_{EE}$

$V_1 = V_{1L} = V_{1R}$ ,  $V_2 = V_{2L} = V_{2R}$ ,  $V_5 = V_{5L} = V_{5R}$ ,  $V_{EE} = V_{EEL} = V_{EER}$

#### **ELECTRICAL CHARACTERISTICS**

#### **DC** Characteristics

| Parameter          | Symbol             | Condition                                         | Min.                        | Тур.               | Max. | Unit               |    |

|--------------------|--------------------|---------------------------------------------------|-----------------------------|--------------------|------|--------------------|----|

| "H" Input Voltage  | V <sub>IH</sub> *1 | _                                                 |                             | 0.8V <sub>DD</sub> |      | $V_{DD}$           | V  |

| "L" Input Voltage  | V <sub>IL</sub> *1 | _                                                 |                             | Vss                | _    | 0.2V <sub>DD</sub> | V  |

| "H" Input Current  | I <sub>IH</sub> *1 | $V_I = V_{DD}, V_{DD} = 5.5V$                     |                             | _                  |      | 1                  | μΑ |

| "L" Input Current  | I <sub>IL</sub> *1 | $V_{I} = 0V, V_{DD} = 5.5V$                       | $V_{I} = 0V, V_{DD} = 5.5V$ |                    | _    | -1                 | μΑ |

| "H" Output Voltage | V <sub>OH</sub> *2 | $I_0 = -0.2$ mA, $V_{DD} = 2.7$ V                 |                             | $V_{DD} - 0.4$     | _    | _                  | V  |

| "L" Output Voltage | V <sub>0L</sub> *2 | $I_0 = 0.2 \text{mA}, V_{DD} = 2.7 \text{V}$      |                             | _                  |      | 0.4                | V  |

| ON Resistance      | R <sub>ON</sub> *4 | $V_{DD} - V_{EE} = 25V,$ $ V_N - V_0  = 0.25V$ *3 |                             |                    |      | 2                  | kΩ |

| Supply Current     | I <sub>SS</sub>    | $f_{CP} = 28kHz, V_{DD} = 3.0V$                   |                             | _                  |      | 50                 |    |

|                    | I <sub>EE</sub>    | $V_{DD} - V_{EE} = 25V$ , No load                 |                             | _                  |      | 300                | μΑ |

| Input Capacitance  | Cı                 | f = 1MHz                                          | _                           | 5                  | _    | pF                 |    |

<sup>\*1</sup> Applicable to CP,  $IO_1$ ,  $IO_{50}$ ,  $IO_{100}$ , SHL, DF,  $\overline{DISP}$  OFF, MODE1, MODE2.

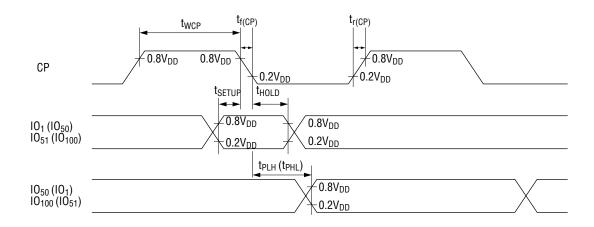

#### **Switching Characteristics**

$(V_{DD} = 2.7 \text{ to } 5.5V, Ta = -20 \text{ to } +75^{\circ}C, C_{L} = 15pF)$

|                                 |                                           | , 55      |      |      |      | - ' ' |

|---------------------------------|-------------------------------------------|-----------|------|------|------|-------|

| Parameter                       | Symbol                                    | Condition | Min. | Тур. | Max. | Unit  |

| "H", "L" Propagation Delay Time | t <sub>PLH</sub> , t <sub>PHL</sub>       | _         | _    | _    | 3    | μs    |

| Clock Frequency                 | f <sub>CP</sub>                           | _         | _    | _    | 1    | MHz   |

| CP Pulse Width                  | twcp                                      | _         | 63   | _    | _    | ns    |

| Data Setup Time                 | t <sub>SETUP</sub>                        | _         | 100  | _    | _    | ns    |

| Data Hold Time                  | t <sub>HOLD</sub>                         | _         | 100  | _    | _    | ns    |

| Rise/Fall Time of CP            | t <sub>r (CP)</sub> , t <sub>f (CP)</sub> | _         | _    | _    | 20   | ns    |

Note 1: When display is controlled by  $\overline{DISPOFF}$  pin, CP rise and fall time must be  $\leq 1 \,\mu s$ .

<sup>\*2</sup> Applicable to  $IO_1$ ,  $IO_{50}$ ,  $IO_{51}$ ,  $IO_{100}$

<sup>\*3</sup>  $V_N = V_{DD}$  to  $V_{EE}$ ,  $V_2 = 1/16$  ( $V_{DD} - V_{EE}$ ),  $V_5 = 15/16$  ( $V_{DD} - V_{EE}$ ),  $V_{DD} = V1$ ,  $V_{DD} = 4.5$ V

<sup>\*4</sup> Applicable to  $O_1$  to  $O_{100}$

#### **FUNCTIONAL DESCRIPTION**

#### **Pin Functional Description**

#### • IO, IO<sub>50</sub>, IO<sub>51</sub>, IO<sub>100</sub>

These are I/O pins for the two 50-bit bidirectional shift registers.

#### • SHL

This is an input pin to select the shift direction of the two 50-bit bidirectional shift registers. Set this pin to "H" or "L" level during power-on.

#### • MODE1, MODE2

These are input pins to select whether the two 50-bit shift registers are used as a two 50-bit application or a 40-bit and 50-bit application.

Functions of the SHL, MODE1 and MODE2 pins are shown below.

| SHL | MODE1 | MODE2 | Scan<br>direction            | Data input pin    | Scan output pin   | Function                                                                                                                                                                                  |

|-----|-------|-------|------------------------------|-------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |       |       | $0_1 \rightarrow 0_{50}$     | 101               | 1050              | The scan data input into the IO <sub>1</sub> , and IO <sub>51</sub> pins are                                                                                                              |

| L   | _     | L     | $0_{51} \rightarrow 0_{100}$ | IO <sub>51</sub>  | IO <sub>100</sub> | shifted at the falling edge of CP and are output from the IO <sub>50</sub> and IO <sub>100</sub> pins after the lapse of 50 clock pulses.                                                 |

| Н   |       |       | $0_{50} \rightarrow 0_1$     | 1050              | 101               | The scan data input into the IO <sub>100</sub> and IO <sub>50</sub> pins are                                                                                                              |

| п   | L     | _     | $0_{100} \rightarrow 0_{51}$ | IO <sub>100</sub> | IO <sub>51</sub>  | shifted at the falling edge of CP and are output from the IO <sub>51</sub> and IO <sub>1</sub> pins after 50 clock pulses.                                                                |

|     |       |       | $0_{11} \rightarrow 0_{50}$  | IO <sub>1</sub>   | IO <sub>50</sub>  | This condition means a mode of bypassing between the $O_1$ and $O_{10}$ pins. The scan data input into the $IO_1$ pin is stored in the $IO_{11}$ pin and is output from the $IO_{50}$ pin |

| L   | _     | Н     | $0_{51} \rightarrow 0_{100}$ | IO <sub>51</sub>  | IO <sub>100</sub> | after 40 clock pulses. The operation in the $\rm O_{51}$ to $\rm O_{100}$ pins is the same as that in setting SHL to "L" and MODE2 to "L".                                                |

| Н   | 11    |       | $0_{50} \rightarrow 0_1$     | 10 <sub>50</sub>  | 101               | This condition means a mode of bypassing between the $O_{91}$ and $O_{100}$ pins. The scan data input into the $IO_{100}$ pin is stored in $O_{90}$ and is                                |

| п   | Н     | _     | $0_{90} \rightarrow 0_{51}$  | IO <sub>100</sub> | 10 <sub>51</sub>  | output from the $10_{51}$ pin after 40 clock pulses. The operation in the $0_1$ to $0_{50}$ pins is the same as that in setting SHL to "H" and MODE1 to "L".                              |

#### • CP

This is a clock pulse input pin for two 50-bit bi-directional shift registers. Scan data is shifted at the falling edge of a clock pulse.

#### DF

This is an input pin for an LCD drive waveform AC synchronization signal, which generally inputs a frame inversion signal. See the Truth Table.

#### • DISP OFF

This is an input pin used to control the output pins  $O_1$  to  $O_{100}$ . Signals on the  $V_1$  level are output from the output pins  $O_1$  to  $O_{100}$ , independent of the shift register data during low signal input. See the Truth Table.

#### O<sub>1</sub> to O<sub>100</sub>

These are 4-level driver output pins, directly corresponding to each bit of the shift register. DF signals combined to shift register data select and output any of four levels  $V_1$ ,  $V_2$ ,  $V_5$ , and  $V_{EE}$ .

#### • V<sub>DD</sub>, V<sub>SS</sub>

These are power supply pins.  $V_{DD}$  is normally 2.7 to 5.5 V.  $V_{SS}$  is a grounding pin, which is normally set to 0 V.

#### • V<sub>1L</sub>, V<sub>2L</sub>, V<sub>5L</sub>, V<sub>EEL</sub>, V<sub>1R</sub>, V<sub>1R</sub>, V<sub>5R</sub>, V<sub>EER</sub>

These are LCD drive bias voltage pins. The  $V_1$  pin may be separated from the  $V_{DD}$  pin. Bias supply voltages are supplied from an external source.

#### **Truth Table**

| DF | Shift register data | DISP OFF | Driver output (O <sub>1</sub> to O <sub>100</sub> ) |

|----|---------------------|----------|-----------------------------------------------------|

| L  | L                   | Н        | $V_2$                                               |

| L  | Н                   | Н        | V <sub>EE</sub>                                     |

| Н  | L                   | Н        | V <sub>5</sub>                                      |

| Н  | Н                   | Н        | V <sub>1</sub>                                      |

| ×  | ×                   | L        | V <sub>1</sub>                                      |

×: Don't care

#### **NOTES ON USE**

Note the following when turning power on and off:

The LCD drivers of this IC requires a high voltage. If a high voltage is applied to them with the logic power supply floating, excess current flows. This may damage the IC. Be sure to carry out the following power-on and power-off sequences.

When turning power on:

First turn on the logic circuits, then the LCD drivers, or turn on both of them at the same time. When turning power off:

First turn off the LCD drivers, then the logic circuits, or turn off both of them at the same time.

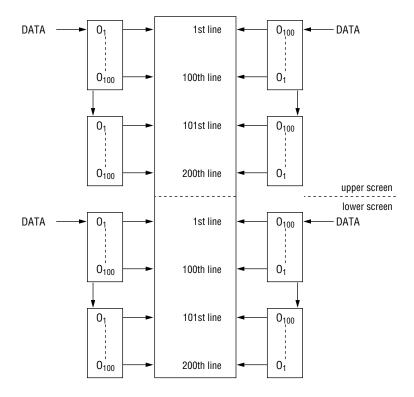

# **APPLICATION CIRCUITS**

# **Example of connecting to LCD panel**

In the case of 400 (200  $\times$  2) lines

In the case of 480 (240  $\times$  2) lines