# High Performance 512x8 PROM TiW PROM Family

53/63\$480 53/63\$481 53/63\$481A

#### Features/Benefits

- 30 ns maximum access time

- Reliable titanium-tungsten fuses (TIW) guarantees greater than 98% programming yields

- . Low voltage generic programming

- Pin-compatible with standard Schottky PROMs

- . PNP inputs for low input current

- . Open collector or three-state outputs

## **Applications**

- · Microprogram control store

- · Microprocessor program store

- Look-up table

- · Character generator

- Code converter

- Programmable Logic Element (PLE") with 9 inputs, 8 outputs, and 512 product terms per output

# Description

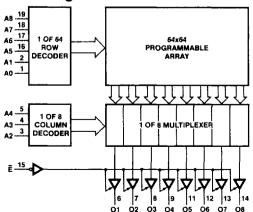

The 53/63S480 and 53/63S481/A are 512x8 bipolar PROMs featuring low input current PNP inputs, full Schottky clamping, and open collector or three-state outputs. The titanium-tungsten fuses store a logical low and are programmed to the high state. Special on-chip circuitry and extra fuses provide preprogramming testing which assures high programming yields and high reliability.

The 63 series is specified for operation over the commercial temperature and voltage range. The 53 series is specified for the military ranges.

## **Programming**

The 53/63S480 and 53/63S481/A PROMs are programmed with the same programming algorithm as all other Monolithic Memories' generic TiW PROMs. For details contact the factory.

#### **Selection Guide**

| MEMORY |              | PACKAGE |                     | OUTPUT | DEDEORMANCE | PART NUMBER  |                 |  |

|--------|--------------|---------|---------------------|--------|-------------|--------------|-----------------|--|

| SIZE   | ORGANIZATION | PINS    | TYPE                | 001701 | PERFORMANCE | 0°C to +75°C | -55°C to +125°C |  |

| 4K     | 512x8        | 20      | N,J<br>NL,L*,<br>F* | 70     | Enhanced    | 63S481A      | 53S481A         |  |

|        |              |         |                     | TS     | Standard    | 63S481       | 53S481          |  |

|        |              |         |                     | ОС     |             | 63S480       | 53\$480         |  |

<sup>\*</sup>Contact factory for package dimensions.

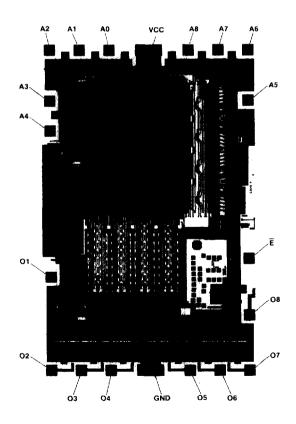

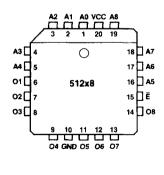

# **Pin Configurations**

# **Block Diagram**

PLE" is a trademark of Monolithic Memories.

TWX: 910-338-2376

Monolithic Memories

#### 53/63S480 53/63S481/A

| Absolute Maximum Ratings       | Operating      | Programming |

|--------------------------------|----------------|-------------|

| Supply voltage V <sub>CC</sub> |                |             |

| Input voltage                  |                |             |

| Input current                  |                |             |

| Off-state output voltage       | 0.5 V to 5.5 V |             |

| Storage temperature            | -65° to +150°C |             |

**Operating Conditions**

| SYMBOL | DADAMETED                      |     | MILITARY<br>MIN NOM MAX |     | COMMERCIAL<br>MIN NOM MAX |   | UNIT |    |

|--------|--------------------------------|-----|-------------------------|-----|---------------------------|---|------|----|

| Vcc    | Supply voltage                 | 4.5 | 5                       | 5.5 | 4.75                      | 5 | 5.25 | ٧  |

| TA     | Operating free-air temperature | -55 |                         | 125 | 0                         |   | 75   | °C |

# DC Electrical Characteristics Over Operating Conditions

| SYMBOL           | PARAMETER                      | TEST CONDITION                                                          |                               | MIN TYP                     | MAX | UNIT  |    |

|------------------|--------------------------------|-------------------------------------------------------------------------|-------------------------------|-----------------------------|-----|-------|----|

| VIL              | Low-level input voltage        | Guaranteed input logical low voltage for all inputs††                   |                               |                             |     | 0.8   | V  |

| VIH              | High-level input voltage       | Guaranteed input logical high voltage for all inputs††                  |                               |                             | 2   |       | ٧  |

| V <sub>IC</sub>  | Input clamp voltage            | V <sub>CC</sub> = MIN                                                   | MIN I <sub>I</sub> = -18 mA   |                             |     | -1.5  | V  |

| I <sub>IL</sub>  | Low-level input current        | V <sub>CC</sub> = MAX                                                   | V <sub>I</sub> = 0.4 V        | V <sub>1</sub> = 0.4 V      |     | -0.25 | mA |

| ΊΗ               | High-level input current       | V <sub>CC</sub> = MAX                                                   | VI = VCC MAX                  |                             |     | 40    | μΑ |

|                  | Low-level output voltage       | V <sub>CC</sub> = MIN                                                   | I <sub>OL</sub> = 16 mA       | Com                         | `   | 0.45  |    |

| VOL.             |                                |                                                                         |                               | Mil                         |     | 0.5   | V  |

|                  | 1 C - b - d d *   b *          | V <sub>CC</sub> = MIN                                                   | Com I <sub>OH</sub> = -3.2 mA |                             | 2.4 |       | ,, |

| VОН              | High-level output voltage*     |                                                                         | Mil I <sub>OH</sub> = -2 mA   | Mil I <sub>OH</sub> = -2 mA |     |       | V  |

| <sup>I</sup> OZL | O#*                            |                                                                         | V <sub>O</sub> = 0.4 V        | V <sub>O</sub> = 0.4 V      |     | -40   | _  |

| lozh             | Off-state output current*      | V <sub>CC</sub> = MAX                                                   | V <sub>O</sub> = 2.4 V        |                             | 40  |       | μΑ |

| CEX              | 0 11 11                        |                                                                         | V <sub>O</sub> = 2.4 V        |                             |     | 40    |    |

|                  | Open collector output current  | V <sub>CC</sub> = MAX                                                   | V <sub>O</sub> = 5.5 V        |                             |     | 100   | μA |

| los              | Output short-circuit current** | V <sub>CC</sub> = 5 V                                                   | V <sub>O</sub> = 0 V          | V <sub>O</sub> = 0 V        |     | -90   | mA |

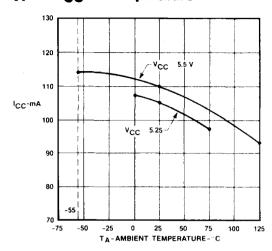

| lcc              | Supply current                 | y current V <sub>CC</sub> = MAX. All inputs grounded. All outputs open. |                               | 104                         | 155 | mA    |    |

# Switching Characteristics Over Operating Conditions (See standard test load)

| OPERATING<br>CONDITIONS | DEVICE TYPE      |      | (ns)<br>CCESS TIME | t <sub>EA</sub> ANI<br>ENABLE A<br>RECOV | UNIT |    |  |

|-------------------------|------------------|------|--------------------|------------------------------------------|------|----|--|

|                         |                  | TYP† | MAX                | TYP†                                     | MAX  |    |  |

|                         | 63S481A          | 22   | 30                 | 18                                       | 25   |    |  |

| COMMERCIAL              | 63S480, 63S481   | 22   | 45                 | 18                                       | 25   | 1  |  |

| MILITARY                | 53S481A          | 22   | 40                 | 18                                       | 30   | ns |  |

|                         | 53\$480, 53\$481 | 22   | 50                 | 18                                       | 35   |    |  |

<sup>†</sup> Typicals at 5.0 V V<sub>CC</sub> and 25°C T<sub>A</sub>.

<sup>††</sup> V<sub>IL</sub> and V<sub>IH</sub> limits are absolute values with respect to the device ground pin(s) and includes all overshoots due to test equipment noise.

# 5

# Typical ICC vs Temperature

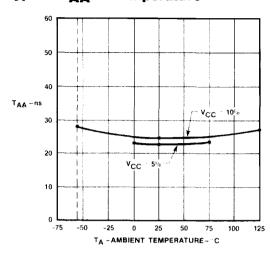

# Typical TAA vs Temperature

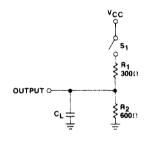

# **Switching Test Load**

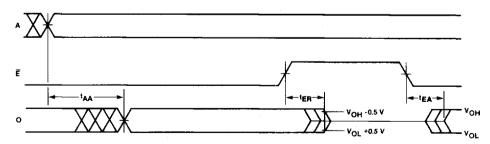

# **Definition of Timing Diagram**

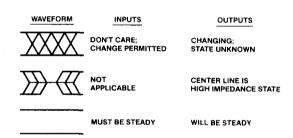

#### **Definition of Waveforms**

- NOTES. 1. Input pulse amplitude 0 V to 3.0 V.

- 2. Input rise and fall times 2-5 ns from 0.8 V to 2.0 V.

- 3. Input access measured at the 1.5 V level.

- 4.  $t_{AA}$  is tested with switch S<sub>1</sub> closed,  $C_L$  = 30 pF and measured at 1.5 V output level.

- 5. For open collector devices, TEA and TER are measured at the 1.5 V output level with  $S_1$  closed and  $C_L \equiv 30$  pF.

- For three-state devices, TEA is measured at the 1.5 V output level with C<sub>L</sub> = 30 pF S<sub>1</sub> is open for high-impedance to "1" test and closed for high-impedance to "0" test.

TER is tested with  $C_L \approx 5$  pF,  $S_1$  is open for "1" to high-impedance test, measured at  $V_{OH}$  =0.5 V output level;  $S_1$  is closed for "0" to high-impedance test measured at  $V_{OL} \approx 0.5$  V output level

## **Commercial Programmers**

Monolithic Memories PROMs are designed and tested to give a programming yield greater than 98%. If your programming yield is lower, check your programmer. It may not be properly calibrated.

Programming is final manufacturing — it must be quality-controlled. Equipment must be calibrated as a regular

routine, ideally under the actual conditions of use. Each time a new board or a new programming module is inserted, the whole system should be checked. Both timing and voltages must meet published specifications for the device.

Remember — The best PROMs available can be made unreliable by improper programming techniques.

#### PROM PROGRAMMING EQUIPMENT INFORMATION

SOURCE AND LOCATION

Data I/O Corp. 10525 Willows Rd. N.E. Redmond, WA 98073

Kontron Electronics, Inc. 630 Price Ave. Redwood City, CA 94063 Digelec Inc. 586 Weddell Dr. Suite 1 Sunnyvale, CA 94089

## **Metal Mask Layout**