#### **DESCRIPTION**

The Rockwell CMOS R65C52 Dual Asynchronous Communications Interface Adapter (DACIA) provides an easily implemented, program controlled two-channel interface between 8-bit microprocessor-based systems and serial communication data sets and moderns.

The DACIA is designed for maximum programmed control from the microprocessor (MPU) to simplify hardware implementation. Dual sets of registers allow independent control and monitoring of each channel.

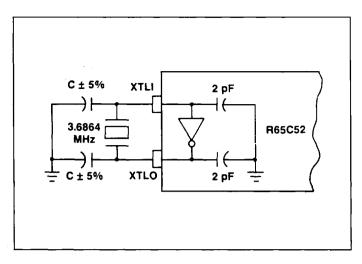

Transmitter and Receiver bit rates may be controlled by an internal baud rate generator or external times 16 clocks. The baud rate generator accepts either a crystal or a clock input, and provides 15 programmable baud rates. When a 3.6864 MHz crystal is used, the baud rates range from 50 bps to 38,400 bps.

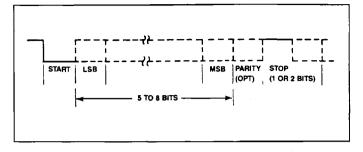

The DACIA may be programmed to transmit and receive frames having word lengths of 5, 6, 7 or 8 bits; even, odd, space, mark or no parity; and 1 or 2 stop bits.

A Compare Register, and the ability to detect address frames, facilitate address recognition in a multidrop mode.

#### **FEATURES**

- Low power CMOS N-well silicon gate technology

- Two independent full duplex channels with buffered receivers and transmitters.

- Data set/modem control functions

- Internal baud rate generator with 15 programmable baud rates (50 bps to 38,400 bps)

- Program-selectable internally or externally controlled receiver and transmitter bit rates

- Programmable word lengths, number of stop bits, and parity bit generation and detection

- Programmable interrupt control

- Edge detect for DCD, DSR, and CTS

- Program-selectable echo mode for each channel

- Compare Register

- Address/Data frame recognition

- 5.0 Vdc ±5% supply requirements

- 40-pin plastic or ceramic DIP or 44-pin PLCC

- Full TTL or CMOS input/output compatibility

- Compatible with R6500 and R65C00 microprocessors and R6500/\* microcomputers

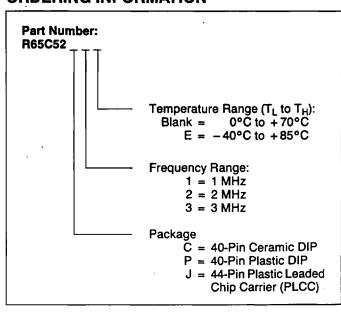

#### ORDERING INFORMATION

#### INTERFACE SIGNALS

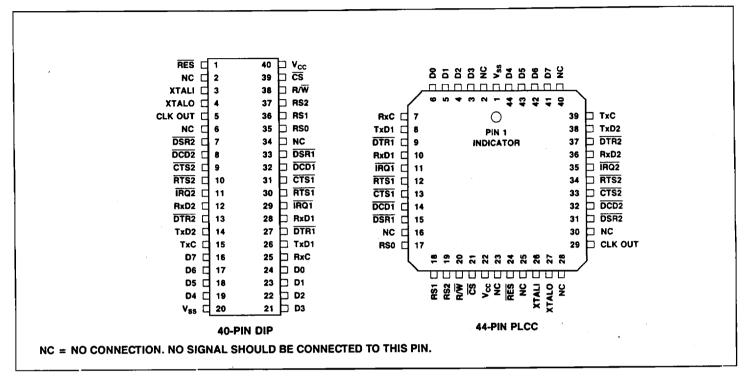

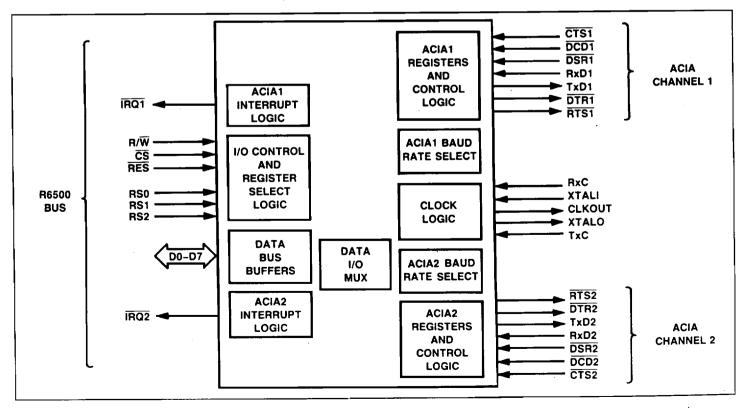

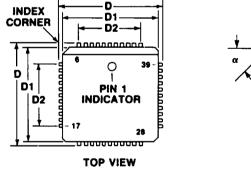

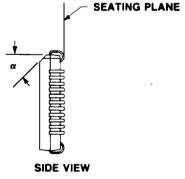

The DACIA is available in a 40-pin DIP or a 44-pin PLCC. Figure 1 shows the pin assignments for each package. The DACIA interface signals are shown in Figure 2. Table 1 contains a description of each signal.

Figure 1. R65C52 Pin Assignments

Figure 2. R65C52 DACIA Interface Signals

Table 1. DACIA Interface Signal Definitions

|                | Pin            | No.          |     | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|----------------|----------------|--------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Signal         | DIP            | PLCC         | 1/0 | Name/Description                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Host Interfa   | ce             |              |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| RES            | 1              | 24           | I   | Reset. Active low input controlling the reset function. This signal must be driven low for a minimum of 4 $\mu$ s for a valid reset to occur. It is driven high during normal operation.                                                                                                                                                                                                                                                                            |  |  |  |  |

| R/W            | 38             | 20           | 1   | <b>Read/Write.</b> Input controlling the direction of data transfer. It is driven low during write cycles, and is driven high at all other times.                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| CS             | 39             | 21           | ı   | <b>Chip Select.</b> Active low input enabling data transfers between the host CPU and the DACIA. The DACIA latches register selects and the $R/\overline{W}$ input on the falling edge of $\overline{CS}$ . It latches input data on the rising edge of $\overline{CS}$ .                                                                                                                                                                                           |  |  |  |  |

| RS0-RS3        | 35–37          | 17–19        | 1   | <b>Register Select.</b> Three inputs controlling access to the DACIA internal registers. Table 3 lists to coding for each register.                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| D0-D3<br>D4-D7 | 24–21<br>19–16 | 6–3<br>44–41 | 1/0 | Data Bus. Eight bidirectional lines used to transfer data between the host and the DACIA. These lines output data during READ cycles when $\overline{CS}$ is low. At all other times, they are in the high impedance state.                                                                                                                                                                                                                                         |  |  |  |  |

| IRQ1<br>IRQ2   | 29<br>11       | 11<br>35     | 0   | Interrupt Request. Two active low, open-drain outputs from the interrupt control logic. These output are normally high. An IRQ line goes low when one of the flags of the associated ISR is set if the corresponding enable bit is set in the IER.                                                                                                                                                                                                                  |  |  |  |  |

| Clock Inter    | ace            |              |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| XTALI<br>XTALO | 3<br>4         | 26<br>27     | 0   | Crystal Input/Output. One input and one output through which the reference signal for the internal clock oscillator is supplied. A parallel resonant crystal may be connected across the pins or a clock may be input at XTALI. When a clock is used, XTALO must be left open.                                                                                                                                                                                      |  |  |  |  |

| CLK OUT        | 5              | 29           | 0   | Clock Out. A buffered output from the internal clock oscillator which is in phase with XTALI. This output may be used to drive the XTALI input of another DACIA. Therefore, several DACIA chips may be driven with one crystal.                                                                                                                                                                                                                                     |  |  |  |  |

| RxC            | 25             | 7            | ı   | Receiver Clock. Input for external 16x receiver clock.                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| TxC            | 15             | 39           |     | Transmitter Clock. Input for external 16x transmitter clock.                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| Serial Chan    | nel Interfa    | ce           | 1   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| DTR1<br>DTR2   | 27<br>13       | 9<br>37      | 0   | Data Terminal Ready. Two general purpose outputs which are set high upon reset. The output level is programmed by setting the appropriate bit in the associated Format Register (FR) high or low. The state of each DTR line is reflected by the DTR LVL bit in the associated Control Status Registe (CSR).                                                                                                                                                        |  |  |  |  |

| DSR1<br>DSR2   | 33<br>7        | 15<br>31     | ı   | Data Set Ready. Two general purpose inputs. An active transition sets the DSRT bit in the Interrupt Status Register (ISR). The DSR LVL bit in the associated CSR reflects the current state of a DSR line.                                                                                                                                                                                                                                                          |  |  |  |  |

| RTS1<br>RTS2   | 30<br>10       | 12<br>34     | 0   | Request To Send. Two general purpose outputs which are set high upon reset. The output level is programmed by setting the appropriate bit in the associated FR high or low. The state of an RTS line is reflected by the RTS LVL bit in the associated CSR.                                                                                                                                                                                                         |  |  |  |  |

| CTS1<br>CTS2   | 31<br>9        | 13<br>33     | l   | Clear To Send. The CTS control line inputs allow handshaking by the transmitters. When CTS is low, the data is transmitted continuously. When CTS is high, the Transmit Data Register Empty bit (TDRE) in the associated ISR is not set. The word presently in the Transmit Shift Register is sent normally. Any active transition on a CTS line sets the CTST bit in the appropriate ISR. The CTS LVL bit in the associated CSR reflects the current state of CTS. |  |  |  |  |

| TxD1<br>TxD2   | 26<br>14       | 8<br>38      | 0   | <b>Transmit Data.</b> The TxD outputs transfer serial non-return to zero (NRZ) data to the data communication equipment (DCE). The data is transferred, LSB first, at a rate determined by the baud rate generator or external clock.                                                                                                                                                                                                                               |  |  |  |  |

| DCD1<br>DCD2   | 32<br>8        | 14<br>32     | 1   | Data Carrier Detect. Two general purpose inputs. An active transition sets the DCDT bit in the appropriate ISR. The DCD LVL bit in the associated CSR reflects the current state of a DCD line.                                                                                                                                                                                                                                                                     |  |  |  |  |

| RxD1<br>RxD2   | 28<br>12       | 10<br>36     | 1   | Receive Data. The RxD inputs transfer serial NRZ data into the DACIA from the DCE, LSB first. The receiver baud rate is determined by the baud rate generator or external clock.                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Power          |                | <u> </u>     | J   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| VCC            | 40             | 22           | 1   | DC Power Input, 5.0V ±5%.                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| VSS            | 20             | 1            | l , | Power and Signal Reference.                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

#### **FUNCTIONAL DESCRIPTION**

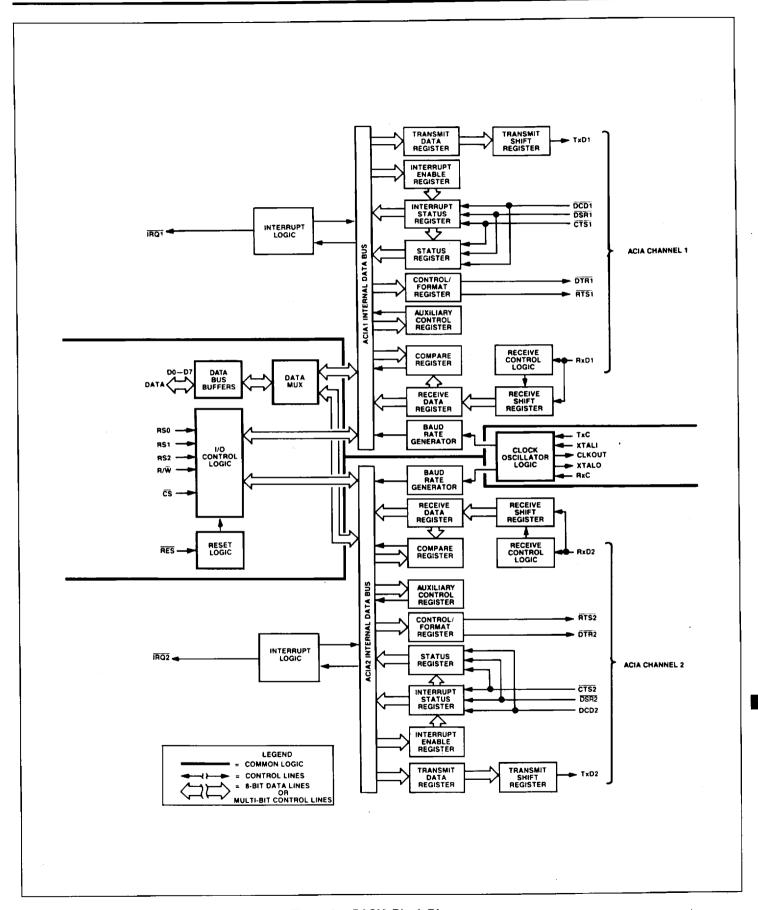

Figure 3 is a block diagram of the DACIA which consists of two asynchronous communications interface adapters with common microprocessor interface control logic and data bus buffers. The individual functional elements of the DACIA are described in the following paragraphs.

#### **RESET LOGIC**

The Reset Logic sets various internal registers, status bits and control lines to a known state. The  $\overline{RES}$  input must be driven low for a minimum of 4  $\mu s$  for a valid reset to occur. At this time, the IERs are set to \$80, the RDRs and ACRs are cleared, and the compare mode is disabled. Also, the  $\overline{DTR}$  and  $\overline{RTS}$  outputs are driven high and the  $\overline{CTS}$ ,  $\overline{DCD}$  and  $\overline{DSR}$  transition detect flags are cleared. No other bits are affected.

#### **DATA BUS BUFFER**

The Data Bus Buffer is a bidirectional interface between the data lines and the internal data bus. The state of the Data Bus Buffer is controlled by the I/O Control Logic and the Interrupt Logic. Table 2 summarizes the Data Bus Buffer states.

#### I/O CONTROL LOGIC

The I/O Control Logic controls data transfers between the Internal Registers and the Data Bus Buffer. Internal Register selection is determined by the Register Select inputs as shown in Table 3. When  $R/\overline{W}$  is high and  $\overline{CS}$  is low, data from the selected register

is transferred from the internal data bus to the data lines. When  $\overline{\text{CS}}$  is high, the DACIA is deselected and the data lines are tri-stated.

#### INTERRUPT LOGIC

The interrupt logic causes the  $\overline{IRQ}$  lines ( $\overline{IRQ1}$  or  $\overline{IRQ2}$ ) to go low when conditions are met that require the attention of the MPU. There are two registers (the Interrupt Enable Register and the Interrupt Status Register) involved in the control of interrupts in the DACIA. An  $\overline{IRQ}$  will be asserted on the transition of one of the flags in an ISR from 0 to 1 if the corresponding bit in the associated IER is set. The  $\overline{IRQ}$  line is negated when the ISR is read or when the interrupting condition is cleared. CAUTION: When the interrupt is generated by TDRE, 1/16 of a bit time must elapse before  $\overline{IRQ}$  can be cleared by reading the ISR.

#### **CLOCK OSCILLATOR LOGIC**

The internal clock oscillator supplies the time base for the baud rate generator. The oscillator can be driven by a crystal or an external clock.

The baud rate generator may be disabled by connecting XTALI to ground and leaving XTALO open. When this is done, a transmitter times 16 clock must be input at TxC, a receiver times 16 clock must be input at RxC and the Control Registers must be programmed to select TxC and RxC clocks.

Table 2. Data Bus Buffer Summary

| Contro | l Signals |                         |

|--------|-----------|-------------------------|

| R/W    | CS        | Data Bus Buffer State   |

| L      | L         | Write Mode — Tri-State  |

| H      | L         | Read Mode — Output Data |

| X      | Н         | Deselected — Tri State  |

Figure 3. DACIA Block Diagram

Table 3. DACIA Register Selection

|     | Registe | r Select |                         |                | Register                                | Accessed |                                |  |

|-----|---------|----------|-------------------------|----------------|-----------------------------------------|----------|--------------------------------|--|

|     | _       | nes      |                         | <del>.</del> . | Write                                   |          | Read                           |  |

| HEX | RS2     | RS1      | RS0                     | Symbol         | Name                                    | Symbol   | Name                           |  |

| 0   | L       | L        | L                       | IER1           | interrupt Enable<br>Register 1          | ISR1     | Interrupt Status<br>Register 1 |  |

| 1   | L       | L        | CR1 Control Register 11 | CSR1           | Control Status                          |          |                                |  |

| ,   |         | _        | П                       | FR1            | Format<br>Register 1 <sup>2</sup>       | - Coni   | Register 1                     |  |

| 2   | L       | н        | Ļ                       | CDR1           | Compare Data<br>Register 13             |          | Not Used                       |  |

| 2   | _       | П        | _                       | ACR1           | Auxiliary Control<br>Register 14        | ].       |                                |  |

| 3   | L       | н        | Н                       | TDR1           | Transmit Data<br>Register 1             | RDR1     | Receive Data<br>Register 1     |  |

| 4   | н       | L        | L                       | IER2           | Interrupt Enable<br>Register 2          | ISR2     | Interrupt Status<br>Register 2 |  |

| 5   | н       |          | н                       | CR2            | Control<br>Register 21                  | CSR2     | Control Status                 |  |

| J   | ''      | _        | •1                      | FR2            | Format<br>Register 2²                   |          | Register 2                     |  |

| 6   | н       | Н        | L                       | CDR2           | Compare Data<br>Register 2 <sup>3</sup> |          | Not Used                       |  |

|     |         |          |                         | ACR2           | Auxiliary Control<br>Register 24        |          |                                |  |

| 7   | н       | н        | н                       | TDR2           | Transmit Data<br>Register 2             | RDR2     | Receive Data<br>Register 2     |  |

#### Notes:

- 1. D7 must be set low to write to the Control Registers.

- D7 must be set high to write to the Format Registers.

Control Register bit 6 must be set to 0 to access the Compare Register.

- 4. Control Register bit 6 must be set to 1 to access the Auxiliary Control Register.

#### **SERIAL DATA CHANNELS**

Two independent serial data channels are available for the full duplex (simultaneous transmit and receive) transfer of asynchronous frames. Separate internal registers are provided for each channel for the selection of frame parameters (number of bits per character, parity options, etc.), status flags, interrupt control and handshake. The asynchronous frame format is shown in Figure 4.

Transmit data from the host system is loaded into the Transmit Data Register. From there, it is transferred to the Transmit Shift Register where it is shifted, LSB first, onto the TxD line. All transmissions begin with a start bit and end with the user selected number of stop bits. A parity bit is transmitted before the stop bit(s) if parity is enabled.

Receive data is shifted into the Receive Shift Register from the associated RxD line. Start and stop bits are stripped from the frame and the data is transferred to the Receive Data Register. Parity bits may be discarded or stored in the ISR.

Five I/O lines are provided for each channel for handshake with the data communications equipment (DCE). Four of these signals (RTS, DTR, DSR and DCD) are general purpose inputs or outputs. The fifth signal, CTS, enables/disables the transmitter. When CTS

is high and the Transmit Shift Register is empty, the transmitter (except for Echo Mode) is inhibited. When  $\overline{\text{CTS}}$  is low, the transmitter is enabled.

Figure 4. Asynchronous Frame Format

#### **INTERNAL REGISTERS**

The DACIA contains ten control registers and four status registers in addition to the transmit and receive registers. The Control Registers provide for control of frame parameters, baud rate, interrupt generation, handshake lines, transmission and reception. The status registers provide status information on transmit and receive registers, error conditions and interrupt sources. Table 4 summarizes the bit definitions of these registers. A detailed description follows.

Register Bit Reset Select Value R/W 7 (Hex) Register 76543210 6 5 4 3 2 1 0 0 ISR1 R ANY **CTST TDRE** DCDT DSRT F/O/B **RDRF** 1 - 00000 -PAR ISR2 BIT SET **CTST** DCDT IER1 W CLR/SET **TDRE** DSRT F/O/B **RDRF** PAR - 0000000 IER2 **BITS** ΙE ΙE ΙE ΙE ΙE ΙE ΙE CSR<sub>1</sub> **CTS** DCD DSR DTR 1 RTS FE TUR BRK - - - 011 5 CSR<sub>2</sub> LVL LVL LVL LVL LVL 1 CR1 W CDR/ STOP 0 **BIT RATE SEL ECHO** 5 CR2 **BITS ACR** DTR FR1 W PAR RTS 1 **DATA BITS** PAR SEL 5 FR2 CNTL CNTL 2 CDR<sub>1</sub> COMPARE DATA 6 CDR<sub>2</sub> (CR6 = 0)ACR1 2 W **TRNS** PAR UNUSED ----00 6 ACR2 (CR6 = 1)ERR/ST BRK 3 RDR1 R 00000000 RECEIVE DATA REGISTER 7 RDR2 3 TDR1 W TRANSMIT DATA REGISTER 7 TDR2

Table 4. Register Formats

#### **INTERRUPT STATUS REGISTERS (ISR1, ISR2)**

The Interrupt Status Registers are read-only registers indicating the status of each interrupt source. Bits 6 through 0 are set when the indicated IRQ condition has occurred. Bit 7 is set to a 1 when any IRQ source bit is set, or if Echo Mode is disabled, when CTS is high.

| 7                 | 6    | 5    | 4    | 3    | 2   | 1     | 0    |

|-------------------|------|------|------|------|-----|-------|------|

| ANY<br>BIT<br>SET | TORE | CTST | DCDT | DSRT | PAR | F/O/B | RDRF |

Address = 0.4

Reset Value = 1 - 00000 -

| ddress = 0,4 | Reset Value = 1 - 00000 -                                                    |

|--------------|------------------------------------------------------------------------------|

| Bit 7        | Any Bit Set Any bit (6 through 0) has been set to a 1 or CTS                 |

|              | is high with echo disabled                                                   |

| 0            | No bits have been set to a 1 or echo is enabled                              |

| Bit 6        | Transmit Data Register Empty (TDRE)                                          |

| 1            | Transmit Data Register is empty and CTS is low                               |

| 0 ,          | Transmit Data Register is full or CTS is high                                |

| Bit 5        | Transition On CTS Line (CTST)                                                |

| 1            | A positive or negative transition has occurred on CTS                        |

| 0            | No transition has occurred on CTS, or ISR has                                |

|              | been Read                                                                    |

|              |                                                                              |

| Bit 4        | Transition On DCD Line (DCDT)                                                |

| 1            | A positive or negative transition has occurred on DCD                        |

| 0            | No transition has occurred on DCD, or ISR has been Read                      |

|              |                                                                              |

| Bit 3        | Transition On DSR Line (DSRT)                                                |

| 1            | A positive or negative transition has occurred on DSR                        |

| 0            | No transition has occurred on $\overline{\text{DSR}}$ , or ISR has been Read |

| Bit 2        | Parity Status (PAR)  ACR bit 0 = 0                                           |

| 1            | A parity error has occurred in received data                                 |

| Ò            | No parity error has occurred, or the Receive Data                            |

| Ü            | Register (RDR) has been Read  ACR bit 0 = 1                                  |

| 1            | Parity bit = 1                                                               |

| Ó            | Parity bit = 0                                                               |

| J            | rainy bit = 0                                                                |

| Bit 1        | Frame Error, Overrun, Break                                                  |

## **INTERRUPT ENABLE REGISTERS (IER1, IER2)**

The Interrupt Enable Registers are write-only registers that enable/disable the IRQ sources. IRQ sources are enabled by writing to an IER with bit 7 set to a 1 and the bit for every IRQ source to be enabled set to a 1. IRQ sources are disabled by writing to an IER with bit 7 reset to a 0 and the bit for every source to be disabled set to a 1. Any source bit reset to 0 is unaffected and remains in its original state. Thus, writing \$7F to an IER disables all of that channel's interrupts and writing an \$FF to an IER enables all of that channel's interrupts.

| 7    | 6    | 5    | 4    | 3    | 2   | 1     | 0    |

|------|------|------|------|------|-----|-------|------|

| SET  | TDRE | CTST | DCDT | DSRT | PAR | F/O/B | RDRF |

| BITS | IE   | IE   | IE   | IE   | IE  | IE    | IE   |

| SET                                   | TDRE | CTST | DCDT | DSRT | PAR | F/O/B | RDRF |

|---------------------------------------|------|------|------|------|-----|-------|------|

| BITS                                  | IE   | IE   | IE   | IE   | IE  | IE    | IE   |

| Address = 0,4 Reset Value = - 0000000 |      |      |      |      |     |       |      |

| Bit 7    | Enable/Disable              |

|----------|-----------------------------|

| 1        | Enable selected IRQ source  |

| 0        | Disable selected IRQ source |

| Bits 0-6 |                             |

| 1        | Select for enable/disable   |

| 0        | No change                   |

#### **CONTROL STATUS REGISTERS (CSR1, CSR2)**

The Control Status Registers are read-only registers that provide I/O status and error condition information. A CSR is normally read after an IRQ has occurred to determine the exact cause of the interrupt condition.

| 7  | 6   | 5          | 4          | 3          | 2   | 1          | 0          |

|----|-----|------------|------------|------------|-----|------------|------------|

| FE | TUR | CTS<br>LVL | DCD<br>LVL | DSR<br>LVL | BRK | DTR<br>LVL | RTS<br>LVL |

| 1       |       | LVL                                        | LVL       |            |            |          | ~~~       |  |

|---------|-------|--------------------------------------------|-----------|------------|------------|----------|-----------|--|

| Address | = 1,5 | Reset Value = 1 011                        |           |            |            |          |           |  |

| Bit 7   | ,     | Framing Error (FE)                         |           |            |            |          |           |  |

| 1       |       | A frami                                    | ng error  | occurre    | ed in rec  | eive dat | a         |  |

| 0       |       | No fram                                    | ing erro  | r occurr   | ed, or the | e RDR w  | as read   |  |

| Bit 6   | i     | Transm                                     | itter Un  | nderrun    | (TUR)      |          |           |  |

| 1       |       | Transmi                                    | t Shift R | legister i | s empty    | and TDF  | RE is set |  |

| 0       |       | Transmi                                    | itter Shi | ft Regis   | ter is no  | t empty  |           |  |

| Bit 5   | 5     | CTS Le                                     | vel (CTS  | S LVL)     |            |          |           |  |

| 1       |       | CTS line is high                           |           |            |            |          |           |  |

| 0       |       | CTS line is low                            |           |            |            |          |           |  |

| Bit 4   | 1     | DCD Level (DCD LVL)                        |           |            |            |          |           |  |

| 1       |       | DCD lin                                    | e is hig  | h          |            |          |           |  |

| 0       |       | DCD lin                                    | e is low  | ,          |            |          | •         |  |

| Bit 3   | 3     | DSR Le                                     | vel (DS   | R LVL)     |            |          |           |  |

| 1.      |       | DSR lin                                    |           |            |            |          |           |  |

| . 0     |       | DSR line is low                            |           |            |            |          |           |  |

| Bit 2   | 2     | Receive                                    | e Break   | (BRK)      |            |          |           |  |

| 1       |       | A Receive Break has occurred               |           |            |            |          |           |  |

| 0       |       | No Receive Break occurred, or RDR was read |           |            |            |          |           |  |

| Bit 1   | i     | DTR Level (DTR LVL)                        |           |            |            |          |           |  |

| 1       |       |                                            |           |            |            |          |           |  |

DTR line is low

RTS line is high

RTS line is low

RTS Level (RTS LVL)

#### Note: To reset ISR

1

0

Bit 0

0

(a) bits 0, 1, 2: Read Receive Data Register

A framing error, receive overrun, or receive break

No error, overrun, break has occurred or RDR

has occurred or has been detected

Receive Data Register Full (RDRF) Receive Data Register is full

(b) bits 3, 4, 5: Read ISR

has been Read

(c) bit 6: Write Data Register

Receive Data Register is empty

0

Bit 0

1 0

# R65C52

# **Dual Asynchronous Communications Interface Adapter (DACIA)**

# **CONTROL REGISTERS (CR1, CR2)**

The Control Registers are write-only registers. They control access to the Auxiliary Control Register and the Compare Data Register. They select the number of stop bits, control Echo Mode, and select the data rate.

#### (Accessed when Bit 7 = 0)

| 7 | 6       | 5            | 4    | 3 | 2      | 1       | 0 |

|---|---------|--------------|------|---|--------|---------|---|

| 0 | CDR/ACR | STOP<br>BITS | ECHO |   | BAUD R | ATE SEL |   |

Address = 1,5

Reset Value = 0 -----

## **FORMAT REGISTERS (FR1, FR2)**

The Format Registers are write-only registers. They select the number of data bits per character and parity generation/checking options. They also control RTS and DTR.

## (Accessed when Bit 7 = 1)

| 7 | 6 5          | 4 3        | 2         | 1           | 0           |

|---|--------------|------------|-----------|-------------|-------------|

| 1 | DATA<br>BITS | PAR<br>SEL | PAR<br>EN | DTR<br>CNTL | RTS<br>CNTL |

Address ≈ 1,5

Reset Value = 1 -----

|   |      |            | .,- |                                                                                            |                  |                  |                                                   |

|---|------|------------|-----|--------------------------------------------------------------------------------------------|------------------|------------------|---------------------------------------------------|

|   |      | t 7        |     | Control or Format Register Access Control Register                                         |                  | it 7<br>1        | Control or Format Register Access Format Register |

|   | •    | t 6<br>1   |     | CDR/ACR Access the Auxiliary Control Register (ACR) Access the Compare Data Register (CDR) | Bits<br>6        | s 6-5<br>5       | Number of Data Bits Per Character                 |

|   |      | t 5<br>1   |     | Number of Stop Bits Per Character<br>Two stop bits<br>One stop bit                         | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | 5<br>6<br>7<br>8                                  |

|   |      | <b>t 4</b> |     | Echo Mode Selection<br>Echo Mode enabled<br>Echo Mode disabled                             |                  | s 4-3            | Parity Mode Selection                             |

| _ | Bits |            | -   | Baud Rate Selection                                                                        | 0                | 0                | Odd Parity                                        |

| 3 | 2    | 1          | 0   | (bits per second with 3.6864 MHz crystal)                                                  | 0                |                  | Even Parity                                       |

| 0 | 0    | 0          | 0   | 50                                                                                         | 1                | 0                | Mark in Parity bit                                |

| 0 | 0    | 0          | 1   | 109.2                                                                                      | 1                | 1                | Space in Parity bit                               |

| 0 | 0    | 1          | 0   | 134.58                                                                                     |                  |                  |                                                   |

| 0 | 0    | 1          | 1   | 150                                                                                        | Ri               | it 2             | Parity Enable                                     |

| 0 | 1    | 0          | 0   | 300                                                                                        |                  | 1                | Parity Enable Parity as specified by bits 4-3     |

| 0 | 1    | 0          | 1   | 600                                                                                        |                  | o                | No Parity                                         |

| 0 | 1    | 1          | 0   | 1200                                                                                       | ,                | •                | 140 r diffy                                       |

| 0 | 0    | 0          | 1   | 1800<br>2400                                                                               |                  |                  |                                                   |

| 1 | 0    | 0          | 1   | 3600                                                                                       | Bi               | it 1             | DTR Control                                       |

| 1 | 0    | 1          | Ö   | 4800                                                                                       |                  | 1                | Set DTR high                                      |

| 1 | 0    | 1          | 1   | 7200                                                                                       | . (              | 0                | Set DTR low                                       |

| 1 | 1    | ò          | 0   | 9600                                                                                       |                  |                  |                                                   |

| 1 | 1    | Ö          | 1   | 19200                                                                                      | Di               | it O             | RTS Control                                       |

| 1 | 1    | 1          | ò   | 38400                                                                                      |                  | 1                | Set RTS high                                      |

| 1 | 1    | 1          | 1   | External TxC and RxC X16 Clocks                                                            |                  | 0                | Set RTS low                                       |

|   | -    | -          | -   |                                                                                            | ,                | -                | COLLING TOTAL                                     |

#### **COMPARE DATA REGISTERS (CDR1, CDR2)**

The Compare Data Registers are write-only registers which can be accessed when CR bit 6=0. By writing a value into the CDR, the DACIA is put in the compare mode. In this mode, setting of the RDRF bit is inhibited until a character is received which matches the value in the CDR. The next character is then received and the RDRF bit is set. The receiver will now operate normally until the CDR is again loaded.

#### (Control Register bit 6 = 0)

| 7 | 6 | 5 | 4     | 3       | 2 | 1 | 0 |

|---|---|---|-------|---------|---|---|---|

|   |   |   | COMPA | RE DATA |   |   |   |

Address = 2,6

Reset Value = -----

#### **AUXILIARY CONTROL REGISTERS (ACR1, ACR2)**

The Auxiliary Control Registers are write-only registers. Bits 7-2 are unused. Bit 1 causes the transmitter to transmit a BREAK. Bit 0 determines whether parity error or the parity bit is displayed in ISR bit 2.

#### (Control Register bit 6 = 1)

| 7 | 6 | 5   | 4    | 3 | 2 | 1           | 0             |

|---|---|-----|------|---|---|-------------|---------------|

|   |   | NOT | JSED |   |   | TRNS<br>BRK | PAR<br>ERR/ST |

Address = 2,6

Address = 3.7

Reset Value = ----- 00

Reset Value = 00000000

| Bits 7-2 | Not Used                                       |

|----------|------------------------------------------------|

| Bit 1    | Transmit Break (TRNS BRK)                      |

| 1        | Transmit continuous Break                      |

| 0        | Normal transmission                            |

| Bit 0    | Parity Error/State (PAR ERR/ST)                |

| 1        | Send value of parity bit to ISR bit 2 (Address |

|          | Recognition mode)                              |

| 0        | Send Parity Error status to ISR bit 2          |

#### RECEIVE DATA REGISTERS (RDR1, RDR2)

The Receive Data Registers are read-only registers which are loaded with the received data character of each frame. Start bits, stop bits and parity bits are stripped off of incoming frames before the data is transferred from the Receive Shift Register to the Receive Data Register. For characters of less than eight bits, the unused bits are the high order bits which are set to 0.

| MSB |   |   |        |         |   |   | LSB |

|-----|---|---|--------|---------|---|---|-----|

| 7   | 6 | 5 | 4      | 3       | 2 | 1 | 0   |

|     |   |   | RECEIV | /E DATA |   |   |     |

#### TRANSMIT DATA REGISTERS (TDR1, TDR2)

The Transmit Data Registers are write-only registers which are loaded from the CPU with data to be transmitted. For data characters of less than eight bits, the unused bits are the high order bits which are "don't care".

| MSB     |      |   |       |         |         |           | LSB |

|---------|------|---|-------|---------|---------|-----------|-----|

| 7       | 6    | 5 | 4     | 3       | 2       | 1         | 0   |

|         |      |   | TRANS | ATA TIN |         |           |     |

| Addross | - 27 |   |       |         | Pacet \ | /alue = = |     |

#### **OPERATION**

# **TERMINATION OF UNUSED INPUTS**

Noise on floating inputs can affect chip operation. All unused inputs must be terminated. If the baud rate generator is bypassed, XTALI must be connected to ground (XTALO is an output and must be left open). If the external clock mode is not used, RxC and TxC may be tied either to +5V or to ground. If the handshake inputs are not needed, the  $\overline{CTS}$  inputs should be tied low to enable the transmitters. The  $\overline{DCD}$  and  $\overline{DSR}$  inputs may either be tied high or low.

#### RESET INITIALIZATION

During power on initialization, all readable registers should be read to assure that the status registers are initialized. Specifically, the RDRF bit of the Interrupt Status Registers is not initialized by reset. The Receiver Data Registers must be read to clear this bit.

TDRE IRQ is generated only on the transition of the corresponding TDR from full to empty. Initialization software must account for this occurrence.

#### **BAUD RATE CLOCK OPTIONS**

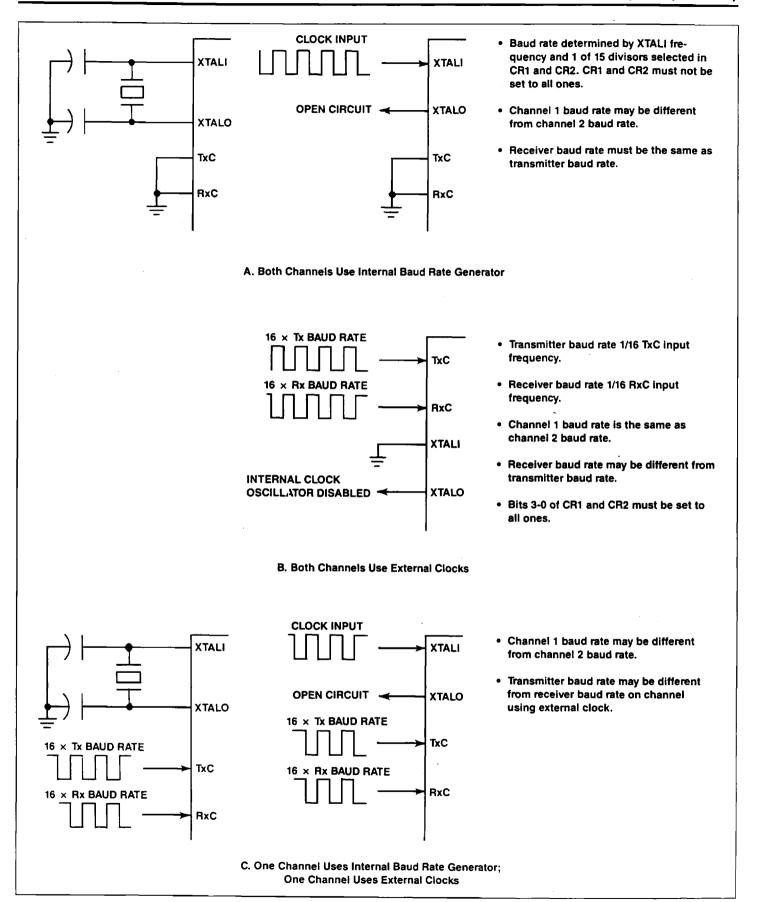

The receiver and transmitter clocks may be supplied either by the internal Baud Rate Generator or by use r supplied external clocks. Both channels may use the same clock source or one may use the Baud Rate Generator and the other channel external clocks. If both channels use the Baud Rate Generator, each channel may have a different bit rate. The options are shown in Figure 5.

An internal clock oscillator supplies the time base for the Baud Rate Generator. The oscillator can be driven by a crystal or an external clock.

If the on-chip oscillator is driven by a crystal, a parallel resonant crystal is connected between the XTALI and XTALO pins. The equivalent oscillator circuit is shown in Figure 6.

A parallel resonant crystal is specified by its load capacitance and series resonant resistance. For proper oscillator operation, the load capacitance ( $C_L$ ), series resistance ( $R_s$ ) and the crystal resonant frequency (F) must meet the following two relations:

$$(C + 2) = 2C_L$$

or  $C = 2C_L - 2$

$$R_s \le R_{smax} = \frac{2 \times 10^6}{(FC_L)^2}$$

where: F is in MHz; C and CL are in pF; R is in ohms.

To select a parallel resonant crystal for the oscillator, first select the load capacitance from a crystal manufacturer's catalog. Next, calculate  $R_{\mathsf{smax}}$  based on F and  $C_L$ . The selected crystal must have a  $R_\mathsf{s}$  less than the  $R_{\mathsf{smax}}$ .

Figure 5. Baud Rate Clock Options

Figure 6.

For example, if  $C_L = 22 \text{ pF}$  for a 3.6864 MHz parallel resonant crystal, then

$C = (2 \times 22) - 2 = 42 pF$  (use standard value of 43 pF)

The series resistance of the crystal must be less than

$$R_{smax} = \frac{2 \times 10^6}{(3.6864 \times 22)^2} = 304 \text{ ohms}$$

If the on-chip oscillator is driven by an external clock, the clock is input at XTALI and XTALO is left open.

An internal counter/divider circuit divides the frequency input at XTALI by the divisor selected in bits 3 through 0 of the Control Registers. Table 5 lists the divisors that may be selected and shows the bit rates generated with a 3.6864 MHz crystal or clock input. Other bit rates may be generated by changing the clock or crystal frequency. However, the input frequency must not exceed 4 MHz.

For external clock operation, a transmitter times 16 clock must be supplied at TxC and a receiver times 16 clock must be input at RxC. Since there are separate receiver and transmitter clock inputs, the receiver data rate may be different from the transmitter data rate.

Table 5. Baud Rate Generator Divisor Selection

| Control<br>Register<br>Bits |   |   |   | Divisor Selected<br>For The | Baud Rate Generated<br>With 3.6864 MHz             | Baud Rate Generated* With a Crystal or Clock |

|-----------------------------|---|---|---|-----------------------------|----------------------------------------------------|----------------------------------------------|

| 3                           | 2 | 1 | 0 | Internal Counter            | Crystal or Clock                                   | of Frequency (f)                             |

| 0                           | 0 | 0 | 0 | 73,728                      | $(3.6864 \times 10^{\circ})/73,728 = 50$           | f/73,728                                     |

| 0                           | 0 | 0 | 1 | 33,538                      | $(3.6864 \times 10^{\circ})/33,538 = 109.92$       | f/33,538                                     |

| 0                           | 0 | 1 | 0 | 27,408                      | $(3.6864 \times 10^{\circ})/27,408 \approx 134.58$ | f/27,408                                     |

| 0                           | 0 | 1 | 1 | 24,576                      | $(3.6864 \times 10^{\circ})/24,576 \approx 150$    | 1/24,576                                     |

| 0                           | 1 | 0 | 0 | 12,288                      | $(3.6864 \times 10^{\circ})/12,288 = 300$          | f/12,288                                     |

| 0                           | 1 | 0 | 1 | 6,144                       | $(3.6864 \times 10^{\circ})/6,144 \approx 600$     | f/6,144                                      |

| 0                           | 1 | 1 | 0 | 3,072                       | $(3.6864 \times 10^{\circ})/3,072 = 1,200$         | f/3,072                                      |

| 0                           | 1 | 1 | 1 | 2,048                       | $(3.6864 \times 10^{\circ})/2,048 = 1,800$         | f/2,048                                      |

| 1                           | 0 | 0 | 0 | 1,536                       | $(3.6864 \times 10^{\circ})/1,536 = 2,400$         | f/1,536                                      |

| 1                           | 0 | 0 | 1 | 1,024                       | $(3.6864 \times 10^{\circ})/1,024 \approx 3,600$   | f/1,024                                      |

| 1                           | 0 | 1 | 0 | 768                         | $(3.6864 \times 10^{\circ})/768 = 4,800$           | f/768                                        |

| 1                           | 0 | 1 | 1 | 512                         | $(3.6864 \times 10^{\circ})/512 \approx 7,200$     | f/512                                        |

| 1                           | 1 | 0 | 0 | 384                         | $(3.6864 \times 10^6)/384 = 9,600$                 | f/384                                        |

| 1                           | 1 | 0 | 1 | 192                         | (3.6864 × 10°)/192 = 19,200                        | f/192                                        |

| 1                           | 1 | 1 | 0 | 96                          | $(3.6864 \times 10^{6})/96 = 38,400$               | f/96                                         |

| 1                           | 1 | 1 | 1 | 16                          | Transmitter Baud Rate = TxC/16                     | Receiver Baud Rate = RxC/16                  |

\*Baud Rate =

$$\frac{\text{Frequency}}{\text{Divisor}}$$

#### **CONTINUOUS DATA TRANSMIT**

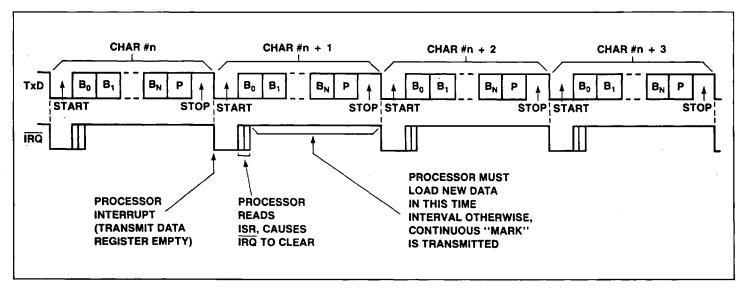

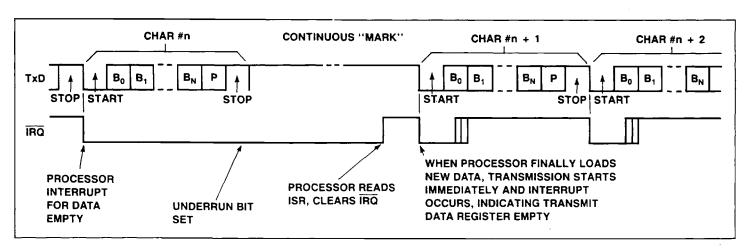

In the normal operating mode, the TDRE bit in the ISR signals the MPU that the DACIA is ready to accept the next data word. An  $\overline{\text{IRQ}}$  occurs on the transition of the TDR from full to empty if the corresponding TDRE  $\overline{\text{IRQ}}$  enable bit is set in the IER. The TDRE bit is set at the beginning of the start bit. When the MPU writes a word

to the TDR the TDRE bit is cleared. In order to maintain continuous transmission the TDR must be loaded before the stop bit(s) are ended. 1/16 of a bit time after  $\overline{IRQ}$  goes low, the  $\overline{IRQ}$  line may be reset by reading the ISR.  $\overline{IRQ}$  will always reset when data is written to the TDR. Figure 7 shows the relationship between  $\overline{IRQ}$  and TxD for the Continuous Data Transmit mode.

Figure 7. Continuous Data Transmit

#### TRANSMIT UNDERRUN CONDITION

If the MPU is unable to load the TDR before the last stop bit is sent, the TxD line goes to the MARK condition and the underrun flag

(TUR) is set. This condition persists until the TDR is loaded with a new word. Figure 8 shows the relation between IRQ and TxD for the Transmit Underrun Condition.

Figure 8. Transmit Underrun Condition Relationship

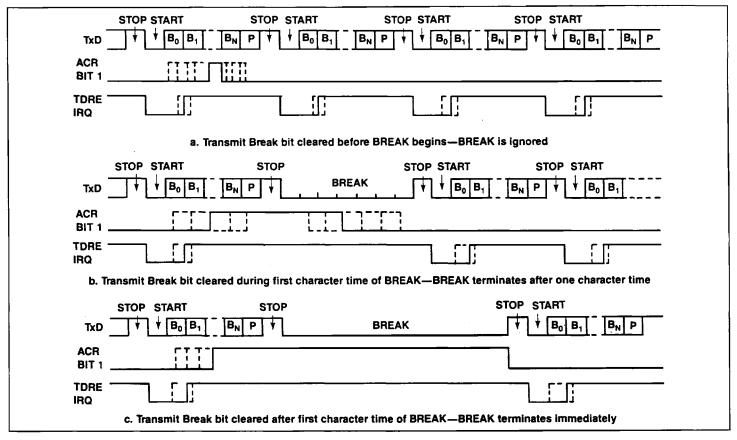

#### TRANSMIT BREAK CHARACTER

A BREAK may be transmitted by setting bit 1 of the ACR (Transmit Break bit) to a 1. The BREAK is transmitted after the character in the Transmit Shift Register is sent. If there is a character in the Transmit Data Register, it will be transmitted after the BREAK is terminated. The Transmit Break bit must remain set for at least

one character time to assure that a proper BREAK is transmitted. If the Transmit Break bit is cleared before one character time of BREAK has been transmitted, the BREAK will be terminated after one character time has elapsed. If the Transmit Break bit is cleared after one character time of BREAK has been transmitted, the BREAK will be terminated immediately. Figure 9 shows the relationship of TxD, IRQ and ACR bit 1 for various BREAK options.

Figure 9. Transmit BREAK

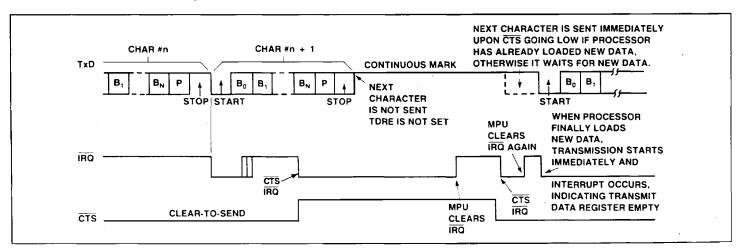

#### **EFFECTS OF CTS ON TRANSMITTER**

The CTS control line controls the transmission of data or the handshaking of data to a "busy" device (such as a printer). When the CTS line is low, the transmitter operates normally. A high condition inhibits the TDRE bit in the ISR from becoming set. Transmission of the word currently in the shift register is completed but any word in the TDR is held until CTS goes low.

Any transition on CTS sets bit 5 (CTST) of the ISR. A high on CTS forces bit 6 (TDRE) of the ISR to a 0. Bit 7 of the ISR also goes to a 1 when CTS is high, if Echo Mode is disabled. Thus, when the ISR is \$80, it means that CTS is high and no interrupt source requires service. A processor interrupt will not be generated under these circumstances, but an ISR polling routine should accommodate this.

Figure 10. Effects of CTS on Transmitter

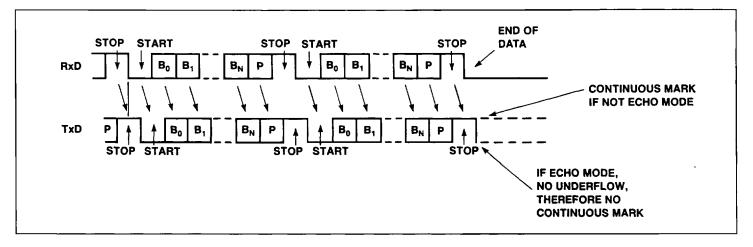

#### **ECHO MODE TIMING**

In the Echo Mode, the TxD line re-transmits the data received on the RxD line, delayed by 1/2 of a bit time. An internal underrun mode must occur before Echo Mode will start transmitting. In normal transmit mode if TDRE occurs (indicating end of data) an underflow flag would be set and continuous Mark transmitted. If Echo is initiated, the underflow flag will not be set at end of data and continuous Mark will not be transmitted. Figure 11 shows the relationship of RxD and TxD for Echo Mode.

Figure 11. Echo Mode Timing

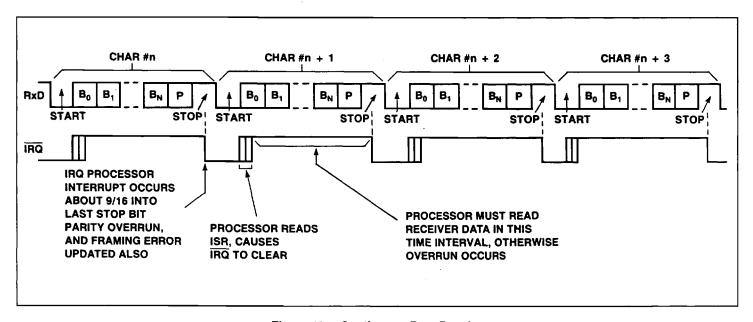

#### **CONTINUOUS DATA RECEIVE**

The normal receive mode sets the RDRF bit in the ISR when the DACIA channel has received a full data word. This occurs at about the 9/16 point through the stop bit. The processor must read the

RDR before the next stop bit, or an overrun error occurs. Figure 12 shows the relationship between IRQ and RxD for the continuous Data Receive mode.

Figure 12. Continuous Data Receive

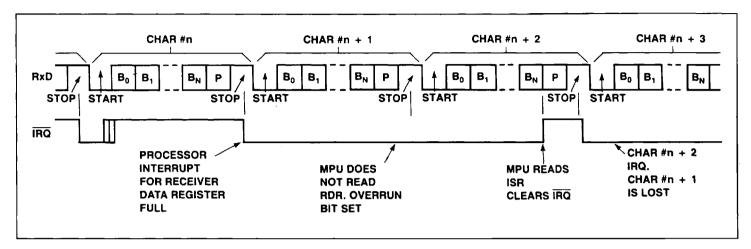

#### **EFFECTS OF OVERRUN ON RECEIVER**

If the processor does not read the RDR before the stop bit of the next word, an overrun error occurs, the overrun bit is set in the ISR, and the new data word is not transferred to the RDR. The RDR

contains the last word not read by the MPU and all following data is lost. The receiver will return to normal operation when the RDR is read. Figure 13 shows the relationship of IRQ and RxD when overrun occurs.

Figure 13. Effects of Overrun on Receiver

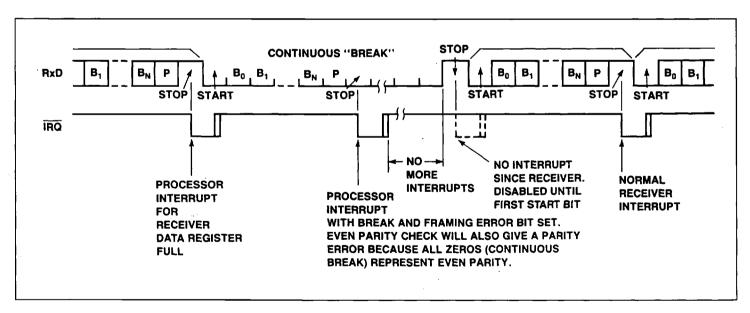

#### RECEIVE BREAK CHARACTER

When a Break character is received, the Break bit is set. The receiver does not set the RDRF bit and remains in this state until a stop bit is received. At this time the next character is received

normally. Figure 14 shows the relationship of IRQ and RxD for a Receive Break Character.

Figure 14. Receive Break Character

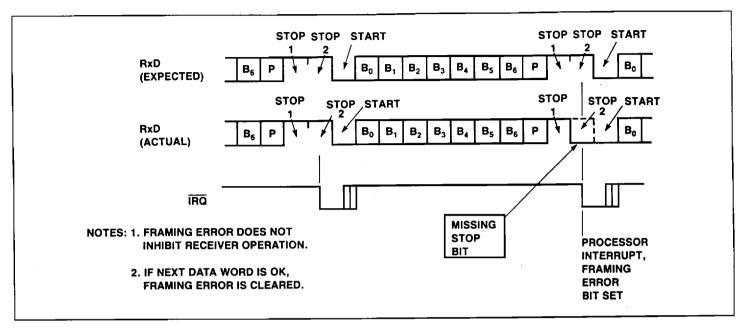

#### FRAMING ERROR

Framing error is caused by the absence of stop bit(s) on received data. The framing error bit is set when the RDRF bit is set. Subsequent data words are tested separately, so the status bit always

reflects the last data word received. Figure 15 shows the relationship of IRQ and RxD when a framing error occurs.

Figure 15. Framing Error

# PARITY ERROR DETECT/ADDRESS FRAME RECOGNITION

The Parity Status bit (ISR bit 2) may be programmed to indicate parity errors (ACR bit 0 = 0) or to display the parity bit received (ACR bit 0 = 1).

In applications where parity checking is used, one of the parity checking modes is enabled by setting bits 2, 3 and 4 of the Format Register to the desired option and bit 0 of the Auxiliary Control Register is reset to 0. Then, when the RDRF bit (bit 0) is set in the ISR, the PAR bit (bit 2) will be set when a parity error is detected.

In multi-drop applications, the parity bit is used as an address/data flag. It is set to 1 for address frames and is 0 on data frames. For

this type of operation, bit 0 of the ACR is set to a 1 and bits 2, 3 and 4 of the FR select a parity checking mode. Then, ISR bit 2 will be set to a 1 by incoming address frames and it will be a 0 on data frames.

## **COMPARE MODE**

The Compare Mode is automatically enabled, i.e., the channel is put to sleep, whenever data is written to the Compare Data Register. NOTE: Bit 6 of the Control Register must be set to 0 to enable access to the Compare Data Register. When the channel is in the compare mode, the RDRF bit (bit 0 of the ISR) is forced to a 0. Upon receipt of a matching character, normal receiver operation resumes and the RDRF bit (bit 0 of the ISR) will be set upon receipt of the *next* character.

# **SPECIFICATIONS**

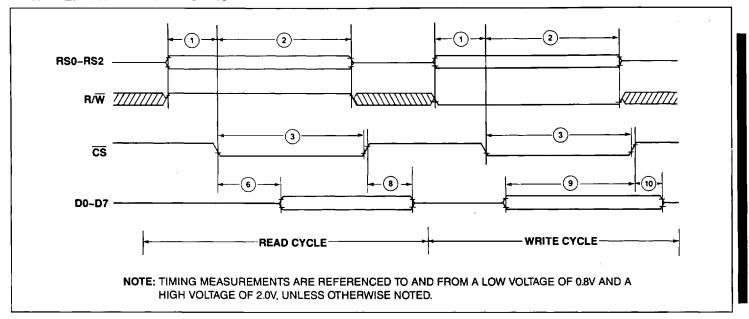

#### **DACIA READ/WRITE WAVEFORMS**

## DACIA READ/WRITE CYCLE TIMING

( $V_{CC}$  = 5 Vdc ±5%,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ , unless otherwise noted)

|        |                                       |                  | 1 MHz |      | 2 MHz    |      | 3 MHz |      |      |  |

|--------|---------------------------------------|------------------|-------|------|----------|------|-------|------|------|--|

| Number | Characteristic                        | Symbol           | Min.  | Max. | Min.     | Max. | Min.  | Max. | Unit |  |

| 1      | R/W, RS0-RS2 Valid to CS Low (Setup)  | T <sub>RSU</sub> | 5     | _    | 5        | _    | 5     | _    | ns   |  |

| 2 .    | CS Low to R/W, RS0-RS2 Invalid (Hold) | T <sub>RH</sub>  | 45    | _    | 45       |      | 45    |      | ns   |  |

| 3      | CS Pulse Width                        | T <sub>CP</sub>  | 410   | _    | 340      |      | 210   | _    | ns   |  |

| 6      | CS Low to Data Valid (Read)           | T <sub>CDV</sub> |       | 360  | <u> </u> | 290  |       | 170  | ns   |  |

| 8      | CS High to Data Invalid (Read)        | T <sub>CDR</sub> | 10    | 50   | 10       | 50   | 10    | 50   | ns   |  |

| 9      | Data Valid to CS High (Write, Setup)  | T <sub>DSU</sub> | 30    |      | 30       | _    | 30    | _    | ns   |  |

| 10     | CS High to Data Invalid (Write Hold)  | T <sub>CDW</sub> | 10    | _    | 10       | -    | 10    | _    | ns   |  |

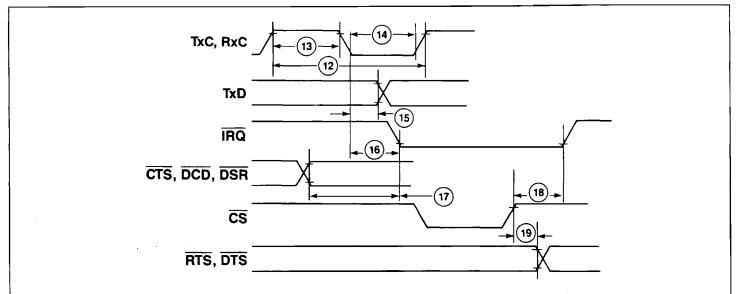

#### DACIA TRANSMIT/RECEIVER WAVEFORMS

NOTE: TRQ WILL NOT CHANGE STATE WHEN CS IS LOW. NOTE: TIMING MEASUREMENTS ARE REFERENCED TO AND FROM A LOW VOLTAGE OF 0.8V AND A HIGH VOLTAGE OF 2.0V, UNLESS OTHERWISE NOTED.

#### TRANSMIT/RECEIVE AND INTERRUPT ACKNOWLEDGE TIMING

( $V_{CC}$  = 5 Vdc ±5%,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ , unless otherwise noted)

| Number          | Characteristic                    | Symbol           | Min. | Мах. | Unit |

|-----------------|-----------------------------------|------------------|------|------|------|

| TRANSMIT/RECEIV | E TIMING                          | <del></del>      |      |      |      |

| 12              | Transmit/Receive Clock Rate       | t <sub>CY</sub>  | 300  | -    | ns   |

| 13              | Transmit/Receive Clock High       | t <sub>сн</sub>  | 125  | _    | ns   |

| 14              | Transmit/Receive Clock Low        | t <sub>CL</sub>  | 125  | -    | ns   |

| 15              | TxC, RxC to TxD Propagation Delay | t <sub>DD</sub>  |      | 285  | ns   |

| 16              | TxC, RxC to IRQ Propagation Delay | t <sub>DI</sub>  |      | 285  | ns   |

| 17              | CTS, DCD, DSR Valid to IRQ Low    | t <sub>CTI</sub> | _    | 150  | ns   |

| 18              | IRQ Propagation Delay (Clear)     | t <sub>IRQ</sub> | _    | 150  | ns   |

| 19              | RTS, DTR Propagation Delay        | t <sub>DLY</sub> | _    | 150  | ns   |

# R65C52

# **Dual Asynchronous Communications Interface Adapter (DACIA)**

## **ABSOLUTE MAXIMUM RATINGS\***

| Parameter                                         | Symbol           | Value                        | Unit |

|---------------------------------------------------|------------------|------------------------------|------|

| Supply Voltage                                    | V <sub>cc</sub>  | -0.3 to +7.0                 | Vdc  |

| Input Voltage                                     | V <sub>IN</sub>  | -0.3 to V <sub>CC</sub> +0.3 | Vdc  |

| Output Voltage                                    | V <sub>OUT</sub> | -0.3 to V <sub>CC</sub> +0.3 | Vdc  |

| Operating Temperature<br>Commercial<br>Industrial | T <sub>A</sub>   | 0 to +70<br>-40 to +85       | °C   |

| Storage Temperature                               | T <sub>STG</sub> | - 55 to +150                 | °C   |

\*NOTE: Stresses above those listed may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in other sections of this document is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **OPERATING CONDITIONS**

| Parameter                                     | Symbol          | Value                        |

|-----------------------------------------------|-----------------|------------------------------|

| Supply Voltage                                | V <sub>CC</sub> | 5V ± 5%                      |

| Temperature Range<br>Commercial<br>Industrial | T <sub>A</sub>  | 0 to 70°C<br>- 40°C to +85°C |

## DC CHARACTERISTICS

(V<sub>CC</sub> = 5.0 V  $\pm$ 5%, V<sub>SS</sub> = 0, T<sub>A</sub> = T<sub>L</sub> to T<sub>H</sub>, unless otherwise noted)

| Parameter                                                                       | Symbol           | Min          | Тур      | Max                                            | Unit .   | Test Conditions                                      |

|---------------------------------------------------------------------------------|------------------|--------------|----------|------------------------------------------------|----------|------------------------------------------------------|

| Input High Voltage Except XTALI XTALI                                           | V <sub>IH</sub>  | +2.0<br>+3.0 |          | V <sub>CC</sub> + 0.3<br>V <sub>CC</sub> + 0.3 | ٧        |                                                      |

| Input Low Voltage Except XTALI XTALI                                            | V <sub>IL</sub>  | -0.3<br>-0.3 |          | + 0.8<br>+ 0.4                                 | ٧        |                                                      |

| Input Leakage Current R/W, RES, RS0, RS1, RS2, RxD, CTS, DCD, DSR, RxC, TxC, CS | I <sub>IN</sub>  | _            | 10       | 50                                             | μА       | $V_{IN} = 0V \text{ to } 5.0V$<br>$V_{CC} = 5.25V$   |

| Input Leakage Current for Three-State Off<br>D0-D7                              | I <sub>TSI</sub> | -            | ±2       | 10                                             | μΑ       | $V_{IN} = 0.4V \text{ to } 2.4V$<br>$V_{CC} = 5.25V$ |

| Output High Voltage<br>D0-D7, TxD, CLK OUT, RTS, DTR                            | V <sub>OH</sub>  | + 2.4        | _        | _                                              | V        | $V_{CC} = 4.75V$ $I_{LOAD} = -100 \mu\text{A}$       |

| Output Low Voltage D0-D7, TxD, CLK OUT, RTS, DTR                                | V <sub>OL</sub>  | _            | _        | + 0.4                                          | ٧        | $V_{CC} = 4.75V$ $I_{LOAD} = 1.6 \text{ mA}$         |

| Output Leakage Current (Off State)                                              | I <sub>OFF</sub> | _            | ±2       | ± 10                                           | μA       | $V_{CC} = 5.25V$<br>$V_{OUT} = 0 \text{ to } 2.4V$   |

| Power Dissipation                                                               | P <sub>D</sub>   |              | _        | 10                                             | mW/MHz   |                                                      |

| Input Capacitance Except XTALI XTALI                                            | C <sub>IN</sub>  | _ ·          | <u> </u> | 5<br>10                                        | pF<br>pF | $V_{CC} \approx 5.0V$ $V_{IN} = 0V$ $f = 2 MHz$      |

| Output Capacitance                                                              | C <sub>OUT</sub> |              |          | 10                                             | pF       | T <sub>A</sub> = 25°C                                |

#### Notes:

- 1. All units are direct current (dc) except for capacitance.

- 2. Negative sign indicates outward current flow, positive indicates inward flow.

- 3. Typical values are shown for  $V_{CC} = 5.0V$  and  $T_A = 25$  °C.

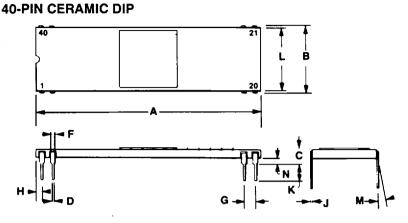

# PACKAGE DIMENSIONS

|     | MILLIMETERS |       | INCHES    |       |

|-----|-------------|-------|-----------|-------|

| DIM | MIN         | MAX   | MIN       | MAX   |

| A   | 50.29       | 51.31 | 1.980     | 2.020 |

| 8   | 15.11       | 15.88 | 0.595     | 0.625 |

| С   | 2.54        | 4.19  | 0.100     | 0.165 |

| D   | 0.38        | 0.53  | 0.015     | 0.021 |

| F   | 0.76        | 1.27  | 0.030     | 0.050 |

| G   | 2.54 BSC    |       | 0.100 BSC |       |

| Н   | 0.76        | 1.78  | 0.030     | 0.070 |

| J   | 0.20        | 0.33  | 0.008     | 0.013 |

| K   | 2.54        | 4.19  | 0.100     | 0.165 |

| L   | 14.60       | 15.37 | 0.575     | 0.605 |

| М   | 0°          | 10°   | °         | 10°   |

| N   | 0.51        | 1.52  | 0.020     | 0.060 |

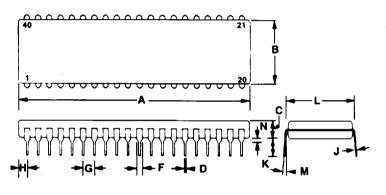

## **40-PIN PLASTIC DIP**

|     | MILLIMETERS |       | INCHES    |       |

|-----|-------------|-------|-----------|-------|

| DIM | MIN         | MAX   | MIN       | MAX   |

| A   | 51.82       | 52.32 | 2.040     | 2.060 |

| В   | 13.46       | 13.97 | 0.530     | 0.550 |

| С   | 3.56        | 5.08  | 0.140     | 0.200 |

| D   | 0.38        | 0.53  | 0.015     | 0.021 |

| F   | 1.02        | 1.52  | 0.040     | 0.060 |

| G   | 2.54 BSC    |       | 0.100 BSC |       |

| н   | 1.65        | 2.16  | 0.065     | 0.085 |

| J   | 0.20        | 0.30  | 0.008     | 0.012 |

| K   | 3.30        | 4.32  | 0.130     | 0.170 |

| L   | 15.24 BSC   |       | 0.600 BSC |       |

| М   | 7°          | 10°   | 7°        | 10°   |

| N   | 0.51        | 1.02  | 0.020     | 0.040 |

CHAM.J × 45

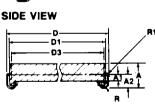

| l   | MILLIMETERS |       | INCHES    |       |  |

|-----|-------------|-------|-----------|-------|--|

| DIM | MIN         | MAX   | MIN       | MAX   |  |

| A   | 4.14        | 4.39  | 0.163     | 0.173 |  |

| A1  | 1.37        | 1.47  | 0.054     | 0.058 |  |

| A2  | 2.31        | 2.46  | 0.091     | 0.097 |  |

| Ð   | 0.457 TYP   |       | 0.018 TYP |       |  |

| D   | 17.45       | 17.60 | 0.687     | 0.693 |  |

| D1  | 16.46       | 16.56 | 0.648     | 0.652 |  |

| D2  | 12.62       | 12.78 | 0.497     | 0.503 |  |

| D3  | 15.75 REF   |       | 0.620 REF |       |  |

| e   | 1.27 BSC    |       | 0.050 BSC |       |  |

| h.  | 1.15 TYP    |       | 0.045 TYP |       |  |

| J   | 0.25 TYP    |       | 0.010 TYP |       |  |

| α   | 45° TYP     |       | 45° TYP   |       |  |

| R   | 0.89 TYP    |       | 0.035 TYP |       |  |

| R1  | 0.25 TYP    |       | 0.010 TYP |       |  |

SECTION A-A

TYP FOR BOTH AXIS (EXCEPT FOR BEVELED EDGE)

CHAM. 11 PINS E

h × 45° PER SIDE

3 PLCS EQUALLY

SPACES

BOTTOM VIEW

28

EJECTOR PIN MARKS 4 PLCS BOTTOM OF PACKAGE ONLY (TYPICAL) Information furnished by Rockwell International Corporation is believed to be accurate and reliable. However, no responsibility is assumed by Rockwell International for its use, nor any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent rights of Rockwell International other than for circuitry embodied in Rockwell products. Rockwell International reserves the right to change circuitry at any time without notice. This document subject to change without notice.

#### DIGITAL COMMUNICATIONS DIVISION **REGIONAL SALES OFFICES**

Headquarters Digital Communications Division Rockwell International

4311 Jamboree Road Newport Beach, CA 92660-3095

(Mailing Address) P.O. Box C Newport Beach, CA 92658-8902

**United States** Digital Communications Division Rockwell International 4311 Jamboree Road Suite 501-301 Newport Beach, CA 92660-3095 (714) 833-4655 FAX: (714) 833-6898

Digital Communications Division Rockwell International 2525 Meridian Parkway Suite 270 Durham, NC 27713 (919) 544-0087 FAX: (919) 544-1009

Digital Communications Division Rockwell International 9700 Koger Blvd. Suite 202 St. Petersburg, FL 33702 (813) 577-4750 FAX: (813) 577-1495

Digital Communications Division Rockwell International 2001 N. Collins Blvd. Suite 103 Richardson, TX 75080 (214) 996-6500 FAX: (214) 996-7812 TWX or TLW: (650) 227-9516

Digital Communications Division Rockwell International 5001-B Greentree **Executive Campus** Route 73 Mariton, NJ 08053 (609) 596-0090 FAX: (609) 596-5681

U.S./E. Canada Digital Communications Division Rockwell International 239 Littleton Road Suite 1B Westford, MA 01886 (508) 692-7660 FAX: (508) 692-8185 TLX (MCI) 6502512464

U.S./W. Canada Digital Communications Division Rockwell International 3600 Pruneridge Avenue Suite 100 Santa Clara, CA 95051 (408) 249-9696 FAX: (408) 249-6518

Digital Communications Division Rockwell International Japan Co., Ltd. Hockwell International Japan Co., Li Sogo Hanzomon Bldg., 8F 7, Kojimachi 1-chome, Chiyoda-ku Tokyo, Japan 102 (011-81-3) 3-265-8808 FAX: (011-81-3) 3-263-0638 TLX: J22198

Australia

Digital Communications Division

Rockwell International 30-332 Rutland Road Box Hill, Victoria 3128 Australia (61-3) 890-6999 FAX: (61-3) 898-6427 TLX: AA30450

Digital Communications Division Rockwell International Rm. 608 Leema Bldg. 146-1 Soosong-Dong Chongro-Ku K.P.O. Box 527 Seoul, Korea (Dept. 553) (82-2) 720-7157 FAX: (82-2) 736-9124 TLX: RCIIK22710

Taiwan

Digital Communications Division Rockwell International Room 2808 International Trade Building 333 Keelung Road, Section 1 Taipei, Taiwan 10548, R.O.C. (886-2) 720-0282 FAX: (886-2) 757-6760 TLX: 26049 ENTTPE

Germany Digital Communications Division Rockwell International GmbH Fraunhoferstrasse 11b D-8033 Muenchen-Martinsried West Germany (49-89) 857-6016 FAX: (49-89) 857 57 93 TLX: 521-2650 rimd d

United Kingdom Digital Communications Division Rockwell International Ltd. Central House 3, Lampton Road Hounslow, Middlesex TW3 1HY England (44-81) 577-1034 FAX: (44-81) 570-0758

France Digital Communications Division Rockwell International Tour GAN, 16 Place de l'Iris Cedex 13 92082 Paris La Defense 2, France (33-1) 49-06-39-80 FAX: (33-1) 49-06-39-90