2097152-BIT(262144-WORD BY 8-BIT)

CMOS ONE TIME PROGRAMMABLE ROM

### **DESCRIPTION**

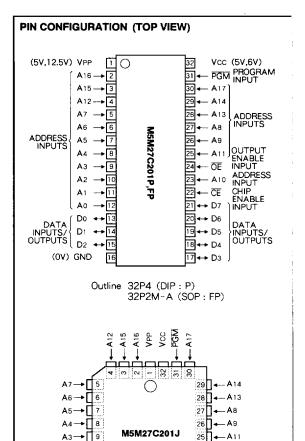

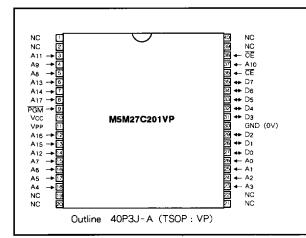

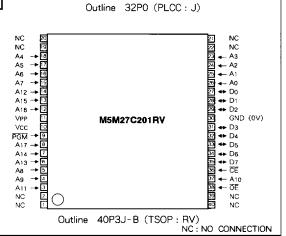

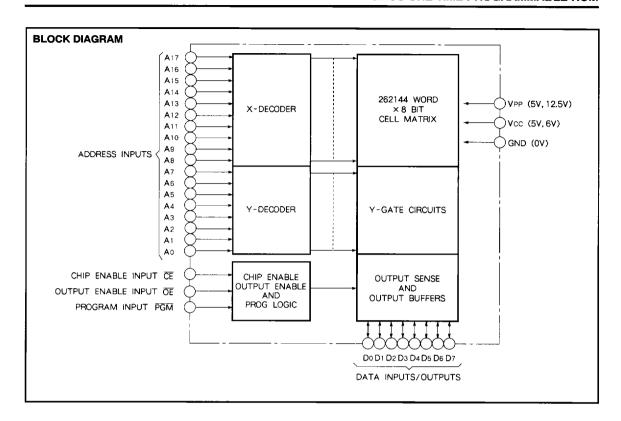

The Mitsubishi M5M27C201P,FP,J,VP,RV are high-speed 2097152-bit one time programmable read only memories. They are suitable for microprocessor programming applications where rapid turn-around is required. The M5M27C201P, FP, J, VP, RV are fabricated by N-channel double polysilicon gate for Memory and CMOS technology for peripheral circuits, and are available in 32 pin plastic packages (DIP, SOP, PLCC) and 40 pin plastic packages (TSOP).

### **FEATURES**

- 262114 word × 8 bit organization

- Two line control OE, CE

- Low power current (Icc): Active ......30mA (max.) (IsB2): Stand-by.....0.1mA (max.)

- Single 5V power supply (read operation)

- 3 State output buffer

- Input and output TTL-compatible in read and program mode

- Standard 32 pin DIP, PLCC, Pin-compatible with 2Mbit EPROM

- Byte programming algorithm

- Page programming algorithm

### APPLICATION

Microcomputer systems and peripheral equipment

A0 → 12

24 **→** OE

23 **→** A10

22 ] ← CE 21 ] ← D7

2097152-BIT(262144-WORD BY 8-BIT)

CMOS ONE TIME PROGRAMMABLE ROM

## M5M27C201P.FP.J.VP.RV-12.-15

2097152-BIT(262144-WORD BY 8-BIT)

CMOS ONE TIME PROGRAMMABLE ROM

### **FUNCTION**

#### Read

Set the  $\overline{CE}$  and  $\overline{OE}$  terminals to the read mode (low level). Low level input to  $\overline{CE}$  and  $\overline{OE}$  and address signals to the address inputs (A0~A17) make the data contents of the designated address location available at the data input/output (D0~D7). When the  $\overline{CE}$  or  $\overline{OE}$  signal is high, data input/output are in a floating state.

When the CE signal is high, the device is in the stand by mode or power-down mode.

### **Programming**

### (Byte programming algorithm)

The M5M27C201P, FP, J, VP, RV enter the byte programming mode when 12.5V is supplied to the VPP power supply input,  $\overline{\text{CE}}$  is at low level and  $\overline{\text{OE}}$  is at high level. A location is designated by address signals (A0~A17), and the data to be programmed must be applied at 8-bits in parallel to the data inputs (D0~D7). In this state, byte programming is completed when  $\overline{\text{PGM}}$  is at low level.

### (Page programming algorithm)

Page programming feature of the M5M27C201P, FP, J, VP, RV allows 4 bytes of data to be simultaneously programmed. The destination addresses for a page programming operation must reside on the same page; that is, A2 through A17 must not change. At first, the M5M27C201P, FP, J, VP,RV enter the page data latch mode when VPP = 12.5V,  $\overline{\text{CE}}$  = "H",  $\overline{\text{OE}}$  = "L"and  $\overline{\text{PGM}}$  = "H". The four locations in same page are designated by address signals (A0, A1 change) and the data to be programmed must be applied to each location at 8-bits in parallel to the data inputs (D0~D7). In this state, the data (4-bytes) latch is completed. Then the M5M27C201P, FP, J, VP, RV enter the page programming mode when  $\overline{\text{OE}}$  = "H". In this state, page (4-bytes) programming is completed when  $\overline{\text{PGM}}$  = "L".

#### Erase

The M5M27C201P, FP, J, VP, RV cannot be erased, because they are packaged in plastic without transparent lid.

### MODE SELECTION

| Pins                     | Œ   | ŌĒ  | PGM | Vpp   | Vcc | Data I/O |

|--------------------------|-----|-----|-----|-------|-----|----------|

| Read                     | VIL | VIL | X*  | 5∨    | 5V  | Data out |

| Output disable           | VIL | ViH | Χ*  | 5∨    | 5V  | Floating |

| Stand-by<br>(Power down) | ViH | ×*  | X*  | 5∨    | 5V  | Floating |

| Byte program             | VIL | ViH | VIL | 12.5V | 6V  | Data in  |

| Program verify           | VIL | VIL | Vін | 12.5V | 6V  | Data out |

| Page data latch          | ViH | VIL | VIH | 12.5V | 67  | Data in  |

| Page program             | ViH | Vih | VIL | 12.5V | 6V  | Floating |

|                          | VIL | VIL | VIL | 12.5V | 6V  |          |

| December inhihit         | VIL | ViH | Viн | 12.5V | 6V  | Floating |

| Program inhibit          | ViH | VIL | VIL | 12.5V | 6V  | ricating |

|                          | VIH | Vih | Vін | 12.5V | 6V  |          |

<sup>\* :</sup> X can be either VIL or VIH

### ABSOLUTE MAXIMUM RATINGS (Note 1)

| Symbol          | Parameter                                   | Conditions             | Ratings    | Unit |

|-----------------|---------------------------------------------|------------------------|------------|------|

| Vii             | All input or output voltage except VPP · As |                        | - 0.6~7    | ٧    |

| V <sub>12</sub> | VPP supply voltage                          | With respect to Ground | - 0.6~14.0 | ٧    |

| Vıз             | As supply voltage                           |                        | - 0.6~13.5 | V    |

| Topr            | Operating temperature                       |                        | - 10~80    | ℃    |

| Tsto            | Storage temperature                         |                        | - 65~150   | ~    |

Note 1: Stresses above those listed may cause parmanent damage to the device. This is a stress rating only and functional operation of the device at those or at any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods affects device reliability.

2097152-BIT(262144-WORD BY 8-BIT)

CMOS ONE TIME PROGRAMMABLE ROM

### **READ OPERATION**

DC ELECTRICAL CHARACTERISTICS (Ta = 0~70 ℃, Vcc = 5V ± 10 %, Vpp = Vcc, unless otherwise noted)

| Symbol            | Parameter                 | Test conditions                               |       | Limits |         | 11.5 |  |

|-------------------|---------------------------|-----------------------------------------------|-------|--------|---------|------|--|

| Symbol            | Farameter                 | rest conditions                               | Min   | Тур    | Max     | Unit |  |

| Li                | Input leakage current     | VIN = 0~VCC                                   |       |        | 10      | μА   |  |

| lro               | Output leakage current    | Vout = 0∼Vcc                                  |       |        | 10      | μА   |  |

| lpp1              | VPP current read/stand-by | VPP = Vcc = 5.5V                              |       | 1      | 100     | μА   |  |

| Is <sub>B</sub> 1 | Vcc current stand-by      | CE = ViH                                      |       |        | 1       | mA   |  |

| IsB2              | vcc current stand-by      | CE = Vcc                                      |       | 1      | 100     | μА   |  |

| lcc1              | Vcc current active        | CE = OE = VIL, DC, lout = 0mA                 |       |        | 30      | mA   |  |

| lcc2              | vec current active        | $\overline{CE}$ = Vie, f = 8.3MHz, lout = 0mA |       |        | 30      | mA   |  |

| VIL               | Input low voltage         |                                               | - 0.1 |        | 0.8     |      |  |

| Vін               | Input high voltage        |                                               | 2.2   |        | Vcc + 1 | ٧    |  |

| Vol               | Output low voltage        | lo <sub>L</sub> = 2.1mA                       |       |        | 0.45    | ٧    |  |

| Voн               | Output high voltage       | Ioн = - 400 μ A                               | 2.4   | •      |         | ٧    |  |

Note 2: Typical values are at Ta = 25 °C and normal supply voltages

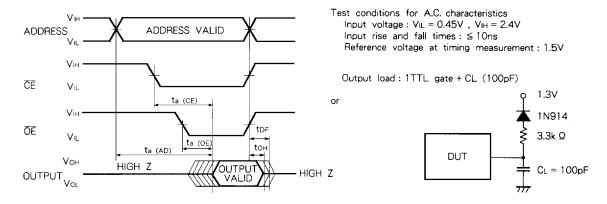

## AC ELECTRICAL CHARACTERISTICS (Ta = $0 \sim 70 \, \text{°C}$ , $V_{CC} = 5V \pm 10 \, \text{%}$ , $V_{PP} = V_{CC}$ , unless otherwise noted)

|         |                                    |                      |        | Limits  |        |      |    |  |  |

|---------|------------------------------------|----------------------|--------|---------|--------|------|----|--|--|

| Symbol  | Parameter                          | Test conditions      | M5M27C | 201P-12 | M5M27C | Unit |    |  |  |

|         |                                    |                      | Min    | Max     | Min    | Max  |    |  |  |

| ta (AD) | Address to output delay            | CE = OE = VIL        |        | 120     |        | 150  | ns |  |  |

| ta (CE) | CE to output delay                 | OE = V <sub>1L</sub> |        | 120     |        | 150  | ns |  |  |

| ta (OE) | Output enable to output delay      | CE = VIL             |        | 60      |        | 60   | ns |  |  |

| tDF     | Output enable high to output float | ČE = VIL             | 0      | 50      | 0      | 50   | ns |  |  |

| tон     | Output hold from CE, OE or address |                      | 0      |         | 0      |      | ns |  |  |

Note 3:VCC must be applied simultaneously VPP and removed simultaneously VPP.

### **AC WAVEFORMS**

### **CAPACITANCE**

| Symbol | Parameter                                | Test conditions                   |     | l lada |     |      |

|--------|------------------------------------------|-----------------------------------|-----|--------|-----|------|

|        |                                          |                                   | Min | Тур    | Max | Unit |

| Cin    | Input capacitance (Address, CE, OE, PGM) | Ta = 25°C, f = 1MHz,V₁ = Vo = 0V  |     |        | 15  | pF   |

| Соит   | Output capacitance                       | 1a - 25 C, 1 - 110Hz, 1 - 10 - 00 |     |        | 15  | pF   |

2097152-BIT(262144-WORD BY 8-BIT)

CMOS ONE TIME PROGRAMMABLE ROM

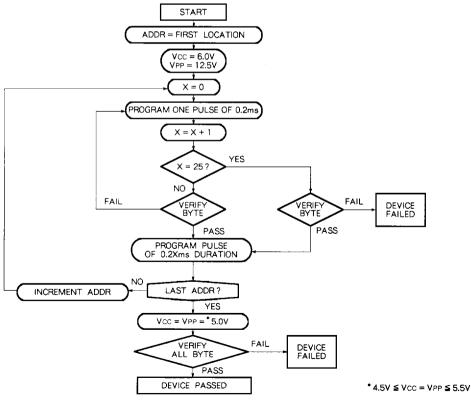

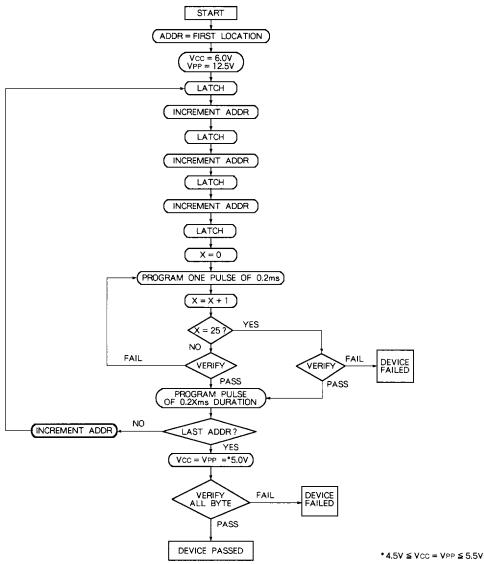

# PROGRAM OPERATION BYTE PROGRAMMING ALGORITHM

First set Vcc = 6V, Vpp = 12.5V and then set an address to first address to be programmed. After applying 0.2ms program pulse ( $\overline{PGM}$ ) to the address, verify is performed. If the output data of that address is not verified correctly, apply one more 0.2ms program pulse. The programmer continues 0.2ms pulse-then-verify routines until the device verify correctly or twenty five of these pulse-then-verify routines have been completed. The programmer also maintains its total

number of 0.2ms pulse applied to that address in register X. And then applied a program pulse X times of 0.2ms width as an overprogram pulse. When the programming procedure above is finished, step to the next address and repeat this procedure till last address to be programmed. When the entire addresses have been programmed completely, all addresses should be verified with Vcc = VPP = 5V.

### DC ELECTRICAL CHARACTERISTICS (Ta = 25 ± 5 °C, Vcc = 6V ± 0.25V, VPP = 12.5V ± 0.3V, unless otherwise noted)

| Symbol Parameter | Baramatar                    | Test conditions  |       | Limits |      |      |  |

|------------------|------------------------------|------------------|-------|--------|------|------|--|

|                  | Farameter                    | l est conditions | Min   | Тур    | Max  | Unit |  |

| lu               | Input leakage current        | VIN = 0~VCC      |       |        | 10   | μΑ   |  |

| Vol              | Output low voltage (verify)  | lot = 2.1mA      |       |        | 0.45 |      |  |

| Vон              | Output high voltage (verify) | Ioн = - 400 µ A  | 2.4   |        |      | V    |  |

| VIL              | Input low voltage            |                  | - 0.1 |        | 0.8  | V    |  |

| ViH              | Input high voltage           |                  | 2.2   |        | Vcc  | V    |  |

| Icc              | Vcc supply current           |                  |       |        | 30   | mΑ   |  |

| <b>I</b> PP      | VPP supply current           | PGM = VIL        |       |        | 30   | mA   |  |

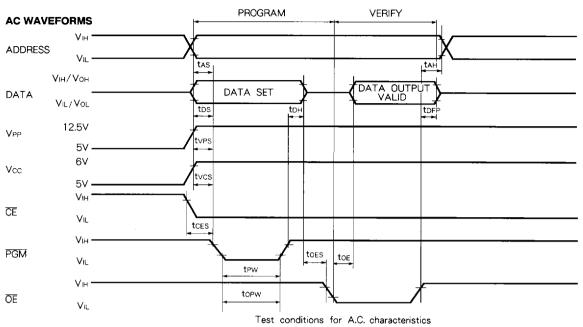

### AC ELECTRICAL CHARACTERISTICS (Ta = 25 ± 5 ℃, Vcc = 6V ± 0.25V, VPP = 12.5V ± 0.3V, unless otherwise noted)

| Symbol | Parameter                         | Test conditions |      | Limits |      |      |  |

|--------|-----------------------------------|-----------------|------|--------|------|------|--|

| Symbol | Farameter                         | Test conditions | Min  | Тур    | Max  | Unit |  |

| tas    | Address setup time                |                 | 2    |        |      | μs   |  |

| toes   | OE setup time                     |                 | 2    |        |      | μs   |  |

| tos    | Data setup time                   |                 | 2    |        |      | μs   |  |

| tah    | Address hold time                 |                 | 0    |        |      | μs   |  |

| tDн    | Data hold time                    |                 | 2    |        |      | μs   |  |

| tDFP   | Chip enable to output float delay |                 | 0    |        | 130  | ns   |  |

| tvcs   | Vcc setup time                    |                 | 2    |        |      | μs   |  |

| tvps   | VPP setup time                    |                 | 2    |        |      | μs   |  |

| tpw    | PGM initial program pulse width   |                 | 0.19 | 0.2    | 0.21 | ms   |  |

| topw   | PGM over program pulse width      |                 | 0.19 | , i    | 5.25 | ms   |  |

| tces   | CE setup time                     |                 | 2    |        |      | μs   |  |

| toE    | Data valid from OE                |                 |      |        | 150  | ns   |  |

Note 4: VCC must be applied simultaneously VPP and removed simultaneously VPP.

2097152-BIT(262144-WORD BY 8-BIT)

CMOS ONE TIME PROGRAMMABLE ROM

Input voltage: VIL = 0.45V, VIH = 2.4VInput rise and fall time:  $(10 \% \sim 90 \%)$ :  $\leq 20$ ns Reference voltage at timing measurement: Input, Output "L" = 0.8V, "H" = 2V

# BYTE PROGRAMMING ALGORITHM FLOW CHART

2097152-BIT(262144-WORD BY 8-BIT)

CMOS ONE TIME PROGRAMMABLE ROM

### **PAGE PROGRAMMING ALGORITHM**

First set Vcc = 6V, Vpp = 12.5V and then set an address to first page address to be programmed. After data of 4 bytes are latched, these latch data are programmed simultaneously by applying 0.2ms program pulse. Then a verify is performed. If each output data is not verified correctly, apply one more 0.2ms program pulse. The programmer continues 0.2ms pulse - then - verify routines until each output data is verified correctly or twenty five of these pulse-then-verify routines have been completed. The programmer also maintains its total

number of 0.2ms pulse applied to that page addresses in register X. And then applied a program pulse X times of 0.2 ms width as an overprogram pulse. When the programming procedure above is finished, step to the next page address and repeat this procedure till last page address to be programmed. When the entire page addresses have been programmed completely, all addresses should be verified with  $V_{CC} = V_{PP} = 5V$ .

# PAGE PROGRAMMING ALGORITHM FLOW CHART

2097152-BIT(262144-WORD BY 8-BIT) CMOS ONE TIME PROGRAMMABLE ROM

### DC ELECTRICAL CHARACTERISTICS (Ta = $25 \pm 5 \, ^{\circ}$ C, Vcc = $6V \pm 0.25V$ , Vpp = $12.5V \pm 0.3V$ , unless otherwise noted)

| Symbol | Parameter                    | Test conditions |       | Limits |      |      |  |

|--------|------------------------------|-----------------|-------|--------|------|------|--|

| Symbol | i arameter                   | Test conditions | Min   | Тур    | Max  | Unit |  |

| lLi    | Input leakage current        | VIN = OV~VCC    |       |        | 10   | μА   |  |

| VoL    | Output low voltage (verify)  | loL = 2.1mA     | _     |        | 0.45 | ٧    |  |

| Voн    | Output high voltage (verify) | lон = − 400 µ A | 2.4   |        |      | V    |  |

| VIL    | Input low voltage            |                 | - 0.1 |        | 0.8  | V    |  |

| ViH    | Input high voltage           |                 | 2.2   |        | Vcc  | V    |  |

| lcc    | Vcc supply current           |                 |       |        | 30   | mA   |  |

| lpp    | VPP supply current           | PGM = VIL       |       |        | 100  | mA   |  |

### AC ELECTRICAL CHARACTERISTICS (Ta = 25 ± 5 °C, Vcc = 6V ± 0.25V, Vpp = 12.5V ± 0.3V, unless otherwise noted)

| symbol | Parameter                       | Tank and distance |      | Limits |      |      |  |

|--------|---------------------------------|-------------------|------|--------|------|------|--|

| symbol | r arameter                      | Test conditions   | Min  | Тур    | Max  | Unit |  |

| tas    | Address setup time              |                   | 2    |        |      | μs   |  |

| toes   | OE setup time                   |                   | 2    |        |      | μs   |  |

| tos    | Data setup time                 |                   | 2    |        | · ·  | μs   |  |

| tah    | Address hold time               |                   | 0    |        |      | μs   |  |

| tahl   | Address floid time              |                   | 2    |        |      | μs   |  |

| tрн    | Data hold time                  |                   | 2    |        |      | μs   |  |

| tDFP   | OE to output float delay        |                   | 0    |        | 130  | ns   |  |

| tvcs   | Vcc setup time                  |                   | 2    |        |      | μs   |  |

| t∨PS   | VPP setup time                  |                   | 2    |        |      | μs   |  |

| tpw    | PGM initial program pulse width |                   | 0.19 | 0.2    | 0.21 | ms   |  |

| topw   | PGM over program pulse width    |                   | 0.19 |        | 5.25 | ms   |  |

| tces   | CE setup time                   |                   | 2    | •      |      | μs   |  |

| toe    | Data valid from OE              |                   |      |        | 150  | ns   |  |

| tLW    | Data latch time                 |                   | . 1  |        |      | μs   |  |

| tpgms  | PGM setup time                  |                   | 2    |        |      | μs   |  |

| tceh   | CE hold time                    |                   | 2    |        |      | μs   |  |

| toen   | OE hold time                    |                   | 2    |        |      | μs   |  |

Note 5: VCC must be applied simultaneously Vpp and removed simultaneously VPP.

### **AC WAVEFORMS**

Input rise and fall tame : (10% $\sim$ 90%) :  $\leq$  20ns Reference voltage at timing measurement : Input, Output "L" = 0.8V, "H" = 2V

2097152-BIT(262144-WORD BY 8-BIT) CMOS ONE TIME PROGRAMMABLE ROM

### **DEVICE IDENTIFIER MODE**

The Device Identifier Mode allows the reading of a binary code from the OTP ROM that identifies the manufacturer and device type

The PROM Programmer reads the manufacturer code and the device code and automatically selects the corresponding programming algorithm.

### M5M27C201P, FP, J, VP, RV DEVICE IDENTIFIER CODE

| Code              | Ao  | D7 | D6 | D <sub>5</sub> | D4 | Dз | D2 | D1 | Do | Hex<br>Data |

|-------------------|-----|----|----|----------------|----|----|----|----|----|-------------|

| Manufacturer code | VIL | 0  | 0  | 0              | 1  | 1  | 1  | 0  | 0  | 1C          |

| Device code       | ViH | 1  | 0  | 0              | 0  | 1  | 0  | 1  | 0  | 8A          |

Note  $6: A9 = 12.0 \pm 0.5V$

A1~A8, A10~A17,  $\overline{CE}$ ,  $\overline{OE}$  = VIL,  $\overline{PGM}$  = VIH VCC = VPP = 5V ± 10%.

### RECOMMENDED SCREENING CONDITION

The following screening test is recommended before using.