Fast CMOS 16-Bit Registered/Latched Transceivers with Parity

December 1996

### Features

- These Devices are High-speed, Low Power Devices with High Current Drive

- V<sub>CC</sub> = 5V ±10%

- · Hysteresis on All Inputs

- · CD74FCT16511T

- High Output Drive: I<sub>OH</sub> = -32mA; I<sub>OL</sub> = 64mA

- Power Off Disable Outputs Permit "Live Insertion"

- Typical  $V_{OLP}$  (Output Ground Bounce) < 1.0V at  $V_{CC} = 5V$ ,  $T_A = 25^{\circ}C$

- · CD74FCT162511T

- Balanced Output Drivers: ±24mA

- Open Drain Parity Error Allows Wire-OR

- Typical V<sub>OLP</sub> (Output Ground Bounce) < 1.0V at  $V_{CC} = 5V$ ,  $T_A = 25^{\circ}C$

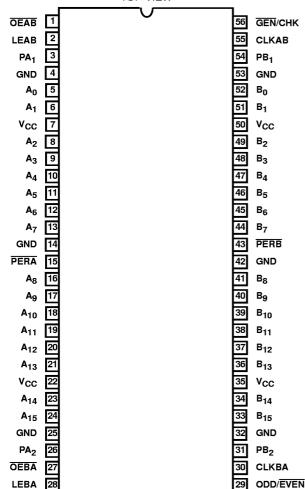

#### **Pinout**

CD74FCT16511T, CD74FCT162511T (SSOP, TSSOP)

TOP VIEW

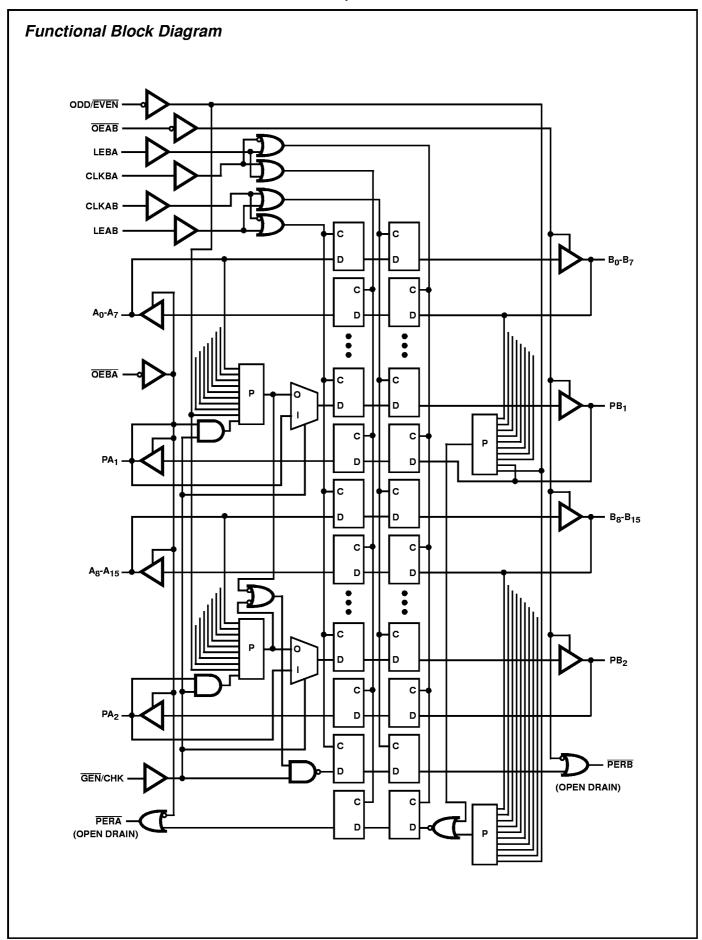

## Description

Harris' CD74FCT16511T and CD74FCT162511T are produced in an advanced 0.8 micron CMOS technology, achieving industry leading speed grades.

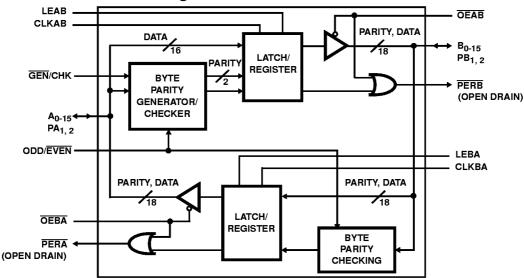

The CD74FCT16511T and CD74FCT162511T are high-speed, low-power 16-bit registered/latched transceiver with parity which combines D-type latches and D-type flip-flops to allow data flow in transparent, latched or clocked modes. It has a parity generator/checker in the A-to-B direction and a parity checker in the B-to-A direction. Error checking is done at the byte level with separate parity bits for each byte. One error flag for each direction (A-to-B or B-to-A) exists to indicate an error for either byte in either direction. The parity error flags which are open drain outputs, can be tied together and/or tied with flags from other devices to form a single error flag or interrupt. To disable the error flag during combinational transitions, a designer can disable the parity error flag by the  $\overline{OEXX}$  control pins.

The operation in A-to-B direction is controlled by LEAB, CLKAB and OEAB control pins, and the operation in B-to-A direction is controlled by LEBA, CLKBA and OEBA control pins. GEN/CHK is used to select the operation of A-to-B direction, while B-to-A direction is always in checking mode. The ODD/EVEN select is common between the two directions. Independent operation can be achieved between the two directions by using the corresponding control lines except for the ODD/EVEN control.

# Ordering Information

| PART NUMBER       | TEMP.<br>RANGE<br>(°C) | PACKAGE     | PKG.<br>NO. |

|-------------------|------------------------|-------------|-------------|

| CD74FCT16511ATSM  | -40 to 85              | 56 Ld SSOP  | M56.300-P   |

| CD74FCT16511TSM   | -40 to 85              | 56 Ld SSOP  | M56.300-P   |

| CD74FCT162511ATMT | -40 to 85              | 56 Ld TSSOP | M56.240-P   |

| CD74FCT162511ATSM | -40 to 85              | 56 Ld SSOP  | M56.300-P   |

| CD74FCT162511TMT  | -40 to 85              | 56 Ld TSSOP | M56.240-P   |

| CD74FCT162511TSM  | -40 to 85              | 56 Ld SSOP  | M56.300-P   |

NOTE: When ordering, use the entire part number. Add the suffix 96 to obtain the varient in the tape and reel.

# Simplified Functional Block Diagram

#### TRUTH TABLE (NOTES 1, 2)

|      | INP  | итѕ   |    | OUTPUT<br>BUFFERS |

|------|------|-------|----|-------------------|

| OEAB | LEAB | CLKAB | Вχ |                   |

| Н    | Х    | Х     | Х  | Z                 |

| L    | Н    | Х     | L  | L                 |

| L    | Н    | Х     | Н  | Н                 |

| L    | L    | 1     | L  | L                 |

| L    | L    | 1     | Н  | Н                 |

| Ĺ    | L    | L     | Х  | B (Note 3)        |

| L    | L    | Н     | Х  | B (Note 4)        |

## NOTES:

- 1. H = High Voltage Level

- L = Low Voltage Level

- X = Don't Care or Irrelevant

- Z = High Impedance

- ↑ = LOW-to-HIGH Transition

- A-to-B data flow is shown. B-to-A flow control is the same, except using OEBA, LEBA, and CLKBA.

- Output level before the indicated steady-state input conditions were established.

- Output level before the indicated steady-state input conditions were established, assuming CLKAB was HIGH before LEAB went LOW.

#### TRUTH TABLE (PARITY GENERATION) (NOTES 5, 6, 7, 8, 9)

| TOTAL NUMBER OF INPUTS THAT ARE HIGH, A <sub>0</sub> - A <sub>7</sub> | ODD/EVEN | PB <sub>1</sub> |

|-----------------------------------------------------------------------|----------|-----------------|

| 1, 3, 5 or 7                                                          | L        | Н               |

| 1, 3, 5 or 7                                                          | Н        | L               |

| 0, 2, 4, 6 or 8                                                       | L        | L               |

| 0, 2, 4, 6 or 8                                                       | Н        | Н               |

#### NOTES:

- 5. Conditions shown are for  $\overline{GEN}/CHK = L$ ,  $\overline{OEAB} = L$ ,  $\overline{OEBA} = H$ .

- A-to-B parity generation is shown. B-to-A can check parity while A-to-B is performing generation. B-to-A will not generate parity.

- 7. The response shown is for LEAB = H. If LEAB = L, then CLKAB will control as an edge triggered clock.

- 8. Conditions shown are for the byte A0-A7. The byte A8-A15 is similar but will output the parity on PB2.

- 9. The error flag PERB will remain in a high state during parity generation

#### TRUTH TABLE (PARITY CHECKING) (NOTES 10, 11, 12, 13)

| TOTAL NUMBER OF INPUTS THAT ARE HIGH, A <sub>0</sub> - A <sub>7</sub> AND PA <sub>1</sub> (NOTE 14) | ODD/<br>EVEN | PB <sub>1</sub> |

|-----------------------------------------------------------------------------------------------------|--------------|-----------------|

| 1, 3, 5, 7 or 9                                                                                     | L            | L               |

| 1, 3, 5, 7 or 9                                                                                     | Н            | H (Note 15)     |

| 0, 2, 4, 6 or 8                                                                                     | L            | H (Note 15)     |

| 0, 2, 4, 6 or 8                                                                                     | Η            | L               |

- 10. Conditions shown are for  $\overline{GEN}/CHK = H$ ,  $\overline{OEAB} = L$ ,  $\overline{OEBA} = H$ .

- A-to-B parity checking is shown. B-to-A parity checking is same but uses OEBA = L, OEAB = H and errors will be indicated on PERA.

- In parity checking mode the parity bits will be transmitted unchanged along with the corresponding data regardless of parity errors. (PB<sub>1</sub> = PA<sub>1</sub>)

- 13. The response shown is for LEAB = H. If LEAB = L, then CLK-AB will control as an edge triggered clock.

- 14. Conditions shown are for the byte  $\rm A_0\text{-}A_7$  and  $\rm PA_1$ . The byte  $\rm A_8\text{-}A_{15}$  and  $\rm PA_2$  is same.

- 15. The parity error flag  $\overline{PERB}$  is a combined flag for both bytes  $A_0$   $A_7$  and  $A_8$ - $A_{15}$ . If a parity error occurs on either byte  $\overline{PERB}$  will go low.

# Pin Descriptions

| PIN NAME                  | DESCRIPTION                                      |

|---------------------------|--------------------------------------------------|

| OEAB                      | A-to-B Output Enable Input (Active LOW)          |

| OEBA                      | B-to-A Output Enable Input (Active LOW)          |

| CLKAB                     | A-to-B Clock Input                               |

| CLKBA                     | B-to-A Clock Input                               |

| LEAB                      | A-to-B Latch Enable Input                        |

| LEBA                      | B-to-A Latch Enable Input                        |

| PERA                      | Parity Error (Open Drain) on A Outputs           |

| PERB                      | Parity Error (Open Drain) on B Outputs           |

| A <sub>X</sub>            | A-to-B Data Inputs or B-to-A Three State Outputs |

| ВХ                        | B-to-A Data Inputs or B-to-A Three State Outputs |

| ODD/EVEN<br>(Note 16)     | Parity Mode Selection Input                      |

| GEN/CHK<br>(Note 16)      | A-to-B Port Generate or Check Mode Input         |

| PA <sub>X</sub> (Note 17) | A-to-B Parity Input, B-to-A Parity Output        |

| PBX                       | B-to-A Parity Input, A-to-B Parity Output        |

| GND                       | Ground                                           |

| V <sub>CC</sub>           | Power                                            |

#### NOTES:

- 16. ODD/ $\overline{\text{EVEN}}$  and  $\overline{\text{GEN}}/\text{CHK}$  should be tied to  $V_{CC}$  or GND with no resistor for optimum results.

- 17. The  $PA_X$  pin input is internally disabled during parity generation. This means that when generating parity in the A-to-B direction, there is no need to add a pull-up resistor to guarantee state. The pin will still function properly as the parity output for the B-to-A direction.

#### **Absolute Maximum Ratings Thermal Information** $\theta_{JA}$ (°C/W) DC Input Voltage .....-0.5V to 7.0V Thermal Resistance (Typical, Note 18) TSSOP Package ..... 85 **Operating Conditions** Operating Temperature Range . . . . . . . . -40°C to 85°C Maximum Storage Temperature Range $\,\ldots\,$ -65°C to 150°C Supply Voltage to Ground Potential Maximum Lead Temperature (Soldering 10s).....300°C Inputs and V<sub>CC</sub> Only.....-0.5V to 7.0V (Lead Tips Only) Supply Voltage to Ground Potential Outputs and D/O Only.....-0.5V to 7.0V

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

18.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

## **Electrical Specifications**

| PARAMETER                              | SYMBOL           | (NOTE 19)                                                | ONS                               | MIN                                   | (NOTE 20)                 | MAX    | UNITS |

|----------------------------------------|------------------|----------------------------------------------------------|-----------------------------------|---------------------------------------|---------------------------|--------|-------|

| DC ELECTRICAL SPE                      | CIFICATIO        | <b>IS</b> Over the Operating Range, T <sub>A</sub>       | = -40°C to 85°C, V <sub>C</sub>   | C = 5.0V ±10                          | 0%                        |        | ı     |

| Input HIGH Voltage                     | V <sub>IH</sub>  | Guaranteed Logic HIGH Level                              |                                   | 2.0                                   | -                         | -      | V     |

| Input LOW Voltage                      | V <sub>IL</sub>  | Guaranteed Logic LOW Level                               |                                   | -                                     | -                         | 0.8    | V     |

| Input HIGH Current<br>(Input Pins)     | lн               | V <sub>CC</sub> = Max                                    | V <sub>IN</sub> = Vcc             | -                                     | -                         | 1      | μΑ    |

| Input HIGH Current<br>(I/O Pins)       | lн               | V <sub>CC</sub> = Max                                    | V <sub>IN</sub> = Vcc             | -                                     | -                         | -1     | μΑ    |

| Input LOW Current<br>(Input Pins)      | I <sub>IL</sub>  | V <sub>CC</sub> = Max                                    | V <sub>IN</sub> = GND             | -                                     | -                         | 1      | μΑ    |

| Input LOW Current<br>(I/O Pins)        | I <sub>IL</sub>  | V <sub>CC</sub> = Max                                    | V <sub>IN</sub> = GND             | -                                     | -                         | -1     | μА    |

| High Impedance                         | lozh             | V <sub>CC</sub> = Max                                    | V <sub>OUT</sub> = 2.7V           | -                                     | -                         | 1      | μА    |

| Output Current                         | lozL             | V <sub>CC</sub> = Max                                    | V <sub>OUT</sub> = 0.5V           | -                                     | -                         | -1     | μА    |

| Clamp Diode Voltage                    | V <sub>IK</sub>  | V <sub>CC</sub> = Min, I <sub>IN</sub> = -18mA           |                                   | -                                     | -0.7                      | -1.2   | V     |

| Short Circuit Current (I/O Pins)       | los              | V <sub>CC</sub> = Max (Note 21), V <sub>OUT</sub> = G    | GND                               | -80                                   | -140                      | -225   | mA    |

| Output Drive Current<br>(I/O Pins)     | lo               | V <sub>CC</sub> = Max (Note 21), V <sub>OUT</sub> = 2    | 5V                                | -50                                   | -                         | -180   | mA    |

| Output Leakage<br>Current (Open Drain) | l <sub>OFF</sub> | $V_{CC} = Max, V_{OUT} = 4.5V$                           |                                   | -                                     | -                         | ±100   | μΑ    |

| Input Hysteresis                       | V <sub>H</sub>   |                                                          |                                   | -                                     | 100                       | -      | mV    |

| CD74FCT16511T OUT                      | PUT DRIVE        | SPECIFICATIONS Over the Ope                              | rating Range, T <sub>A</sub> = -4 | 0°C to 85°C                           | C, V <sub>CC</sub> = 5.0V | ±10%   | •     |

| Output HIGH Voltage                    | V <sub>OH</sub>  | $V_{CC}$ = Min, $V_{IN}$ = $V_{IH}$ or $V_{IL}$          | I <sub>OH</sub> = -3.0mA          | 2.5                                   | 3.5                       | -      | V     |

|                                        |                  |                                                          | I <sub>OH</sub> = -15.0mA         | 2.4                                   | 3.5                       | -      | V     |

|                                        |                  |                                                          | I <sub>OH</sub> = -32.0mA         | 2.0                                   | 3.0                       | -      | V     |

| Output LOW Voltage                     | V <sub>OL</sub>  | $V_{CC}$ = Min, $V_{IN}$ = $V_{IH}$ or $V_{IL}$          | I <sub>OL</sub> = 64mA            | -                                     | 0.2                       | 0.55   | V     |

| Power Down Disable                     | loff             | $V_{CC} = 0V$ , $V_{IN}$ or $V_{OUT} \le 4.5V$           |                                   | -                                     | -                         | ±100   | μΑ    |

| CD74FCT162511T OU                      | TPUT DRIV        | E SPECIFICATIONS Over the Op                             | erating Range, T <sub>A</sub> = - | -40 <sup>o</sup> C to 85 <sup>c</sup> | $^{0}C$ , $V_{CC} = 5.0$  | V ±10% |       |

| Output HIGH Voltage                    | V <sub>OH</sub>  | $V_{CC}$ = Min, $V_{IN}$ = $V_{IH}$ or $V_{IL}$          | I <sub>OH</sub> = -24.0mA         | 2.4                                   | 3.3                       | -      | V     |

| Output LOW Voltage                     | V <sub>OL</sub>  | $V_{CC}$ = Min, $V_{IN}$ = $V_{IH}$ or $V_{IL}$          | I <sub>OL</sub> = 24mA            | -                                     | 0.3                       | 0.55   | ٧     |

| Output LOW Current                     | lodl             | $V_{CC} = 5V$ , $V_{IN} = V_{IH}$ or $V_{IL}$ , $V_{OL}$ | T = 1.5V (Note 21)                | 60                                    | 115                       | 150    | mA    |

| Output HIGH Current                    | lodh             | $V_{CC} = 5V$ , $V_{IN} = V_{IH}$ or $V_{IL}$ , $V_{OL}$ | <sub>T</sub> = 1.5V (Note 21)     | -60                                   | -115                      | -150   | mA    |

# **Electrical Specifications (Continued)**

| PARAMETER                                        | SYMBOL                                                    | (NOTE 19<br><b>TEST CONDIT</b>                                                                    | MIN                                                        | (NOTE 20) | MAX | UNITS             |            |

|--------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------|-----|-------------------|------------|

| CAPACITANCE TA = 2                               | 25 <sup>0</sup> C, f = 1Mł                                | -<br>Iz                                                                                           |                                                            |           |     |                   |            |

| Input Capacitance<br>(Note 22)                   | C <sub>IN</sub>                                           | V <sub>IN</sub> = 0V                                                                              |                                                            | -         | 4.5 | 6.0               | pF         |

| I/O Capacitance<br>(Note 22)                     | C <sub>I/O</sub>                                          | V <sub>OUT</sub> = 0V                                                                             |                                                            | -         | 5.5 | 8.0               | pF         |

| Open Drain<br>Capacitance (Note 22)              | CO                                                        | V <sub>OUT</sub> = 0V                                                                             |                                                            | -         | 4.5 | 6.0               | рF         |

| POWER SUPPLY SPE                                 | CIFICATION                                                | is                                                                                                |                                                            |           |     |                   |            |

| Quiescent Power<br>Supply Current                | I <sub>CCL</sub> ,<br>I <sub>CCH</sub> , I <sub>CCZ</sub> | V <sub>CC</sub> = Max                                                                             | V <sub>IN</sub> = GND<br>or V <sub>CC</sub>                | -         | 0.1 | 500               | μΑ         |

| Supply Current per Input at TTL HIGH             | Δl <sub>CC</sub>                                          | V <sub>CC</sub> = Max                                                                             | V <sub>IN</sub> = 3.4V<br>(Note 23)                        | -         | 0.5 | 1.5               | mA         |

| Supply Current per<br>Input per MHz<br>(Note 24) | ICCD                                                      | V <sub>CC</sub> = Max, Outputs Open  OEAB = GND  OEBA = VCC  One Bit Toggling  50% Duty Cycle     | V <sub>IN</sub> = V <sub>CC</sub><br>V <sub>IN</sub> = GND | -         | 75  | 120               | μΑ/<br>MHz |

| Total Power Supply<br>Current (Note 26)          | lc                                                        | V <sub>CC</sub> = Max, Outputs Open<br>f <sub>CP</sub> = 10MHz (CLKAB)                            | V <sub>IN</sub> = V <sub>CC</sub><br>V <sub>IN</sub> = GND | -         | 0.8 | 1.7<br>(Note 25)  | mA         |

|                                                  |                                                           | 50% Duty Cycle  LEAB = OEAB = GND  OEBA = V <sub>CC</sub> f <sub>I</sub> = 5MHz  One Bit Toggling | V <sub>IN</sub> = 3.4V<br>V <sub>IN</sub> = GND            | -         | 1.3 | 3.2<br>(Note 25)  | mA         |

|                                                  |                                                           | V <sub>CC</sub> = Max, Outputs Open<br>f <sub>CP</sub> = 10MHz (CLKAB)                            | $V_{IN} = V_{CC}$<br>$V_{IN} = GND$                        | -         | 3.8 | 6.5<br>(Note 25)  | mA         |

|                                                  |                                                           | 50% Duty Cycle LEAB = OEAB = GND OEBA = V <sub>CC</sub> f <sub>I</sub> = 2.5MHz 18 Bits Toggling  | V <sub>IN</sub> = 3.4V<br>V <sub>IN</sub> = GND            | -         | 9.0 | 21.8<br>(Note 25) | mA         |

# **Switching Specifications Over Operating Range** (Propagation Delays)

|                                                                       |                                        | (NOTE 27)                         | 7                |      | A.               | Т   |       |

|-----------------------------------------------------------------------|----------------------------------------|-----------------------------------|------------------|------|------------------|-----|-------|

| PARAMETER                                                             | SYMBOL                                 | TEST<br>CONDITIONS                | (NOTE 28)<br>MIN | MAX  | (NOTE 28)<br>MIN | мах | UNITS |

| Propagation Delay $PA_X$ to $PB_X$                                    | t <sub>PLH</sub><br>t <sub>PHL</sub>   | $C_L = 50pF$<br>$R_L = 500\Omega$ | 1.5              | 6.5  | 1.5              | 5.7 | ns    |

| Propagation Delay $A_X$ to $B_X$ or $B_X$ to $A_X$ , $PB_X$ to $PA_X$ | t <sub>PLH</sub><br>t <sub>PHL</sub>   | $C_L = 50pF$<br>$R_L = 500\Omega$ | 1.5              | 6.5  | 1.5              | 5.0 | ns    |

| Propagation Delay $A_X$ to $PB_X$                                     | t <sub>PLH</sub><br>t <sub>PHL</sub>   | $C_L = 50pF$<br>$R_L = 500\Omega$ | 1.5              | 9.0  | 1.5              | 7.5 | ns    |

| Propagation Delay                                                     | t <sub>PLH</sub> C <sub>L</sub> = 50pF |                                   | 1.5              | 10.5 | 1.5              | 9.0 | ns    |

| A <sub>X</sub> to PERB, PA <sub>X</sub> to PERB                       | (Note 29)<br>t <sub>PHL</sub>          | $R_L = 500\Omega$                 | 1.5              | 9.5  | 1.5              | 8.0 | ns    |

| Propagation Delay                                                     | t <sub>PLH</sub>                       | C <sub>L</sub> = 50pF             | 1.5              | 10.5 | 1.5              | 9.0 | ns    |

| B <sub>X</sub> to PERA, PB <sub>X</sub> to PERA                       | (Note 29)<br>t <sub>PHL</sub>          | $R_L = 500\Omega$                 | 1.5              | 9.5  | 1.5              | 8.0 | ns    |

| Propagation Delay LEBA to $A_X$ and $PA_X$ , LEAB to $B_X$ and $PB_X$ | t <sub>PLH</sub><br>t <sub>PHL</sub>   |                                   |                  | 6.0  | 1.5              | 5.6 | ns    |

| Propagation Delay                                                     | t <sub>PLH</sub>                       | C <sub>L</sub> = 50pF             | 1.5              | 7.5  | 1.5              | 7.0 | ns    |

| LEBA to PERA, LEAB to PERB                                            | (Note 29)<br>t <sub>PHL</sub>          | $R_L = 500\Omega$                 | 1.5              | 6.5  | 1.5              | 6.0 | ns    |

# Switching Specifications Over Operating Range (Propagation Delays) (Continued)

|                                                                                                              |                                      | (NOTE 27)                         | 7                | Г    | A                | Т    |       |

|--------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------------------------------|------------------|------|------------------|------|-------|

| PARAMETER                                                                                                    | SYMBOL                               | TEST CONDITIONS                   | (NOTE 28)<br>MIN | MAX  | (NOTE 28)<br>MIN | MAX  | UNITS |

| Propagation Delay CLKBA to $A_X$ and $PA_X$ CLKAB to $B_X$ and $PB_X$                                        | tPLH<br>tPHL                         | $C_L = 50pF$<br>$R_L = 500\Omega$ | 1.5              | 6.0  | 1.5              | 5.6  | ns    |

| Propagation Delay                                                                                            | t <sub>PLH</sub>                     | C <sub>L</sub> = 50pF             | 1.5              | 7.5  | 1.5              | 7.0  | ns    |

| CLKBA to PERA<br>CLKAB to PERB                                                                               | (Note 29)<br>t <sub>PHL</sub>        | $R_L = 500\Omega$                 | 1.5              | 6.5  | 1.5              | 6.0  | ns    |

| Output Enable Time $\overline{\text{OEBA}}$ to $A_X$ and $PA_X$ $\overline{\text{OEAB}}$ to $B_X$ and $PB_X$ | t <sub>PZH</sub><br>t <sub>PZL</sub> | $C_L = 50pF$<br>$R_L = 500\Omega$ | 1.5              | 7.0  | 1.5              | 6.0  | ns    |

| Output Disable Time (Note 30) OEBA to Ax and PAx OEAB to Bx and PBx                                          | t <sub>PHZ</sub><br>t <sub>PLZ</sub> | $C_L = 50pF$<br>$R_L = 500\Omega$ | 1.5              | 7.0  | 1.5              | 5.6  | ns    |

| Parity ERROR Enable                                                                                          | t <sub>PLZ</sub>                     | C <sub>L</sub> = 50pF             | 1.5              | 6.0  | 1.5              | 6.0  | ns    |

| OEBA to PERA, OEAB to PERB                                                                                   | (Note 29)<br>t <sub>PZL</sub>        | $R_L = 500\Omega$                 | 1.5              | 6.0  | 1.5              | 6.0  | ns    |

| ODD/EVEN to PERB                                                                                             | t <sub>PLH</sub>                     | C <sub>L</sub> = 50pF             | 1.5              | 10.0 | 1.5              | 10.0 | ns    |

|                                                                                                              | tPHL                                 | $R_L = 500\Omega$                 | 1.5              | 10.0 | 1.5              | 10.0 | ns    |

| ODD/EVEN to PBX                                                                                              | t <sub>PLH</sub><br>t <sub>PHL</sub> | $C_L = 50pF$<br>$R_L = 500\Omega$ | 1.5              | 10.0 | 1.5              | 10.0 | ns    |

# **Switching Specifications Over Operating Range** (Setup Times)

|                                |                 | ,,           | NOTES 27, 31)             |                       |     | Т   | Α   | λT  |       |

|--------------------------------|-----------------|--------------|---------------------------|-----------------------|-----|-----|-----|-----|-------|

| DESCRIPTION                    | SYMBOL          |              | CONDITIONS                |                       |     | МАХ | MIN | MAX | UNITS |

| Setup Time                     | t <sub>SU</sub> | GEN/CHK LOW  | PB <sub>X</sub> valid     | C <sub>L</sub> = 50pF | 6.5 | -   | 4   | -   | ns    |

| HIGH or LOW $A_X$ to CLKAB     |                 |              | PB <sub>X</sub> not valid | $R_L = 500\Omega$     | 3   | -   | 3   | -   | ns    |

|                                |                 | GEN/CHK HIGH | PERB valid                | C <sub>L</sub> = 50pF | 6.5 | -   | 4   | -   | ns    |

|                                |                 |              | PERB not valid            | $R_L = 500\Omega$     | 3   | -   | 3   | -   | ns    |

| Setup Time                     | t <sub>SU</sub> | GEN/CHK HIGH | PERB valid                | C <sub>L</sub> = 50pF | 6.5 | -   | 4   | -   | ns    |

| PA <sub>X</sub> to CLKAB       |                 |              | PERB not valid            | $R_L = 500\Omega$     | 3   | -   | 3   | -   | ns    |

| Setup Time                     | t <sub>SU</sub> |              | PERA valid                | C <sub>L</sub> = 50pF | 6.5 | -   | 4   | -   | ns    |

| $B_X$ to CLKBA $PB_X$ to CLKBA |                 |              | PERA not valid            | $R_L = 500\Omega$     | 3   | -   | 3   | -   | ns    |

| Setup Time                     | tsu             | CLKAB LOW    | PB <sub>X</sub> valid     | C <sub>L</sub> = 50pF | 6.5 | -   | 3.5 | -   | ns    |

| $A_X$ to LEAB                  |                 | GEN/CHK LOW  | PB <sub>X</sub> not valid | $R_L = 500\Omega$     | 3   | -   | 3   | -   | ns    |

|                                |                 | CLKAB LOW    | PERB valid                | C <sub>L</sub> = 50pF | 6.5 | -   | 3.5 | -   | ns    |

|                                |                 | GEN/CHK HIGH | PERB not valid            | $R_L = 500\Omega$     | 3   | -   | 3   | -   | ns    |

|                                |                 | CLKAB HIGH   | PB <sub>X</sub> valid     | C <sub>L</sub> = 50pF | 6.5 | -   | 3.5 | -   | ns    |

|                                |                 | GEN/CHK LOW  | PB <sub>X</sub> not valid | $R_L = 500\Omega$     | 3   | -   | 3   | -   | ns    |

|                                |                 | CLKAB HIGH   | PERB valid                | C <sub>L</sub> = 50pF | 6.5 | -   | 3.5 | -   | ns    |

|                                |                 | GEN/CHK HIGH | PERB not valid            | $R_L = 500\Omega$     | 3   | -   | 3   | -   | ns    |

## Switching Specifications Over Operating Range (Setup Times) (Continued)

|                              |        | (1)          | (NOTES 27, 31) |                       | -   | Г   | Α   | ·Τ  |       |

|------------------------------|--------|--------------|----------------|-----------------------|-----|-----|-----|-----|-------|

| DESCRIPTION                  | SYMBOL | ,            | CONDITIONS     |                       | MIN | MAX | MIN | MAX | UNITS |

| Setup Time                   | tsu    | CLKAB LOW    | PERB valid     | C <sub>L</sub> = 50pF | 6.5 | -   | 3.5 | -   | ns    |

| PAx to LEAB                  |        | GEN/CHK HIGH | PERB not valid | $R_L = 500\Omega$     | 3   | -   | 3   | -   | ns    |

|                              |        | CLKAB HIGH   | PERB valid     | C <sub>L</sub> = 50pF | 6.5 | -   | 3.5 | -   | ns    |

|                              |        | GEN/CHK HIGH | PERB not valid | $R_L = 500\Omega$     | 3   | -   | 3   | -   | ns    |

| Setup Time                   | tsu    | CLKBA LOW    | PERA valid     | C <sub>L</sub> = 50pF | 6.5 | -   | 3.5 | -   | ns    |

| $B_X$ to LEBA $PB_X$ to LEBA |        |              | PERA not valid | $R_L = 500\Omega$     | 3   | -   | 3   | -   | ns    |

|                              |        | CLKAB HIGH   | PERA valid     | C <sub>L</sub> = 50pF | 6.5 | -   | 3.5 | -   | ns    |

|                              |        |              | PERA not valid | $R_L = 500\Omega$     | 3   | -   | 3   | -   | ns    |

## **Switching Specifications Over Operating Range** (Hold Times)

|                                                    |                | (NOTE 27)             | T 77) |     | Α   | Т   |       |

|----------------------------------------------------|----------------|-----------------------|-------|-----|-----|-----|-------|

| DESCRIPTION                                        | SYMBOL         | CONDITIONS            | MIN   | MAX | MIN | MAX | UNITS |

| Hold Time HIGH or LOW $A_X$ to LEAB, $B_X$ to LEBA | t <sub>H</sub> | C <sub>L</sub> = 50pF | 1     | -   | 1   | -   | ns    |

| Hold Time HIGH or LOW PA <sub>X</sub> to LEAB      | t <sub>H</sub> | $R_L = 500\Omega$     | 1     | -   | 1   | -   | ns    |

| Hold Time HIGH or LOW PB <sub>X</sub> to LEBA      | t <sub>H</sub> |                       | 1     | -   | 1   | -   | ns    |

| Hold Time $A_X$ to CLKAB, $PA_X$ to CLKAB          | t <sub>H</sub> |                       | 1     | -   | 1   | -   | ns    |

| Hold Time $B_X$ to CLKBA, $PB_X$ to CLKBA          | t <sub>H</sub> |                       | 1     | -   | 1   | -   | ns    |

| LEAB or LEBA Pulse Width HIGH (Note 30)            | t <sub>W</sub> |                       | 3     | -   | 3   | -   | ns    |

| CLKAB or CLKBA Pulse Width HIGH or LOW (Note 30)   | tW             |                       | 3     | -   | 3   | -   | ns    |

#### NOTES:

- 19. For conditions shown as Max or Min, use appropriate value specified under Electrical Specifications for the applicable device type.

- 20. Typical values are at  $V_{CC} = 5.0V$ ,  $25^{\circ}$ C ambient and maximum loading.

- 21. Not more than one output should be shorted at one time. Duration of the test should not exceed one second.

- 22. This parameter is determined by device characterization but is not production tested.

- 23. Per TTL driven input ( $V_{IN} = 3.4V$ ); all other inputs at  $V_{CC}$  or GND.

- 24. This parameter is not directly testable, but is derived for use in Total Power Supply Calculations.

- 25. Values for these conditions are examples of the  $I_{CC}$  formula. These limits are guaranteed but not tested.

- 26.  $I_C = I_{QUIESCENT} + I_{INPUTS} + I_{DYNAMIC}$

- $I_{C} = I_{CC} + \Delta I_{CC} D_{H} N_{T} + I_{CCD} (f_{CP}/2 + f_{I} N_{I})$

- I<sub>CC</sub> = Quiescent Current

- $\Delta I_{\hbox{\footnotesize CC}}$  = Power Supply Current for a TTL High Input (V\_{IN} = 3.4V)

- D<sub>H</sub> = Duty Cycle for TTL Inputs High

- $N_T$  = Number of TTL Inputs at  $D_H$

- $I_{CCD}$  = Dynamic Current Caused by an Input Transition Pair (HLH or LHL)

- f<sub>CP</sub> = Clock Frequency for Register Devices (Zero for Non-Register Devices)

- f<sub>I</sub> = Input Frequency

- N<sub>I</sub> = Number of Inputs at f<sub>I</sub>

- All currents are in milliamps and all frequencies are in megahertz.

- 27. See test circuit and wave forms.

- 28. Minimum limits are guaranteed but not tested on Propagation Delays.

- 29. On Open Drain Outputs  $t_{PLH}$  is measured up to  $V_{OUT}$  =  $V_{OL}$  + 0.3V.

- 30. This parameter is guaranteed but not production tested.

- 31. "Not Valid" means the setup time indicated is not sufficient to assure proper funtioning of this output; however, the set-up time indicated will assure proper functioning of the A-to-B or B-to-A port respective to the indicated direction.

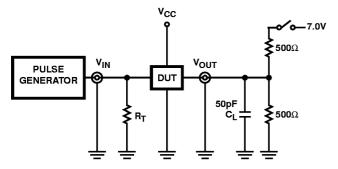

## Test Circuits and Waveforms

### NOTE:

32. Pulse Generator for All Pulses: Rate  $\leq$  1.0MHz;  $Z_{OUT} \leq$  50  $\!\Omega$ ;  $t_f,\,t_r \leq$  2.5ns.

FIGURE 1. TEST CIRCUIT

#### **SWITCH POSITION**

| TEST                                | SWITCH |

|-------------------------------------|--------|

| t <sub>PLZ</sub> , t <sub>PZL</sub> | Closed |

| tPHZ, tPZH, tPLH, tPHL              | Open   |

#### **DEFINITIONS:**

C<sub>L</sub> = Load capacitance, includes jig and probe capacitance.

$R_T$  = Termination resistance, should be equal to  $Z_{OUT}$  of the Pulse Generator.

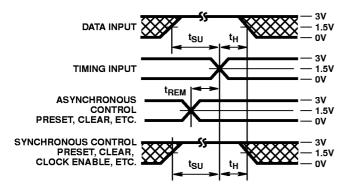

FIGURE 2. SETUP, HOLD, AND RELEASE TIMING

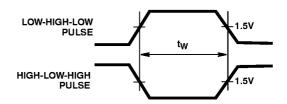

FIGURE 3. PULSE WIDTH

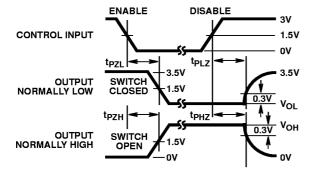

FIGURE 4. ENABLE AND DISABLE TIMING

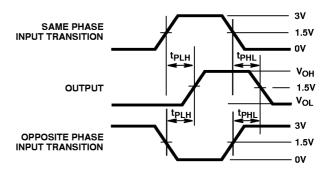

FIGURE 5. PROPAGATION DELAY