# FAST CMOS EEPROM WITH SERIAL PROTOCOL CHANNEL (SPC") 16K (2K x 8-BIT)

IDT78C18A

### **FEATURES:**

- 2K x 8 EEPROM with serial write and readback

- 5 volt only operation

- Fast access times

- Military: 75ns (max.)

- Commercial: 70ns (max.)

- Low-power CEMOS<sup>™</sup> technology

- Active Current: 125mA

- Standby Current (full CMOS): 0.9mA

- Serial Protocol Channel (SPC) allows load and readout of the memory array over a 4-wire channel

- On-chip timer

- Automatic byte erase before write

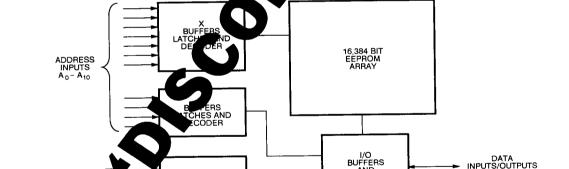

**FUNCTIONAL BLOCK DIAGRAM**

- Byte write 10ms max.

- DATA Polling—detection of write cycle completion

- Data protection circuitry (Vcc lockout for Vcc < 3.8V) provides data integrity on power up/power down

- Minimum endurance of 10,000 write cycles per byte

- Endurance failure rate < 0.1% per 1000 cycles</li>

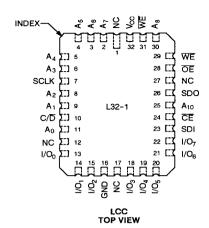

- Available in 28-pin THINDIP and 32-pin LCC

- Military product compliant to MIL-STD-883, Class B

#### **DESCRIPTION:**

The IDT78C18A is a 5 volt only 2K x 8 Electrically Erasable Programmable Read-Only Mem (EEPROM) with Serial Protocol Channel (SPC). SPC complete into the EEPROM's parallel information path by providing, serial link (4 additional pins) by which its nonvolatile array can be loaded or read. The IDT78C18A is written on a byte basis ovides 16,384 bits of nonvolatile data storage (data retg on harcess of 100 years). Fast read access times allow zellow it st. cycles with high-performance microprocessors.

Writing is simpled by all internal charge-pump and timer circuit which elia and write pulse she with the cuits. Internal latches free the host system for other lates do a write cycle. Byte erase before write occurs automat. A DATA Polling mode is provided for determining the cycle impletion.

The IDT: sideal for systems requiring nonvolatility and in-systems requiring nonvolatility and in-systems requiring nonvolatility and in-systems required in the latest revision of MIL-STD-883, Class B, making it has been dily as ded to military temperature applications demanding the level of performance and reliability.

CEMOS and SPC are trademarks of Integrated Device Technology, Inc.

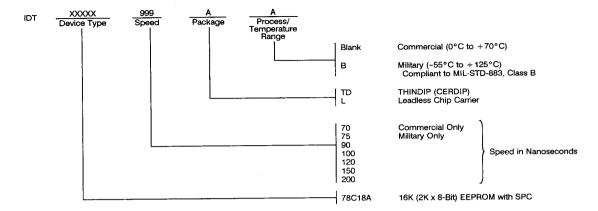

MILITARY AND COMMERCIAL TEMPERATURE RANGES

**DECEMBER 1987**

1/00 - 1/07

© 1987 Integrated Device Technology, Inc

12-10

AND

SERIAL DATA OUT

DSC-8001/-

CONTROL LOGIC

SERIAL PROTOCOL

CHANNEL

#### PIN CONFIGURATIONS

# **DEVICE OPERATIONAL MODE (1,2)**

| MODE PIN       | CE              | ŌĒ                 | WE                 | I/O <sub>0</sub> - I/O <sub>7</sub>                    |

|----------------|-----------------|--------------------|--------------------|--------------------------------------------------------|

| Read           | V <sub>IL</sub> | V <sub>IL</sub>    | V <sub>IH</sub>    | Data <sub>OUT</sub> (O <sub>0</sub> - O <sub>7</sub> ) |

| Byte Write     | V <sub>IL</sub> | V <sub>IH</sub>    | V <sub>IL</sub>    | Data <sub>IN</sub> (I <sub>0</sub> - I <sub>7</sub> )  |

| Standby        | V <sub>IH</sub> | Don't<br>Care      | Don't<br>Care      | High Z                                                 |

| Write Inhibit  | Don't<br>Care   | V <sub>IL</sub>    | Don't<br>Care      | High Z                                                 |

| TTTTO TITLIBIT | Don't<br>Care   | Don't<br>Care      | V <sub>IH</sub>    | High Z                                                 |

| Chip Erase     | V <sub>IL</sub> | V <sub>H</sub> (2) | V <sub>H</sub> (2) | High Z                                                 |

#### NOTES:

- 1. All control inputs are TTL-compatible.

- 2. V<sub>H</sub> = High Voltage; optional function, consult IDT for more details.

#### **PIN NAMES**

| FIN NAMES                                                                           |  |  |  |

|-------------------------------------------------------------------------------------|--|--|--|

| Addresses-Column                                                                    |  |  |  |

| Addresses-Row                                                                       |  |  |  |

| Chip Enable                                                                         |  |  |  |

| Output Enable                                                                       |  |  |  |

| Write Enable                                                                        |  |  |  |

| Data Input ( $I_0 - I_7$ ) during write;<br>Data Output ( $O_0 - O_7$ ) during read |  |  |  |

| Serial Data Input                                                                   |  |  |  |

| Serial Data Output                                                                  |  |  |  |

| Data Clock Input                                                                    |  |  |  |

| Command/Data                                                                        |  |  |  |

|                                                                                     |  |  |  |

12

# SPC OPERATIONAL MODES (1)

| MODE    | CE | ŌĒ | WE | C/D | SCLK | FUNCTION                                         |

|---------|----|----|----|-----|------|--------------------------------------------------|

| Command | ×  | ×  | ×  | н   |      | Shift bit into command register                  |

| Data    | ×  | Х  | х  | L   |      | Shift bit into data register                     |

| Execute | ×  | ×  | ×  | 7_  |      | Execute command during time between C/D and SCLK |

NOTE:

1. X = Don't Care

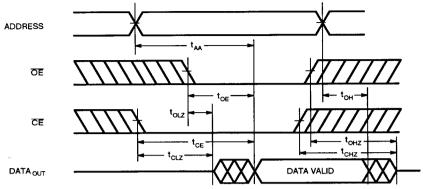

#### READ MODE

Chip Enable  $(\overline{\text{CE}})$  and Output Enable  $(\overline{\text{OE}})$  must be logically active in order for data to be available at the outputs. After a selected byte address is stable,  $\overline{\text{CE}}$  is taken to a TTL LOW (enabling chip). The Write Enable  $(\overline{\text{WE}})$  pin should remain deselected (TTL HIGH) during the entire read cycle. Data is gated from the device outputs by selecting the  $\overline{\text{OE}}$  pin (TTL LOW). For serial read function, see description within "Serial Protocol Channel" section.

#### WRITE MODE

The IDT78C18A is programmed electrically in-circuit and does not require any external latching, erasing or timing. Writing to the IDT78C18A is as easy as writing to a static RAM. When a write cycle is initiated, the device automatically latches the address, data and control signals as it begins its write operation.

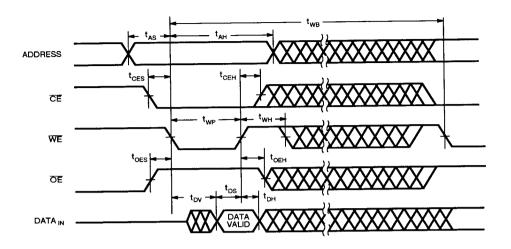

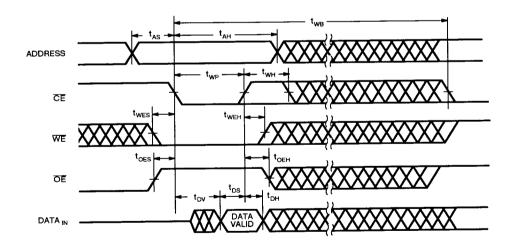

A write cycle is initiated when both  $\overline{CE}$  and  $\overline{WE}$  are LOW and  $\overline{OE}$  is HIGH. The IDT78C18A supports both a  $\overline{CE}$  and  $\overline{WE}$  controlled write cycle. All inputs, except for data, are latched on the falling edge of either  $\overline{CE}$  or  $\overline{WE}$ , whichever occurs last. Data is then latched in by the rising edge of either  $\overline{CE}$  or  $\overline{WE}$ , whichever occurred first. An automatic byte erase of the existing data at the addressed location is performed before the new data byte is written. Once initiated, a byte write operation will automatically proceed to completion within 10ms. For serial write function, see description within "Serial Protocol Channel" section.

#### STANDBY MODE

The IDT78C18A features a standby mode which reduces the maximum active current from 125mA to 20mA for TTL levels and to 0.9mA for CMOS levels. With  $\overline{\text{CE}} \geq \text{V}_{\text{H}}$  all outputs are in the high impedance state.

#### **DATA PROTECTION**

Nonvolatile data is protected from inadvertent writes in the following manner:

#### Power Up/Down

On-chip circuitry provides protection against false write during  $V_{\rm CC}$  power up/down. The IDT78C18A features an internal sensing circuit that disables the internal programming circuit if  $V_{\rm CC} < 3.8V$ . This prevents input signals at CE, WE and OE from triggering a write cycle during a  $V_{\rm CC}$  power up/down event.

#### **Noise Protection**

The IDT78C18A will typically reject write pulses that are less than 15ns. This prevents the initiation of a write cycle by a noise occurrence.

#### Write Inhibit

Holding either OE LOW, WE HIGH or CE HIGH during a poweron and power-off, will inhibit inadvertent writes.

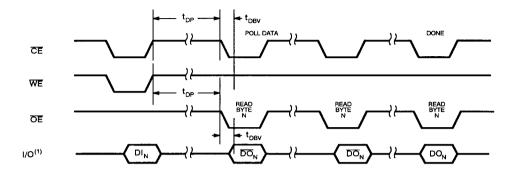

# DATA POLLING

The IDT78C18A has a maximum write cycle time of 10ms; a write will always be completed in less than the maximum cycle time. Write cycle completion is readily determined via a simple software routine ( $\overline{\rm DATA}$  Polling) that performs a read operation while the device is in an automatic write mode. If a read command (addressed to the last byte written) is given while the IDT78C18A is still writing, the inverse of the most significant bit (I/O7 pin) of the last byte written will be present. The most significant bit becomes valid when the write cycle is completed. Thus, a  $\overline{\rm DATA}$  Polling

monitor of the output (or periodic read of the last written byte) for true data can be used to detect early completion of a write cycle.

#### **CHIP ERASE**

In particular applications, erasure of the entire chip (all bytes simultaneously) may be desired. An optional chip erase feature of the IDT78C18A allows erasure of the entire chip within 5ms. Contact IDT for more details regarding this optional function.

#### **ENDURANCE**

IDT's EEPROM technology employs the Fowler-Nordheim method of tunneling across a thin oxide. IDT78C18A EEPROMs are designed and tested for applications requiring extended endurance.

The endurance failure mechanism associated with EEPROMs results from the charge trapping in the thin tunneling dielectric. This failure is a function of the number of write cycles that each byte in the part has experienced. Trapped charges accumulate slowly with each write cycle and eventually become large enough to prevent reliable writing to the bit cell. Since some bits are more sensitive than others, an endurance failure is typically a single bit failure (i.e. a failure of a single bit to properly write or retain data).

To test for endurance, sample devices are written 10,000 times at every byte location and checked for data retention capability. IDT's tests ensure that shipped devices will write a minimum of 10,000 times (at every byte location) with a maximum failure rate of 1%. This means that up to 1% of a sample of devices will fail to write or retain data after being written to 10,000 times. Those devices that do fail typically have a single bit(s) that fails to retain data after being written.

For more detailed information please refer to the *IDT Reliability* Report on Endurance.

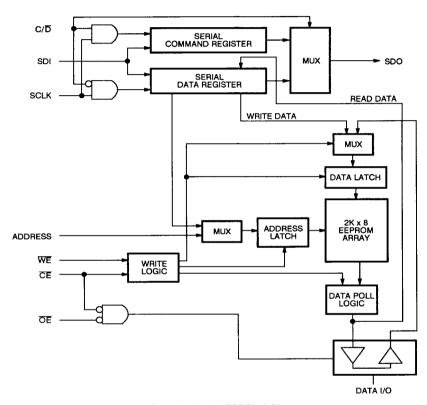

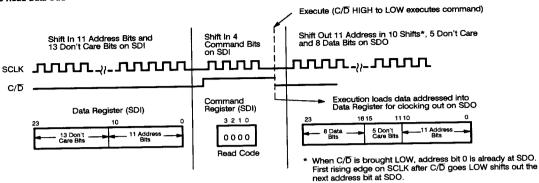

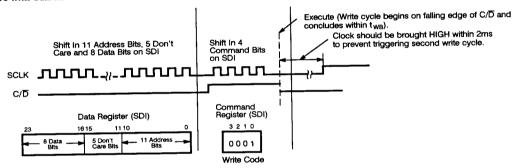

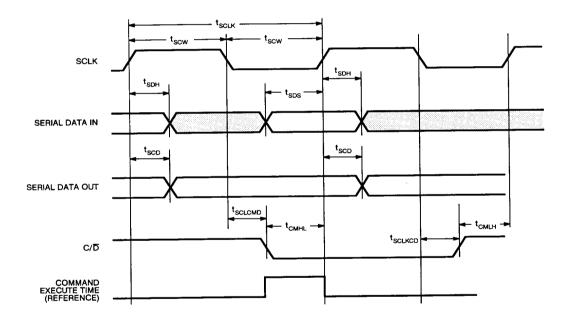

## SERIAL PROTOCOL CHANNEL

The Serial Protocol Channel (SPC ™) provides a method by which data can be entered or extracted from the memory array via four unique pins CD̄, SCLK, SDI and SDO. SPC logic consists of a 24-bit data shift register, a 4-bit command register and clock logic consisting of gates and a flip-flop (see block diagram). From the outside, SPC appears like two parallel serial shift registers; one for command and the other data. Data is clocked in on a Serial Data Input pin (SDI) and out on a Serial Data Output pin (SDO). The transfer of data is controlled by a serial clock (SCLK) and a Command/Data mode input (C/D̄). The serial clock (SCLK input) shifts information and the Command/Data (C/D̄) input selects the register that will be shifted. The command register (when loaded and executed) controls the loading of data into and out of the data register with regard to writing to or reading from an addressed location of the memory array.

There are two modes for the shift operation: when C/\overline{D} input is LOW, data information is shifted through the device and, when C/\overline{D} is HIGH, command is shifted through. As the C/\overline{D} line transitions from HIGH (command) to LOW (data), a clock pulse is internally generated to the command decode logic and is used to execute the instruction in the command register (clock pulse ends when serial clock transitions from LOW to HIGH). There are four steps to executing an SPC command: data is shifted in, command bits are then shifted in, the command is then executed and data is clocked (shifted) out. (Note: The data to the SPC is shifted in LSB first.) During the data mode, data is simultaneously shifted into the serial data register while data in the register is shifted out.

15

Command codes that are utilized for read/write operations are shown below:

Command Words (4-bit Command Register):

All functions can be performed serially, including DATA Polling. The operation of serial DATA Polling is the same as SPC read. The byte being written is read and bit 23 (representing I/O<sub>7</sub>) will be the complement of the most significant data bit until the write cycle is completed. (After completion of the write cycle, bit 23 will show true data.)

Figure 1. Detailed SPC Block Diagram

12

#### To Read Data Out:

#### To Write Data In:

#### ABSOLUTE MAXIMUM RATINGS (1)

| SYMBOL            | RATING                                     | COMMERCIAL   | MILITARY     | UNIT |

|-------------------|--------------------------------------------|--------------|--------------|------|

| V <sub>TERM</sub> | Terminal Voltage<br>with Respect to<br>GND | -0.5 to +7.0 | -0.5 to +7.0 | >    |

| TA                | Operating<br>Temperature                   | 0 to +70     | -55 to + 125 | ô    |

| T <sub>BIAS</sub> | Temperature<br>Under Bias                  | -55 to +125  | -65 to +135  | ပံ   |

| Т <sub>STG</sub>  | Storage<br>Temperature                     | -55 to +125  | -65 to +150  | ç    |

| P <sub>T</sub>    | Power Dissipation                          | 1.0          | 1.0          | W    |

| lout              | DC Output Current                          | 50           | 50           | mA   |

#### NOTE:

Stresses greater than those listed under ABSOLUTE MAXIMUM RAT-INGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### **ENDURANCE**

| PARAMETER         | VALUE  | UNIT        |

|-------------------|--------|-------------|

| Minimum Endurance | 10,000 | Cycles/Byte |

# RECOMMENDED OPERATING TEMPERATURE AND SUPPLY VOLTAGE

| GRADE      | RADE AMBIENT GND TEMPERATURE |    | V <sub>cc</sub> |  |

|------------|------------------------------|----|-----------------|--|

| Military   | -55°C to +125°C              | ٥٧ | 5.0V ± 10%      |  |

| Commercial | 0°C to +70°C                 | 0V | 5.0V ± 10%      |  |

# RECOMMENDED DC OPERATING CONDITIONS

| SYMBOL          | PARAMETER          | MIN. | TYP. | MAX. | UNIT |

|-----------------|--------------------|------|------|------|------|

| V <sub>CC</sub> | Supply Voltage     | 4.5  | 5.0  | 5.5  | ٧    |

| V <sub>IH</sub> | Input High Voltage | 2.2  | 3.5  | 6.0  | ٧    |

| V <sub>IL</sub> | Input Low Voltage  | -0.3 | 0.4  | 0.8  | ٧    |

| V <sub>W1</sub> | Write Inhibit      | 3.8  | _    | _    | ٧    |

#### CAPACITANCE ( $T_A = +25^{\circ}C$ , f = 1.0MHz, $V_{CC} = 5.0$ V)

| SYMBOL          | PARAMETER(1)       | CONDITIONS            | TYP. | UNIT |

|-----------------|--------------------|-----------------------|------|------|

| C <sub>IN</sub> | Input Capacitance  | V <sub>IN</sub> = 0V  | 6    | pF   |

| Соот            | Output Capacitance | V <sub>OUT</sub> = 0V | 8    | рF   |

#### NOTE:

1. This parameter is sampled and not 100% tested.

#### DC ELECTRICAL CHARACTERISTICS

Following Conditions Apply Unless Otherwise Specified:

$T_A = 0$ °C to +70°C

$V_{CC} = 5.0V \pm 10\%$  (Commercial)

$T_A = -55$ °C to + 125°C

$V_{CC} = 5.0V \pm 10\%$  (Military)

$V_{HC} = V_{CC} - 0.2V$

$V_{LC} = 0.2V$  $C_L = 30pF$

| SYMBOL           | PARAMETER                                                                 | TEST CONDITIONS                                                                                                                                      | MIN. | MAX.  | UNIT |

|------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|

| lul              | Input Leakage Current                                                     | V <sub>CC</sub> = Max.,V <sub>IN</sub> = GND to V <sub>CC</sub>                                                                                      | _    | 10    | μА   |

| I <sub>LO</sub>  | Output Leakage Current                                                    | $\overline{CE} = V_{IH}$ or $\overline{OE} = V_{IH}$ , $V_{I/O} = \overline{GND}$ to $V_{CC}$                                                        |      | 10    | μА   |

| l <sub>CC1</sub> | Operating Power Supply Current V <sub>CC</sub> = Max., f = 0              | CE = V <sub>IL</sub> , I <sub>I/O</sub> = 0mA                                                                                                        | _    | 125   | mA   |

| I <sub>CC2</sub> | Dynamic Operating Current<br>V <sub>CC</sub> = Max., f = f <sub>MAX</sub> | CE = V <sub>IL</sub> , I <sub>I/O</sub> = 0mA                                                                                                        | _    | 125   | mA   |

| I <sub>SB</sub>  | Standby Power Supply Current (TTL Level)                                  | $\begin{array}{c c} \overline{CE} \geq V_{IH} \ , V_{CC} = Max \ I_{I/O} = OmA \\ V_{IN} \geq V_{IH} \ or \ 0 \leq V_{IN} \leq V_{IL} \end{array}$   | _    | 20    | mA   |

| I <sub>SB1</sub> | Full Standby Power Supply Current<br>(CMOS Level)                         | $\overline{\text{CE}} \ge V_{HC}, V_{CC} = \text{Max., } I_{VO} = 0\text{mA}$<br>$V_{IN} \ge V_{CC} -0.2 \text{V or } 0 \le V_{IN} \le 0.2 \text{V}$ | _    | 0.9   | mA   |

| V <sub>OL</sub>  | Output Low Voltage                                                        | V <sub>CC</sub> = Min., I <sub>OL</sub> = 8mA                                                                                                        | -    | 0.4   | ٧    |

| V <sub>OH</sub>  | Output High Voltage                                                       | V <sub>CC</sub> = Min., I <sub>OH</sub> = -2mA                                                                                                       | 2.4  | l – – | ٧    |

AC ELECTRICAL CHARACTERISTICS (V<sub>CC</sub> = 5V ±10%, All Temperature Ranges; C<sub>L</sub> = 30pF)

| SYMBOL           | PARAMETER                                       | COM'L. C<br>IDT78C18<br>MIN. | ONLY | IDT78C18<br>MIN. |       |   | NAL/MILITA<br>8A100/120<br>MAX. | IDT78C18 | BA150/200<br>MAX. | TINU |

|------------------|-------------------------------------------------|------------------------------|------|------------------|-------|---|---------------------------------|----------|-------------------|------|

| READ CY          | CLE                                             |                              |      |                  |       | · |                                 |          |                   |      |

| t <sub>CE</sub>  | Chip Enable Access Time                         | _                            | 70   | <b>-</b>         | 75/90 |   | 100/120                         |          | 150/200           | ns   |

| tAA              | Address Access Time                             | _                            | 70   | _                | 75/90 | - | 100/120                         |          | 150/200           | ns   |

| t <sub>OE</sub>  | Output Enable to Output Valid                   | _                            | 50   | Ţ —              | 50/60 | - | 65/70                           |          | 70                | ns   |

| toLZ             | Chip Enable to Output in Low Z <sup>(1)</sup>   | 5                            | _    | 5                |       | 5 |                                 | <b>T</b> |                   | ns   |

| toLZ             | Output Enable to Output in Low Z <sup>(1)</sup> | 5                            | _    | 5                | _     | 5 |                                 | 5        |                   | ns   |

| t <sub>CHZ</sub> | Chip Disable to Output in High Z (1)            | 0                            | 20   | 0                | 20/30 | 0 | 20/30                           | 0        | 20/30             | ns   |

| t <sub>OHZ</sub> | Output Disable to Output in High Z (1)          | 0                            | 20   | 0                | 20/30 | 0 | حات                             | 0        | 20/30             | ns   |

| t <sub>OH</sub>  | Output Hold from Address Change                 | 5                            |      | 5                | _     | 5 |                                 | 5        |                   | ns   |

#### NOTES:

- 1. This parameter is guaranteed but not tested.

- Military temperature range only.

AC ELECTRICAL CHARACTERISTICS (V<sub>CC</sub> = 5V ±10%, All Temperature Ranges, 30, 2)

| SYMBOL           | PARAMETER                        | MIN. | MAX.            | UNIT |

|------------------|----------------------------------|------|-----------------|------|

| WRITE CYCLE      |                                  |      |                 |      |

| t <sub>AS</sub>  | Address Set-up Time              | 5    |                 | ns   |

| t <sub>AH</sub>  | Address Hold Time                | 50   |                 | ns   |

| t <sub>DS</sub>  | Data Set-up Time                 | 20   | -               | ns   |

| t <sub>DH</sub>  | Data Hold from Write Time        | 15   |                 | ns   |

| t <sub>OES</sub> | Output Enable Set-up Time        | 5    |                 | ns   |

| t <sub>OEH</sub> | Chip Enable Hold from Write Time | 15   |                 | ns   |

| t <sub>CES</sub> | Chip Enable Set-up Time          | 0    | -               | ns   |

| t <sub>CEH</sub> | Chip Enable Hold Time            | 0    | -               | ns   |

| t <sub>WP</sub>  | Write Pulse Width                | 50   |                 | ns   |

| t <sub>WB</sub>  | Byte Write Cycle                 |      | 10              | ms   |

| t <sub>DBV</sub> | DATA Polling to DATA Valid       | -    | t <sub>OE</sub> |      |

| t <sub>wH</sub>  | Write Hold Time                  | 15   | _               | ns   |

| t <sub>DP</sub>  | End of Write Pulse to DATA Pung  | 15   | _               | ns   |

| t <sub>wes</sub> | Write Enable Set-up Time         | 0    |                 | ns   |

| t <sub>WEH</sub> | Write Enable Hold Time           | 0    | _               | ns   |

| t <sub>DV</sub>  | Data Valid Time (1, 2)           | _    | 1               | μs   |

#### NOTES:

- Data must be valid within 1μs maxim.

d must remain valid if t<sub>WP</sub> is longer than 1μs.

- 2. This parameter is guaranteed but not test

# AC TEST CONDITION

| Input Pulse Levels Input Rise/Fall Times Input Timing Reference Levels | GND to 3.0V<br>5ns<br>1.5V |

|------------------------------------------------------------------------|----------------------------|

| Output Reference Levels                                                | 1.5V                       |

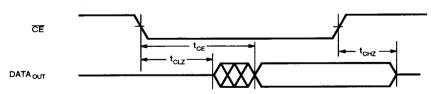

## TIMING WAVEFORM OF READ CYCLE NO. 1(1)

NOTE:

1. WE is HIGH for Read Cycle.

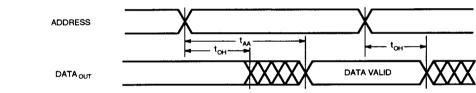

# TIMING WAVEFORM OF READ CYCLE NO. 2(1)

NOTE: 1. WE is HIGH;  $\overline{CE} = V_{jL}$ ;  $\overline{OE} = V_{jL}$

# TIMING WAVEFORM OF READ CYCLE NO. 3(1)

NOTE: 1.  $\overline{WE}$  is HIGH;  $\overline{OE} = V_{IL}$ : address valid prior to or coincident with  $\overline{CE}$  transition LOW.

# TIMING WAVEFORM OF WRITE CYCLE NO. 1, WE CONTROLLED

# TIMING WAVEFORM OF WRITE CYCLE NO. 2, $\overline{\text{CE}}$ CONTROLLED

#### **DATA POLLING**

#### NOTE:

Most significant bit of the byte being written is inverted and available at I/O 7 if a Read command is issued. All other outputs are high impedance at this

time. True data will not be released until the Write cycle is completed.

# SPC AC ELECTRICAL CHARACTERISTICS V<sub>CC</sub> = 5V ±10%, All Temperature Ranges

| SYMBOL            | PARAMETER                                                        |                   | COMMERCIAL(1) |                      | MILITARY (1) |                      | UNIT |

|-------------------|------------------------------------------------------------------|-------------------|---------------|----------------------|--------------|----------------------|------|

|                   |                                                                  |                   | MIN.          | MAX.                 | MIN.         | MAX.                 |      |

| t <sub>SCLK</sub> | SCLK Period                                                      |                   | 100           |                      | 100          |                      | ns   |

| tscw              | SCLK Pulse Width                                                 |                   | 50            | _                    | 50           |                      | ns   |

| t <sub>SDS</sub>  | Serial Data Set-up Time                                          |                   | 15            | -                    | 15           |                      | ns   |

| t <sub>SDH</sub>  | Serial Data Hold Time                                            |                   | 5             | _                    | 5            |                      | ns   |

| t <sub>SCD</sub>  | Clock to Serial Data Output Delay                                |                   | 4             | 25                   | 4            | 25                   | ns   |

| tsclcmd           | Clock to Command Set-up Time (3)                                 |                   | 50            |                      | 50           |                      | ns   |

| t <sub>CMLH</sub> | Command/Data Set-up Time, LOW to HIGH                            |                   | 50            |                      | 50           |                      | ns   |

| t <sub>CMHL</sub> | Command Set-up Time, HIGH to LOW (Execution Time) <sup>(4)</sup> | Read Cycle        | tAA           | -                    | tAA          | _                    | ns   |

|                   |                                                                  | Write/Erase Cycle | 100           | 2(10) <sup>(6)</sup> | 100          | 2(10) <sup>(6)</sup> |      |

| tsclkcd           | Clock LOW to C/D HIGH                                            |                   | 0             |                      | 0            | _                    | ns   |

#### NOTES:

- 1. These specifications apply to all speed grades of the product.

- 2. This parameter guaranteed but not tested.

- 3. C/D cannot change while clock is high.

- 4. During a write/erase cycle SCLK should be brought HIGH within 2ms to prevent triggering another write/erase cycle.

## **ACTEST CONDITIONS**

| AC LEST COMPLITIONS           |             |  |  |  |

|-------------------------------|-------------|--|--|--|

| Input Pulse Levels            | GND to 3.0V |  |  |  |

| Input Rise/Fall Times         | 5ns         |  |  |  |

| Input Timing Reference Levels | 1.5V        |  |  |  |

| Output Reference Levels       | 1.5V        |  |  |  |

## ORDERING INFORMATION