### Feature

- Logic supply voltage: 3.3V~5.5V

- 8-channel constant current output

- Channel output current is fixed at 48mA

- Build-in current setting resistor

- High output current accuracy: Variation between chips is less than ±6%

- Up to 25MHz serial interface clock frequency

- Maximum output terminal voltage 17V

- Schmitt trigger input structure

- 16-pin NSOP package

# Applications

- LED Display

- Digital clock, thermometer, counter, voltmeter

- Other consumer application

# **General Description**

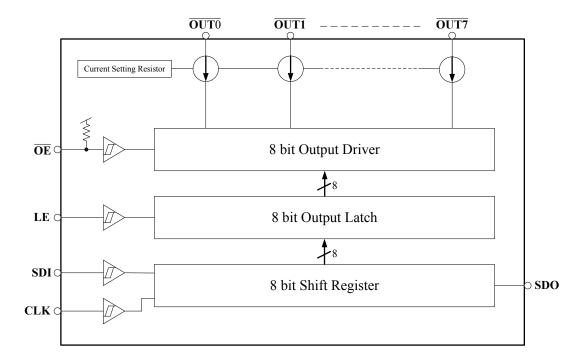

The HT16D595 is a high accuracy constant current driver which is specifically designed for LED display applications. The device provides 8-channel stable and constant current outputs for driving LEDs which may have different forward voltage characteristics, VF, due to process variations. Communication with the outside world is catered for by including a fully integrated serial interface function, which provides designers with a means of easy communication with external peripheral hardware. In this way, many devices can be cascaded together to drive larger LED displays. Furthermore, with this serial-to-serial or serial-to-parallel structure, the device is very suitable as a replacement for the 74HC595, in applications and related products which include an 8-bit serial input and serial or parallel output.

## **Block Diagram**

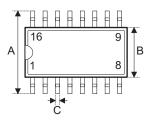

# Pin Assignment

| OUT1                  | 1 | 16 |   | VDD  |  |

|-----------------------|---|----|---|------|--|

| OUT2                  | 2 | 15 |   | OUT0 |  |

| OUT3                  | 3 | 14 | Þ | SDI  |  |

| OUT4                  | 4 | 13 | Þ | ŌĒ   |  |

| OUT5                  | 5 | 12 | Þ | LE   |  |

|                       | 6 | 11 | Þ | CLK  |  |

|                       | 7 | 10 |   | NC   |  |

| GND 🗆                 | 8 | 9  | Þ | SDO  |  |

| HT16D595<br>16 NSOP-A |   |    |   |      |  |

# **Pin Description**

| Pin Name  | I/O | Description                                                                                                  |

|-----------|-----|--------------------------------------------------------------------------------------------------------------|

| VDD       | —   | Power supply                                                                                                 |

| GND       | —   | Ground                                                                                                       |

| SDI       | I   | Serial data input                                                                                            |

| CLK       | I   | Clock input. Each data bit is shifted in to the shift register on the rising edge of the input clock signal. |

| LE        | I   | Data Latch control. Data will be latched into the internal register on high level on the LE pin.             |

| ŌĒ        | 0   | Output enable control:<br>1: all outputs disabled<br>0: all outputs enabled                                  |

| SDO       | 0   | Serial data output                                                                                           |

| OUT0~OUT7 | 0   | Parallel data output                                                                                         |

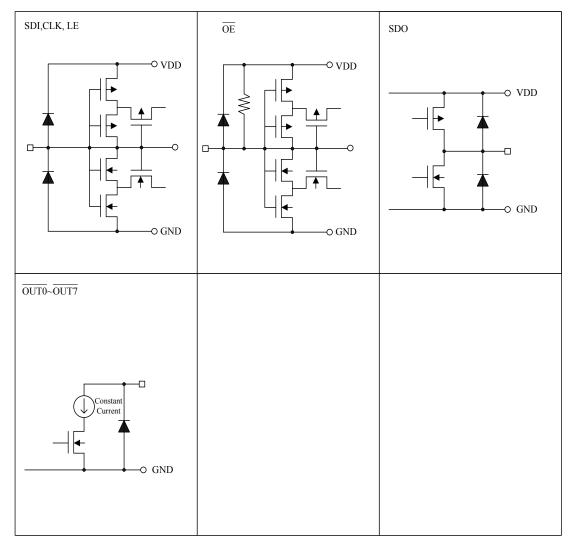

# **Generic Input / Output Structure**

T--0500

# **Absolute Maximum Ratings**

| Logic Supply Voltage (VDD) | VGND-0.3V to VGND+6.0V |

|----------------------------|------------------------|

| Logic Input Voltage        |                        |

| Output Voltage             |                        |

| Output Current             | 60mA                   |

| GND Terminal Current       | 450mA                  |

| Storage Temperature        | 55°C to 150°C          |

| Operating Temperature      | 40°C to 85°C           |

Note: These are stress ratings only. Stresses exceeding the range specified under "Absolute Maximum Ratings" may cause substantial damage to the device. Functional operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.

# **D.C. Characteristics**

|                    | İ.                                             |                          |                                      |                    |      |                    | Ta=25°0 |

|--------------------|------------------------------------------------|--------------------------|--------------------------------------|--------------------|------|--------------------|---------|

| Symbol             | Parameter                                      | Test condition           |                                      | Min.               | Тур. | Max.               | Unit    |

| Symbol             | Farameter                                      | $\mathbf{V}_{\text{DD}}$ | Condition                            |                    | Typ. | IVIAA.             | Onit    |

| V <sub>DD</sub>    | Logic Supply Voltage                           | _                        | _                                    | 3.3                | 5.0  | 5.5                | V       |

| V <sub>OUT</sub>   | Output Voltage                                 | 5V                       | OUT0~OUT7                            | _                  |      | 17                 | V       |

| V <sub>IH</sub>    | High Input Voltage                             | 5V                       | SDI, CLK                             | 0.7V <sub>DD</sub> |      | V <sub>DD</sub>    | V       |

| V <sub>IL</sub>    | Low Input Voltage                              | 5V                       | SDI, CLK                             | 0                  | _    | 0.3V <sub>DD</sub> | V       |

| V <sub>OH</sub>    | High-Level Output Voltage                      | 5V                       | SDO, I <sub>out</sub> =-4mA          | 4.6                | _    | —                  | V       |

| V <sub>OL</sub>    | Low-Level Output Voltage                       | 5V                       | SDO, I <sub>out</sub> =+4mA          | _                  |      | 0.4                | V       |

| l <sub>oz</sub>    | Output Leakage Current                         | 5V                       | V <sub>DS</sub> =17V                 | _                  |      | 0.5                | μA      |

| I <sub>OUT</sub>   | Output Current                                 | 5V                       | V <sub>DS</sub> =1V                  | _                  | 48   | —                  | mA      |

| dl <sub>out2</sub> | Current Skew(chip)                             | 5V                       | V <sub>DS</sub> =1V                  | _                  | ±3   | ±6                 | %       |

| %/dV <sub>DS</sub> | Output Current VS Output<br>Voltage Regulation | 5V                       | $V_{\text{DS}}$ within 1.0V and 3.0V | _                  | ±0.5 | ±1                 | %/V     |

| %/dV <sub>DD</sub> | Output Current VS Supply Voltage Regulation    |                          | $V_{\text{DD}}$ within 4.5V and 5.5V | _                  | ±1   | ±2                 | %/V     |

| R <sub>PU</sub>    | Pull High Resistance                           | 5V                       | ŌĒ                                   | 250                | 500  | 800                | KΩ      |

| I <sub>DD1</sub>   | Supply Current                                 | 5V                       | OUT0~OUT7=off                        | _                  | 3    | 4.5                | mA      |

| I <sub>DD2</sub>   | Supply Current                                 | 5V                       | OUT0~OUT7=on                         | _                  | 3.5  | 5.3                | mA      |

# A.C. Characteristics

|                      |                                                         |                 |                                                                       |      |                                         |      | Ta=25° |

|----------------------|---------------------------------------------------------|-----------------|-----------------------------------------------------------------------|------|-----------------------------------------|------|--------|

| Symbol               | Parameter                                               | Test condition  |                                                                       | Min. | Тур.                                    | Max. | Unit   |

| Cynnoor              | i di di interiori                                       | $V_{\text{DD}}$ | Condition                                                             |      | .,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | maxi | onic   |

| t <sub>pLH1</sub>    | Propagation Delay Time<br>("L" to "H", CLK→SDO)         | 5V              |                                                                       | _    | 17                                      | 25   | ns     |

| t <sub>pLH2</sub>    | Propagation Delay Time<br>("L" to "H", LE→OUTn)         | 5V              |                                                                       | _    | 200                                     | 250  | ns     |

| t <sub>pLH3</sub>    | Propagation Delay Time<br>("L" to "H", OE→OUTn)         | 5V              |                                                                       | _    | 200                                     | 250  | ns     |

| t <sub>pHL1</sub>    | Propagation Delay Time<br>("H" to "L", CLK→SDO)         | 5V              |                                                                       | _    | 17                                      | 25   | ns     |

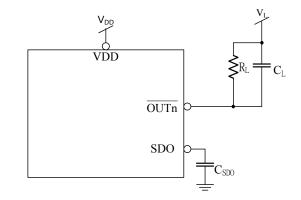

| t <sub>pHL2</sub>    | Propagation Del <u>ay Time</u><br>("H" to "L", LE→OUTn) | 5V              | V <sub>DS</sub> =0.9V<br>V <sub>IH</sub> =VDD<br>V <sub>II</sub> =GND | _    | 150                                     | 200  | ns     |

| t <sub>pHL3</sub>    | Propagation Delay Time<br>("H" to "L", OE→OUTn)         | 5V              | $V_{L}=C(R)$<br>$V_{L}=4V$<br>$R_{1}=62\Omega$                        | _    | 150                                     | 200  | ns     |

| t <sub>w(CLK)</sub>  | Pulse Width                                             | 5V              | C <sub>L</sub> =10pF                                                  | 10   | _                                       | _    | ns     |

| t <sub>W(LE)</sub>   | Pulse Width                                             | 5V              | C <sub>SDO</sub> = 50pF                                               | 10   |                                         |      | ns     |

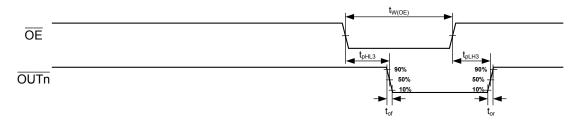

| t <sub>W(OE)</sub>   | Pulse Width                                             | 5V              |                                                                       | 300  | _                                       | _    | ns     |

| t <sub>h(LE)</sub>   | Hold Time For LE                                        | 5V              |                                                                       | 7    | _                                       | _    | ns     |

| t <sub>su(LE)</sub>  | Setup Time For LE                                       | 5V              |                                                                       | 10   |                                         |      | ns     |

| t <sub>h(SDI)</sub>  | Hold Time For SDI                                       | 5V              |                                                                       | 5    | _                                       | _    | ns     |

| t <sub>su(SDI)</sub> | Setup Time For SDI                                      | 5V              |                                                                       | 3    | _                                       | _    | ns     |

| f <sub>CLK</sub>     | Clock Frequency                                         | 5V              | Cascade operation                                                     | _    | _                                       | 25   | MHz    |

| t <sub>r</sub>       | Maximum CLK Rise Time                                   | 5V              | (Noto1)                                                               | _    | _                                       | 500  | ns     |

| t <sub>f</sub>       | Maximum CLK Fall Time                                   | 5V              | (Note1)                                                               | _    | _                                       | 500  | ns     |

| t <sub>or</sub>      | Output Rise Time of $V_{\text{OUT}}$                    | 5V              |                                                                       | _    | 70                                      | 200  | ns     |

| t <sub>of</sub>      | Output Fall Time of V <sub>OUT</sub>                    | 5V              |                                                                       | _    | 40                                      | 120  | ns     |

Note 1: If the devices are connected in cascade and if  $t_r$  or  $t_f$  is large, then these timings may be critical to achieve the correct timings for data transfer between two cascaded devices.

# **Test Circuit for AC Characteristics**

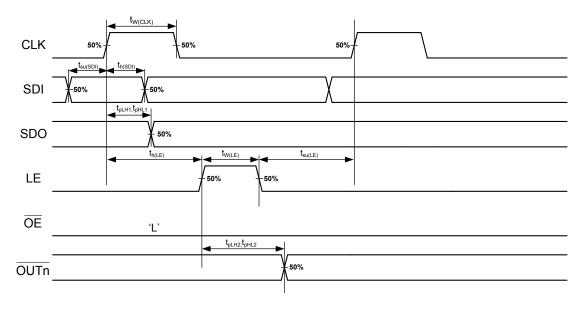

# **Timing Waveform**

### Serial-to-Serial Operation

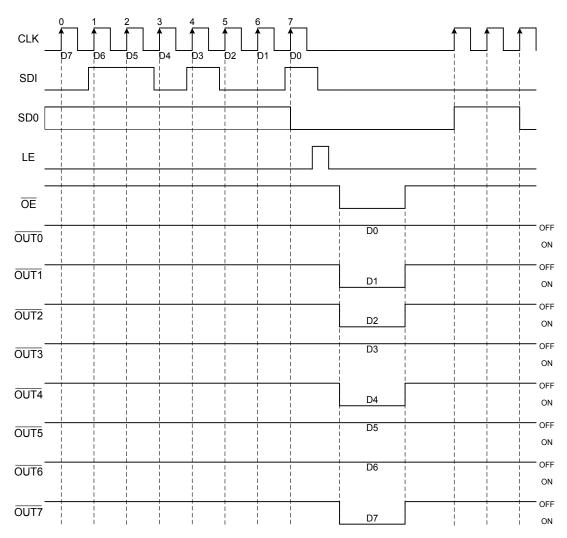

The serial-to-serial function is implemented using the SDI and SDO pins. The SDI pin is used to receive serial input data for transfer into the LSB of the internal shift register while the SDO pin is used to transmit the MSB of the internal shift register to cascaded devices. Each bit of the data is shifted in from the SDI pin into the register on the rising edge of the CLK input signal where it will become the LSB of the internal shift register. At the same time, the SDO pin will shift out the MSB in the shift register to any connected cascaded devices.

## Serial-to-Parallel Output Operation

If the LE pin is high, then data will be latched from the shift register into an internal latch for transfer to the OUT pins. Data from the internal latch is transferred to the OUT pins using the OE pin. If the OE pin is low, then the data in the shift register will be transmitted to the output pins. The OUT pins can be disabled by setting the OE pin to a high level. The SDO pin will not be affected by the LE or OE pin status. The following timing diagram illustrates the serial-to-serial and serial-to-parallel operational waveform.

## **Truth Table**

| CLK      | LE | ŌE | SDI              | OUT0OUT3OUT7                                       | SDO              |

|----------|----|----|------------------|----------------------------------------------------|------------------|

|          | н  | L  | D <sub>n</sub>   | D <sub>n</sub> ,D <sub>n-3</sub> ,D <sub>n-7</sub> | D <sub>n-7</sub> |

|          | L  | L  | D <sub>n+1</sub> | No Change                                          | D <sub>n-6</sub> |

|          | Н  | L  | D <sub>n+2</sub> | D <sub>n+2</sub> D <sub>n-1</sub> D <sub>n-5</sub> | D <sub>n-5</sub> |

|          | х  | L  | D <sub>n+3</sub> | D <sub>n+2</sub> D <sub>n-1</sub> D <sub>n-5</sub> | D <sub>n-5</sub> |

| <b>_</b> | х  | Н  | D <sub>n+3</sub> | Off                                                | D <sub>n-5</sub> |

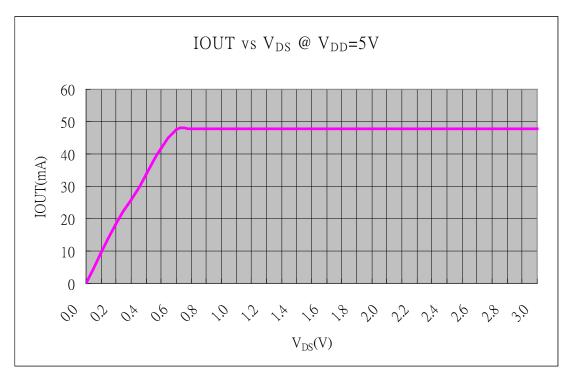

## **Constant Current Output**

The output constant current is fixed at 48mA for the 8 output channels. The constant current variation between devices is less than  $\pm 6\%$ .

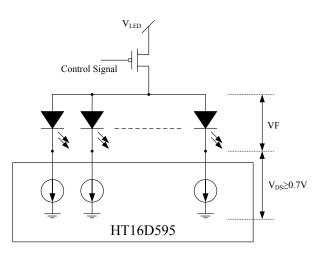

# Load Supply Voltage (V<sub>LED</sub>)

HT16D595 can be operated very well when  $V_{DS}$  is set from 0.7V to 2V. It is recommended to use the lowest supply voltage ( $V_{LED}$ ) to reduce the  $V_{DS}$  value in order to lower both the power consumption of HT16D595 and IC temperature.

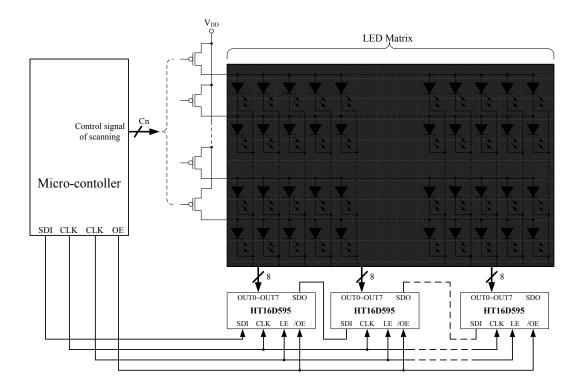

# **Application Circuit**

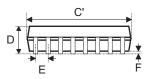

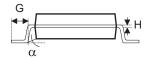

## Package Information

### 16-pin NSOP (150mil) Outline Dimensions

### MS-012

| Symbol | Dimensions in inch |       |       |  |  |  |

|--------|--------------------|-------|-------|--|--|--|

| Symbol | Min.               | Nom.  | Max.  |  |  |  |

| A      | 0.228              | —     | 0.244 |  |  |  |

| В      | 0.150              | _     | 0.157 |  |  |  |

| С      | 0.012              | _     | 0.020 |  |  |  |

| C'     | 0.386              | _     | 0.402 |  |  |  |

| D      | —                  | _     | 0.069 |  |  |  |

| E      | _                  | 0.050 | —     |  |  |  |

| F      | 0.004              | _     | 0.010 |  |  |  |

| G      | 0.016              | _     | 0.050 |  |  |  |

| Н      | 0.007              | _     | 0.010 |  |  |  |

| α      | 0°                 | _     | 8°    |  |  |  |

| Symbol | Dimensions in mm |      |       |  |  |  |

|--------|------------------|------|-------|--|--|--|

| Symbol | Min.             | Nom. | Max.  |  |  |  |

| A      | 5.79             | _    | 6.20  |  |  |  |

| В      | 3.81             | —    | 3.99  |  |  |  |

| С      | 0.30             | —    | 0.51  |  |  |  |

| C'     | 9.80             | —    | 10.21 |  |  |  |

| D      | _                | _    | 1.75  |  |  |  |

| E      | _                | 1.27 | _     |  |  |  |

| F      | 0.10             | _    | 0.25  |  |  |  |

| G      | 0.41             | —    | 1.27  |  |  |  |

| Н      | 0.18             | —    | 0.25  |  |  |  |

| α      | 0°               | _    | 8°    |  |  |  |

#### Holtek Semiconductor Inc. (Headquarters)

No.3, Creation Rd. II, Science Park, Hsinchu, Taiwan Tel: 886-3-563-1999 Fax: 886-3-563-1189 http://www.holtek.com.tw

### Holtek Semiconductor Inc. (Taipei Sales Office)

4F-2, No. 3-2, YuanQu St., Nankang Software Park, Taipei 115, Taiwan Tel: 886-2-2655-7070 Fax: 886-2-2655-7373 Fax: 886-2-2655-7383 (International sales hotline)

#### Holtek Semiconductor Inc. (Shenzhen Sales Office)

5F, Unit A, Productivity Building, No.5 Gaoxin M 2nd Road, Nanshan District, Shenzhen, China 518057 Tel: 86-755-8616-9908, 86-755-8616-9308 Fax: 86-755-8616-9722

#### Holtek Semiconductor (USA), Inc. (North America Sales Office)

46729 Fremont Blvd., Fremont, CA 94538, USA Tel: 1-510-252-9880 Fax: 1-510-252-9885 http://www.holtek.com

#### Copyright<sup>®</sup> 2011 by HOLTEK SEMICONDUCTOR INC.

The information appearing in this Data Sheet is believed to be accurate at the time of publication. However, Holtek assumes no responsibility arising from the use of the specifications described. The applications mentioned herein are used solely for the purpose of illustration and Holtek makes no warranty or representation that such applications will be suitable without further modification, nor recommends the use of its products for application that may present a risk to human life due to malfunction or otherwise. Holtek's products are not authorized for use as critical components in life support devices or systems. Holtek reserves the right to alter its products without prior notification. For the most up-to-date information, please visit our web site at <a href="http://www.holtek.com.tw">http://www.holtek.com.tw</a>.