Approved Product

#### **PRODUCT FEATURES**

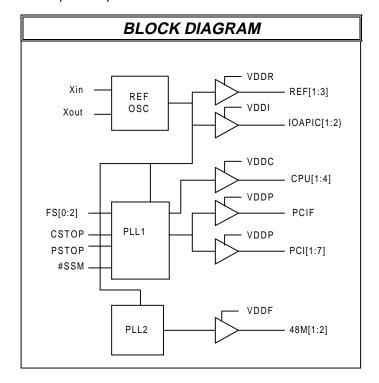

- Supports Pentium<sup>®</sup>. Pentium<sup>®</sup> II & Pro CPUs.

- Designed to meet Intel chipset specification

- 4 CPU and 8 PCI clocks

- Two 48 MHz fixed clocks for USB and Super IO.

- Separate supply pins for mixed CPU, IOAPIC, and Fixed/PCI clocks

- < 175 ps Max. skew among CPU clocks.</p>

- < 250 ps Max. skew among PCI clocks.</p>

- Controlled current output buffers

- Power management feature

- 2 IOAPIC clocks for multiprocessor support.

- 48-pin SSOP package

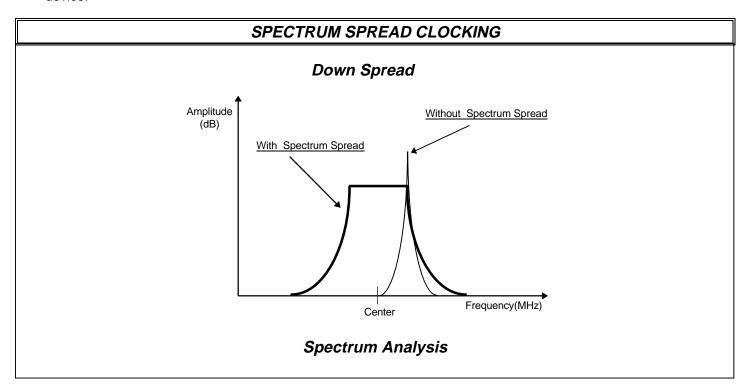

- Spread Spectrum EMI reduction mode

|     | FREQUENCY TABLE |               |              |           |  |  |  |  |  |  |  |

|-----|-----------------|---------------|--------------|-----------|--|--|--|--|--|--|--|

| FS2 | FS1 FS0 CPU PCI |               |              |           |  |  |  |  |  |  |  |

| 0   | 0               | 0             | Tri-State    | Tri-State |  |  |  |  |  |  |  |

| 0   | 1               | 1 66 (66.58)* |              | 33.3*     |  |  |  |  |  |  |  |

| 1   | 0               | 0             | Ref/2        | Ref/4     |  |  |  |  |  |  |  |

| 1   | 1               | 1             | 100 (99.7)** | 33.2**    |  |  |  |  |  |  |  |

NOTE: \*Down Spread 1.25% (total)

\*\*Down Spread .5% (total)

#### **CONNECTION DIAGRAM** IMISG577 VDDR REF2 2 REF3 VSS 3 46 VDDI IOAPIC1 XIN 45 XOUT IOAPIC2 VSS 43 VSS PCI F 7 42 N/C □ vddc PCI1 VDDP \_\_\_ CPU1 PCI2 39 CPU2 10 PCI3 11 38 VSS VSS 12 37 VDDC CPU3 PCI4 13 36 PCI5 14 35 CPU4 VDDP 🗌 15 34 VSS 16 VDD PCI6 33 PCI7 17 32 □vss VSS 🗌 PSTOP VDD 30 CSTOP 19 □PD vss 🗌 20 29 VDDF 28 #SSM 21 48M1 22 27 FS0 23 48M2 26 FS1 VSS 24 25 FS2

Approved Product

| Approved                                         | d Product       |      |     |           |                                                                                                                                                                 |  |  |  |  |  |  |

|--------------------------------------------------|-----------------|------|-----|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                                                  | PIN DESCRIPTION |      |     |           |                                                                                                                                                                 |  |  |  |  |  |  |

| PIN                                              | Pin             | PWR  | I/O | TYPE      | Description                                                                                                                                                     |  |  |  |  |  |  |

| No.                                              | Name            |      |     |           |                                                                                                                                                                 |  |  |  |  |  |  |

| 4                                                | Xin             | VDD  | I   | OSC1      | On-chip reference oscillator input pin. Requires either an external parallel resonant crystal (nominally 14.318 MHz) or externally generated reference signal   |  |  |  |  |  |  |

| 5                                                | Xout            | VDD  | 0   | OSC1      | O-chip reference oscillator output pin. Drives an external parallel resonant crystal when an externally generated reference signal is used, is left unconnected |  |  |  |  |  |  |

| 25, 26,<br>27                                    | FS(0:2)         | -    | I   | PAD<br>PU | Frequency select input pins. See frequency select table on page 1. These pin has an internal pull-up                                                            |  |  |  |  |  |  |

| 40, 39,<br>36, 35                                | CPU(1:4)        | VDDC | 0   | BUF1      | Clock outputs. CPU frequency table specified on page 1.                                                                                                         |  |  |  |  |  |  |

| 45, 44                                           | IOAPIC(1:2)     | VDDI | 0   | BUF2      | IOAPIC clock for multi processor support. Fixed frequency at 14.31818 MHz. (2.5 or 3.3 supply = VDDI)                                                           |  |  |  |  |  |  |

| 8, 10,<br>11, 13,<br>14, 16,<br>17               | PCI(1:7)        | VDDP | 0   | BUF4      | PCI bus clocks. See frequency select table on page 1.                                                                                                           |  |  |  |  |  |  |

| 7                                                | PCI_F           | VDDP | 0   | BUF4      | PCI clock that ceases only when PD (pin 29) is ascerted. See frequency select table on page 1.                                                                  |  |  |  |  |  |  |

| 3, 6,<br>12, 18,<br>20, 24,<br>32, 34,<br>38, 43 | vss             | -    | Р   | -         | Ground pins for the device.                                                                                                                                     |  |  |  |  |  |  |

| 46                                               | VDDI            | -    | Р   | -         | 3.3 or 2.5 Volt power supply pins for IOAPIC clock output buffers.                                                                                              |  |  |  |  |  |  |

| 9, 15                                            | VDDP            | -    | Р   | -         | 3.3 Volt power supply pins for PCI and PCI_F clock output buffers.                                                                                              |  |  |  |  |  |  |

| 21                                               | VDDF            | -    | Р   | -         | 3.3 Volt power supply pins for 48 MHz clock output buffers.                                                                                                     |  |  |  |  |  |  |

| 48                                               | VDDR            | -    | Р   |           | 3.3 Volt power supply pins for reference clock output buffers.                                                                                                  |  |  |  |  |  |  |

| 37, 41                                           | VDDC            | -    | Р   | -         | 3.3 or 2.5 Volt power supply pins for CPU clock output buffers.                                                                                                 |  |  |  |  |  |  |

| 19, 33                                           | VDD             |      |     |           | Power supply pins for analog circuits and core logic                                                                                                            |  |  |  |  |  |  |

| 1, 2, 47                                         | REF(1:3)        | VDDR | 0   | BUF3      | Buffered outputs of on-chip reference oscillator.                                                                                                               |  |  |  |  |  |  |

| 22, 23                                           | 48M(1:2)        | VDDF | 0   | BUF3      | Fixed 48 MHz frequency clock outputs.                                                                                                                           |  |  |  |  |  |  |

| 31                                               | PSTOP           | -    | ı   | PAD<br>PU | When driven to a logic low level, this pin will synchronously stop all PCI clocks (except PCI_F) at a logic low level.                                          |  |  |  |  |  |  |

| 30                                               | CSTOP           | -    | I   | PAD<br>PU | When driven to a logic low level, this pin will synchronously stop all CPU clocks at a logic low level.                                                         |  |  |  |  |  |  |

| 28                                               | #SSM            | -    | I   | PAD<br>PU | When driven to a logic low level this pin enables EMI reducing Spread Spectrum mode (affects only CPU and PCI clocks).                                          |  |  |  |  |  |  |

| 29                                               | PD              | -    | I   | PAD<br>PU | When this pin is driven to a logic low the IC will enter shutdown mode and <b>ALL</b> internal circuitry is turned off.                                         |  |  |  |  |  |  |

Approved Product

|              | Outputs |                                    |      |      |      |  |  |  |  |  |  |

|--------------|---------|------------------------------------|------|------|------|--|--|--|--|--|--|

| Descriptions | CPU     | CPU PCI, PCIF 48 MHz REF1:3 IOAPIC |      |      |      |  |  |  |  |  |  |

| Tri-State    | Hi-Z    | Hi-Z                               | Hi-Z | Hi-Z | Hi-Z |  |  |  |  |  |  |

| Test Mode    | TCLK/2  | TCLK/4 TCLK/2 TCLK TCLK            |      |      |      |  |  |  |  |  |  |

NOTE: TCLK is a test clock that is driven into the XTAL\_IN input during test mode.

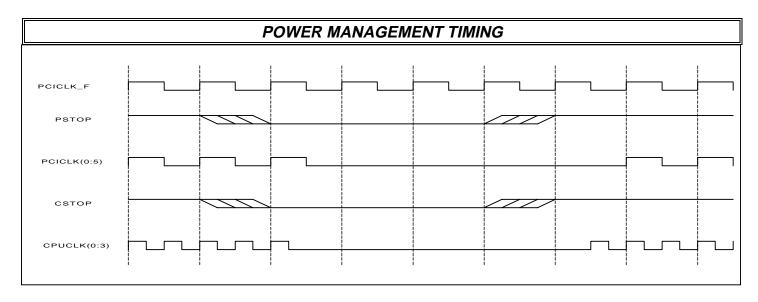

#### **POWER MANAGEMENT FUNCTIONS**

All PCI (excluding PCI\_F) and CPU clocks can be enabled or stopped via the PSTOP and CSTOP input pins. All clocks are stopped in the low state. All clocks maintain a valid high period on transitions from running to stopped and on transitions from stopped to running when the chip was not powered down. On power up, (after bring PD from a low to high state) the VCOs will stabilize to the correct pulse widths within about 0.2 mS. The CPU, and PCI clocks transition between running and stopped by waiting for one positive edge on PCI\_F followed by a negative edge on the clock of interest, after which high levels of the output are either enabled or disabled.

| CSTOP | PSTOP | PD | CPUCLK  | PCICLK  | OTHER CLKs | XTAL & VCOs |

|-------|-------|----|---------|---------|------------|-------------|

| X     | X     | 0  | LOW     | LOW     | LOW        | OFF         |

| 0     | 0     | 1  | LOW     | LOW     | RUNNING    | RUNNING     |

| 0     | 1     | 1  | LOW     | RUNNING | RUNNING    | RUNNING     |

| 1     | 0     | 1  | RUNNING | LOW     | RUNNING    | RUNNING     |

| 1     | 1     | 1  | RUNNING | RUNNING | RUNNING    | RUNNING     |

Approved Product

|        | Power Management Timing |                                                   |  |  |  |  |  |  |  |

|--------|-------------------------|---------------------------------------------------|--|--|--|--|--|--|--|

|        |                         |                                                   |  |  |  |  |  |  |  |

| Signal | Signal State            | No. of rising edges of free running PCICLK (PCIF) |  |  |  |  |  |  |  |

| CSTOP  | 0 (disabled)            | 1                                                 |  |  |  |  |  |  |  |

|        | 1 (enabled)             | 1                                                 |  |  |  |  |  |  |  |

| PSTOP  | 0 (disabled)            | 1                                                 |  |  |  |  |  |  |  |

|        | 1 (enabled)             | 1                                                 |  |  |  |  |  |  |  |

| PD     | 1 (normal operation)    | 3 mS                                              |  |  |  |  |  |  |  |

|        | 0 (power down)          | 2 mS max.                                         |  |  |  |  |  |  |  |

#### NOTES:

- 1. Clock on/off latency is defined in the number of rising edges of free running PCICLKs between the clock disable goes low/high to the first valid clock comes out of the device.

- 2. Power up latency is when PWR\_DWN# goes inactive (high) to when the first valid clocks are driven from the device.

Approved Product

|              | SPECTRUM SPREADING SELECTION TABLE             |       |    |                     |             |  |  |  |  |  |  |  |

|--------------|------------------------------------------------|-------|----|---------------------|-------------|--|--|--|--|--|--|--|

| Min<br>(MHz) |                                                |       |    |                     |             |  |  |  |  |  |  |  |

| 99.50        | 99.50 99.75 99.7 100 .5% (5% + 0%) Down Spread |       |    |                     |             |  |  |  |  |  |  |  |

| 65.4         | 66.4                                           | 67.39 | 66 | 1.25% (-1.25% + 0%) | Down Spread |  |  |  |  |  |  |  |

#### **MAXIMUM RATINGS**

Voltage Relative to VSS:

Voltage Relative to VDD:

Storage Temperature:

O°C to + 125°C

Operating Temperature:

Maximum Power Supply:

7V

This device contains circuitry to protect the inputs against damage due to high static voltages or electric field; however, precautions should be taken to avoid application of any voltage higher than the maximum rated voltages to this circuit. For proper operation, Vin and Vout should be constrained to the range:

VSS<(Vin or Vout)<VDD

Unused inputs must always be tied to an appropriate logic voltage level (either VSS or VDD).

|                                   | ELECTRICAL CHARACTERISTICS |         |               |           |             |                                                     |  |  |  |  |  |  |

|-----------------------------------|----------------------------|---------|---------------|-----------|-------------|-----------------------------------------------------|--|--|--|--|--|--|

| Characteristic                    | Symbol                     | Min     | Тур           | Max       | Units       | Conditions                                          |  |  |  |  |  |  |

| Input Low Voltage                 | VIL                        | -       | -             | 0.8       | Vdc         | -                                                   |  |  |  |  |  |  |

| Input High Voltage                | VIH                        | 2.0     | -             | -         | Vdc         | -                                                   |  |  |  |  |  |  |

| Input Low Current                 | IIL                        | -66     |               | -         | μA          |                                                     |  |  |  |  |  |  |

| Input High Current                | IIH                        |         |               | 5         | μA          |                                                     |  |  |  |  |  |  |

| Output Low Voltage<br>IOL = 4mA   | VOL                        | -       | -             | 0.4       | Vdc         | All Outputs (see buffer spec)                       |  |  |  |  |  |  |

| Output High Voltage<br>IOH = 4mA  | VOH                        | 2.4     | -             | -         | Vdc         | All Outputs Using 3.3V Power (see buffer spec)      |  |  |  |  |  |  |

| Tri-State leakage Current         | loz                        | -       | -             | 10        | μΑ          |                                                     |  |  |  |  |  |  |

| Dynamic Supply Current            | ldd                        | -       | -             | 175       | mA          | CPU = 66.6 MHz, PCI = 33.3 MHz                      |  |  |  |  |  |  |

| Static Supply Current             | Isdd                       | -       | -             | 75        | mA          | -                                                   |  |  |  |  |  |  |

| Crystal Oscillator<br>Capacitance | Сх                         | -       | 18            | -         | pF          | Xin and Xout crystal load capacitance values (each) |  |  |  |  |  |  |

| Short Circuit Current             | ISC                        | 25      | -             | -         | mA          | 1 output at a time - 30 seconds                     |  |  |  |  |  |  |

| VDD = VDDP=                       | =VDDF =VD                  | DDR =3. | <i>3V</i> ±5% | , VDDC, & | 2 VDDI =2.5 | iV±5%,, TA = 0°C to +70°C                           |  |  |  |  |  |  |

Approved Product

| SWITCHING CHARACTERISTICS                      |                                                                     |     |     |              |       |                                                                          |  |  |  |  |  |

|------------------------------------------------|---------------------------------------------------------------------|-----|-----|--------------|-------|--------------------------------------------------------------------------|--|--|--|--|--|

| Characteristic                                 | Symbol                                                              | Min | Тур | Max          | Units | Conditions                                                               |  |  |  |  |  |

| Output Duty Cycle                              | -                                                                   | 45  | 50  | 55           | %     | Measured at 1.5V                                                         |  |  |  |  |  |

| CPU to PCI Offset                              | tOFF                                                                | 1.5 | -   | 4            | ns    | CPU load = 20 pF, PCI load = 30 pF<br>measured at 1.5V PCI and 1.25V CPU |  |  |  |  |  |

| Buffer out Skew All CPU<br>Buffer Outputs      | tSKEW <sub>1</sub>                                                  | -   | -   | 175          | ps    | 20 pF Load Measured at 1.5V                                              |  |  |  |  |  |

| Buffer out Skew All PCI<br>Buffer Outputs      | tSKEW <sub>2</sub>                                                  | -   | -   | 250          | ps    | 30 pF Load Measured at 1.5V                                              |  |  |  |  |  |

| ΔPeriod Adjacent Cycles                        | ΔΡ                                                                  | -   | -   | <u>+</u> 250 | ps    | -                                                                        |  |  |  |  |  |

| Jitter Spectrum 20 dB<br>Bandwidth from Center | BWJ                                                                 |     |     | 500          | KHz   |                                                                          |  |  |  |  |  |

| VDD - VDDB                                     | VDD = VDDP=VDDP = 3.3V +5% VDDC & VDDL = 2.5V +5% TA = 00C to +700C |     |     |              |       |                                                                          |  |  |  |  |  |

$VDD = VDDP = VDDF = VDDR = 3.3V \pm 5\%$ , VDDC, &  $VDDI = 2.5V \pm 5\%$ ,  $TA = 0^{\circ}C$  to  $+70^{\circ}C$

| I                                                  | BUFFER 1 CHARACTERISTICS FOR CPUCLK(1:4) |     |   |     |    |                |  |  |  |  |  |

|----------------------------------------------------|------------------------------------------|-----|---|-----|----|----------------|--|--|--|--|--|

| Characteristic Symbol Min Typ Max Units Conditions |                                          |     |   |     |    |                |  |  |  |  |  |

| Pull-Up Current Min                                | IOH <sub>min</sub>                       | -27 | - | -   | mA | Vout = 1.0 V   |  |  |  |  |  |

| Pull-Up Current Max                                | IOH <sub>max</sub>                       | -   | - | -27 | mA | Vout = 2.375 V |  |  |  |  |  |

| Pull-Down Current Min                              | IOL <sub>min</sub>                       | 27  | - | -   | mA | Vout = 1.2 V   |  |  |  |  |  |

| Pull-Down Current Max                              | IOL <sub>max</sub>                       | -   | - | 30  | mA | Vout = 0.3 V   |  |  |  |  |  |

| Rise/Fall Time Min/Max<br>Between 0.4 V and 2.0 V  | TRF                                      | 0.4 | - | 1.6 | ns | 20 pF Load     |  |  |  |  |  |

$VDD = VDDP = VDDF = VDDR = 3.3V \pm 5\%$ , VDDC, &  $VDDI = 2.5V \pm 5\%$ , TA = 0% to +70%

Approved Product

| BUFFER 2 CHARACTERISTICS FOR IOAPIC (1:2)          |                    |     |   |     |    |              |  |  |  |  |

|----------------------------------------------------|--------------------|-----|---|-----|----|--------------|--|--|--|--|

| Characteristic Symbol Min Typ Max Units Conditions |                    |     |   |     |    |              |  |  |  |  |

| Pull-Up Current Min                                | IOH <sub>min</sub> | -36 | - | -   | mA | Vout = 1.4 V |  |  |  |  |

| Pull-Up Current Max                                | IOH <sub>max</sub> | -   | - | -21 | mA | Vout = 2.5 V |  |  |  |  |

| Pull-Down Current Min                              | IOL <sub>min</sub> | 36  | - | -   | mA | Vout = 1.0 V |  |  |  |  |

| Pull-Down Current Max                              | IOL <sub>max</sub> | -   | - | 31  | mA | Vout = 0.2 V |  |  |  |  |

| Rise/Fall Time Min/Max<br>Between 0.4 V and 2.0 V  | TRF <sub>max</sub> | 0.4 | - | 1.6 | nS | 20 pF Load   |  |  |  |  |

$VDD = VDDP = VDDF = VDDR = 3.3V \pm 5\%$ , VDDC, &  $VDDI = 2.5V \pm 5\%$ ,  $TA = 0^{\circ}C$  to  $+70^{\circ}C$

| BUFFE                                              | BUFFER 3 CHARACTERISTICS FOR REF(1:3) and 48(1:2) MHz |     |   |     |    |                |  |  |  |  |  |

|----------------------------------------------------|-------------------------------------------------------|-----|---|-----|----|----------------|--|--|--|--|--|

| Characteristic Symbol Min Typ Max Units Conditions |                                                       |     |   |     |    |                |  |  |  |  |  |

| Pull-Up Current Min                                | IOH <sub>min</sub>                                    | -29 | - | -   | mA | Vout = 1.0 V   |  |  |  |  |  |

| Pull-Up Current Max                                | IOH <sub>max</sub>                                    | -   | - | -23 | mA | Vout = 3.135 V |  |  |  |  |  |

| Pull-Down Current Min                              | IOL <sub>min</sub>                                    | 29  | - | -   | mA | Vout = 1.95 V  |  |  |  |  |  |

| Pull-Down Current Max                              | IOL <sub>max</sub>                                    | -   | - | 27  | mA | Vout = 0.4 V   |  |  |  |  |  |

| Rise/Fall Time Min/Max<br>Between 0.4 V and 2.4 V  | TRF                                                   | 0.5 | - | 2.0 | ns | 20 pF Load     |  |  |  |  |  |

$VDD = VDDP = VDDF = VDDR = 3.3V \pm 5\%$ , VDDC, &  $VDDI = 2.5V \pm 5\%$ , TA = 0°C to +70°C

| BUFFER 4 CHARACTERISTICS FOR PCICLK(1:8,F)         |                    |     |   |     |    |                |  |  |  |  |  |

|----------------------------------------------------|--------------------|-----|---|-----|----|----------------|--|--|--|--|--|

| Characteristic Symbol Min Typ Max Units Conditions |                    |     |   |     |    |                |  |  |  |  |  |

| Pull-Up Current Min                                | IOH <sub>min</sub> | -33 | - | -   | mA | Vout = 1.0 V   |  |  |  |  |  |

| Pull-Up Current Max                                | IOH <sub>max</sub> | -   | - | -33 | mA | Vout = 3.135 V |  |  |  |  |  |

| Pull-Down Current Min                              | IOL <sub>min</sub> | 30  | - | -   | mA | Vout = 1.95 V  |  |  |  |  |  |

| Pull-Down Current Max                              | IOL <sub>max</sub> | -   | - | 38  | mA | Vout = 0.4 V   |  |  |  |  |  |

| Rise/Fall Time Min/Max<br>Between 0.4 V and 2.4 V  | TRF                | 0.5 | - | 2.0 | ns | 30 pF Load     |  |  |  |  |  |

$VDD = VDDP = VDDF = VDDR = 3.3V \pm 5\%$ , VDDC, &  $VDDI = 2.5V \pm 5\%$ , TA = 0°C to +70°C

Approved Product

| CRYSTAL AND REFERENCE OSCILLATOR PARAMETERS |            |        |          |         |       |                                                             |  |  |  |

|---------------------------------------------|------------|--------|----------|---------|-------|-------------------------------------------------------------|--|--|--|

| Characteristic                              | Symbol     | Min    | Тур      | Max     | Units | Conditions                                                  |  |  |  |

| Frequency                                   | Fo         | 12.00  | 14.31818 | 16.00   | MHz   |                                                             |  |  |  |

| Tolerence                                   | TC         | -      | -        | +/-100  | PPM   | Calibration note 1                                          |  |  |  |

|                                             | TS         | -      | -        | +/- 100 | PPM   | Stability (Ta -10 to +60C) note 1                           |  |  |  |

|                                             | TA         | -      | -        | 5       | PPM   | Aging (first year @ 25C) note 1                             |  |  |  |

| Mode                                        | ОМ         | -      | -        | -       |       | Parallell Resonant                                          |  |  |  |

| Pin Capacitance                             | СР         |        | 5        |         | pF    | Capacitance of XIN and Xout pins                            |  |  |  |

| DC Bias Voltage                             | $V_{BIAS}$ | 0.3Vdd | Vdd/2    | 0.7Vdd  | V     |                                                             |  |  |  |

| Startup time                                | Ts         | -      | -        | 30      | μS    |                                                             |  |  |  |

| Load Capacitance                            | CL         | -      | 20       | -       | pF    | note 1                                                      |  |  |  |

| Effective Series resonant resistance        | R1         | -      | -        | 40      | Ohms  |                                                             |  |  |  |

| Power Dissipation                           | DL         | -      | -        | 0.10    | mW    | note 1                                                      |  |  |  |

| Shunt Capacitance                           | СО         | -      |          | 7       | pF    |                                                             |  |  |  |

| X1 and X2 Load                              | CL         |        | 17       |         | pF    | internal crystal loading gapacitors on each pin (to ground) |  |  |  |

For maximum accuracy, the total circuit loading capacitance should be equal to CL. This loading capacitance is the effective capacitance across the crystal pins and includes the device pin capacitance (CP) in parallel with any circuit traces, the clock generator and any onboard discrete load capacitors.

**Budgeting Calculations**

Typical trace capacitance, (< half inch) is 4 pF, Load to the crystal is therefore 2.0 pF Clock generator internal pin capacitance of 36 pF, Load to the crystal is therefore 18.0 pF

the total parasitic capacitance would therefore be = 20.0 pF.(matching CL)

Note 1: It is recommended but not mandatory that a crystal meets these specifications.

Approved Product

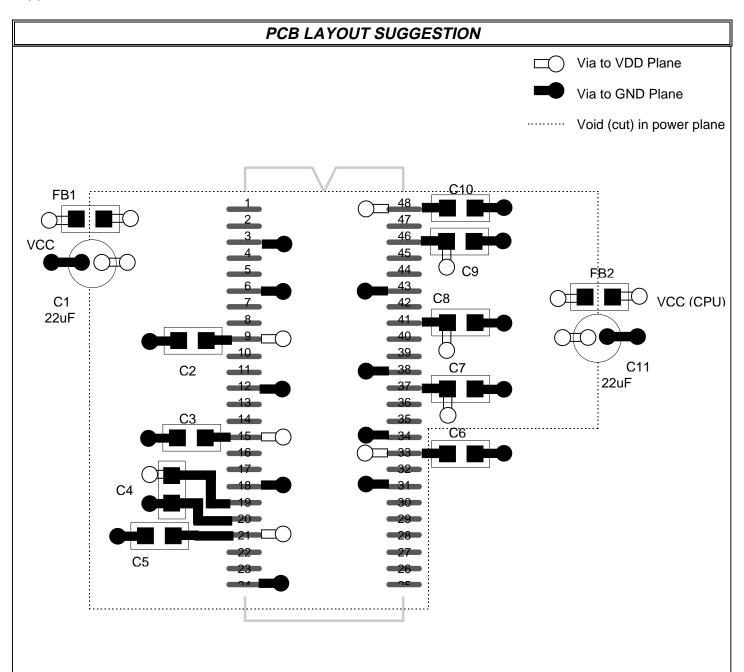

This is only a layout recommendation for best performance and lower EMI. the designer may choose a different approach but C2, C3, C4, C5, C6, C7, C8, C9, and C10 (all are 0.1 uf) should always be used and placed as close to their VDD pins as is physically possible. The topological hookup of C4 with respect to its power and ground vias is especially important.

Approved Product

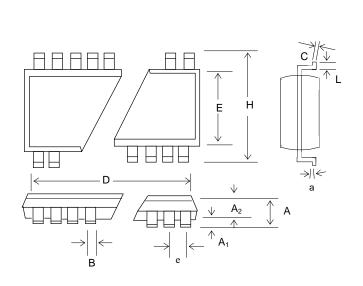

#### PACKAGE DRAWING AND DIMENSIONS

| 48 PIN SSOP OUTLINE DIMENSIONS |       |           |        |             |       |       |  |  |

|--------------------------------|-------|-----------|--------|-------------|-------|-------|--|--|

|                                |       | INCHES    |        | MILLIMETERS |       |       |  |  |

| SYMBOL                         | MIN   | NOM       | MAX    | MIN         | NOM   | MAX   |  |  |

| Α                              | 0.095 | 0.102     | 0.110  | 2.41        | 2.59  | 2.79  |  |  |

| A <sub>1</sub>                 | 0.008 | 0.012     | 0.016  | 0.20        | 0.31  | 0.41  |  |  |

| A2                             | 0.088 | 0.090     | 0.092  | 2.24        | 2.29  | 2.34  |  |  |

| В                              | 0.008 | 0.010     | 0.0135 | 0.203       | 0.254 | 0.343 |  |  |

| С                              | 0.005 | -         | 0.010  | 0.127       | -     | 0.254 |  |  |

| D                              | 0.620 | 0.625     | 0.630  | 15.75       | 15.88 | 16.00 |  |  |

| E                              | 0.292 | 0.296     | 0.299  | 7.42        | 7.52  | 7.59  |  |  |

| е                              |       | 0.025 BS0 | O      | 0.635 BSC   |       |       |  |  |

| Н                              | 0.400 | 0.406     | 0.410  | 10.16       | 10.31 | 10.41 |  |  |

| L                              | 0.024 | 0.032     | 0.040  | 0.61        | 0.81  | 1.02  |  |  |

| а                              | 00    | 5°        | 80     | 00          | 5°    | 80    |  |  |

| Х                              | 0.085 | 0.093     | 0.100  | 2.16        | 2.36  | 2.54  |  |  |

| ORDERING INFORMATION |              |                          |  |  |  |

|----------------------|--------------|--------------------------|--|--|--|

| Part Number          | Package Type | Production Flow          |  |  |  |

| IMISG577CYB          | 48 PIN SSOP  | Commercial, 0°C to +70°C |  |  |  |

<u>Note</u>: The ordering part number is formed by a combination of device number, device revision, package style, and screening as shown below.

Marking:

Example: IMI

SG577CYB

Date Code, Lot #

IMISG577CYB

\_ Flow

B = Commercial, 0°C to + 70°C

Package Y = SSOP

Revision

**IMI Device Number**