|     | REVISIONS                                                                              | <b>*</b>          |                       |

|-----|----------------------------------------------------------------------------------------|-------------------|-----------------------|

| LTR | DESCRIPTION                                                                            | DATE (YR-MO-DA)   | APPROVED              |

| A   | Table I: Correct limits, figure I: Correct case outline. Editorial changes throughout. | 92-02 <b>-</b> 21 | Monica L.<br>Poelking |

| В   | Changes in accordance with NOR 5962-R098-93                                            | 93-03-10          | Monica L.<br>Poelking |

| С   | Add device 02. Editorial changes throughout.                                           | 94-04-25          | Monica L.<br>Poelking |

## THE ORIGINAL FIRST PAGE OF THIS DRAWING HAS BEEN REPLACED

| REV                      | С                                                                                                      | С  | С                        | С                                   | С         | С    | С    | С  | С   | С                                                                                      | С     | С  | С   | C  |          |              |    | _        |    |    |

|--------------------------|--------------------------------------------------------------------------------------------------------|----|--------------------------|-------------------------------------|-----------|------|------|----|-----|----------------------------------------------------------------------------------------|-------|----|-----|----|----------|--------------|----|----------|----|----|

| SHEET                    | 35                                                                                                     | 36 | 37                       | 38                                  | 39        | 40   | 41   | 42 | 43  | 44                                                                                     | 45    | 46 | 47  | 48 |          |              |    |          |    |    |

| REV                      | С                                                                                                      | С  | С                        | С                                   | С         | С    | С    | С  | С   | С                                                                                      | С     | С  | С   | U  | С        | С            | С  | С        | С  | С  |

| SHEET                    | 15                                                                                                     | 16 | 17                       | 18                                  | 19        | 20   | 21   | 22 | 23  | 24                                                                                     | 25    | 26 | 27  | 28 | 29       | 30           | 31 | 32       | 33 | 34 |

| REV STATUS REV C C C     |                                                                                                        |    | С                        | С                                   | С         | С    | С    | С  | С   | С                                                                                      | С     | С  | С   | С  |          |              |    |          |    |    |

| OF SHEET                 | S                                                                                                      |    |                          | SH                                  | SHEET 1 2 |      |      | 3  | 4   | 5                                                                                      | 6     | 7  | 8   | 9  | 10       | 11           | 12 | 13       | 14 |    |

| PMIC N/A                 |                                                                                                        |    |                          | PREPARED BY<br>Christopher A. Rauch |           |      |      |    |     | Di                                                                                     | EFENS |    |     |    |          | PPLY<br>454  |    | rer<br>- |    |    |

| STANDARDIZED<br>MILITARY |                                                                                                        |    | CHECKED BY<br>Tim H. Noh |                                     |           |      |      |    |     |                                                                                        |       | •  |     |    |          | <del>,</del> |    |          |    |    |

| THIS DRAWIN              | DRAWING THIS DRAWING IS AVAILABLE FOR USE BY ALL DEPARTMENTS AND AGENCIES OF THE DEPARTMENT OF DEFENSE |    |                          | APPROVED BY<br>William K. Heckman   |           |      |      |    | 56- | MICROCIRCUIT, DIGITAL, CMOS,<br>56-BIT DIGITAL SIGNAL<br>PROCESSOR, MONOLITHIC SILICON |       |    |     |    |          |              |    |          |    |    |

|                          |                                                                                                        |    | Ē                        |                                     | ING AP    |      | DATE |    |     |                                                                                        | -     |    |     |    | ·        |              |    |          |    |    |

| AMSC N/A                 |                                                                                                        |    |                          | 28                                  | March     | 1990 |      |    |     | SIZE CAGE CODE 5962-8                                                                  |       |    |     |    | 895      | <b>L2</b>    |    |          |    |    |

| MMSC N/A                 | ľ                                                                                                      |    |                          | REVI                                | SION L    | EVEL | С    |    |     | A                                                                                      |       |    | 726 | 8  | <u> </u> |              |    |          |    |    |

|                          |                                                                                                        |    |                          |                                     |           |      |      |    |     | SHI                                                                                    | ĒΤ    |    | 1   |    | 0        | F            | 4  | 8        |    |    |

DESC FORM 193

JUL 91

<u>DISTRIBUTION STATEMENT A</u>. Approved for public release; distribution is unlimited.

5962-E472-93

9004708 0001261 671

### 1. SCOPE

Scope. This drawing describes device requirements for class B microcircuits in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices".

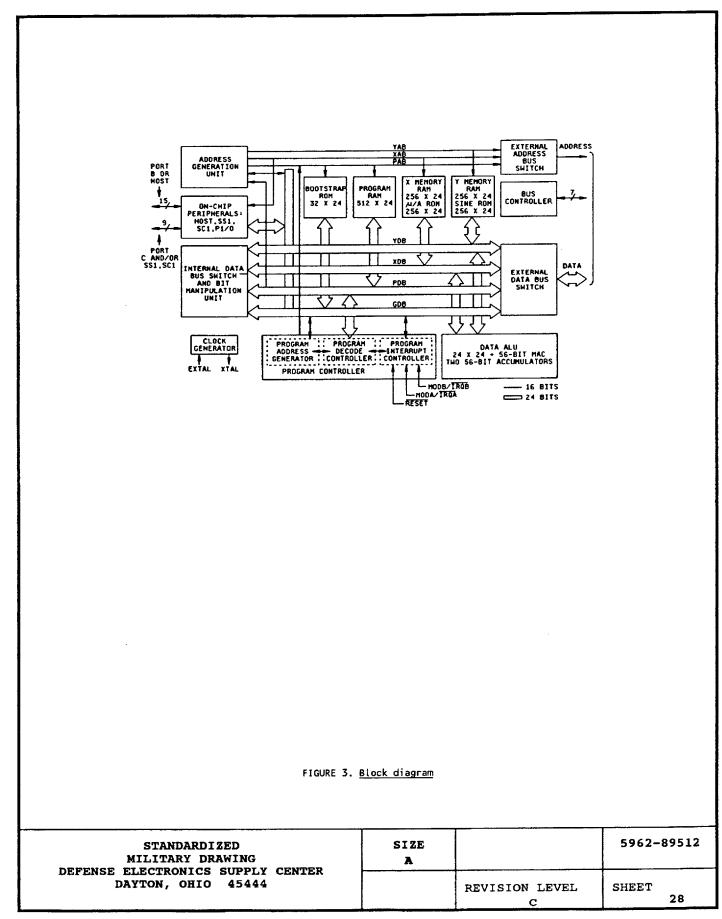

1.2 Part or Identifying Number (PIN). The complete PIN shall be as shown in the following example:

1.2.1 Device type(s). The device type(s) shall identify the circuit function as follows:

| Device type | Generic number | <u>Circuit function</u>    |

|-------------|----------------|----------------------------|

| 01          | 56001-20       | 56-bit general purpose DSP |

| 02          | 56001A-20      | 56-bit general purpose DSP |

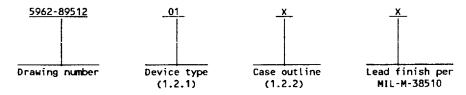

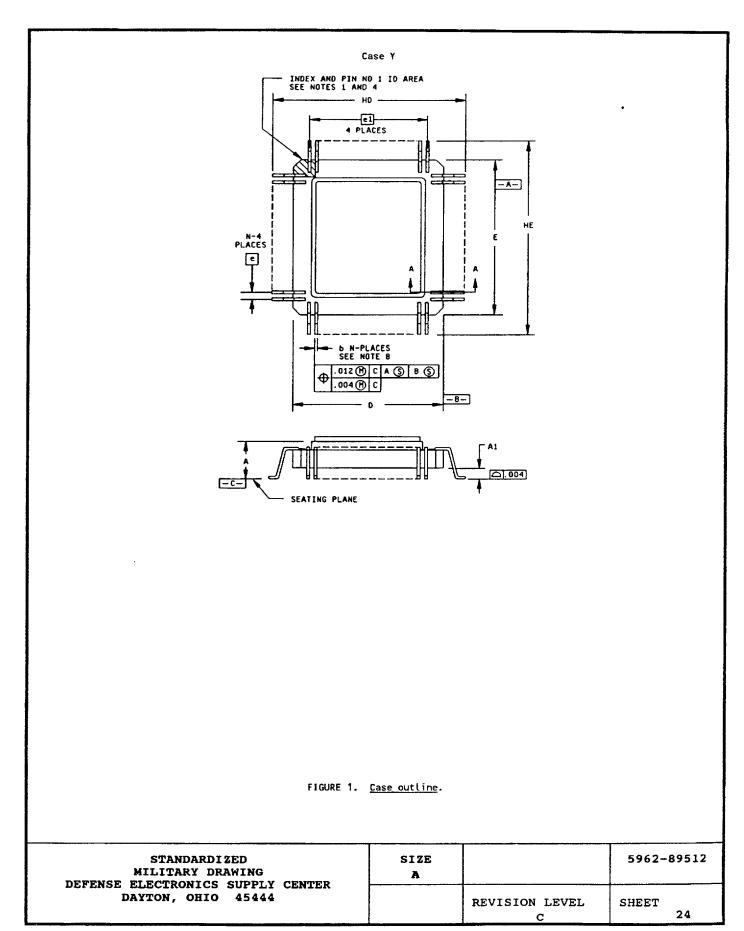

1.2.2 <u>Case outline(s)</u>. The case outline(s) shall be as designated in MIL-STD-1835 and as follows:

| Outline letter | Descriptive designator | <u>Terminals</u> | Package style       |

|----------------|------------------------|------------------|---------------------|

| X              | CMGA5-P88              | 88               | Pin grid array      |

| Y              | See figure 1           | 100              | Leaded chip carrier |

1.3 Absolute maximum ratings.

| Supply voltage range with respect to GND (V <sub>CC</sub> ) | -0.3 V dc to +7.0 V dc       |

|-------------------------------------------------------------|------------------------------|

| Input voltage (V <sub>IN</sub> )                            | -0.5 V dc to V <sub>cc</sub> |

| Storage temperature range                                   | -65°C to +150°Č              |

| Maximum power dissipation                                   |                              |

| device 01                                                   | 1.1 W                        |

| device 02                                                   | 0.63 W                       |

| Maximum operating temperature (T <sub>C</sub> )             | -55°C to +125°C              |

| Lead temperature (soldering, 5 seconds)                     | +270°C                       |

| Junction temperature (T <sub>j</sub> )                      | +150°C                       |

| Thermal resistance, junction-to-case $(\theta_{JC})$ :      |                              |

| Case X · · · · · · · · · · · · · · · · · ·                  | See MIL-STD-1835             |

| Case Y                                                      | 10°C/W                       |

1.4 Recommended operating conditions.

| Supply voltage (V <sub>CC</sub> ) device 01                                |                                                    |

|----------------------------------------------------------------------------|----------------------------------------------------|

| device 01                                                                  | 4.5 V dc to 5.5 V dc                               |

| device 02                                                                  | 4.75 V dc to 5.25 V dc                             |

| High level input voltage (V <sub>1H</sub> )                                | 2 V dc to V <sub>CC</sub><br>-0.5 V dc to 0.8 V dc |

| High level input voltage ( $V_{IH}$ ) Low level input voltage ( $V_{IL}$ ) | -0.5 V dc to 0.8 V dc                              |

| Minimum high level output voltage (V <sub>OH</sub> )                       | 2.4 V dc                                           |

| Maximum low level output voltage (V <sub>OI</sub> )                        | 0.8 V dc                                           |

| Frequency of operation                                                     | 4.0 to 20.5 MHz                                    |

| Case operating temperature                                                 | -55°C to +125°C                                    |

|                                                                            |                                                    |

1/ Must withstand the added P<sub>D</sub> due to short circuit test; e.g.,  $I_{OS}$ .

2/  $V_{I\perp} \le 0.2$  V dc,  $V_{IH} \ge V_{CC}$  - 2.0 V dc. No dc loads. EXTAL is driven by a square wave.

3/ In order to obtain these results all inputs must be terminated, i.e., not allowed to float.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE |                | 5962-89512 |

|-----------------------------------------------------------------|------|----------------|------------|

| DAYTON, OHIO 45444                                              |      | REVISION LEVEL | SHEET 2    |

DESC FORM 193A JUL 91

9004708 0001262 508 📟

#### 2. APPLICABLE DOCUMENTS

2.1 <u>Government specification, standard, and bulletin</u>. Unless otherwise specified, the following specification, standard, and bulletin of the issue listed in that issue of the Department of Defense Index of Specifications and Standards specified in the solicitation, form a part of this drawing to the extent specified herein.

SPECIFICATION

MILITARY

MIL-M-38510

- Microcircuits, General Specification for.

STANDARD

MILITARY

MIL-STD-883

Test Methods and Procedures for Microelectronics.

MIL-STD-1835

Microcircuit Case Outlines.

BULLETIN

MILITARY

MIL-BUL-103

- List of Standardized Military Drawings (SMD's).

(Copies of the specification, standard, and bulletin required by manufacturers in connection with specific acquisition functions should be obtained from the contracting activity or as directed by the contracting activity.)

2.2 <u>Order of precedence</u>. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing shall take precedence.

#### 3. REQUIREMENTS

- 3.1 <u>Item requirements</u>. The individual item requirements shall be in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices" and as specified herein.

- 3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-M-38510 and herein.

- 3.2.1 Case outline(s). The case outline(s) shall be in accordance with 1.2.2 herein and figure 1

- 3.2.2 <u>Terminal connections</u>. The terminal connections shall be as specified on figure 2.

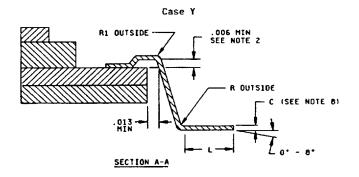

- 3.2.3 Block diagram. The block diagram shall be as specified on figure 3.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE 5962-89  REVISION LEVEL SHEET C 3 | 5962-89512          |            |

|-----------------------------------------------------------------|----------------------------------------|---------------------|------------|

| DAYTON, OHIO 45444                                              |                                        | REVISION LEVEL<br>C | SHEET<br>3 |

DESC FORM 193A JUL 91

**■ 9004708 0001263 444 ■**

- 3.3 <u>Electrical performance characteristics</u>. Unless otherwise specified herein, the electrical performance characteristics are as specified in table I and shall apply over the full case operating temperature range.

- 3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table II. The electrical tests for each subgroup are described in table I.

- 3.5 <u>Marking</u>. Marking shall be in accordance with MIL-STD-883 (see 3.1 herein). The part shall be marked with the PIN listed in 1.2 herein. In addition, the manufacturer's PIN may also be marked as listed in MIL-BUL-103 (see 6.6 herein).

- 3.6 <u>Certificate of compliance</u>. A certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-BUL-103 (see 6.6 herein). The certificate of compliance submitted to DESC-EC prior to listing as an approved source of supply shall affirm that the manufacturer's product meets the requirements of MIL-STD-883 (see 3.1 herein) and the requirements herein.

- 3.7 <u>Certificate of conformance</u>. A certificate of conformance as required in MIL-STD-883 (see 3.1 herein) shall be provided with each lot of microcircuits delivered to this drawing.

- 3.8 <u>Notification of change</u>. Notification of change to DESC-EC shall be required in accordance with MIL-STD-883 (see 3.1 herein).

- 3.9 <u>Verification and review</u>. DESC, DESC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

- 4. QUALITY ASSURANCE PROVISIONS

- 4.1 <u>Sampling and inspection</u>. Sampling and inspection procedures shall be in accordance with section 4 of MIL-M-38510 to the extent specified in MIL-STD-883 (see 3.1 herein).

- 4.2 <u>Screening</u>. Screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection. The following additional criteria shall apply:

- a. Burn-in test, method 1015 of MIL-STD-883.

- (1) Test condition D. The test circuit shall be maintained by the manufacturer under document revision level control and shall be made available to the preparing or acquiring activity upon request. The test circuit shall include the requirements for inputs, outputs, biases, and power dissapation, as applicable, in accordance with the specified purpose of method 1015.

- (2)  $T_A = +125$ °C, minimum.

- b. Interim and final electrical test parameters shall be as specified in table II herein, except interim electrical parameter tests prior to burn-in are optional at the discretion of the manufacturer.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-89512 |

|-----------------------------------------------------------------|-----------|---------------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>C | SHEET      |

| Test                                                     | Symbol            | Conditions $\underline{1}/$ -55°C $\leq$ T <sub>C</sub> $\leq$ +125°C unless otherwise specified | Group A<br>subgroups | Device | Lin<br>Min        | mits<br>  Max   | Unit     |

|----------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------|----------------------|--------|-------------------|-----------------|----------|

| Input high voltage<br>Except EXTAL, RESET,<br>MODA, MODB | v <sub>I H</sub>  |                                                                                                  | 1, 2, 3              | ALL    | 2.0               | v <sub>cc</sub> | v        |

| Input low voltage<br>Except EXTAL, MODA, MODB            | v <sub>IL</sub>   | <del>-</del><br> <br>                                                                            |                      |        | -0.5              | 0.8             |          |

| Input high voltage: EXTAL                                | VIHC              | †                                                                                                | -                    | 01     | V <sub>CC</sub> - | v <sub>CC</sub> |          |

|                                                          |                   |                                                                                                  |                      | 02     | 4.0               | V <sub>CC</sub> | Ī        |

| Input low voltage: EXTAL                                 | V                 | Ī                                                                                                | -                    | 01     | -0.5              | 0.4             |          |

| THE TOWN TOTAL BATTLE                                    | VILC              | 1                                                                                                |                      | 02     | -0.5              | 0.6             | <u> </u> |

| Input high voltage: RESET                                | V <sub>I HR</sub> |                                                                                                  |                      | ALL    | 2.5               | V <sub>CC</sub> |          |

| Input low voltage: RESET                                 | VILR              | İ                                                                                                | -                    | 01     |                   | 0.6             |          |

|                                                          | +                 | 1                                                                                                | -                    | 02     | -0.5              | 0.8             | -        |

| Input high voltage: MODA,<br>MODB                        | VIHM              |                                                                                                  |                      | ALL    | 3.5               | V <sub>CC</sub> |          |

| Input low voltage: MODA,                                 | VILM              | <u> </u><br>                                                                                     |                      | 01     | -0.5              | 0.6             | -        |

| MODB                                                     | I LM              |                                                                                                  |                      | 02     | -0.5              | 2.0             | -        |

|                                                          |                   | †                                                                                                | 1, 2, 3              | 01     | -1.0              | 1.0             | -        |

| Input leakage current:<br>EXTAL, RESET, MODA, MODB,      | IIN               |                                                                                                  | 1, 2                 | 02     | -1.0              | 1.0             | μΑ       |

| BR                                                       |                   |                                                                                                  | 3                    | 02     | -10               | -10             | =        |

| Three state input current                                | 1 TSI             | V <sub>IH</sub> = 2.4 V, V <sub>IL</sub> = 0.5 V                                                 | 1, 2, 3              | Ali    | -10               | 10              | -        |

| Output high voltage                                      | v <sub>ohc</sub>  | V <sub>CC</sub> = V <sub>CC</sub> min<br>I <sub>OH</sub> = -10 μA                                |                      | 01     | 4.3               |                 | v        |

| Output high voltage                                      | v <sub>OH</sub>   | V <sub>CC</sub> = V <sub>CC</sub> min<br>I <sub>OH</sub> = -400 μA                               |                      | All    | 2.4               |                 | •        |

| Output low voltage                                       | V <sub>OLC</sub>  | V <sub>CC</sub> = V <sub>CC</sub> min<br>I <sub>OL</sub> = -10 $\mu$ A                           |                      | 01     |                   | 0.1             | •        |

| see footnotes at end of tabl                             | •                 |                                                                                                  | ł                    |        |                   |                 | •        |

STANDARDIZED

MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

REVISION LEVEL

C

5962-89512

REVISION LEVEL

SHEET

C

DESC FORM 193A JUL 91

**9**004708 0001265 217 **m**

| Test                                                    | Symbol                                                                | Conditions<br>-55°C ≤ T <sub>C</sub> ≤ +1<br>unless otherwise s                        | 1/<br>25°C<br>pecified | Group A<br>subgroups                  | Device | <u>Lin</u><br>Min | mits<br>  Max | Unit         |

|---------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------|---------------------------------------|--------|-------------------|---------------|--------------|

| Output low voltage:<br>Except HREQ                      | v <sub>ol</sub>                                                       | V <sub>CC</sub> = V <sub>CC</sub> min<br>I <sub>OL</sub> = 1.6 mA                      |                        | 1, 2, 3                               | All    |                   | 0.4           | v            |

| Output low voltage: Open drain output HREQ              | V <sub>OLOD</sub>                                                     | V <sub>CC</sub> = V <sub>CC</sub> min<br>I <sub>OL</sub> = 6.7 mA                      |                        | 1                                     | 01     |                   | 0.8           | <u> </u>     |

| Total supply current                                    | I <sub>DD</sub>                                                       | V <sub>CC</sub> = V <sub>CC</sub> max<br>V <sub>DD</sub> = 5.0 V, f <sub>o</sub> = 20. | 5 MHz                  | †                                     | 01     |                   | 200           | mA.          |

| Total supply current: In WAIT mode 2/                   | I IDW                                                                 | V <sub>CC</sub> = V <sub>CC</sub> max                                                  |                        | †                                     | 01     |                   | 50            | <del> </del> |

| Total supply current: In                                | I <sub>DDS</sub>                                                      |                                                                                        |                        |                                       | 01     |                   | 10            |              |

| STOP mode <u>2</u> /                                    | DUS                                                                   |                                                                                        |                        |                                       | 02     | İ                 | 2             |              |

| Input capacitance                                       | CIN                                                                   | See 4.3.1c                                                                             |                        | 4                                     | All    |                   | 10            | pF           |

| Functional test                                         |                                                                       | See 4.3.1d                                                                             |                        | 7, 8                                  | All    |                   |               |              |

| Frequency of operation                                  | fo                                                                    | V <sub>CC</sub> = V <sub>CC</sub> min<br>EXTAL pin                                     |                        | 9,10,11                               | All    | 4.0               | 20.5          | MHz          |

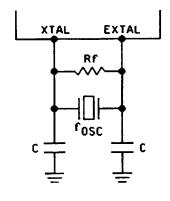

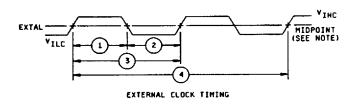

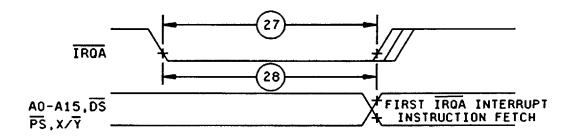

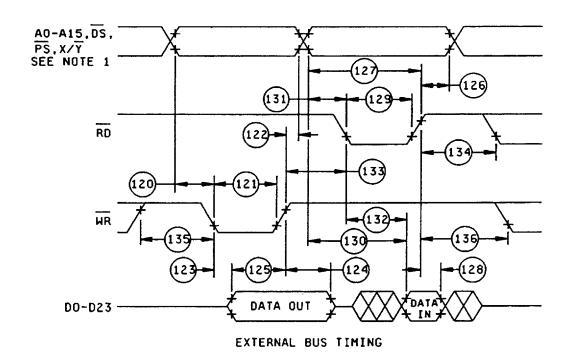

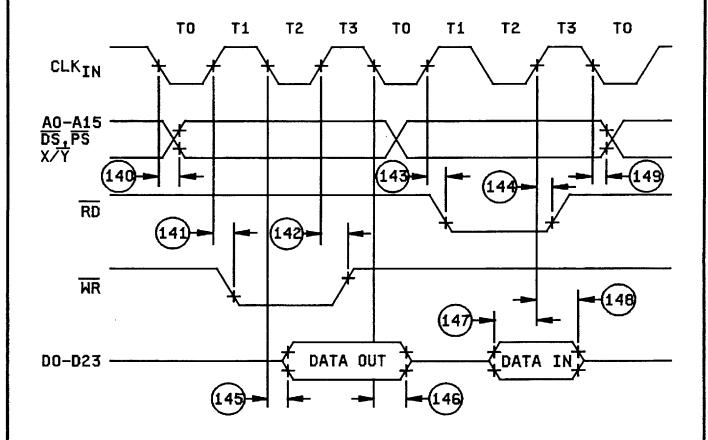

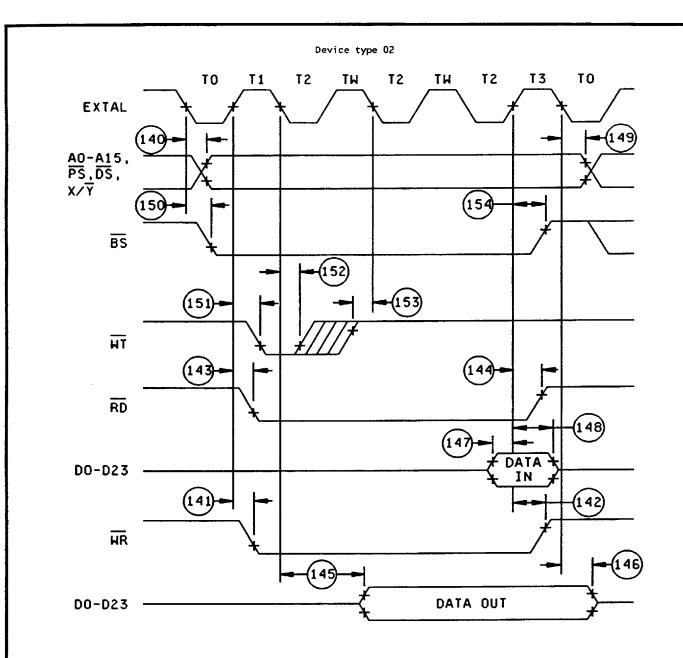

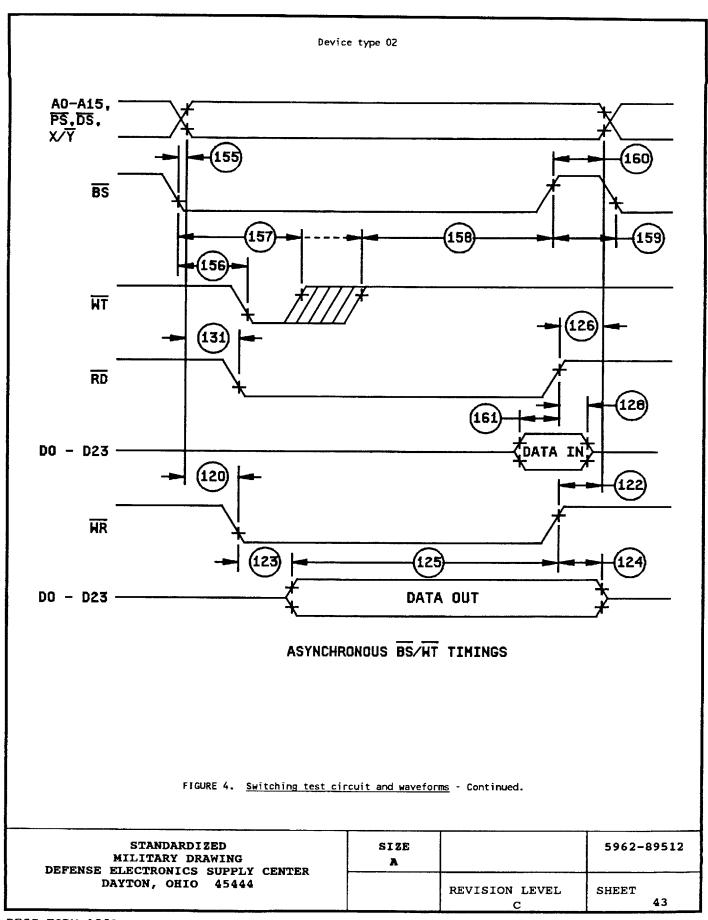

| External clock input high                               | 1                                                                     | EXTAL pin, see figur<br>external clock timi                                            |                        | †<br>                                 | All    | 22                | 150           | ns           |

| External clock input low                                | 2                                                                     | $V_{CC} = V_{CC} \min_{\underline{3}/\underline{4}/}$                                  |                        |                                       |        | 22                | 150           |              |

| Clock cycle time = 2T                                   | 3                                                                     | <br>  See figure 4<br>  external clock timin                                           | g <u>4</u> /           |                                       |        | 48.75             | 250           |              |

| Instruction cycle time<br>time = Icyc                   | 4                                                                     | V <sub>CC</sub> = V <sub>CC</sub> min                                                  |                        |                                       |        | 97.5              | 500           |              |

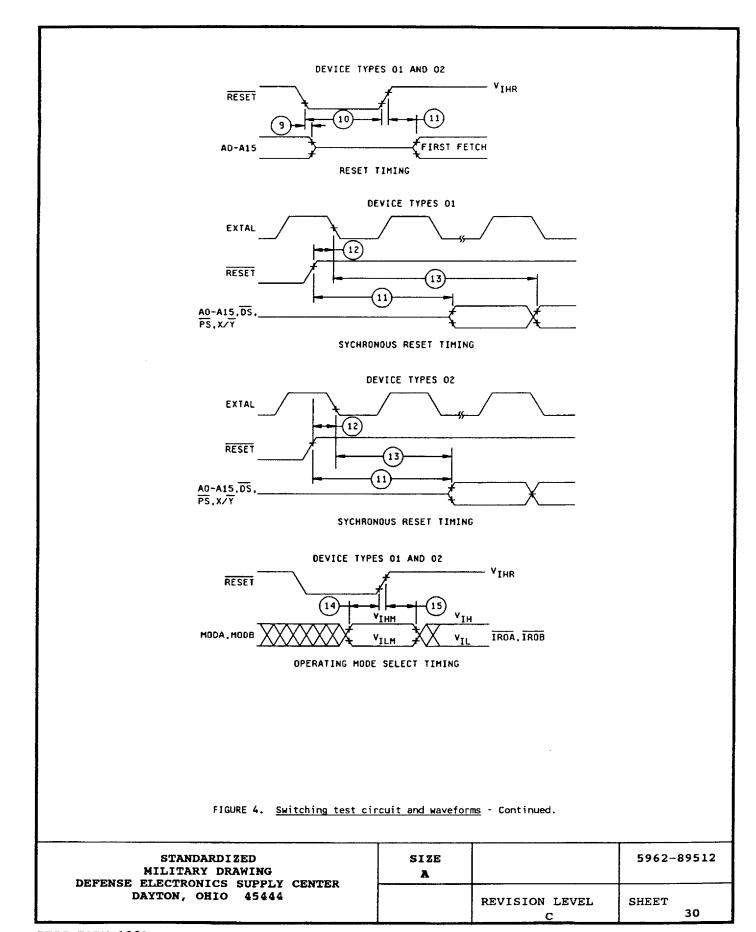

| Delay from RESET assertion<br>to address high impedance | 9                                                                     | See figure 4, reset<br>V <sub>CC</sub> = V <sub>CC</sub> min                           | timing                 | 9,10,11                               |        |                   | 50            | ns           |

| Minimum stabalization                                   | 10a                                                                   | See figure 4, reset<br> V <sub>CC</sub> = V <sub>CC</sub> min                          | timing <u>5</u> /      |                                       |        | <br> 15E4T<br>    |               |              |

|                                                         | 10b                                                                   | See figure 4, reset timing V <sub>CC</sub> = V <sub>CC</sub> min 6/                    |                        |                                       |        | 50т               |               |              |

| See footnotes at end of tabl                            | e.                                                                    |                                                                                        |                        | · · · · · · · · · · · · · · · · · · · |        | •                 |               | •            |

|                                                         | ARDIZEI                                                               |                                                                                        | SIZ                    | E                                     |        |                   |               | 5962-89      |

|                                                         | MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                                                                                        |                        | RI                                    | VISION | LEVEI             |               | SHEET        |

6

С

DESC FORM 193A JUL 91

| Test                                                                                                                                | Symbol                                                                                 | Conditions 1/                                                                      | Group A        |                    | Lim                 | Unit         |                                         |

|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|----------------|--------------------|---------------------|--------------|-----------------------------------------|

|                                                                                                                                     |                                                                                        | -55°C ≤ T <sub>C</sub> ≤ +125°C<br>unless otherwise specified                      | subgroups      | Device             | Min                 | Max          |                                         |

| Delay from asynchronous<br>RESET deassertion to<br>first external address<br>output (internal RESET<br>negation)                    | See figure 4, reset and synchronous reset timing V <sub>CC</sub> = V <sub>CC</sub> min | 9,10,11                                                                            | All            | 161                | 18T+<br>40          | ns           |                                         |

| Synchronous RESET setup<br>time from RESET<br>deassertion to falling<br>edge of external clock                                      | 12<br><u>7</u> /                                                                       | See figure 4, synchronous<br>reset timing<br>V <sub>CC</sub> = V <sub>CC</sub> min |                |                    | 20<br> <br>         | 2T<br>-10    | *************************************** |

| Synchronous RESET delay<br>time from the sync.<br>falling edge of ext.                                                              | 13                                                                                     |                                                                                    |                | 01                 | 16T+8               | 16T+<br>30   |                                         |

| clock to the first<br>external address output                                                                                       |                                                                                        |                                                                                    | <br> <br>      | 02                 | 16T+5<br><u>7</u> / | 16T+<br>30   |                                         |

| Mode select setup time                                                                                                              | 14                                                                                     | See figure 4, operating mode select timing                                         |                | All                | 100                 |              |                                         |

| Mode select hold time                                                                                                               | 15                                                                                     | V <sub>CC</sub> = V <sub>CC</sub> min                                              |                |                    | 0                   |              |                                         |

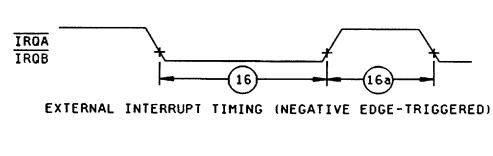

| Wi-i                                                                                                                                |                                                                                        | V <sub>CC</sub> = V <sub>CC</sub> min<br>See figure 4, external                    | Ţ.             | 01                 | 48                  | -            | Į                                       |

| Minimum edge-triggered<br>interrupt request width                                                                                   | 16                                                                                     | interrupt timing Assertion:                                                        |                | 02                 | 25                  |              |                                         |

|                                                                                                                                     | -                                                                                      | De-assertion:                                                                      | <del> </del> . | 01                 | 15<br>19T           | <del> </del> | †                                       |

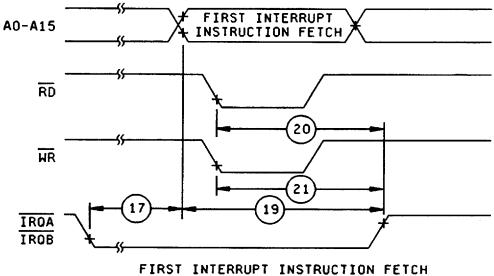

| Delay from IRQA,IRQB<br>assertion to external<br>memory access address                                                              | 17                                                                                     | See figure 4, external<br>level sensitive fast<br>interrupt timing                 |                |                    |                     |              |                                         |

| output valid caused by<br>first interrupt<br>instruction fetch                                                                      | <br>                                                                                   | V <sub>CC</sub> = V <sub>CC</sub> min Fetch:<br>  <u>8</u> /<br>  Ex:              |                | 02<br> <br>        | 11T<br>19T          |              |                                         |

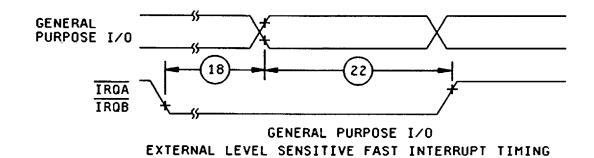

| Delay from IRQA, IRQB to<br>assertion to genpurpose<br>transfer output valid<br>caused by first interrupt<br>instruction execution. | 18                                                                                     | V <sub>CC</sub> = V <sub>CC</sub> min                                              | 9,10,11        | <br>  All<br> <br> | 231                 |              |                                         |

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-89512 |

|-----------------------------------------------------------------|-----------|---------------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>C | SHEET 7    |

DESC FORM 193A JUL 91

**--** 9004708 0001267 09T **--**

| Test                                                                                                                                                                            | Symbol            | Conditions 1/                                                                  | Group A   |        | Limits |                       | Uni |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------------------------------------------------------------------|-----------|--------|--------|-----------------------|-----|

|                                                                                                                                                                                 |                   | -55°C ≤ T <sub>C</sub> ≤ +125°C<br>unless otherwise specified                  | subgroups | Device | Min    | Max                   |     |

| Delay from address output valid caused by first interrupt instruction fetch to interrupt request deaasertion for level sensitive fast interrupts                                | 19                | See figure 4, external level sensitive fast interrupt timing  VCC = VCC min 8/ | 9,10,11   | All    |        | 5T+2T<br> *WS-<br> 44 | ns  |

| Delay from RD assertion to<br>interrupt request<br>deassertion for level<br>sensitive fast interrupts                                                                           | 20                |                                                                                |           |        |        | 4T+2T<br>*WS-<br>40   |     |

| Delay from WR assertion to<br>interrupt request<br>deassertion for level<br>sensitive fast interrupts<br>WS = 0                                                                 | 21a               |                                                                                |           |        |        | 4T<br>-40             |     |

| Delay from WR assertion to<br>interrupt request<br>deassertion for level<br>sensitive fast interrupts<br>WS > 0                                                                 | 216               |                                                                                |           |        |        | 31+21<br>*ws-<br>40   |     |

| Delay from general purpose<br>output valid to interrupt<br>request deassertion for<br>level sensitive fast<br>interrupts, If second<br>interrupt instruction is<br>single cycle | 22a               |                                                                                |           |        |        | T-60                  |     |

| Delay from general purpose<br>output valid to interrupt<br>request deassertion for<br>level sensitive fast<br>interrupts, if second<br>interrupt instruction is<br>two cycles   | 22b<br> <br> <br> |                                                                                |           |        |        | 5 <b>T</b><br>-60     |     |

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-89512 |

|-----------------------------------------------------------------|-----------|----------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET 8    |

DESC FORM 193A JUL 91

■ 9004708 0001268 T26 ■

| Test                                                                                                                     | Symbol | Conditions 1/                                                                                                                   | Group A   | }      | Lim                 | its                                          | Uni  |

|--------------------------------------------------------------------------------------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------|-----------|--------|---------------------|----------------------------------------------|------|

|                                                                                                                          |        | -55°C ≤ T <sub>C</sub> ≤ +125°C<br>unless otherwise specified                                                                   | subgroups | Device | Min                 | Max                                          |      |

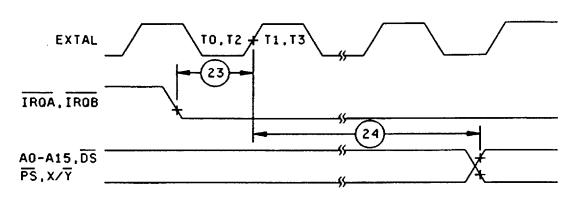

| Synchronous interrupt<br>set-up time from IRQA,<br>IRQB assertion to the<br>synchronous rising edge<br>of external clock | 23     | See figure 4, synchronous<br>interrupt from wait state<br>timing                                                                | 9,10,11   | All    | 25                  | 21-10                                        | ns   |

| Synchronous interrupt delay<br>time from the synchronous<br>rising edge of the<br>external clock to the                  | 24     | V <sub>CC</sub> = V <sub>CC</sub> min                                                                                           |           | 01     | 191+8               | 19т+30                                       |      |

| first external address<br>output valid caused by<br>the first instruction<br>fetch after coming out<br>of wait state     |        |                                                                                                                                 |           | 02     | 27T+8<br><u>7</u> / | 271+30                                       |      |

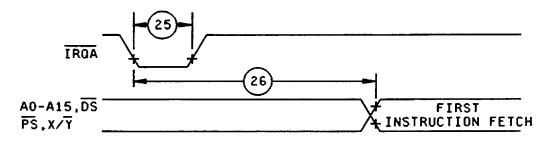

| Duration for IRQA assertion<br>to recover from STOP                                                                      | 25     | V <sub>CC</sub> = V <sub>CC</sub> min,<br>  See figure 4, recovery from<br>  stop state using IRQA                              |           | 01     | 19T+8               | 19T+30                                       | <br> |

| state                                                                                                                    |        | <u> </u>                                                                                                                        |           | 02     | 25                  | <u> i                                   </u> | ļ    |

| Delay from IRQA assertion<br>to fetch of first                                                                           | 26a    | V <sub>CC</sub> = V <sub>CC</sub> min, OMR bit 6 = 0<br>Stable external clock<br>see figure 4, recovery from                    |           | 01     | 128000T<br> +17T    |                                              |      |

| interrupt instruction                                                                                                    |        | stop state using IRQA                                                                                                           | •         | 02     | 1310901             |                                              | Ī    |

| Delay from IRQA assertion<br>to fetch of first                                                                           | 26b    | V <sub>CC</sub> = V <sub>CC</sub> min, OMR bit 6 = 1<br>Internal crystal oscillator<br>clock, see figure 4,                     |           | 01     | 150000T             |                                              |      |

| interrupt instruction                                                                                                    |        | recovery from stop state using IRQA                                                                                             | İ         | 02     | <b>3</b> 4T         |                                              |      |

| Duration of level sensitive IRQA assertion to fetch                                                                      | 27a    | V <sub>CC</sub> = V <sub>CC</sub> min, OMR bit 6 = 0<br>External clock<br>see figure 4, recovery from                           | 1         | 01     | 128000T<br>+17T     |                                              |      |

| of first interrupt instruction                                                                                           | j      | stop state and using IRQA interrupt service                                                                                     |           | 02     | 131067T             |                                              |      |

| Duration of level sensitive IRQA assertion to fetch                                                                      | 27b    | V <sub>CC</sub> = V <sub>CC</sub> min, OMR bit 6 = 1<br>Internal clock<br>see figure 4, recovery from                           |           | 01     | 150000т             |                                              | Ī    |

| of first interrupt                                                                                                       |        | stop state and using IRQA                                                                                                       |           | 02     | 111                 |                                              | †    |

|                                                                                                                          | 28a    | interrupt service<br> V <sub>CC</sub> = V <sub>CC</sub> min, OMR bit 6 = 0<br>  External clock<br>  see figure 4, recovery from | 1         | 01     | 128000T<br>+17T     |                                              | +    |

| of first interrupt                                                                                                       |        | stop state and using IRQA interrupt service                                                                                     | İ         | 02     | 131090T             |                                              | Ī    |

| Delay from level sensitive                                                                                               | 28b    | V <sub>CC</sub> = V <sub>CC</sub> min, OMR bit 6 = 1<br>Internal clock                                                          | †         | 01     | 150000Т             |                                              |      |

| IRQA assertion to fetch of first interrupt                                                                               |        | see figure 4, recovery from stop state and using IRQA                                                                           |           | 02     | 34T                 |                                              | †    |

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |                | 5962-89512 |

|------------------------------------------------------|-----------|----------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET<br>9 |

DESC FORM 193A JUL 91

**= 9004708 0001269 962**

| Test                                                               | Symbol Conditions 1/ | Group A                                                                                                      | į         |        | mits       | Unit |          |

|--------------------------------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------|-----------|--------|------------|------|----------|

|                                                                    | <br>                 | -55°C ≤ T <sub>C</sub> ≤ +125°C<br>unless otherwise specified                                                | subgroups | Device | Min        | Max  |          |

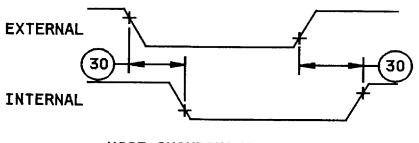

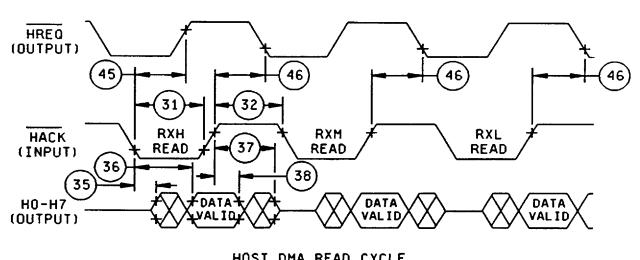

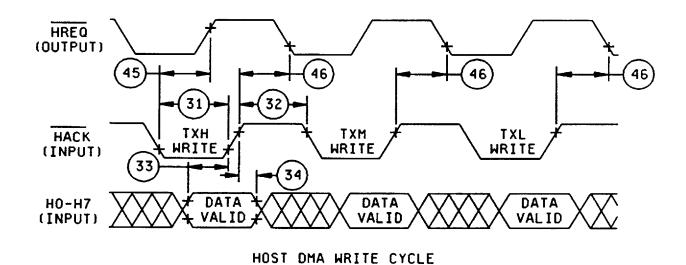

| Host synchronization delay                                         | 30                   | V <sub>CC</sub> = V <sub>CC</sub> min<br>See figure 4, host<br>synchronous delay                             | 9,10,11   | All    | Т          | 31   | ns       |

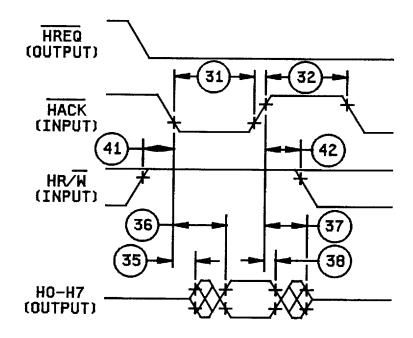

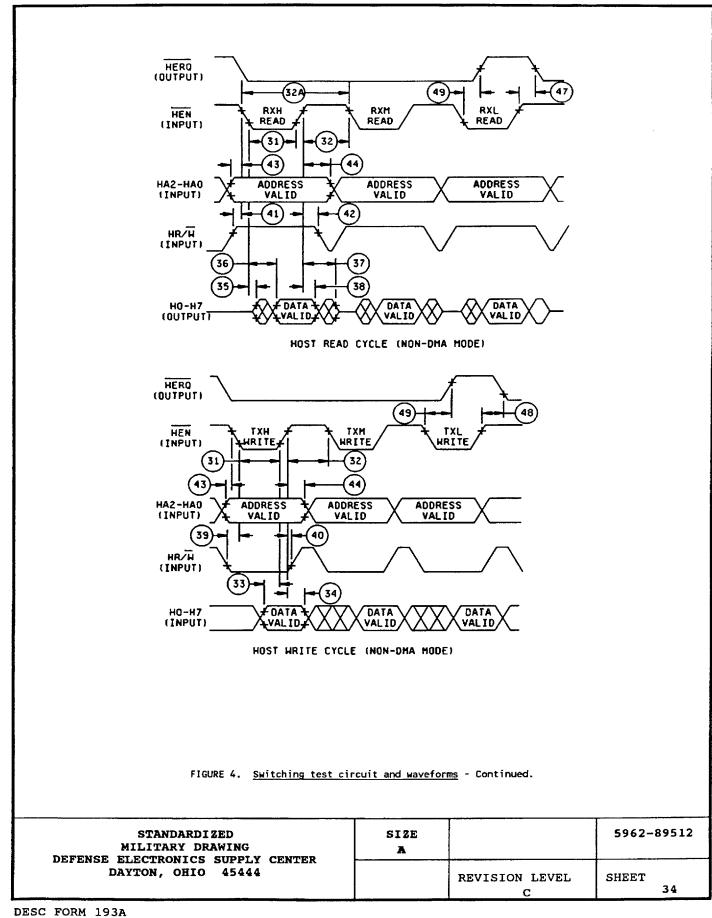

| HEN/HACK assertion width<br>(CVR, ICR, ISR Read)                   | 31                   | V <sub>CC</sub> = V <sub>CC</sub> min<br>See figure 4, host read<br>and write cycles                         |           | 02     | 21+60      |      |          |

| HEN/HACK assertion width<br>(read)                                 | 31a                  |                                                                                                              |           | All    | 50         |      |          |

| HEN/HACK assertion width<br>(write)                                | 31ь                  |                                                                                                              |           | All    | 25         |      |          |

| HEN/HACK deassertion width                                         | 32                   | †                                                                                                            |           | ALL    | 25         |      | Ţ        |

| Min cycle between two HEN                                          | <b>3</b> 2a          |                                                                                                              |           | 02     | 4T+60      |      |          |

| Host data input setup time<br>before HEN/HACK<br>deassertion       | 33                   | V <sub>CC</sub> = V <sub>CC</sub> min<br>  See figure 4, host write<br>  cycle and host DMA write<br>  cycle |           | All    | 5          |      |          |

| Host data input hold time<br>after HEN/HACK<br>deassertion         | 34                   |                                                                                                              |           |        | 5<br> <br> |      | <u> </u> |

| HEN/HACK assertion to<br>output data active from<br>high impedance | 35<br>               | See figure 4, host interrupt vector register (IVR) read, host read cycle and write cycle                     |           | 0      |            |      |          |

| HEN/HACK assertion to<br>output data valid                         | 36                   | V <sub>CC</sub> = V <sub>CC</sub> min                                                                        |           |        |            | 50   |          |

| HEN/HACK deassertion to<br>output data high<br>impedance           | 37                   |                                                                                                              |           |        |            | 35   |          |

| Output data hold time after<br>HEN/HACK deassertion                | 38                   |                                                                                                              |           |        | 5          |      |          |

| HR/W low setup time before HEN assertion                           | 39                   | See figure 4, host write cycle                                                                               |           |        | 0          |      |          |

| HR/W low hold time after<br>HEN deassertion                        | 40                   | V <sub>CC</sub> = V <sub>CC</sub> min                                                                        |           |        | 5          |      |          |

| HR/W high setup time to HEN assertion                              | 41                   | V <sub>CC</sub> = V <sub>CC</sub> min<br>See figure 4, host IVR read<br>and host read cycle                  |           |        | 0          |      |          |

| See footnotes at end of tabl                                       | e.                   |                                                                                                              |           |        | <b></b>    |      |          |

REVISION LEVEL

SHEET

10

DESC FORM 193A JUL 91

MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444

| Test                                                               | Symbol | Conditions $\underline{1}/$ -55°C $\leq$ T <sub>C</sub> $\leq$ +125°C unless otherwise specified | Group A<br>subgroups | Device | Li<br>Min       | mits<br>  Max | Unit |

|--------------------------------------------------------------------|--------|--------------------------------------------------------------------------------------------------|----------------------|--------|-----------------|---------------|------|

| HR/W high hold time after<br>HEN/HACK deassertion                  | 42     | V <sub>CC</sub> = V <sub>CC</sub> min<br>See figure 4, host IVR read<br>and host read cycle      | 9,10,11              | All    | 5               |               | ns   |

| HAO-HA2 setup time before<br>HEN assertion                         | 43     | V <sub>CC</sub> = V <sub>CC</sub> min<br>  See figure 4, host read<br>  cycle and write cycle    | 9,10                 | 01     | 2               |               | +    |

| HAO-HA2 setup time before<br>HEN assertion                         | 43     |                                                                                                  | 9,10,11              | 02     | 1               |               |      |

| HAO-HA2 hold time after HEN<br>deassertion                         | 44     |                                                                                                  | 9,10,11              |        | 5               |               |      |

| DMA HACK assertion to<br>HREQ deassrtion                           | 45     | V <sub>CC</sub> = V <sub>CC</sub> min<br>See figure 4, host DMA read<br>and write cycles         |                      | 01     | 5               | 30            |      |

|                                                                    |        | HREQ is pulled up by a                                                                           |                      | 02     | 5 7/            | 60            |      |

| DMA HACK deassertion to<br>HREQ assertion (for DMA<br>RXL read)    | 46a    | 1 kΩ resistor                                                                                    |                      | All    | tHSDL<br>+3T+5  |               |      |

| DMA HACK deassertion to<br>HREQ assertion (for DMA<br>TXL write)   | 46b    |                                                                                                  |                      | **     | tHSDL<br>+2T+5  |               |      |

| DMA HACK deassertion to<br>HREQ assertion (for all<br>other cases) | 46c    |                                                                                                  |                      |        | 5               |               |      |

| Delay from HEN deassertion<br>HREQ assertion for RXL<br>read       | 47     |                                                                                                  |                      |        | tHSDL<br> +3T+5 |               |      |

| Delay from HEN deassertion<br>to HREQ assertion for TXL<br>write   | 48     | <del> </del><br>                                                                                 |                      |        | tHSDL<br>+2T+5  |               |      |

STANDARDIZED

MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE 5962-89512

REVISION LEVEL SHEET

С

11

DESC FORM 193A JUL 91

■ 9004708 0001271 510 **■**

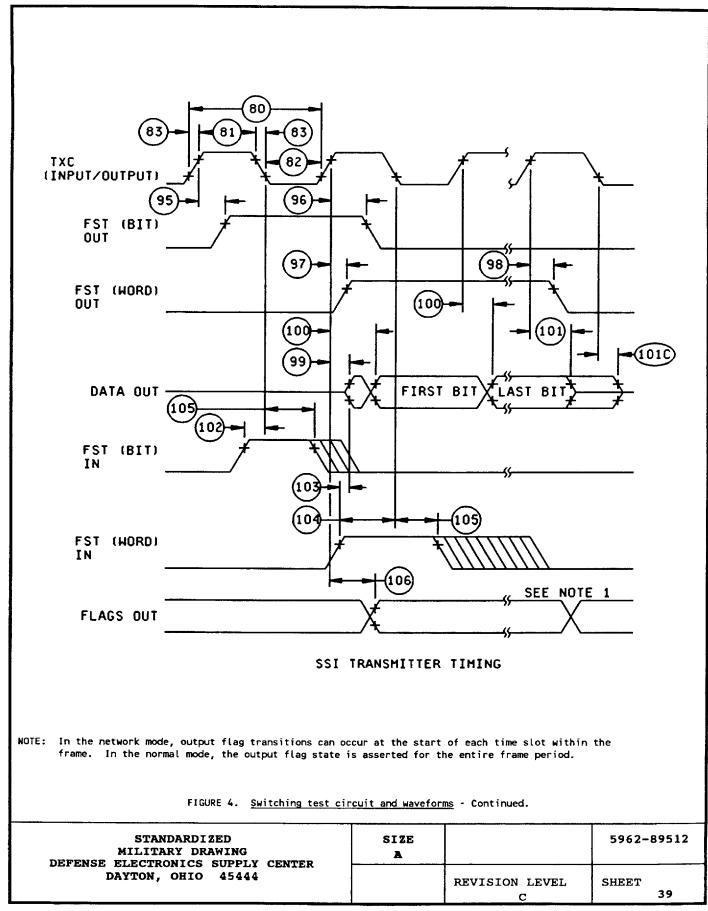

| Output data setup to clock falling edge (internal clock)  Output data hold after clock rising edge (internal clock)  Input data setup time before clock rising edge (internal clock)  Input data not valid before clock rising edge (internal clock)  Input data not valid before clock rising edge (internal clock)  Output data not valid before clock rising edge (internal clock)  Clock falling edge to output data valid (external clock)  Output data hold after clock output data hold after clock rising edge | Test                        | Symbol | Conditions $1/$ -55°C $\leq$ T <sub>C</sub> $\leq$ +125°C unless otherwise specified  | Group A<br>subgroups | Device           | Min   | Max   | Unit    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------|---------------------------------------------------------------------------------------|----------------------|------------------|-------|-------|---------|

| 107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | HREQ deassertion for RXL    | 49     | See figure 4, host read/<br>  write cycles<br>  HREQ is pulled up by a                | 9,10,11              | All              | 5     | 75    | ns      |

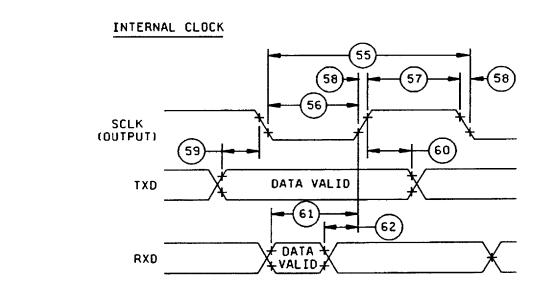

| Clock high period   57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                             | 55     | V <sub>CC</sub> = V <sub>CC</sub> min<br>See figure 4, SCI<br>synchronous mode timing |                      |                  | 161   |       |         |

| 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Clock low period            | 56     |                                                                                       |                      |                  |       |       |         |

| Dutput clock rise/fall time   58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Clock high period           | 57     |                                                                                       |                      | 01               |       |       | †       |

| Output data setup to clock falling edge (internal clock)  Output data hold after clock rising edge (internal clock)  Input data setup time 61                                                                                                                                                                                                                                                                                                                                                                          |                             |        |                                                                                       |                      | 02               | 16T/2 |       |         |

| falling edge (internal clock)  Output data hold after clock rising edge (internal clock)  Input data setup time 61                                                                                                                                                                                                                                                                                                                                                                                                     | Output clock rise/fall time | 58     |                                                                                       |                      | 01               |       | 20    |         |

| clock rising edge (internal clock)  Input data setup time before clock rising edge (internal clock)  Input data not valid before 62 clock rising edge (internal clock)  Clock falling edge to 63 output data valid (external clock)  Output data hold after clock rising edge  Output data hold after clock output data hold after clock rising edge                                                                                                                                                                   | falling edge (internal      | 59     |                                                                                       |                      | ALL              | ,     |       |         |

| before clock rising edge (internal clock)  Input data not valid before 62 clock rising edge (internal clock)  Clock falling edge to 63 output data valid (external clock)  Output data hold after 64 clock rising edge  Output data hold after 64 clock rising edge                                                                                                                                                                                                                                                    | clock rising edge           | 60     |                                                                                       |                      |                  |       |       |         |

| Input data not valid before 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | before clock rising         | 61     |                                                                                       |                      | <br> -<br> -<br> |       |       |         |

| clock rising edge (internal clock)  Clock falling edge to 63 output data valid (external clock)  Output data hold after 64 clock rising edge                                                                                                                                                                                                                                                                                                                                                                           | Input data not valid before | 62     | <del> </del><br>                                                                      |                      | 01               |       | •     | †       |

| Output data valid (external clock)  Output data hold after 64 clock rising edge                                                                                                                                                                                                                                                                                                                                                                                                                                        | clock rising edge           |        |                                                                                       |                      | 02               |       | 16T/4 |         |

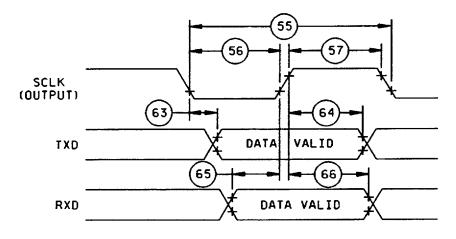

| clock rising edge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | output data valid           | 63     |                                                                                       |                      | ALL              |       | 63    | <u></u> |

| (external clock)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                             | 64     |                                                                                       |                      |                  | 21+12 |       |         |

SIZE

A

5962-89512

12

SHEET

REVISION LEVEL

DESC FORM 193A JUL 91

■ 9004708 0001272 457 **■**

STANDARDIZED MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444

| Test                                                                          | Symbol | Conditions 1/                                                                         | Group A   |        | Li                | imits | Unit     |

|-------------------------------------------------------------------------------|--------|---------------------------------------------------------------------------------------|-----------|--------|-------------------|-------|----------|

|                                                                               |        | -55°C ≤ T <sub>C</sub> ≤ +125°C<br>unless otherwise specified                         | subgroups | Device | Min               | Max   |          |

| Input data setup time<br>before clock rising edge<br>(external clock)         | 65     | V <sub>CC</sub> = V <sub>CC</sub> min<br>See figure 4, SCI<br>synchronous mode timing | 9,10,11   | All    | 30                |       | ns       |

| Input data hold time after<br>clock rising edge<br>(external clock)           | 66     |                                                                                       |           |        | 40                |       |          |

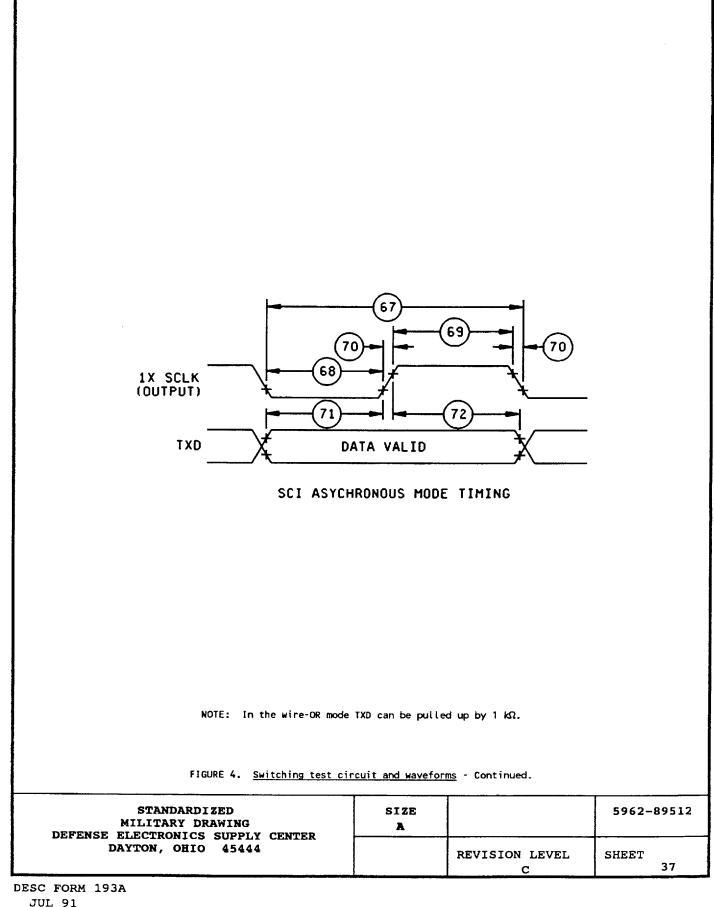

| Asynchronous clock cycle                                                      | 67     | See figure 4, SCI                                                                     |           | 01     | 128T/<br> 2-20    |       |          |

| 11/                                                                           |        | asychronous mode timing                                                               |           | 02     | 128T              |       | 1        |

| Clock low period 7/                                                           | 68     |                                                                                       |           | All    | 128T/<br>2-20     |       |          |

| Clock high period 7/                                                          | 69     |                                                                                       |           |        | 128T/<br> 2-20    |       | <u> </u> |

| Output clock rise/fall time                                                   | 70     |                                                                                       |           | 01     |                   | 20    |          |

| Output data setup to clock<br>rising edge (internal<br>clock)                 | 71     |                                                                                       |           | ALL    | 128T/<br>2-100    |       |          |

| Output data hold after<br>clock rising edge<br>(internal clock)               | 72     |                                                                                       |           |        | 128T/<br>2-100    |       |          |

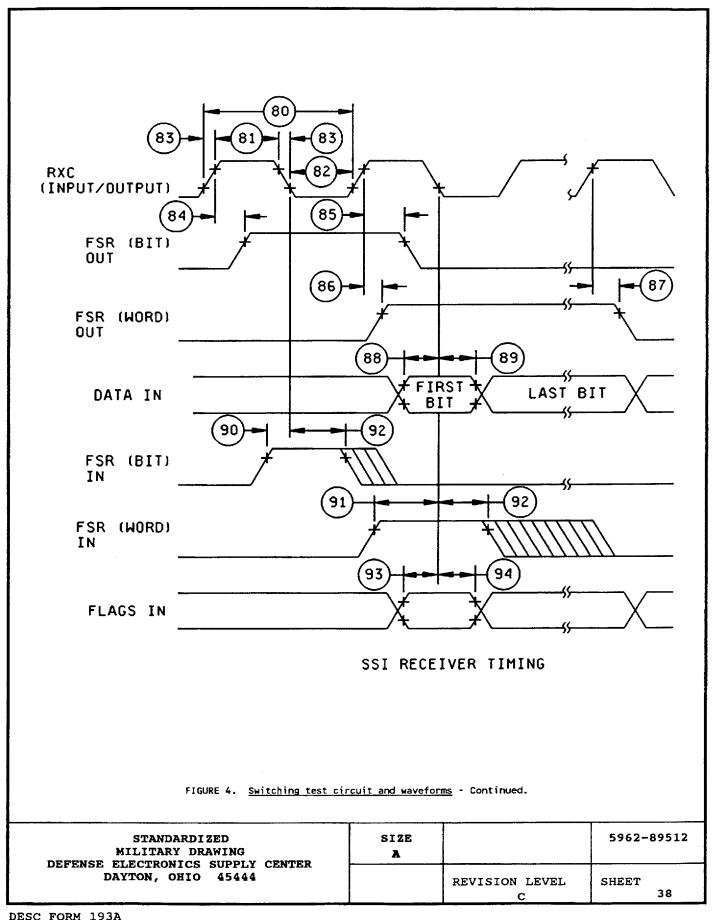

| Clock cycle <u>12</u> /                                                       | 80     | <br>  See figure 4, SSI receiver<br>  and transceiver timing                          |           | [<br>[ | 8T                |       |          |

| Clock high period                                                             | 81     |                                                                                       |           |        | 8T/2-<br>20       |       |          |

| Clock low period                                                              | 82     | V <sub>CC</sub> = V <sub>CC</sub> min                                                 |           |        | <br> 8T/2-<br> 20 |       |          |

| Output clock rise/fall time                                                   | 83     |                                                                                       |           | 01     |                   | 20    |          |

| RXC rising edge to FSR out<br>(bl) high. external<br>clock.                   | 84a    | See figure 4, SSI receiver timing <u>13</u> /                                         |           | All    |                   | 80    |          |

| RXC rising edge to FSR out<br>(bl) high. internal<br>clock, asynchronous mode | 84b    | V <sub>CC</sub> = V <sub>CC</sub> min                                                 |           |        |                   | 50    |          |

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-89512  |

|-----------------------------------------------------------------|-----------|----------------|-------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET<br>13 |

| Test                                                                                                                | Symbol      | Conditions 1/                                                       | Group A   |        | Li  | mits                     | _ Uni1 |

|---------------------------------------------------------------------------------------------------------------------|-------------|---------------------------------------------------------------------|-----------|--------|-----|--------------------------|--------|

|                                                                                                                     |             | -55°C ≤ T <sub>C</sub> ≤ +125°C<br>unless otherwise specified       | subgroups | Device | Min | Max                      |        |

| RXC rising edge to FSR out                                                                                          | 85a         | V <sub>CC</sub> = V <sub>CC</sub> min<br>See figure 4, SSI receiver | 9,10,11   | 01     |     | 80                       | ns     |

| (bl) low. external clock                                                                                            | <u> </u>    | timing                                                              | -         | 02     |     | 70                       | +      |

| RXC rising edge to FSR out (bl) low. internal clock asynchronous mode                                               | 85b         |                                                                     |           | All    |     | 40                       |        |

|                                                                                                                     |             | Ţ                                                                   |           | 01     |     | 80                       |        |

| RXC rising edge to FSR out (wl) high. external clock.                                                               | 86a         |                                                                     |           | 02     |     | 70                       | †      |

| RXC rising edge to FSR out (wl) high. internal clock, asynchronous mode                                             | 86b         |                                                                     |           | All    |     | 40                       |        |

|                                                                                                                     |             | †                                                                   | -         | 01     |     | 80                       | 1      |

| RXC rising edge to FSR out (wl) low. external clock.                                                                | 87a         |                                                                     |           | 02     |     | 70                       | 1      |

| RXC rising edge to FSR out<br>(wl) low. internal clock,<br>asynchronous mode.                                       | 87b         |                                                                     |           | All    |     | 40                       |        |

| Data in setup time before<br>RXC (SCK in synchronous<br>mode) falling edge.<br>external clock.                      | <b>88</b> a |                                                                     |           |        | 15  |                          |        |

| Data in setup time before<br>RXC (SCK in synchronous<br>mode) falling edge.<br>internal clock,<br>asynchronous mode | 88b         |                                                                     |           |        | 35  |                          |        |

| Data in setup time before<br>RXC (SCK in synchronous<br>mode) falling edge.<br>internal clock,<br>synchronous mode. | 88c         |                                                                     |           |        | 25  | <br> <br> <br> <br> <br> |        |

| Data in hold time after                                                                                             | 89a         |                                                                     |           | 01     | 33  | <br>                     | -      |

| RXC falling edge external clock                                                                                     | 070         |                                                                     |           | 02     | 35  |                          | 7      |

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |                     | 5962-89512 |

|------------------------------------------------------|-----------|---------------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL<br>C | SHEET      |

DESC FORM 193A JUL 91

■ 9004708 0001274 22T **■**

| Test                                                                                | Symbol | Conditions                                                               |                     | Group A  |        |          | nits | Unit                |

|-------------------------------------------------------------------------------------|--------|--------------------------------------------------------------------------|---------------------|----------|--------|----------|------|---------------------|

|                                                                                     |        | -55°C ≤ T <sub>C</sub> ≤ +17<br>unless otherwise sp                      | 25°C su<br>pecified | ubgroups | Device | Min      | Max  |                     |

| Data in hold time after<br>RXC falling edge<br>internal clock                       | 89b    | V <sub>CC</sub> = V <sub>CC</sub> min<br>See figure 4, SSI red<br>timing | ceiver 5            | 9,10,11  | ALL    | 5        |      | ns<br>  ns<br>      |

| FSR input (bl) high before<br>RXC falling edge<br>external clock. <u>13</u> /       | 90a    |                                                                          |                     |          |        | 15       |      | <br> <br> <br> <br> |

| FSR input (bl) high before RXC falling edge internal clock, asynchronous mode. 13/  | 90Ь    |                                                                          |                     |          |        | 35       |      |                     |