## Am8150

Display Refresh Controller

#### DISTINCTIVE CHARACTERISTICS

- Address controller in bit-mapped graphics systems

- Performs video refresh, memory arbitration, dynamic RAM control, and dynamic RAM refresh functions

- 18-bit address supports 16K x 1, 16K x 4, 64K x 1, and 64K x 4 RAMs

- Supports pan and scroll

- Programmable priority of Graphics Processor (GP) access to display memory

#### **GENERAL DESCRIPTION**

The Am8150 Display Refresh Controller (DRC) generates the addresses into the display RAM necessary to provide the video refresh function. It also provides the address interface between a bit-mapped display buffer and the Graphics Processor (GP) which updates the buffer. It acts as a memory access arbiter (permitting CPU access to the display memory at user-defined times), a video refresh controller, and a dynamic RAM refresh controller. It provides the signals (RAS, CAS, and video latch enable) and the timing necessary to cycle the dynamic RAMs and latch the video word in either random access or page mode.

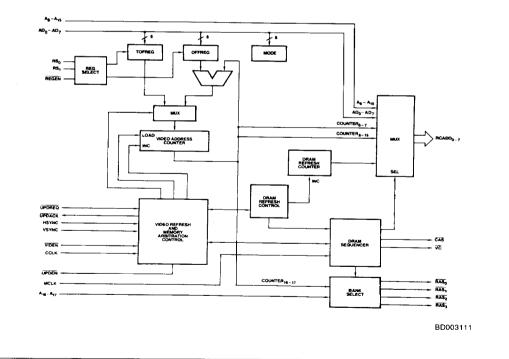

The DRC provides the GP with an 18-bit address path to the bit map. Referring to the block diagram, the 8-bit

multiplexer chooses the row or column address bits for the dynamic RAM. The inputs to this multiplexer are the address supplied by the GP, the Video Address Counter (VAC), and the dynamic RAM refresh counter. The two high-order bits of the address (from the GP or the video refresh counter) control a bank select decoder which activates one of four RAS lines. Each RAS line drives a separate bank of dynamic RAMs.

The DRC contains four write-only 8-bit registers which are programmed by the host. These contain the Top of Frame Address, the Offset, and the operating modes.

### BLOCK DIAGRAM

Order#04478C

#### RELATED PRODUCTS

| Part No. | Description             |  |

|----------|-------------------------|--|

| Am8151   | Graphics Color Palette  |  |

| Am8157   | Video Shift Register    |  |

| Am8158   | Video Timing Controller |  |

| Am8177   | Video Data Serializer   |  |

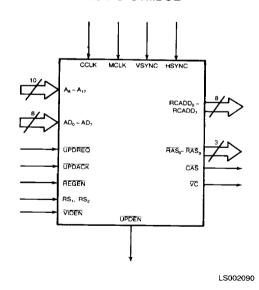

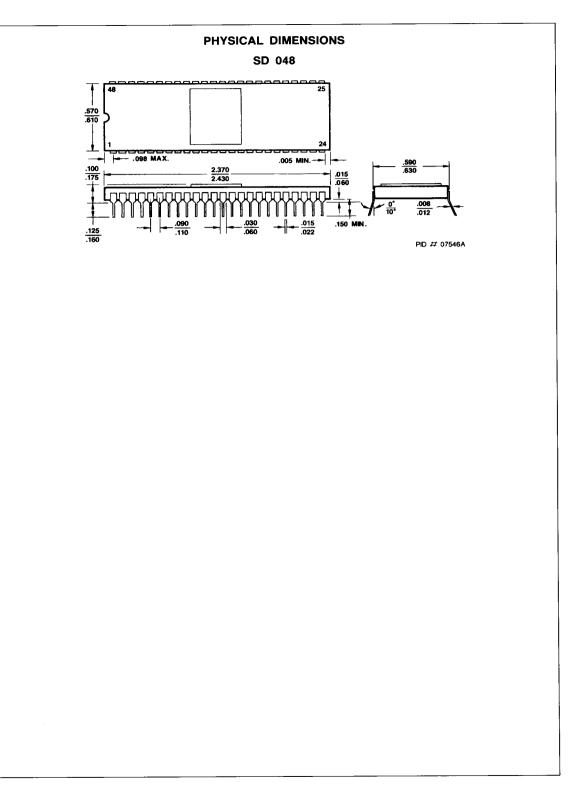

#### **CONNECTION DIAGRAM**

Note: Pin 1 is marked for orientation.

#### LOGIC SYMBOL

V<sub>CC</sub> = Positive Power Supply GND = Ground

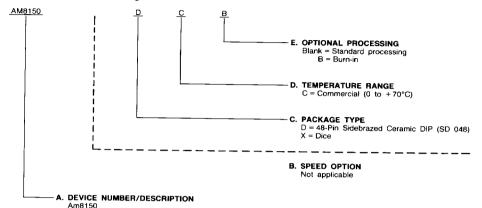

#### ORDERING INFORMATION

#### Standard Products

AMD products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: **A. Device Number**

B. Speed Option (if applicable)

C. Package Type

Display Refresh Controller

D. Temperature Range E. Optional Processing

## Valid Combinations AM8150 DC, DCB, XC

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released valid combinations, and to obtain additional data on AMD's standard military grade products.

#### PIN DESCRIPTION

#### AD<sub>0</sub> - AD<sub>7</sub> Address/Data (Inputs (8))

When loading the 8-bit registers, data is taken from  $AD_0 - AD_7$ . These eight lines are also the low order bits of the address bus (see description of  $A_8 - A_{17}$  below).

#### A<sub>8</sub> - A<sub>17</sub> Address (Inputs (10))

These ten inputs are concatenated with  $AD_0 - AD_7$  to make up the 18 address lines used by the graphics processor to access the display RAM.  $A_{17}$  is the most significant bit (MSB) and  $AD_0$  is the least significant bit (LSB).

$A_{16}$  and  $A_{17}$  are decoded to drive one of the four  $\overline{RAS}$  signals.  $A_{B}$  through  $A_{15}$  provide the row address.  $AD_{0}$  through  $AD_{7}$  provide the column address. When using  $16K\times 4$  RAMs,  $AD_{1}$  through  $AD_{6}$  provide column address ( $AD_{0}$  and  $AD_{7}$  are "'Don't Cares'' in this case).

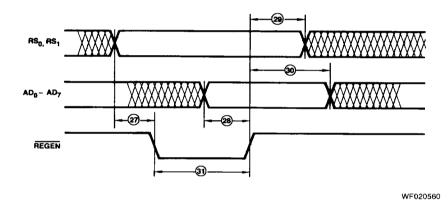

#### RS<sub>0</sub>, RS<sub>1</sub> Register Select (Inputs (2))

These two inputs are decoded to select one of the four 8-bit registers to be loaded with the data on  $AD_0 - AD_7$ . The register is latched on the LOW-to-HIGH transition of REGEN. See Am8150 Register Set.

#### REGEN Register Enable (Input)

The input data on  $AD_0 - AD_7$  is latched into one of the four internal registers on the LOW-to-HIGH transition of REGEN. The register to be loaded is selected with RS<sub>0</sub>, RS<sub>1</sub>.

#### UPDREQ Update Request (Input)

This input signals a request from the GP to access the display RAM (either for a read or write). The DRC recognizeds UPDREQ on the next positive transition of MCLK provided the set-up time (AC Parameter 1) is met.

## UPDACK Update Acknowledge (Output, Open Collector)

This output signal is the handshaking signal which indicates that the current display RAM access has NOT been completed and that the GP must wait. This signal goes active (LOW) following UPDREQ and stays active until the cycle has gone to completion. In the case of a write, the address and data should remain valid until UPDACK goes inactive

#### UPDEN Update Enable (Output)

UPDEN is active except during video and dynamic RAM refresh cycles. It identifies when a cycle can be granted to the GP. UPDEN should be used to gate the write enable signal(s) to the display memory so that writes occur only when the GP is actually given access. In the case where the data-in and data-out pins on the RAMs are connected together, this signal should also be used to gate the data into the array for a write.

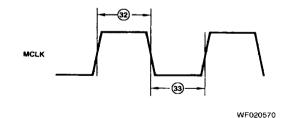

#### MCLK Master Clock (Input)

This clock is used to generate the timing relationships among  $\overline{RAS}$ ,  $\overline{CAS}$ , and the Row/Column multiplexer se-

lects. The frequency is dependent upon the time specifications for the dynamic RAM being used. See the section on CCLK and MCLK Considerations.

#### CCLK Character Clock (Input)

CCLK determines the rate at which RAM cycles for video refresh are executed. CCLK may be taken directly from the CCLK output of the Am8158 Video Timing Controller. The CCLK period will be the pixel period times the width (in pixels) of the display RAM word.

# RCADD<sub>0</sub> - RCADD<sub>7</sub> Row/Column Address (Outputs (8)) These outputs are the multiplexed row and column addresses which are sent to the dynamic RAMs. These are standard TTL outputs and will have to be buffered to drive a display memory

of more than about sixteen dynamic RAMs.

RAS<sub>0</sub> - RAS<sub>3</sub> Row Address Strobe (Outputs (4))

RAS strobes the row address into one of up to four banks of

RAM in the display memory. It is also used to strobe the refresh address during a dynamic RAM refresh cycle. Depending on the array size, these signals may need to be buffered.

#### CAS Column Address Strobe (Output)

CAS strobes the column address into all of the dynamic RAMs in the display memory. All of the banks of memory receive the same CAS signal. This signal may need to be buffered.

#### VC Video Cycle (Output)

This is used externally to latch the parallel video output from the display RAMs. It may be used directly to drive the VLE input on the Am8157 Video Shift Register(s).

#### HSYNC Horizontal Synchronization (Input)

This input causes the DRC to add the contents of the Offset Register to the Video Address Counter, thereby advancing to the first word of the next scan line. It also causes the DRC to execute the dynamic RAM refresh cycles as programmed in the Mode Register. HSYNC may be taken directly from the HSYNC output of the Am8158 VTC.

#### VSYNC Vertical Synchronization (Input)

This input causes the Video Address Counter to be loaded with the contents of the Top of Frame (TOF) Register. During vertical blank, HSYNC pulses are prevented from causing the offset to be added to the Video Address Counter.

#### VIDEN Video Enable (Input)

VIDEN is active (LOW) during the active video time (that is, whenever horizontal blank and vertical blank are both inactive). VIDEN is used in the arbitration logic.

V<sub>CC</sub> TTL Positive Power Supply

GND Ground

#### **FUNCTIONAL DESCRIPTION**

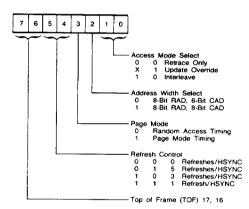

#### Register Set

The DRC has four 8-bit registers which must be loaded by the host. The registers are loaded by placing the desired data on  $AD_0-AD_7$ , placing the register address on  $RS_1,\ RS_0$  and strobing the data into the register using  $\overline{REGEN}$ . The data is loaded into the register on the LOW-to-HIGH transition of  $\overline{REGEN}$  (see timing diagram "Loading Registers"). The Offset Register must be loaded first, then the Mode Register. The Top of Frame Registers may be loaded at any time but are normally changed only during vertical blank.

| RS <sub>1</sub> | RS <sub>0</sub> | Register Name                                   |  |

|-----------------|-----------------|-------------------------------------------------|--|

| 0               | 0               | Top of Frame (TOF)<br>Low<br>Top of Frame (TOF) |  |

| 0               | 1               | High                                            |  |

| 1               | 0               | Offset                                          |  |

| 1               | 1               | Mode                                            |  |

The Top of Frame Registers are concatenated to specify the address of the first word in the video buffer to be displayed on the screen (that is, the word which is to appear at the upper

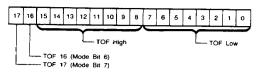

left corner of the screen). The 18-bit address is made up as indicated below:

TB000150

See the sections on Display Refresh and Scrolling and Panning for further information on the programming of the Top Of Frame Registers, but remember that this is a word address, not a pixel address.

The Offset Register is used to treat the case where the width of the display memory is not the same as the width of the screen (the display memory is wider to allow panning). At each HSYNC time, the contents of the Offset Register are added to the contents of the Video Address Counter which forces the display from the last word of the current line to the first word of the next line. See the section on Display Refresh for further information on the use of the Offset Register. Loading the Offset Register forces a hardware reset in the DRC and will

The Mode Register specifies the operating modes. The eight bits in this register are defined as follows:

abort any memory cycle in progress. For this reason, the

Offset Register must be loaded first.

TB000160

#### Display Refresh

A primary function of the DRC is to generate the addresses into the display RAM necessary to refresh the display. It does so with an 18-bit counter whose contents can be modified in three ways. The counter is called the Video Address Counter (VAC).

It is important to keep in mind that the addresses generated in the DRC are word and not pixel addresses. The word width is the number of pixels which are loaded into the shift register for each CCLK cycle.

When the DRC sees VSYNC, the VAC is loaded from the Top of Frame Registers. When the accesses begin for the first scan line, they will begin with the address contained in the Top of Frame Registers. Thus, the word whose address is contained in the Top of Frame Registers will appear at the upper left of the screen. If the screen size is the same as the display

size, the Top of Frame Registers should be programmed to zero.

Once VIDEN has gone active (indicating active video), the DRC will access one word during each CCLK cycle (or every other CCLK cycle in the case of interleaved operation). It will also increment the VAC once for each video word it has accessed. Thus, video words are fetched in order and presented to the Am8157 VSR(s) for serialization. This procedure continues until VIDEN becomes inactive, indicating a horizontal or vertical blank period.

When the DRC receives HSYNC, the contents of the Offset Register are added to the VAC. If the screen width is the same as the display width, the Offset Register will have been programmed to zero and this is an effective NOP. In this case, the first word of the nth scan line is contiguous with the last word of the n-1th scan line. In the case where the display RAM is wider than the screen, the Offset Register will have been programmed with the difference (in words, not pixels). Thus the DRC will skip over the "unused" words to get to the words for the next scan line.

This addition is inhibited for HSYNC pulses which occur between the rising edge of VSYNC and the falling edge of VIDEN. This insures that the value loaded from the Top of Frame Registers does not get altered by HSYNCs which occur during vertical blank.

The offset must be equal to or less than 126, and must be even.

#### Scrolling and Panning

It is possible to effect scrolling on a scan line basis, and if the display memory is wider than the physical screen, panning on a video word basis is possible. This is done as follows:

To scroll the contents of the display up (that is, to cause scan lines to disappear off the top of the screen and previously invisible scan lines to appear from the bottom of the screen), point the Top of Frame Registers to the left-most word of the "next" scan line. To scroll down, point the Top of Frame Registers to the left-most word of the "previous" scan line.

Soft scrolling can be effected by loading the Top of Frame Registers with a series of pointers between the beginning point and the ending point. Obviously, the scroll rate will be determined by the rate at which the pointers are changed.

The display will "wrap" if there are scan lines remaining at the bottom of the screen when the VAC gets to the bottom of the display.

Panning can be effected by loading the Top of Frame Registers with values which do not point to the left-most word of a scan line.

Since there are multiple segments of the Top of Frame Registers, it is important to insure that the VAC never gets loaded with a partially updated Top of Frame value. This can be done by always modifying the registers right after the leading edge of VSYNC.

## Graphics Processor (GP) Access to the Display RAM

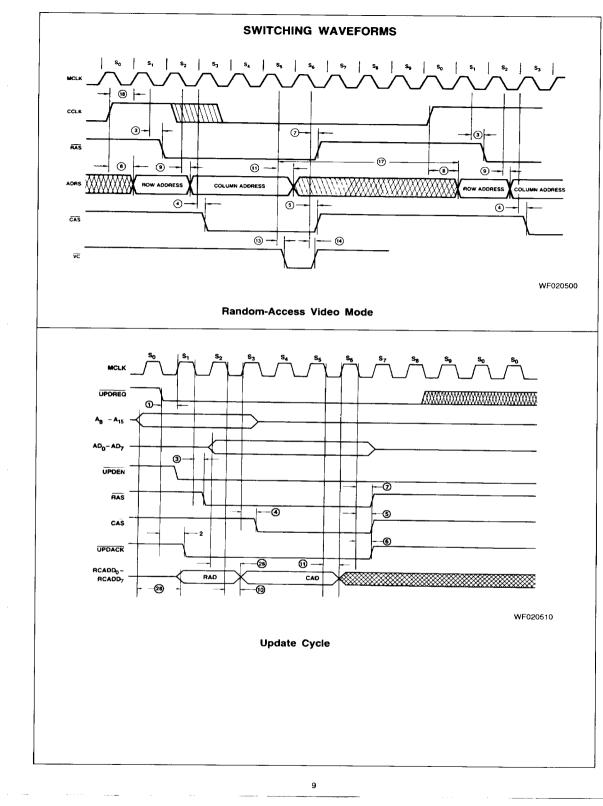

The DRC provides the address pathway to allow the GP access to the display RAM. The address is presented on  $A_8-A_{17}$  and  $AD_0-AD_7$ . The GP signals a request by driving UPDREO active which makes UPDACK active asynchronously. When the cycle actually begins, UPDEN will go active. When the cycle is complete UPDACK goes inactive and the GP may continue.

Since the display RAM (and the address pathway) may be busy taking care of display refresh, it is necessary to provide a

means to arbitrate the access requests. Three modes are available. The user programs bits 1 and 0 of the Mode Register to select the desired mode.

Retrace Only: This mode allows the GP access to the display RAM only when VIDEN is not active (and when no dynamic RAM refresh cycles are pending). This will be the case during vertical blank and horizontal blank. Depending on the relationships of blank and active video times (both horizontal and vertical), this may provide the GP access to the RAM about 10-30% of the time. Observe that this time occurs in bursts during horizontal and vertical blanking time. Retrace Only is selected by programming bits 1 and 0 of the Mode Register to 0,0.

Update Override: If a 1 is programmed in bit zero of the Mode Register, Update Override is selected (regardless of bit 1). In this mode, screen refresh is suspended and the VAC is not incremented. This mode will cause incorrect information to appear on the screen until the next VSYNC after Update Override is turned off, but allows the GP nearly 100% access to the display RAM. Dynamic RAM refresh cycles will still take priority over the GP accesses.

Interleaved Update: This mode allows the GP access to the display RAM on alternate CCLK cycles during video refresh. This permits update access at something greater than 50%. Since this allows display refresh cycles only on alternate cycles, the video RAM bandwidth must be doubled (with respect to what it otherwise would have had to have been). Interleaved access may not be combined with Page Mode operation.

The DRC provides three control pins for the GP interface: UPDREQ is an input which is asserted when the GP needs access to the display RAM. When the DRC sees UPDREQ, it will drive UPDACK active (LOW) until the cycle has been completed. The system designer must insure that UPDACK is recognized by the processor.

When the DRC actually begins the display RAM cycle for the GP, it will make UPDEN active (LOW). The system designer should use UPDEN to gate write enable to the display RAM. This assures that writes occur only during the correct cycles. In addition, if the data-in and data-out pins on the RAMs are tied together, UPDEN should be used to gate the write data into the array.

The trailing edge of  $\overline{\text{CAS}}$  may be used to latch the data during a read cycle. During a write cycle, the address and data must remain valid until the trailing edge of  $\overline{\text{UPDACK}}$ .

#### **Dynamic RAM Refresh**

The DRC is also used to perform the dynamic RAM refresh function. Refresh is accomplished beginning at HSYNC and is asynchronous to CCLK. Bits 5 and 4 of the Mode Register are used to control the number of refresh cycles executed at each HSYNC. An 8-bit counter is used to keep track of the refresh address. It is incremented once for every refresh cycle.

Each refresh cycle consists of a RAS-only memory cycle; all four RAS lines are made active. The duration of RAS is six MCLK cycles, followed by four MCLK cycles for RAS precharge.

Some devices require 128 refresh cycles every 2 ms white others require 256 refresh cycles every 4 ms. In either case, one refresh cycle is required (on the average) every 15.625 microseconds.

The number of refresh cycles per HSYNC is: HSYNC PERIOD/15.625 microseconds

For a 64 kHz horizontal frequency system, this works out to exactly 1.

The refresh cycles take place in the period between the beginning of HSYNC and the beginning of active video. The system designer must insure that this period is long enough to perform the required number of cycles. Each refresh cycle requires ten MCLK cycles.

#### Page Mode Operation

Page Mode operation of the display RAMs may be selected by programming bit three of the Mode Register to a one. This can be used to increase the video bandwidth or allow the use of slower RAM chips or both. The DRC uses ten MCLK periods to execute a non-page mode cycle and seven MCLK periods to execute a Page Mode cycle.

In Page Mode operation, the DRC performs video refresh cycles in page mode and performs CPU accesses with random cycle timing. For this reason, Page Mode operation cannot be combined with interleaved operation.

The system designer should be careful that Page Mode operations do not result in timing which violates the RAS pulse width specification for the RAM chips which are to be used.

#### CCLK and MCLK Considerations

In most systems, CCLK period will be equal to the pixel period times the number of bits accessed and loaded into the shift registers. When interleaved operation is used, CCLK period will be equal to ½ the pixel period times the number of bits accessed (alternate CCLKs are used to access video data). CCLK will always be derived from the Dot Clock.

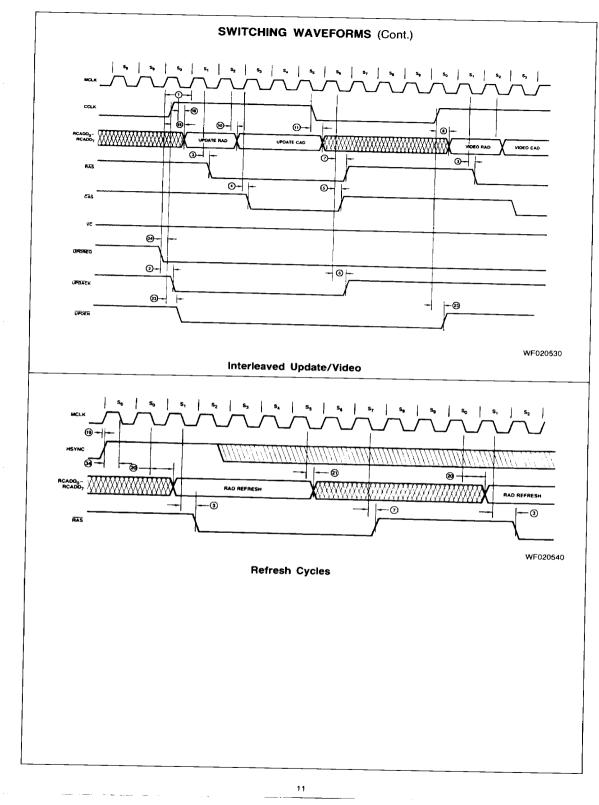

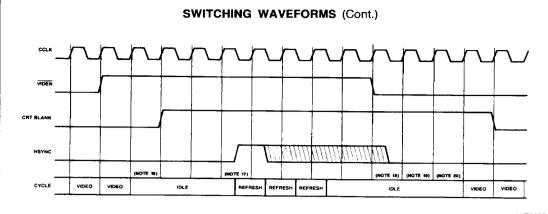

MCLK is used to clock a state machine which controls the RAM timing (in particular the relationship between RAS,  $\overline{CAS}$ , the address bits, and  $\overline{VC}$ ). This timing is shown in detail in the timing diagrams. These diagrams can also be used to explain the lower bound on MCLK period.

The MCLK period will determine the time between the leading edge of RAS and the address bits changing. This is an AC parameter at the RAM chip and is called Row Address Hold Time (t<sub>RAH</sub>). A "typical" DRAM requires 20 ns.

An additional restriction on the lower bound on MCLK period is set by the Column Access Time ( $t_{CAC}$ ) of the devices in the array. There will be four MCLK HIGH times and three MCLK LOW times between the falling edge of  $\overline{CAS}$  and the rising edge of  $\overline{VC}$  (which should be used to latch the data in the serializer). Delays in the drivers should be taken into account.

A third restriction on the lower bound of the MCLK period is that CCLK must be low at the end of a RAM cycle. This means that MCLK >  $^{1}\!/_{20}$  CCLK for Random Mode, and MCLK >  $^{1}\!/_{14}$  CCLK for Page Mode.

The upper bound on MCLK period is:

In Random-Access Video Mode, MCLK period must be  $< 1\!\!/10$  CCLK period.

In Page Mode, MCLK must be < 1/7 CCLK period.

In Interleaved Access Mode, MCLK period must be  $\leqslant 1/10$  CCLK period.

In any case, MCLK period must be such that the programmed dynamic RAM refresh cycles can occur between HSYNC and active video. Each refresh cycle takes ten MCLK periods.

#### **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature65 to +150°C<br>Ambient Temperature Under Bias55 to +125°C |

|-------------------------------------------------------------------------------|

| Supply Voltage to Ground Potential                                            |

| Continuous (TTL)0.5 to +7.0 V                                                 |

| DC Voltage Applied to Outputs for                                             |

| High Output State (TTL)0.5 to +V <sub>CC</sub> Max.                           |

| DC Input Voltage (TTL)0.5 to +7.0 V                                           |

| DC Input Current (TTL)30 to +5.0 mA                                           |

| DC Output Current (TTL)30 mA                                                  |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### OPERATING RANGES

| Commercial (C) Devices        |    |     |      |     |

|-------------------------------|----|-----|------|-----|

| Temperature (T <sub>A</sub> ) | 0  | to  | + 70 | 0°C |

| Supply Voltage (VCC)+4.75     | to | ) + | 5.2  | 5 V |

Operating ranges define those limits between which the functionality of the device is guaranteed.

#### DC CHARACTERISTICS over operating range unless otherwise specified

| Parameter<br>Symbols | Parameter Descriptions                | Test Conditions (Note 1)                                                        | Min. | Typ.<br>(Note 2)                        | Max. | Units |

|----------------------|---------------------------------------|---------------------------------------------------------------------------------|------|-----------------------------------------|------|-------|

| Voн                  | Output HIGH Voltage                   | V <sub>CC</sub> = Min.,<br>I <sub>OH</sub> = -1.0 mA                            | 2.4  | 3.4                                     |      | ٧     |

| VOL                  | Output LOW Voltage                    | V <sub>CC</sub> = Min.,<br>All I <sub>OL</sub> = 16 mA                          |      |                                         | 0.5  | ٧     |

| V <sub>IH</sub>      | Input HIGH Level Voltage              | V <sub>CC</sub> = Max. Guaranteed Input HIGH<br>Voltage for All Inputs (Note 4) | 2.0  |                                         |      | ٧     |

| VIL                  | Input LOW Level Voltage               | V <sub>CC</sub> = Min. Guaranteed Input LOW Voltage for All Inputs (Note 4)     |      |                                         | 0.8  | ٧     |

| VI                   | Input Clamp Voltage                   | V <sub>CC</sub> = Min., I <sub>I</sub> = -18 mA                                 |      |                                         | -1.2 | V     |

| I <sub>1</sub> L     | Input LOW Current                     | V <sub>CC</sub> = Max., V <sub>IL</sub> = 0.4 V                                 |      |                                         | -550 | μΑ    |

| Iн                   | Input HIGH Current                    | V <sub>CC</sub> = Max., V <sub>IH</sub> = 2.4 V                                 |      |                                         | 100  | μΑ    |

| Isc                  | Output Short-Circuit Current (Note 3) | V <sub>CC</sub> = Max.                                                          | -10  |                                         | -55  | mA    |

| Icc                  | Supply Current                        | V <sub>CC</sub> = Max., Outputs Open                                            | 360  | 450                                     | 650  | mA    |

| lvL                  | Input Current at Max. Input Voltage   | V <sub>CC</sub> = Max., V <sub>I</sub> = 5.5 V                                  |      | † · · · · · · · · · · · · · · · · · · · | 1.0  | mA    |

Notes: See notes following Switching Characteristics table.

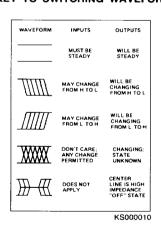

#### KEY TO SWITCHING WAVEFORMS

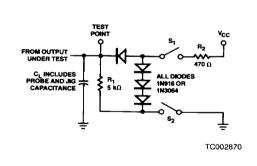

#### SWITCHING TEST CIRCUIT

#### SWITCHING CHARACTERISTICS over operating range unless otherwise specified

| No. | Parameter<br>Symbols | Parameter Descriptions                          | Min. | Max. | Units |

|-----|----------------------|-------------------------------------------------|------|------|-------|

| 1   | ts                   | UPDREQ; to MCLK; (Notes 6, 15)                  | 12   |      | ns    |

| 2   | tPHL                 | UPDREQ1 to UPDACK1                              |      | 20   | ns    |

| 3   | tpHL                 | MCLKi to RASi (Notes 10, 13)                    | 5    | 25   | ns    |

| 4   | tpHL                 | MCLK1 to CASI (Note 11)                         | В    | 25   | ns    |

| 5   | tpLH                 | MCLK1 to CAS1 (Note 14)                         | 5    | 40   | ns    |

| 6   | tPLH                 | MCLK; to UPDACK1                                |      | 30   | ns    |

| 7   | t <sub>PD</sub>      | MCLK; to RASt                                   |      | 40   | ns    |

| 8   | tpD                  | CCLK; to RCADD = VIDEO RAD                      |      | 40   | ns    |

| 9   | tPD                  | MCLK1 to RCADD = VIDEO CAD (Notes 10, 11)       |      | 30   | ns    |

| 10  | tpD                  | MCLK: to RCADD = UPDATE CAD (Notes 10, 11)      |      | 40   | ns    |

| 11  | t <sub>PD</sub>      | MCLK; to RCADD = VIDEO INVALID                  |      | 30   | ns    |

| 12  | tpD                  | MCLK; to RCADD = VIDEO VALID (PM)               |      | 30   | ns    |

| 13  | <sup>†</sup> PHL     | MCKL; to VC;                                    |      | 25   | ns    |

| 14  | tPLH                 | MCLK⊥ to VC₁ (Note 14)                          |      | 25   | ns    |

| 15  | tpD                  | CCLK1 to RCADD = UPDATE RAD (Note 7)            |      | 40   | ns    |

| 16  | tpD                  | MCLK: to RCADD = UPDATE RAD                     |      | 30   | ns    |

| 17  | tPD                  | MCLK↓ to RCADD = VIDEO VALID (RANDOM)           |      | 140  | ns    |

| 18  | ts                   | CCLK1 to MCLK1 (Notes 8, 15)                    | 15   |      | ns    |

| 19  | ts                   | MCLK: to HSYNC: (Notes 12, 15)                  | 2    |      | ns    |

| 20  | t <sub>PD</sub>      | MCLK↓ to RCADD = DRAM REFRESH ADDRESS (Note 13) |      | 50   | ns    |

| 21  | t <sub>PD</sub>      | MCLK1 to RCADD = DRAM REFRESH ADDRESS INVALID   |      | 30   | ns    |

| 22  | t <sub>PD</sub>      | CCLK1 to UPDEN (BLANK)                          |      | 30   | ns    |

| 23  | tPD                  | CCLK1 to UPDEN (INTERLEAVED)                    |      | 30   | ns    |

| 24  | ts                   | UPDREQ1 to CCLKt (INTERLEAVED) (Note 15)        | 1    |      | ns    |

| 25  | t <sub>PD</sub>      | AD <sub>0</sub> – AD <sub>7</sub> to RCADD      |      | 30   | ns    |

| 26  | 1 <sub>PD</sub>      | A <sub>8</sub> – A <sub>15</sub> to RCADD       |      | 30   | ns    |

| 27  | ts                   | RS to REGEN (Note 15)                           | 5    |      | ns    |

| 28  | ts                   | AD to REGEN↑ (Note 15)                          | 5    |      | ns    |

| 29  | t <sub>H</sub>       | REGEN₁ to RS (Note 15)                          | 0    |      | ns    |

| 30  | ţн                   | REGEN↑ to AD (Note 15)                          | 5    |      | ns    |

| 31  | tw                   | REGEN Pulse Width                               | 20   |      | ns    |

| 32  | tw                   | MCLK HIGH (Note 9)                              | 12.5 |      | ns    |

| 33  | t <sub>W</sub>       | MCLK LOW (Note 9)                               | 12.5 |      | ns    |

| 34  | t <sub>H</sub>       | HSYNC1 to MCLK1 (Notes 12, 15)                  | 15   |      | ns    |

#### Notes\*:

- For conditions shown as Min. or Max., use the appropriate value specified under recommended operating ranges.

- All typical values are V<sub>CC</sub> = 5.0 V, T<sub>A</sub> = 25°C.

- The duration of the short-circuit should not exceed one second.

- $V_{\rm IH}$ ,  $V_{\rm IL}$  are tested for each input at least once. Thereafter, hard HIGH and LOW levels are used for all other tests. A combination of skewing the limits and adjusting the pulse test ambient temperature is used to ensure that the data sheet steady state limits are met at the ambient temperature specified.

- Parameter 1 is the setup time required to ensure recognition of an Update Request in the next MCLK cycle. It is not an operating requirement.

- operating requirement.

Applies only in interleaved operation.

Parameter 18 is the setup time required to ensure recognition of CCLK in the next MCLK cycle. It is not an operating parameter

- RAS falling edge to RCADD changing equal or greater than (MCLK minus 5 ns) (Note 15).

RCADD is valid (MCLK/2 minus 11.5 ns) prior to CAS falling edge (Note 15).

- 12.

- Not an operating requirement. Guarantees parameter 20.

- 13 14

- RCADD is valid one MCLK low time prior to falling edge of RAS.

VC rising edge to occur no later than 3 ns after CAS rising edge (Note 15).

Guaranteed by characterization/correlation to other AC parameters that are tested. 15.

- 16.

- During this time, the last video character of the line is being shifted out.

Refresh and update cycles during blank are not synchronized to CCLK.

The 2 CCLK periods following VIDEN1 are allocated to completion of update cycles in progress, if any.

The third CCLK period following VIDEN1 is allocated to RAS precharge in page mode, or idle otherwise.

- \* Notes listed correspond to respective references made in DC Characteristics and Switching Characteristics tables, and Switching Waveforms section.

WF020550

Notes: See notes following Switching Characteristics table.

## Operating Sequence During Blank (Random Cycle, Non-Interleaved, 3 Refresh Cycles, Cycle Programmed)

#### **Loading Registers**

MCLK Waveform

#### **ADVANCED MICRO DEVICES**

#### U.S. SALES OFFICES

| ALABAMA (205) 882-9122                            | MASSACHUSETTS (617) 273-3970                                                      |

|---------------------------------------------------|-----------------------------------------------------------------------------------|

| ARIZONA,                                          | MINNESOTA (612) 938-0001                                                          |

| Tempe (602) 242-4400                              | MISSOURI (314) 275-4415                                                           |

| CALIFORNIA,                                       | NEW JERSEY (201) 299-0002                                                         |

| Culver City (213) 645-1524                        | NEW YORK,                                                                         |

| Newport Beach (714) 752-6262                      | Liverpool                                                                         |

| San Diego                                         | Poughkeepsie (914) 471-8180                                                       |

| Santa Clara                                       | Woodbury (516) 364-8020                                                           |

| Woodland Hills                                    | NORTH CAROLINA (919) 847-8471                                                     |

| COLORADO                                          | OREGON (503) 245-0080                                                             |

| FLORIDA. (203) 264-7800                           | OHIO (614) 891-6455<br>PENNSYLVANIA,                                              |

| Clearwater (813) 530-9971                         | Allentown                                                                         |

| Ft Lauderdale                                     | Willow Grove                                                                      |

| Melbourne                                         | TEXAS,                                                                            |

| Orlando                                           | Austin                                                                            |

| GEORGIA (404) 449-7920                            | Dallas(214) 934-9099                                                              |

| ILLINOIS (312) 773-4422                           | Houston                                                                           |

| NDIANA (317) 244-7207                             | WASHINGTON (206) 455-3600                                                         |

| KANSAS (913) 451-3115                             | WISCONSIN (414) 792-0590                                                          |

| MARYLAND (301) 796-9310                           |                                                                                   |

| INTERNATIONAL                                     | SALES OFFICES                                                                     |

| BELGIUM.                                          | ITALY Milana TEL (00) coccess                                                     |

| Bruxelles TEL: (02) 771 99 93                     | ITALY, Milano                                                                     |

| FAX: (02) 771 99 93                               | FAX: (02) 3498000<br>TLX: 315286                                                  |

| TLX: (02) 762-3716                                | JAPAN, 315286                                                                     |

| CANADA, Ontario,                                  | Tokyo                                                                             |

| Kanata TEL: (613) 592-0090                        | FAX: 3425196                                                                      |

| Willowdale                                        | TLX: J24064AMDTKOJ                                                                |

| FAX: (416) 224-0056                               | Osaka                                                                             |

| FRANCE,                                           | FAX: 06-243-3253                                                                  |

| Paris TEL: (01) 45 60 00 55                       | KOREA, Seoul TEL: 82-733-1021/7                                                   |

| FAX: (01) 46 86 21 85                             | FAX: 82-733-1028                                                                  |

| TLX: 202053F                                      | TLX: K22652                                                                       |

| GERMANY,                                          | LATIN AMERICA,                                                                    |

| Hannover area TEL: (05143) 50 55                  | Ft. Lauderdale TEL: (305) 484-8600                                                |

| FAX: (05143) 55 53<br>TLX: 925287                 | FAX: (305) 485-9736<br>TLX: . 5109554261 AMDFTL                                   |

| München 725267                                    | SWEDEN, Stockholm TEL: (08) 733 03 50                                             |

| FAX: (089) 406490                                 | FAX: (08) 733 03 30                                                               |

| TLX: 523883                                       | TLX:                                                                              |

| Stuttgart TEL: . (0711) 62 33 77                  | UNITED KINGDOM,                                                                   |

| FAX: (0711) 625187                                | Manchester area TEL: (0925) 828008                                                |

| TLX: 721882                                       | FAX: (0925) 827693                                                                |

| HONG KONG.                                        | TLX: 628524                                                                       |

| Kowloon                                           | London area TEL: (04862) 22121                                                    |

| FAX: 1234276                                      | FAX: (04862) 22179                                                                |

| TLX: 50426                                        | TLX: 859103                                                                       |

| NORTH AMERICAN                                    | REPRESENTATIVES                                                                   |

| CALIFORNIA                                        | NEW MEXICO                                                                        |

| I <sup>2</sup> INC OEM (408) 988-3400             | THORSON DESERT STATES (505) 293-8555                                              |

| DISTI (408) 496-6868                              | NEW YORK                                                                          |

| DAHO                                              | NYCOM, INC                                                                        |

| INTERMOUNTAIN TECH MKGT (208) 888-6071            | OHIO (313) 437-6343                                                               |

| NDIANA                                            | Dayton                                                                            |

| ELECTRONIC MARKETING CONSULTANTS . (317) 253-1668 | DOLFUSS ROOT & CO (513) 433-6776                                                  |

| OWA                                               | Strongsville                                                                      |

| LORENZ SALES(319) 377-4666<br>KANSAS              | DOLFUSS ROOT & CO(216) 238-0300<br>PENNSYLVANIA                                   |

| LORENZ SALES (913) 384-6556                       | DOLFUSS ROOT & CO (412) 221-4420                                                  |

| MICHIGAN SAI MARKETING CORP (313) 750-1922        | UTAH R <sup>2</sup> MARKETING(801) 595-0631                                       |

| MISSOURI                                          | 11 MARKETHAG (001) 595-0631                                                       |

| LODENZ CALES (014) 007 4550                       |                                                                                   |

| LORENZ SALES (314) 997-4558                       |                                                                                   |

| NEBRASKA                                          |                                                                                   |

| NEBRASKA<br>LORENZ SALES(402) 475-4660            | notice in order to improve design or performance characteristics. The performance |

PID # 04478C

016945 🗸 ...

Printed in U.S.A. AIS-B-20M-5/87-0

ADVANCED MICRO DEVICES 901 Thompson Pl., P.O. Box 3453, Sunnyvale, CA 94088, USA © 1987 Advanced Micro Devices, Inc.

TEL: (408) 732-2400 • TWX: 910-339-9280 • TELEX: 34-6306 • TOLL FREE: (800) 538-8450