## LIN Bus Transceiver with Integrated Voltage Regulator

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage, VSOP Continuous30 V                         |

|-------------------------------------------------------------|

| Supply Voltage, VSUP Transient (500 ms)40 V                 |

| LIN Bus Voltage, LIN18 to +40 V                             |

| Wake Pin                                                    |

| Logic Pins: RX, TX, EN0.3 V to 7 V                          |

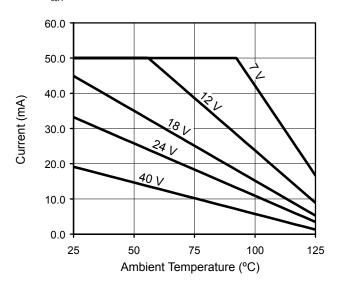

| Package Power Dissipation, P <sub>D</sub> see chart, page 6 |

| Operating Temperature Range                                 |

| Ambient Temperature, T <sub>A</sub> 40°C to +125°C          |

| Junction Temperature, T <sub>J</sub> 55°C to +150°C         |

| Storage Temperature, T <sub>s</sub> 55°C to +150°C          |

|                                                             |

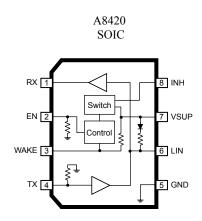

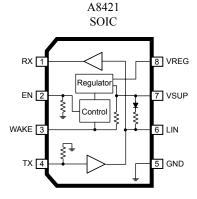

The A8420 and A8421 provide the physical interface requirements of the LIN (Local Interconnect Network) serial communications bus plus either a signal to control an external supply (in the A8420), or an integrated voltage regulator (in the A8421). These allow the development of simple, inexpensive slave nodes in a LIN-Bus system.

The LIN transceiver is compatible with LIN-Bus systems that conform to the LIN Protocol Specification, Revision 1.2. It provides all the necessary interface and timing control to convert signals to and from the bidirectional LIN Bus to individual transmit and receive signals at logic-compatible levels.

The A8421 provides regulated 5V output with a current limit in excess of 50 mA. This is sufficient to power a microcontroller handling the LIN slave node protocol.

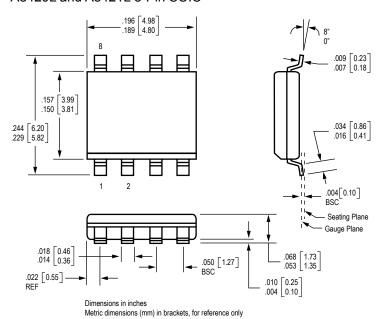

The A8420 and A8421 are supplied in 8-lead plastic SOIC (part number suffix L).

#### **FEATURES**

- Compatible with LIN Bus, Revision 1.2 systems

- Data rate up to 20 kbaud

- Normal operation from 7 to 30 V

- Handles 40 V transients during load dump

- Handles automotive transients per ISO 7637

- Unpowered node does not disturb the network

- 4 kV (hbm) ESD protection on LIN and WAKE pins

- Two options: Control for external supply (A8420) or regulated supply for slave microcontroller (A8421)

- Interface to slave microcontroller

- 8-pin small outline surface mount package

#### APPLICATIONS

Automotive, industrial, and consumer LIN-Bus systems

Use the following complete part numbers when ordering:

| Part Number | Package      | Description       |  |  |

|-------------|--------------|-------------------|--|--|

| A8420KL     | 8-lead, SOIC | INH switch output |  |  |

| A8421KL     | 8-lead, SOIC | Voltage regulator |  |  |

# LIN Bus Transceiver with Integrated Voltage Regulator

### **ELECTRICAL CHARACTERISTICS** at $T_J = -40^{\circ}\text{C}$ to 150°C, $V_{SUP} = 7 \text{ V}$ to 18 V (unless otherwise noted)

| Characteristics              | Symbol                        | Test Conditions                                                   | Min.                  | Тур.                 | Max.                   | Units |

|------------------------------|-------------------------------|-------------------------------------------------------------------|-----------------------|----------------------|------------------------|-------|

| VSUP Power Supply            |                               |                                                                   |                       |                      |                        |       |

| Operating Voltage Range      | V                             | Continuous                                                        | 7                     | -                    | 30                     | V     |

| Operating voltage realige    | $V_{\scriptscriptstyle{SUP}}$ | Transient; 500 ms                                                 | -                     | _                    | 40                     | V     |

| Supply Current               | ı                             | LIN output recessive (High); V <sub>WAKE</sub> = 0                | _                     | 0.8                  | 1                      | mA    |

| Supply Current               | SUP                           | LIN output dominant (Low); V <sub>WAKE</sub> =0                   | -                     | 1.5                  | 2                      | mA    |

| Supply Standby Current       | ı                             | V <sub>WAKE</sub> =0, LIN=N.C.                                    | -                     | 0.8                  | 1                      | mA    |

| Supply Standby Current       | STBY                          | LIN = Dominant (Low), Wake = N.C.                                 | -                     | 1.5                  | 2                      | mA    |

| Supply Sleep Current         | I <sub>SLEEP</sub>            |                                                                   | -                     | 6                    | 10                     | μA    |

| Undervoltage Threshold       | VSUP <sub>UV</sub>            |                                                                   | 4.8                   | 5.0                  | 5.2                    | V     |

| TX and EN Input              |                               |                                                                   | '                     |                      | '                      |       |

| Low Level Input Voltage      | $V_{_{\rm IL}}$               |                                                                   | _                     | -                    | 0.8                    | V     |

| High Level Input Voltage     | V <sub>IH</sub>               |                                                                   | 2                     | _                    | _                      | V     |

| Input Hysteresis             | V <sub>IHYS</sub>             |                                                                   | _                     | 300                  | _                      | mV    |

| Pull-Down Resistor           | $R_{PD}$                      | EN pin                                                            | 60                    | 100                  | 200                    | kΩ    |

| Pull-Up Resistor             | R <sub>PU</sub>               | TX pin                                                            | 60                    | 100                  | 200                    | kΩ    |

| RX Output                    |                               |                                                                   | •                     |                      | •                      |       |

| Low Level Output Current     | I <sub>OL</sub>               | V <sub>RX</sub> =0.4 V                                            | 1.5                   | _                    | _                      | mA    |

| High Level Leakage Current   | I <sub>OH</sub>               | V <sub>RX</sub> =5 V                                              | _                     | -                    | 5                      | μA    |

| Wake Input                   |                               | ,                                                                 |                       |                      |                        |       |

| Low Level Input Voltage      | $V_{_{\rm IL}}$               |                                                                   | _                     | _                    | V <sub>SUP</sub> -5    | V     |

| High Level Input Voltage     | V <sub>IH</sub>               |                                                                   | V <sub>SUP</sub> -1   | _                    | _                      | V     |

| Pull-up Current              | I <sub>L</sub>                | V <sub>WAKE</sub> =0 V                                            | _                     | 40                   | _                      | μA    |

| High Level Leakage Current   | I <sub>IH</sub>               | V <sub>WAKE</sub> =V <sub>SUP</sub> =30 V                         | _                     | _                    | 5                      | μA    |

| INH Output (A8420 Only)      |                               |                                                                   | '                     |                      |                        |       |

| On Resistance VSUP to INH    | R <sub>on</sub>               | I <sub>o</sub> = 15 mA                                            | _                     | 40                   | 100                    | Ω     |

| Off Leakage Current          | I <sub>OL</sub>               |                                                                   | -                     | _                    | 5                      | μA    |

| VREG Regulated 5V Supply     |                               | ly)                                                               |                       |                      |                        |       |

| Output Voltage               | $V_{REG}$                     | I <sub>OUT</sub> = 0 to 50 mA                                     | 4.5                   | 5.0                  | 5.5                    | V     |

| Output Current Limit         | IREG <sub>LIM</sub>           | $V_{REG} = 0 V$                                                   | -                     | -                    | 180                    | mA    |

| External Decoupling Cap      |                               | V <sub>REG</sub> to GND                                           | 1                     | ı                    | _                      | μF    |

| Line Regulation              |                               | I <sub>OUT</sub> = 30 mA                                          | -                     | ı                    | 100                    | mV    |

| Load Regulation              |                               | $V_{SUP} = 13.5 \text{ V}; I_{OUT} = 1 \text{ to } 30 \text{ mA}$ | _                     | ı                    | 100                    | mV    |

| LIN Interface                |                               |                                                                   |                       |                      |                        |       |

| Output Short Circuit Current | l <sub>osc</sub>              |                                                                   | 60                    | 85                   | 110                    | mA    |

| Output Voltage – Recessive   | $V_{OR}$                      | $V_{TX} = 5 \text{ V}; I_{LIN} = 0 \text{ mA}$                    | 0.9 V <sub>SUP</sub>  | _                    | _                      | V     |

| Output Voltage – Dominant    | $V_{od}$                      | V <sub>TX</sub> =0 V; I <sub>LIN</sub> =40 mA                     | _                     | 1                    | 1.2                    | V     |

| High Level Leakage Current   | I <sub>IH</sub>               | V <sub>LIN</sub> =V <sub>SUP</sub>                                |                       | -                    | 10                     | μA    |

| Termination Resistance       | R <sub>SLAVE</sub>            |                                                                   | 20                    | 30                   | 47                     | kΩ    |

| Input Threshold – Dominant   | V <sub>THDOM</sub>            | V <sub>LIN</sub> – Recessive to Dominant                          | 0.4 V <sub>SUP</sub>  | 1                    | _                      | V     |

| Input Threshold – Recessive  | V <sub>THREC</sub>            | V <sub>LIN</sub> – Dominant to Recessive                          | _                     |                      | 0.6 V <sub>SUP</sub>   | V     |

| Input Threshold Hysteresis   | VLIN <sub>HYS</sub>           |                                                                   | 0.05 V <sub>SUP</sub> | 0.1 V <sub>SUP</sub> | 0.175 V <sub>SUP</sub> | V     |

# LIN Bus Transceiver with Integrated Voltage Regulator

### **DYNAMIC CHARACTERISTICS** at $T_J = -40^{\circ}\text{C}$ to 150°C, $V_{SUP} = 7 \text{ V}$ to 18 V (unless otherwise noted)

| Characteristics                         | Symbol           | Test Conditions                            | Min. | Тур. | Max. | Units |  |

|-----------------------------------------|------------------|--------------------------------------------|------|------|------|-------|--|

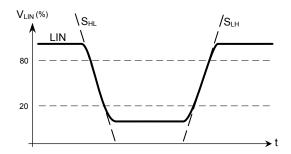

| LIN Falling Edge Slew Rate <sup>1</sup> | S <sub>HL</sub>  | 80% to 20%                                 | 1    | 2    | 3    | V/µs  |  |

| LIN Rising Edge Slew Rate <sup>1</sup>  | u                | 20% to 80% into >1 kΩ and <5 nF            | 1    | 2    | 3    | V/µs  |  |

| Lift Kising Luge Siew Kate              | $S_{LH}$         | 20% to 80% into >1 kΩ and <10 nF           | _    | 1    | _    | V/µs  |  |

| LIN Rise Fall Symmetry                  | t <sub>sym</sub> | 20% to 80% into >1 kΩ and <5 nF            | -2   | -    | 2    | μs    |  |

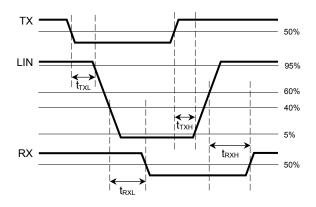

| TX Propagation Delay H→L                | t <sub>TXL</sub> | TX H→L; LIN crossing 95%                   | _    | 1.5  | 4    | μs    |  |

| TX Propagation Delay L→H                | t <sub>TXH</sub> | TX L→H; LIN crossing 5%                    | _    | 1.5  | 4    | μs    |  |

| TX Propagation Delay Matching           |                  |                                            | _    | _    | 2    | μs    |  |

| RX Propagation Delay H→L                | t <sub>RXL</sub> | LIN crossing 40%; RX crossing 50%          | _    | 3    | 6    | μs    |  |

| RX Propagation Delay L→H                | t <sub>RXH</sub> | LIN crossing 60%; RX crossing 50%          | _    | 3    | 6    | μs    |  |

| RX Propagation Delay Matching           |                  |                                            | _    | -    | 2    | μs    |  |

| Glitch Rejection                        | t <sub>GLR</sub> | +ve and -ve pulse rejection on LIN (to RX) | _    | 1.8  | _    | μs    |  |

| Wake-up Delay (LIN or WAKE)             | t <sub>wL</sub>  | Wake-up to INH or VREG 90%                 | _    | 50   | _    | μs    |  |

| Thermal Shutdown                        |                  |                                            |      |      |      |       |  |

| Shutdown Temperature                    | $T_{SD}$         |                                            | _    | 165  | _    | °C    |  |

| Thermal Shutdown Hysteresis             | T <sub>HYS</sub> |                                            | _    | 20   | _    | °C    |  |

<sup>&</sup>lt;sup>1</sup>Slew rate is controlled during both transitions and will not exceed specified limits at any point between test limits.

Figure 1. Propagation timing definition

Figure 2. Slew rate definition

## LIN Bus Transceiver with Integrated Voltage Regulator

### **Functional Description**

**Power Supply.** The device power supply, 13.5 V nominal for automotive applications, is connected to the battery through an external diode, in order to protect against reversal of battery polarity. To comply with the LIN Bus protocol, there must be no more than a 1 V drop between the battery potential and the supply pin. The A8420/A8421 operates continuously up to 30 V, and withstands 40 V during a 500 ms load dump. If the supply drops below the undervoltage limit, this condition is detected and the A8420/A8421 disables the transmission path, while maintaining a high-impedance state on the LIN terminal.

The A8420/A8421 does not disturb the LIN Bus in the case of ground disconnection at the module level. In addition, full functionality is maintained with a ground shift of up to 8 V, provided that the difference between GND and VSUP is greater than the undervoltage threshold.

**LIN Bus Interface.** The A8420/A8421 integrates all components required to drive and monitor the single-wire LIN Bus as a slave node. An external resistor, diode, and capacitor are normally required for the A8420/A8421 to function as a master node. The LIN pin can withstand voltages from +40 V to -18 V with respect to the GND pin without adversly affecting LIN Bus communications between

other devices. When the A8420/A8421 is in Sleep mode or Standby mode, the LIN pin is in the recessive state.

When the A8420/A8421 is the active interface on the LIN Bus, it controls the rise and fall slew rates of the voltage level on the LIN pin, such that the rising or falling slew rate does not exceed the specified limits at any point between the 20% and 80% levels.

If, while in Sleep mode, the A8420/A8421 detects the LIN Bus transitioning into the dominant state, a wake-up signal is generated. This transitions the device from Sleep mode into Standby mode.

The data to be transmitted is input to the TX pin and converted to LIN Bus signals. A logic high on this pin produces a recessive bus (high) state while a logic low produces a dominant bus (low) state. The TX input has an internal pull-up resistor to ensure a recessive state if the pin is not connected or becomes disconnected.

The state of the LIN Bus is determined by the receiver and output as a logic level on the RX pin. This pin is open drain. In Normal mode, RX is active (pull-down) when the LIN Bus is in the dominant (low) state, and RX is inactive (high-Z) when the LIN Bus is in the recessive (high) state.

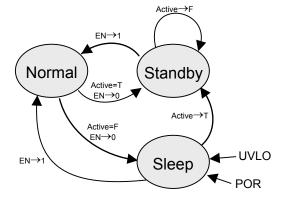

Figure 3. Operating state. Active is true (T) if WAKE is low (L) or if LIN is low (L). Otherwise, Active is false (F). The UVLO feature overrides.

#### **Logic Functions**

|    |    | Inputs |     | State Outpu |    |        | puts             |      |

|----|----|--------|-----|-------------|----|--------|------------------|------|

| TX | EN | WAKE   | LIN | State       | RX | LIN    | INH              | VREG |

| 1  | 1  | *      | Н   | Norm        | Z  | Rec(Z) | V <sub>SUP</sub> | 5V   |

| 1  | 1  | *      | L   | Norm        | L  | Rec(Z) | V <sub>SUP</sub> | 5V   |

| 0  | 1  | *      | *   | Norm        | L  | Dom(L) | V <sub>SUP</sub> | 5V   |

| *  | 0  | L¹     | *   | Standby     | L  | Rec(Z) | V <sub>SUP</sub> | 5V   |

| *  | 0  | *      | L¹  | Standby     | L  | Rec(Z) | V <sub>SUP</sub> | 5V   |

| *  | 0  | H¹     | H¹  | Sleep       | Z  | Rec(Z) | Z                | Z    |

| *  | 1  | *      | *   | UVLO        | Z  | Rec(Z) | Z                | Off  |

| *  | 1  | *      | Н   | TSD         | Z  | Rec(Z) | V <sub>SUP</sub> | 5V   |

| *  | 1  | *      | L   | TSD         | Ĺ  | Rec(Z) | V <sub>SUP</sub> | 5V   |

<sup>1</sup>Sleep mode is entered only when LIN is high, WAKE is high, and EN goes to 0. The A8420/A8421 remains in Standby mode when WAKE or LIN is low.

<sup>2</sup>Z = High Impedance, \* = Don't Care.

# LIN Bus Transceiver with Integrated Voltage Regulator

In Sleep mode RX is not active (high-Z). When in Standby mode, RX asserts an active low and can be used to indicate to the controlling device that either the wake signal has gone low or that a dominant sate is present on the LIN Bus, indicating that the bus has become active.

**Operating Mode.** The A8420/A8421 has three modes of operation: Normal, Standby, and Sleep. The enable input, EN, determines whether Normal mode is maintained (EN high) or one of the two inactive modes, Standby or Sleep, are entered (EN low). If no other wake-up signals are active, EN low sets the A8420/A8421 into low-current Sleep mode. From Sleep mode the A8420/A8421 can be put directly into Normal mode by taking EN high. Alternatively, it can be taken into Standby mode by pulling the WAKE input to ground or by a dominant state on the LIN Bus.

In Sleep mode, the supply current is at its minimum level, and the LIN and RX pins are high impedance. In this mode, the INH output (A8420) or the linear regulator output (A8421) are off. When the power is first applied, the A8420/A8421 enters Sleep mode directly.

From Sleep mode, the A8420/A8421 may be taken through the Standby mode, where the INH or linear regulator are activated, in order to provide power to the protocol control device attached to the TX, RX, and EN pins. Once the controller is active, it may then bring the A8420/A8421 into Normal mode by taking EN high. If there is no need to provide power prior to enabling the A8420/A8421, then simply asserting EN high moves the A8420/A8421 directly from Sleep mode to Normal mode.

The EN input has an internal pull-down resistor to ensure a known safe state when the protocol controller is powered off.

The WAKE signal is a high-voltage input, which is designed to allow a node on a sleeping bus to be awaken by a local

event. Sleep mode may be entered when WAKE is connected directly to the battery or other similar voltage, such as VSUP. To disable Sleep mode and allow the A8420/A8421 to enter Standby mode, the WAKE input should be switched to ground.

The A8420/A8421 incorporates two protection functions. If the die temperature becomes excessive, a thermal shutdown feature (TSD) disables the LIN output dominant-state drive. Once the temperature falls below the hysteresis level, the LIN output resumes the state defined by the TX input. During TSD, the output on INH or VREG is maintained.

If the supply voltage drops below the UVLO threshold, all outputs are disabled. When the supply voltage rises above the UVLO threshold, the A8420/A8421 is reset into the Sleep mode. From that state, it follows the logic shown in figure 1. That is, if Active is true (T), the A8420/A8421 immediately goes to Standby mode. If EN is high, it goes directly to the normal mode.

**Optional Functions.** The two options, the A8420 and the A8421, provide alternatives for powering additional circuits.

The A8420 provides an INH output, a low-impedance (typically 50  $\Omega$ ) connection to VSUP in Normal or Standby mode. In Sleep mode, this output is high-impedance. INH is intended to be used to control an external power supply, such that it powers-up and powers-down according to the LIN Bus or the local WAKE signal.

The A8421 provides a linear regulator output with specified line and load regulation up to 30 mA at 5 V. The regulator output is current-limited, at typically 100 mA. Care must be taken, however, when operating above 30 mA, due to power dissipation. This is especially important under fault conditions such as load dump. As is the case with the INH option, this output is only active in Standby or Normal mode. This

# LIN Bus Transceiver with Integrated Voltage Regulator

output will supply sufficient current for a simple microcontroller operating as a protocol controller.

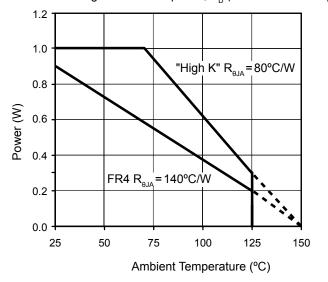

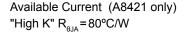

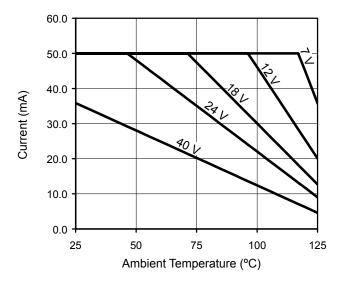

**Power Dissipation.** For the A8421, most power will normally be dissipated in the linear regulator. Because the output of the regulator is fixed at 5 V, but the input supply can vary between 7 V and 18 V, care must be taken when setting the maximum current. This is particularly important if the ability of the A8421 to withstand a 40 V load dump is to be used. This limitation does not apply to the A8420, which has a simple switched output in place of the regulator output.

The figures in the charts on this page show the allowable power dissipation and estimated maximum current for various ambient temperatures and supply voltages. The data were taken using a standard FR4 board with minimal copper (R $_{\tiny \theta JA}$ =140°C/W), and using a "High K" dielectric board with copper ground plane and thermal vias (R $_{\tiny \theta JA}$ =80°C/W).

Allowable Package Power Dissipation, P<sub>D</sub> (A8420 and A8421)

Available Current (A8421 only) FR4  $R_{_{\theta JA}}$ =140°C/W

# LIN Bus Transceiver with Integrated Voltage Regulator

#### Terminal List Table

| Name | Description                                                                                                  | Number |       |  |

|------|--------------------------------------------------------------------------------------------------------------|--------|-------|--|

| Name | Description                                                                                                  | A8420  | A8421 |  |

| RX   | Receive open drain logic output                                                                              | 1      | 1     |  |

| EN   | Enable; logic input with internal pull-down                                                                  | 2      | 2     |  |

| WAKE | High-voltage input controlling modes: active (Standby and Normal) and inactive (Sleep); with pull-up to VSUP | 3      | 3     |  |

| TX   | Transmit logic input with internal pull-up                                                                   | 4      | 4     |  |

| GND  | Ground; connected to battery negative terminal                                                               | 5      | 5     |  |

| LIN  | LIN bus connection                                                                                           | 6      | 6     |  |

| VSUP | Positive supply, 12 V nominal; external diode fitted between the battery and this pin                        | 7      | 7     |  |

| INH  | (Alternative to VREG) Output providing a switched path to VSUP                                               | 8      | _     |  |

| VREG | (Alternative to INH) Output providing regulated 5 V at 30 mA                                                 | _      | 8     |  |

#### A8420L and A8421L 8-Pin SOIC

## LIN Bus Transceiver with Integrated Voltage Regulator

The products described here are manufactured under one or more U.S. patents or U.S. patents pending.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro products are not authorized for use as critical components in life-support devices or systems without express written approval.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

Copyright©2004 AllegroMicrosystems, Inc.