# 8-bit 40MSPS YC 2-channel D/A Converter

### **Description**

The CXD1177Q is an 8-bit high-speed D/A converter for video band use. It has an input/output equivalent to 2 channels of Y and C. It is suitable for use of digital TV, graphic display, and others.

### **Features**

- Resolution 8-bit

- Maximum conversion speed 40MSPS

- YC 2-channel input/output

- Differential linearity error ±0.3 LSB

- Low power consumption 160 mW (200 Ω load at 2 Vp-p output)

- Single 5 V power supply

- · Low glitch noise

- Stand-by function

#### **Structure**

Silicon gate CMOS IC

# Absolute Maximum Ratings (Ta=25 °C)

- Supply voltage AVDD, DVDD 7

- Input voltage (All pins)

- VIN VDD +0.5 to Vss -0.5 V

- Output current (Every each channel)

- lout 0 to 15 mA

- Storage temperature

- Tstg -55 to +150 °C

### **Recommended Operating Conditions**

- Supply voltage AVDD, AVss 4.75 to 5.25 V

- DV<sub>DD</sub>, DVss 4.75 to 5.25

V

- Reference input voltage

- VREF 2.0 V

- Clock pulse width

- TPW1, TPW0 11.2 ns (min.) to 1.1 µs (max.)

- Operating temperature

- Topr -40 to +85 °C

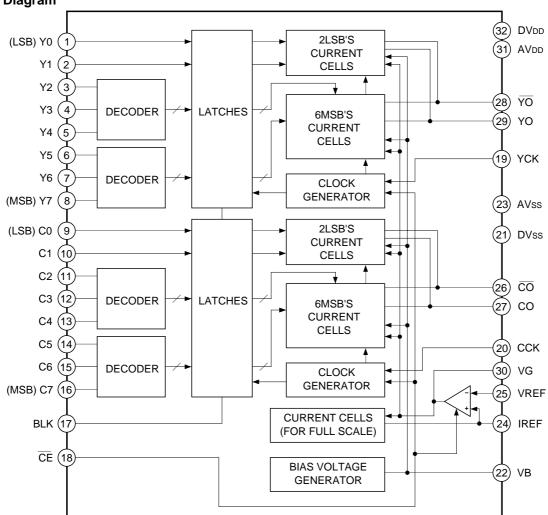

# **Block Diagram**

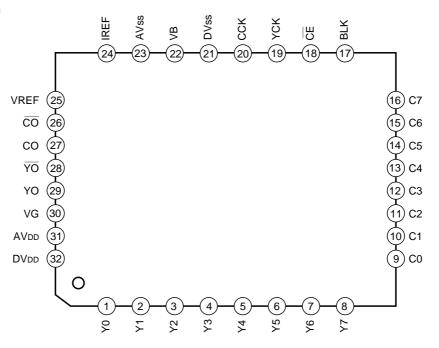

### **Pin Configuration**

# Pin Description and I/O Pins Equivalent Circuit

| Pin No. | Symbol             | I/O | Equivalent circuit                                                                                                               | Description                                                                                                                             |  |  |

|---------|--------------------|-----|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1 to 8  | Y0 to Y7  C0 to C7 | -   | 1) to W                                                                                                                          | Digital input Y0 (LSB) to Y7 (MSB) C0 (LSB) to C7(MSB)                                                                                  |  |  |

| 17      | BLK                | ı   | Blanking input. This is synchronized with the clock in for each channel. No signal at "H" (Output 0 V). Output condition at "L". |                                                                                                                                         |  |  |

| 22      | VB                 | 0   | DVDD O DVDD O DVSS O                                                                                                             | Connect a capacitor of about 0.1 μF.                                                                                                    |  |  |

| 19      | YCK                | I   | DVDD<br>(9)                                                                                                                      | Clock input.  Note) Even though only 1 channel is used, be sure to input the clock signal to YCK.                                       |  |  |

| 20      | ССК                |     | 20 DVss                                                                                                                          |                                                                                                                                         |  |  |

| 21      | DVss               | _   |                                                                                                                                  | Digital ground                                                                                                                          |  |  |

| 23      | AVss               | _   |                                                                                                                                  | Analog ground                                                                                                                           |  |  |

| 18      | CE                 | I   | 18 DVss                                                                                                                          | Chip enable input. This is not synchronized with the clock input signal. No signal (Output 0 V) at "H" and minimizes power consumption. |  |  |

| Pin No. | Symbol           | I/O | Equivalent circuit         | Description                                                                 |                                         |

|---------|------------------|-----|----------------------------|-----------------------------------------------------------------------------|-----------------------------------------|

| 24      | IREF             | 0   | AVDD O AVDD                | Connect a resistance 16 times "RIR" that of output resistance value "ROUT". |                                         |

| 25      | VREF             | I   | AVDD AVSS AVDD             | Set full-scale output value.                                                |                                         |

| 30      | VG               | 0   | AVss & 30 W                | Connect a capacitor of about 0.1 μF.                                        |                                         |

| 31      | AVDD             | _   |                            | Analog power supply                                                         |                                         |

| 27      | СО               |     | AVDD O                     | Current output.  Voltage output can be obtained by connecting               |                                         |

| 29      | YO               | 0   | 27<br>29<br>AVss<br>AVbb o | a resistance.                                                               | , · · · · · · · · · · · · · · · · · · · |

| 26      | co               |     |                            | Inverted current output.                                                    |                                         |

| 28      | YO               |     | 26<br>28<br>AVss           | Normally dropped to analog ground.                                          |                                         |

| 32      | DV <sub>DD</sub> | _   |                            | Digital power supply                                                        |                                         |

# **Electrical Characteristics**

(FCLK=40 MHz, AVDD=DVDD=5 V, ROUT=200  $\Omega$ , VREF=2.0 V, Ta=25 °C)

| Item                             | Symbol      | Measurement conditions                       |      | Min. | Тур. | Max. | Unit |

|----------------------------------|-------------|----------------------------------------------|------|------|------|------|------|

| Resolution                       | n           |                                              |      |      | 8    |      | bit  |

| Conversion speed                 | Fclk        | AVDD=DVDD=4.75 to 5.25 V<br>Ta=-40 to +85 °C |      | 0.5  |      | 40   | MSPS |

| Integral non-linearity error     | EL          | - Endpoint                                   |      | -2.5 |      | 2.5  | LSB  |

| Differential non-linearity error | Ed          |                                              |      | -0.3 |      | 0.3  | LSB  |

| Output full-scale voltage        | VFS         |                                              |      | 1.8  | 2.0  | 2.2  | V    |

| Output full-scale ratio *1       | Fsr         |                                              |      | 0    | 1.5  | 3.0  | %    |

| Output full-scale current        | IFS         |                                              |      |      | 10   | 15   | mA   |

| Output offset voltage            | Vos         | When "00000000" data input                   |      |      |      | 1    | mV   |

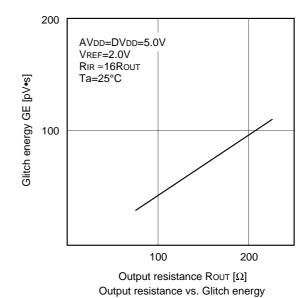

| Glitch energy                    | GE          | Rout=75 Ω                                    |      |      | 30   |      | pV•s |

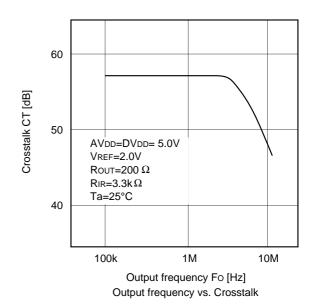

| Crosstalk                        | CT          | When 1 kHz sine wave input                   |      |      | 57   |      | dB   |

| Supply current                   | IDD         | When 14.3 MHz                                | CE=L |      |      | 32   | mA   |

| Зарріу сапені                    | Іѕтв        | color bar data input                         | CE=H |      |      | 1.2  | IIIA |

| Analog input resistance          | Rin         | VREF                                         |      | 1    |      |      | MΩ   |

| Input capacitance                | Сі          |                                              |      |      |      | 9    | pF   |

| Digital input voltage            | Vін         | AVDD=DVDD=4.75 to 5.25 V                     |      | 2.4  |      |      | V    |

| Digital input voltage            | VIL         | Ta=-20 to +75 °C                             |      |      |      | 0.8  |      |

| Digital input ourrant            | Іін         | AVDD=DVDD=4.75 to 5.25 V<br>Ta=-20 to +75 °C |      |      |      | 5 μΑ |      |

| Digital input current            | lıL         |                                              |      | _5   |      |      | μΑ   |

| Setup time                       | ts          | Rout=75 Ω                                    |      | 5    |      |      | ns   |

| Hold time                        | th          | Rουτ= <b>75</b> Ω                            |      | 10   |      |      | ns   |

| Propagation delay time           | <b>t</b> PD |                                              |      |      | 10   |      | ns   |

| CE enable time *2                | tE          | CE=H→L                                       |      |      | 2    | 4    | ms   |

| CE disable time *2               | to          | CE=L→H                                       |      |      | 2    | 4    | ms   |

<sup>\*1</sup> Full-scale output ratio =  $\left| \frac{\text{Full-scale voltage for each channel}}{\text{Full-scale voltage average value for each channels}} \right| -1 \times 100 (\%)$

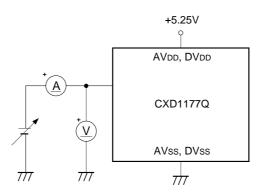

# **Electrical Characteristics Measurement Circuit**

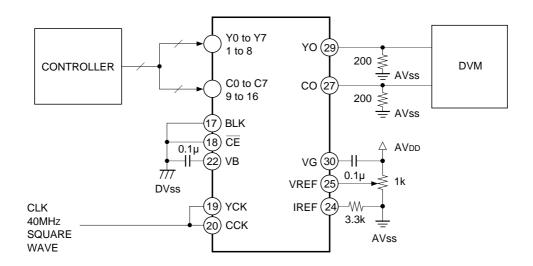

Analog Input Resistance Digital Input Current

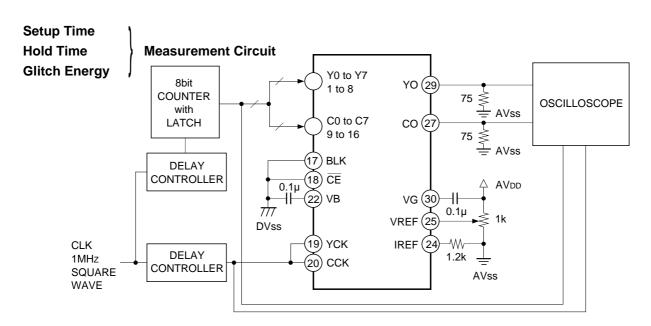

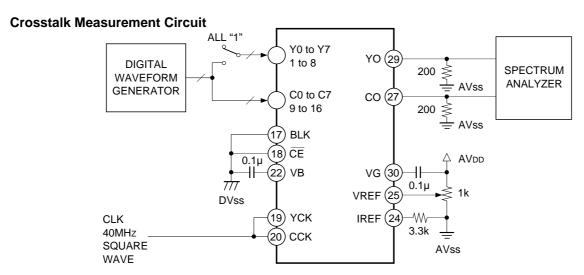

**Measurement Circuit**

$<sup>^{*2}</sup>$  When the external capacitors for the VG pins are 0.1  $\mu$ F.

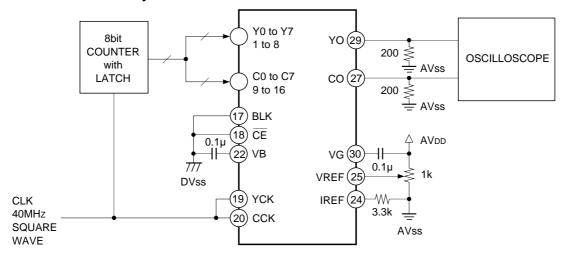

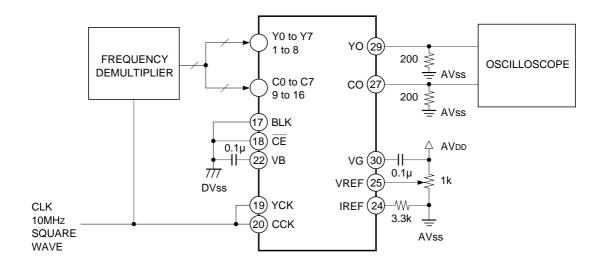

### **Maximum Conversion Velocity Measurement Circuit**

# **DC Characteristics Measurement Circuit**

# **Propagation Delay Time Measurement Circuit**

# **Description of Operation**

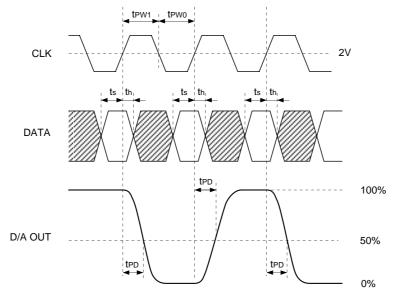

# **Timing Chart**

I/O Chart (When full-scale output voltage at 2.00 V)

| Input | code    | Output voltage |

|-------|---------|----------------|

| MSB   | LSB     |                |

| 1111  | 1 1 1 1 | 2.0 V          |

|       | :       |                |

| 1000  | 0 0 0 0 | 1.0 V          |

|       | :       | 0.1/           |

| 0000  | 0 0 0 0 | 0 V            |

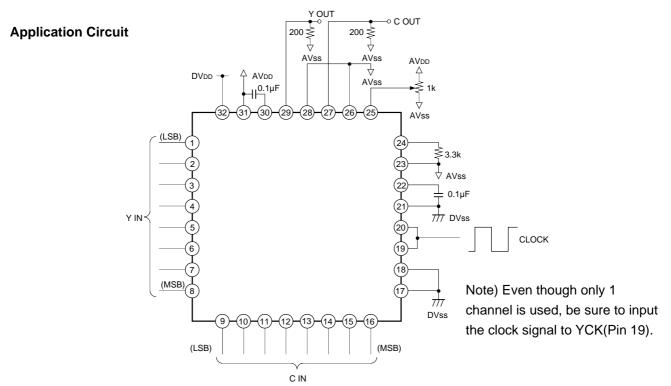

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

#### **Notes on Operation**

#### • How to select the output resistance

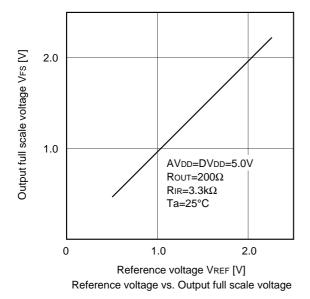

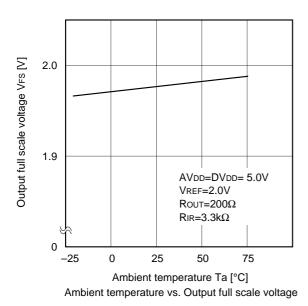

The CXD1177Q is a D/A converter of the current output type. To obtain the output voltage connect the resistance to the current output pins Y0, C0. For specifications we have;

Output full scale voltage VFS = 1.8 to 2.2 [V]

Output full scale current | IFS = less than 15 [mA]

Calculate the output resistance value from the relation of VFs = IFs  $\times$  Rout. Also, 16 times resistance of the output resistance is connected to reference current pin IREF. In some cases, however, this turns out to be a value that does not actually exist. In such a case a value close to it can be used as a substitute. Here please note that VFs becomes VFs = VREF  $\times$  16Rout/Rir. Rout is the resistance connected to the current output pins YO and CO while Rir is connected to IREF. Increasing the resistance value can curb power consumption. On the other hand glitch energy and data settling time will inversely increase. Set the most suitable value according to the desired application.

#### Phase relation between data and clock

To obtain the expected performance as a D/A converter, it is necessary to set properly the phase relation between data and clock applied from the exterior. Be sure to satisfy the provisions of the setup time (ts) and hold time (th) as stipulated in the Electrical Characteristics.

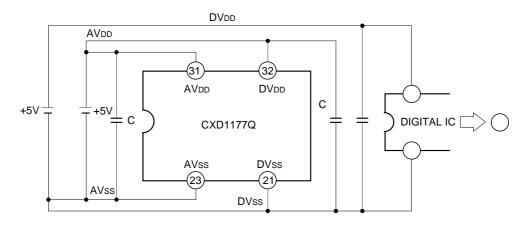

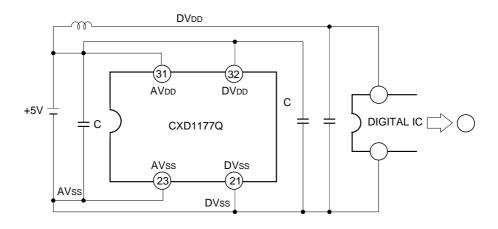

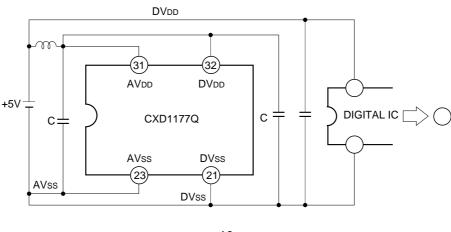

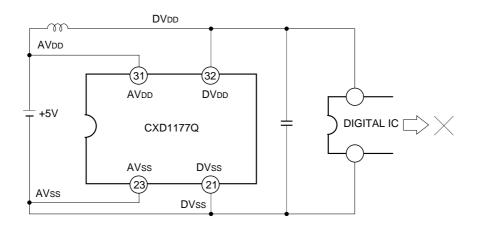

### · Power supply and grand

To reduce noise effects separate analog and digital systems in the device periphery. For the power supply pins, both digital and analog, bypass respective grounds by using a ceramic capacitor of about 0.1  $\mu$ F, as close as possible to the pin.

### Latch up

AVDD and DVDD have to be common at the PCB power supply source. This is to prevent latch up due to voltage difference between AVDD and DVDD pins when power supply is turned ON.

### YO and IO pins

The YO and IO pins are the inverted current output pins described in the Pin Description. The sums shown below become the constant value for any input data.

- a) The sum of the currents output form YO and  $\overline{YO}$

- b) The sum of the currents output form CO and CO

However, the performances such as the linearity error of the inverted current output pin output current is not guaranteed.

#### Clock input signal

Even though only 1 channel is used, be sure to input the clock signal to YCK(Pin 19).

# **Latch Up Prevention**

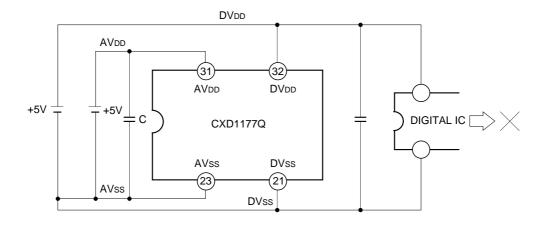

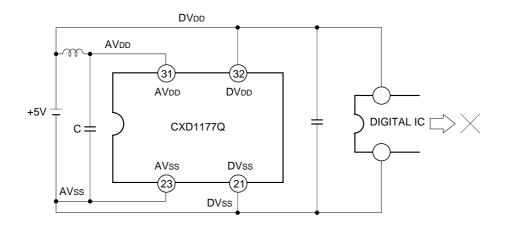

The CXD1177Q is a CMOS IC which requires latch up precautions. Latch up is mainly generated by the lag in the voltage rising time of AVDD (Pin 31) and DVDD (Pin 32), when power supply is ON.

# 1. Correct usage

# a. When analog and digital supplies are from different sources

# b. When analog and digital supplies are from a common source

(i)

(ii)

- 2. Example when latch up easily occurs

- a. When analog and digital supplies are from different sources

# b. When analog and digital supplies are from common source

(i)

(ii)

# **Example of Representative Characteristics**

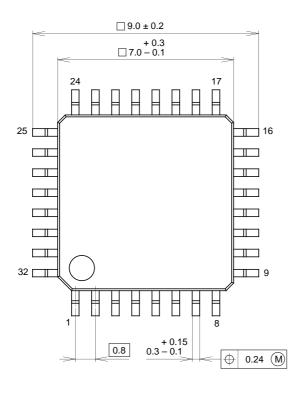

# Package Outline Unit: mm

# 32PIN QFP (PLASTIC)

| SONY CODE  | QFP-32P-L01   |

|------------|---------------|

| EIAJ CODE  | QFP032-P-0707 |

| JEDEC CODE |               |

| PACKAGE MATERIAL | EPOXY RESIN    |

|------------------|----------------|

| LEAD TREATMENT   | SOLDER PLATING |

| LEAD MATERIAL    | 42 ALLOY       |

| PACKAGE MASS     | 0.2g           |