# $\mu$ A212AT 1200/300 bps Full Duplex Modem

# **General Description**

The  $\mu$ A212AT single-chip modem IC performs all signal processing functions required for a Bell 212A/103 compatible modem. Handshaking protocols, and mode control functions are provided by a general purpose single-chip  $\mu$ C. The  $\mu$ A212AT and  $\mu$ C, along with several components to handle the control and telephone line interfaces, provide a high performance, cost-effective solution for an intelligent Bell 212A-compatible modem design.

The modem chip performs the modulation, demodulation, filtering and certain control and self-test functions required for a Bell 212A-compatible modem, as well as additional functional enhancements. Switched capacitor filters provide channel isolation, spectral shaping and fixed compromise equalization for both high and low speed modes.

A novel switched-capacitor modulator and a digital coherent demodulator provide 1200 bps QPSK operation while a separate digital FSK modulator and demodulator handle the 0-300 bps requirement. The  $\mu$ A212AT includes an integral DTMF tone generator on-chip. The receive filter and energy detector may be configured for call progress tone detection (dialtone, busy, ringback, voice), providing the front end for a smart dialer

The µA212AT is fabricated in an advanced Double-Poly Silicon-Gate CMOS process.

### **Features**

- Functions as a 212A and 103 compatible modem

- Performs all signal processing functions

- Interfaces to single chip µC which handles handshaking protocols and mode control functions

- DTMF tone generation

- $\blacksquare$  Pin and firmware compatible with the  $\mu$ A212A (without integral DTMF) for easy upgrade

- Call progress tone detection for smart dialer applications

- On chip oscillator uses standard 3.6864 MHz crystal

- Few external components required

- Operates from +5V and -5V supplies

- Low operating power: 35 mW typical

- 28-lead ceramic DIP, 28-lead plastic DIP, and 28-lead surface mount packages

- µA212AT designer's kit is available

## **Connection Diagram**

TL/H/9430-1 **Top View**

\*Molded Dual-In-Line Package Order Number μΑ212ΑΤQC See NS Package Number V28Α

\*Ceramic Dual-In-Line Package Order Number μA212ATDC See NS Package Number F28B

28-Lead PLCC

(Pin numbers same as 28-lead DIP)

Order Number μA212ATDC, μA212ATQC See NS Package Number N28B

\*For most current package information contact product marketing. For most current order information, contact you local sales office.

# **Absolute Maximum Ratings\***

If Military/Aerospace specified devices are required, contact the National Semiconductor Sales Office/Distributors for availability and specifications.

VDD to DGND or AGND

+7.0V

VSS to DGND or AGND

−7.0V

Voltage at Any Input

VDD + 0.3V to

Voltage at Any Digital Output  $V_{DD} + 0.3V$  to DGND -0.3V

Voltage at Any Analog Output V

$V_{DD} + 0.3V$  to  $V_{SS} - 0.3V$

Operating Temperature Range

Storage Temperature Range

0°C to 70°C -65°C to +150°C

Lead Temperature (soldering, 10 seconds)

300°C

\*Note: Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**Electrical Characteristics** unless otherwise noted:  $V_{DD}=5.0V$ ,  $V_{SS}=-5.0V$ , DGND=AGND=0V,  $T_A=25^{\circ}C$ ; all digital signals are referenced to DGND, all analog signals are referenced to AGND

### **ENERGY DETECTOR**

| Symbol            | Parameter                                                                                               | Conditions                                  | Min       | Тур        | Max       | Units             |

|-------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------|-----------|------------|-----------|-------------------|

| V <sub>thon</sub> | Data Mode<br>OFF/ON Threshold<br>ON/OFF Threshold                                                       | Voltage Level at RXIN<br>Pin In Data Mode   |           | 6.5<br>5.2 | •         | mV <sub>rms</sub> |

| t <sub>on</sub>   | Energy Detect Time Loss of Energy Detect Time                                                           | At EDET Pin                                 | 105<br>10 | 155<br>17  | 205<br>24 | ms<br>ms          |

| V <sub>thon</sub> | Dialer Mode OFF/ON Threshold (Dialtone) ON/OFF Threshold (Busy/Ringback)                                | Voltage Level at RXIN<br>Pin In Dialer Mode |           | 10<br>4.6  |           | mV <sub>rms</sub> |

| t <sub>on</sub>   | Energy Detect in the Dialer Mode<br>(Detecting Call Progress Tones)<br>Energy Detect in the Dialer Mode | At EDET Pin                                 | 25<br>30  | 30<br>36   | 35<br>42  | ms<br>ms          |

| t <sub>off</sub>  | (Detecting Call Progress Tones)                                                                         |                                             | <u> </u>  |            | l         |                   |

### ANALOG LINE INTERFACE

| Symbol                                 | Parameter                                                           | Conditions     | Min  | Тур  | Max  | Units                   |

|----------------------------------------|---------------------------------------------------------------------|----------------|------|------|------|-------------------------|

|                                        | Output Level at TXO: Data Mode                                      |                | 0.66 | 0.71 | 0.76 | V <sub>rms</sub>        |

| V <sub>line</sub> (Note 1)             | Output Level at TXO: Data Mode Output Level at TXO: DTMF HIGH Group |                | 1.02 | 1.1  | 1.18 | V <sub>rms</sub>        |

| V <sub>tonh</sub> (Note 1)             | Output Level at TXO: DTMF LOW Group                                 |                | 0.84 | 0.9  | 0.97 | V <sub>rms</sub>        |

| V <sub>tonl</sub> (Note 1)             | Output Level at TXO: TXSQ Active                                    |                |      | 0.3  | ļ    | mV <sub>rms</sub>       |

| VTXSQ<br>P <sub>ext</sub>              | Extraneous Frequency Output Relative to                             | Any DTMF Digit |      |      | -20  | dB                      |

| Voo                                    | DTMF power Output Offset                                            | At TXO         |      | 5.0  |      | mV                      |

| V <sub>RXIN</sub><br>Z <sub>RXIN</sub> | Talker Echo and Received Signal Input Impedance                     | At RXIN        |      | 100  | 1.56 | V <sub>PEAK</sub><br>kΩ |

Note 1: Output level at TXO will vary directly with VDD supply.

#### **CLOCK INTERFACE**

| Symbol             | Parameter                                 | Conditions                        | Min      | Тур    | Max  | Units    |

|--------------------|-------------------------------------------|-----------------------------------|----------|--------|------|----------|

| F <sub>clock</sub> | Clock Frequency Clock Frequency Tolerance |                                   | 01       | 3.6864 | +.01 | MHz<br>% |

| V <sub>exth</sub>  | External Clock Input HIGH                 | XTAL2 Driven and XTL1<br>Grounded | 4.5      |        |      | V        |

| V <sub>extl</sub>  | External Clock Input LOW                  | Giodinada                         | <u> </u> |        | 0.5  |          |

**Electrical Characteristics** unless otherwise noted:  $V_{DD} = 5.0V$ ,  $V_{SS} = -5.0V$ , DGND = AGND = 0V,  $T_A = 25^{\circ}$ C; all digital signals are referenced to DGND, all analog signals are referenced to AGND (Continued)

### DIGITAL INTERFACE

| Symbol                             | Parameter                                 | Conditions                                                       | Min | Тур | Max  | Units  |

|------------------------------------|-------------------------------------------|------------------------------------------------------------------|-----|-----|------|--------|

| V <sub>IL</sub><br>V <sub>IH</sub> | Input Voltage LOW<br>Input Voltage HIGH   |                                                                  | 2.2 |     | 0.6  | V<br>V |

| V <sub>OL</sub><br>V <sub>OH</sub> | Output Voltage LOW<br>Output Voltage HIGH | $I_L = 1.6 \text{ mA}$ $I_L = -2.0 \text{ mA}$                   | 3.0 |     | 0.6  | V<br>V |

| I <sub>IL</sub>                    | Input Current LOW                         | DGND ≤ V <sub>IN</sub> ≤ V <sub>IL</sub> ,<br>All Digital Inputs |     |     | -100 | μΑ     |

| l <sub>IH</sub>                    | Input Current HIGH                        | V <sub>IH</sub> ≤ V <sub>IN</sub> ≤ V <sub>DD</sub>              | +50 |     |      | μА     |

### **POWER INTERFACE**

| Symbol | Parameter         | Conditions        | Min | Тур  | Max  | Units |

|--------|-------------------|-------------------|-----|------|------|-------|

| IDD    | Operating Current | No Analog Signals |     | 4.3  | 10   | mA    |

| Iss    | Operating Current | No Analog Signals | 1   | -2.7 | -5.0 | mA    |

### TRANSMIT (ASYNC/SYNC) AND RECEIVE (SYNC/ASYNC) BUFFERS

| Symbol              | Parameter                            | Conditions                          | Min    | Тур     | Max  | Units |

|---------------------|--------------------------------------|-------------------------------------|--------|---------|------|-------|

| М                   | Input Character Length               | Start Bit + Data<br>Bits + Stop Bit | 8      |         | 11   | Bits  |

| Rtxchar             | Input Intracharacter Signaling Rate  | At TXD Pin                          | 1170   | 1200    | 1212 | bps   |

| L <sub>break</sub>  | Input Break Sequence Length          | At TXD Pin                          | М      |         |      | Bits  |

| L <sub>brkseq</sub> | Transmitted Break Sequence Length    | At TXO Pin                          | 2M + 3 |         |      | Bits  |

| Ltxchar             | Output Intracharacter Signaling Rate | At RXD Pin                          |        | 1219.05 |      | bps   |

### CARRIER FREQUENCIES AND SIGNALING RATES

| Symbol                                                    | Parameter                                                                       | Conditions                                                                                                        | Min   | Тур                                  | Max   | Units            |

|-----------------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-------|--------------------------------------|-------|------------------|

| F <sub>cxr</sub> (ORIG)<br>F <sub>cxr</sub> (ANS)<br>Baud | HS Cxr Freq. (Orig. Mode)<br>HS Cxr Freq. (Ans. Mode)<br>Dibit Rate             | $HS = 1, O/\overline{A} = 1$ $O/\overline{A} = 0$                                                                 |       | 1200<br>2400<br>600                  |       | Hz<br>Hz<br>Baud |

| F <sub>mark</sub> (ORIG)<br>F <sub>space</sub> (ORIG)     | Mark Frequency, Originate Mode (1270)<br>Space Frequency, Originate Mode (1070) | $HS = 0, O/\overline{A} = 1, \overline{TXD} = 1$ $\overline{TXD} = 0$                                             |       | 1269.42<br>1066.67                   |       | Hz<br>Hz         |

| F <sub>mark</sub> (ANS)                                   | Mark Frequency, Answer Mode (2225)                                              | $\begin{aligned} & \text{HS} = 0, \text{O}/\overline{\text{A}} = 0, \\ & \overline{\text{TXD}} = 1 \end{aligned}$ |       | 2226.09                              |       | Hz               |

| F <sub>anstone</sub>                                      | Answer Tone (2225)                                                              | TEST = 1,<br>HSK1 = HSK2 = 0                                                                                      |       | 2226.09                              |       | Hz               |

| F <sub>space</sub> (ANS)                                  | Space Frequency, Answer Mode (2025)                                             | $HS = 0, O/\overline{A} = 0,$ $\overline{TXD} = 0$                                                                |       | 2021.05                              |       | Hz               |

| F <sub>tonl</sub>                                         | DTMF Low Frequency Tone Group                                                   | Dialer Mode<br>TEST = HSK1 = HSK2 = 0                                                                             |       | 698.2<br>771.9<br>853.3<br>942.3     |       | Hz               |

| F <sub>tonh</sub>                                         | DTMF High Frequency Tone Group                                                  | Dialer Mode<br>TEST = HSK1 = HSK2 = 0                                                                             |       | 1209.4<br>1335.7<br>1476.9<br>1634.0 |       | Hz               |

| Tol                                                       | Tolerance of Above<br>Frequencies/Signaling Rates                               |                                                                                                                   | -0.01 |                                      | +0.01 | %                |

| bps                                                       | Data Rate                                                                       | Low-Speed Mode                                                                                                    | 0     |                                      | 300   | bps              |

**Electrical Characteristics** unless otherwise noted:  $V_{DD} = 5.0V$ ,  $V_{SS} = -5.0V$ , DGND = AGND = 0V,  $T_A = 25^{\circ}$ C; all digital signals are referenced to DGND, all analog signals are referenced to AGND (Continued)

### SYSTEM PERFORMANCE

| SYSTEMPEN                         | Parameter                                                                                                                                                                                                                                                                                      | Conditions                                                                                                               | Min | Тур | Max | Units    |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|----------|

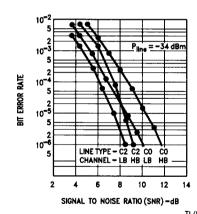

| BER<br>(High-<br>Band<br>Receive) | Bit Error Rate: SNR required for BER = 10 <sup>-5</sup> @ 1200 bps on a 3002–C0 line, with 5 kHz white noise referred to 3 kHz. Values shown are for originate mode. (Note: Pline values assume 4 dB net gain from line to RXIN. Net gain varies with DAA type and design). (See Figures 2, 3) | P <sub>line</sub> = -34 dBm<br>P <sub>line</sub> -44 dBm                                                                 | 10  |     |     | dB<br>dB |

|                                   | Telegraph Isochronous Distortion                                                                                                                                                                                                                                                               | Back-to-Back, 300 bps<br>(Low-Speed Mode)                                                                                |     | 10  |     | % Peak   |

| Fos                               | Frequency offset: Incoming Carrier<br>Frequency Offset Acquirable by<br>1200 bps Receiver                                                                                                                                                                                                      | Zero Errors in 10 <sup>5</sup> Bits,<br>Originate/Answer Modes,<br>Flat, C0 and C2 Lines.<br>P <sub>line</sub> = -40 dBm |     | ±6  |     | Hz       |

# **Pin Descriptions**

| Pin<br>No. | Pin<br>Name | Description                                                                                                                                                                                                                                                                                                                                                       |

|------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 2        | SLIM        | Connect external capacitor between pins 1 and 2 (Note 3).                                                                                                                                                                                                                                                                                                         |

| 3          | RXIN        | Line signal to modem; usually from 2-<br>wire/4-wire hybrid. AC coupling is<br>recommended. (Note 3)                                                                                                                                                                                                                                                              |

| 4          | DOT         | Test pattern. In Data (TEST = 1) or Analog Loop modes, substitutes a dotting pattern for TXD and overrides SYNC, MOD1 and MOD2. If HS = 1, provides a 1200 bps dotting pattern (600 Hz square wave), and places RCVR and XMTR in SYNC mode with internal clock source. If HS = 0, provides a 155 bps dotting pattern. 1 = normal transmit data path, 0 = dotting. |

| 5          | ETC         | External Transmit Clock. 1200 Hz external clock providing XMTR timing in SYNC mode, selected by MOD1, MOD2 pins. TXD changes on negative edge, sampled on positive edge. Provided on SCT pin if selected.                                                                                                                                                         |

| 6          | SYNC        | Selects CHAR ASYNC or BIT SYNC mode. 1 = ASYNC mode: enables XMIT & RCV buffers, sets character length according to MOD1, MOD2 pins. 0 = SYNC mode: disables buffers, selects TX clock source according to MOD1, MOD2 pins. Active only if HS = 1.                                                                                                                |

| 7          | EDET        | Energy Detect. In data mode, EDET = 0 if valid signal above threshold is present for 155 ms ±50 ms, EDET = 1 if signal below threshold for >17 ms ±7 ms. In dialer mode, follows on/off variations of call-progress tones, wher TXSQ = 0.                                                                                                                         |

| Pin<br>No. | Pin<br>Name    | Description                                                                                                                                                                                                                                                                |

|------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8          | HS<br>(Note 1) | Selects modem speed. 1 selects 1200 bps. 0 selects 300 bps.                                                                                                                                                                                                                |

| 9          | SCRM           | Scrambler. "0" disables scrambler and descrambler for testing purposes.                                                                                                                                                                                                    |

| 10         | TXD            | XMIT Data. Serial data from host or<br>UART. Disconnected when digitally<br>looped, or in dialer, dotting answer<br>tone or force continuous mark or<br>space modes.                                                                                                       |

| 11<br>12   | XTL2<br>XTL1   | Frequency control. 3.6864 MHz Pierce crystal oscillator. XTL2 can be driven by external 5V logic, with XTL1 grounded. XTL2 can drive external logic through AC coupled buffer.                                                                                             |

| 13         | SCR            | Serial Clock Receive. In SYNC mode, 1200 Hz bit clock recovered from RCVD signal. May be pin-selected (MOD1, MOD2) as local transmit clock (SLAVE mode); provided on SCT pin if selected. RXD changes on negative edge, sampled on positive edge. Undefined in ASYNC mode. |

| 14         | RXD            | RCVD Data. Serial data to host, internally clamped to mark (= 1) when modem is in digital loop or EDET in inactive (= 1).                                                                                                                                                  |

### Pin Descriptions (Continued)

| Pin<br>No.     | Pin<br>Name                          | Description                                                                                                                                                                                                                                                                                                                                            |

|----------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15             | RLST                                 | Remote Loop Status, used in RDL mode. Responding modem: sets RLST = 0 upon receipt of unscrambled mark for 154 ms-231 ms. Initiating modem: asserts RLST = 0 upon receipt of scrambled mark for 231 ms-308 ms. (See Table III).                                                                                                                        |

| 16<br>17<br>19 | HSK1<br>HSK2<br>TEST                 | When the TEST pin is inactive (high), HSK1 and HSK2 select one of four transmit conditions, for use when programming the Handshake sequences. (See Table I). When TEST is active (low), the HSK1 and HSK2 pins select one of three test conditions, or, alternatively, the dialer mode used for call progress tone detection and DTMF tone generation. |

| 18             | DGND                                 | Digital Ground                                                                                                                                                                                                                                                                                                                                         |

| 20<br>21       | MOD2<br>(Note 1)<br>MOD1<br>(Note 1) | Selects character length (ASYNC) or TX clock (SYNC). In ASYNC mode, selects 8-, 9-, 10- or 11-bit character length; in SYNC mode, selects internal, external or recovered RCV clock as XMTR data clock source. Active only if HS = 1. (See Table I)                                                                                                    |

| 22             | SCT                                  | Serial Clock Transmit. 1200 Hz clock output providing XMTR timing in SYNC mode. SCT source (INT., EXT., SLAVE) selected by MOD1, MOD2 pins. TXD changes on negative edge, sampled on positive edge. Internal clock provided in ASYNC mode.                                                                                                             |

| 23             | TXSQ<br>(Note 2)                     | Squelch XMTRS in data mode. 0 = Both XMTRS off; 1 = turns on XMTR selected by HS pin. In dialer mode, 0 = DTMF generator OFF/Call progress detection. 1 = DTMF generator ON.                                                                                                                                                                           |

| 24             | O/Ā<br>(Note 1)                      | Orig/Answer Mode Select. Assigns channels to XMTRS/RCVRS. 1 = Originate mode, 0 = Answer mode.                                                                                                                                                                                                                                                         |

| 25             | TXO                                  | Transmit line signal from modem; usually to 2-wire/4-wire line hybrid input. AC coupling is recommended (Note 3).                                                                                                                                                                                                                                      |

| 26             | AGND                                 | Analog Ground                                                                                                                                                                                                                                                                                                                                          |

| 27             | V <sub>SS</sub>                      | Negative power supply V <sub>SS</sub> = −5.0V                                                                                                                                                                                                                                                                                                          |

| 28             | V <sub>DD</sub>                      | Positive power supply $V_{DD} = +5.0V$                                                                                                                                                                                                                                                                                                                 |

Note 1: For  $\mu$ A212AT in dialer mode with  $\overline{TXSQ}=1$ , O/ $\overline{A}$ , HS, MOD1 and MOD2 select the desired DTMF tone pair.

Note 2: The  $\mu$ A212AT is pin and function compatible with the  $\mu$ A212A (without integral DTMF); in upgrade applications, insure proper state of  $\overline{TXSQ}$  as indicated. See Technical Bulletin M-1.

Note 3: Capacitors in signal paths should be  $\geq 0.033~\mu\text{F}$  and have  $\sim$  zero voltage coefficients.

## **Functional Description\***

Refer to Figure 1.

### TRANSMITTER

The transmitter consists of high-speed and low-speed modulators, a transmit buffer and scrambler, and a transmit filter and line driver. In high-speed asynchronous mode, serial transmit data from the host or UART enters the transmit buffer, which synchronizes the data to the internal 1200 bps clock. Data which is underspeed relative to 1200 bps periodically has the last stop bit sampled twice resulting in an added stop bit. Similarly, overspeed input data periodically has unsampled-and therefore deleted-stop bits. The MOD1 and MOD2 pins choose 8-, 9-, 10- or 11-bit character lengths. In synchronous mode the transmit buffer is disabled. The transmitter clock source may be chosen by MOD1 and MOD2: internal, external or derived from the recovered received data. A scrambler precedes encoding to ensure that the line spectrum is sufficiently distributed to avoid interference with the in-band supervisory single-frequency signaling system employed in most Bell System toll trunks. The randomized spectrum also facilitates timing recovery in the receiver. The scrambler is characterized by the following recursive equation:

$$Y_i = X_i \oplus Y_{i-14} \oplus Y_{i-17}$$

where  $X_i$  is the scrambler input bit at time i,  $Y_i$  is the scrambler output bit at time i and  $\oplus$  denotes the XOR operation. 212A-type modems achieve full-duplex 1200 bps operation by encoding transmitted data by bit-pairs (dibits), thereby halving the apparent data rate. The resultant reduced spectral width allows both frequency channels to coexist in a limited bandwidth telephone channel with practical levels of filtering. The four unique dibits thus obtained are gray-coded and differentially phase modulated onto a carrier at either 1200 Hz (originate mode) or 2400 Hz (answer mode). Each dibit is encoded as a phase change relative to the phase of the preceding signal dibit element:

| Dibit | Phase Shift (deg) |

|-------|-------------------|

| 00    | + 90              |

| 01    | 0                 |

| 11    | -90               |

| 10    | 180               |

|       |                   |

At the receiver, the dibits are decoded and the bits are reassembled in the correct sequence. The left-hand digit of the dibit is the one occurring first in the data stream as it enters the modulator after the scrambler. The lowspeed transmitter generates phase-coherent FSK using one of two programmable tone generators. Answer mode mark (2225 Hz) is also utilized as answer tone in both low- and high-speed operation.

In Dialer mode, both tone generators are employed to generate DTMF tone pairs. The summed modulator outputs drive a lowpass filter which serves as a fixed compromise amplitude and delay equalizer for the phone line and reduces output harmonic energy well below maximum specified levels. The filter output drives an output buffer amplifier with low output impedance. At the TXO pin, the buffer provides 700 mVrms in data mode, for a nominal -9 dBm level at the line, assuming 2 dB loss in the data access arrangement.

<sup>\*</sup>For additional information ask for Applications Note ASP-1 "Theory of Operation—μA212A" and Technical Bulletins M1, M3 & M4.

# Functional Description\* (Continued)

### DIME TONE GENERATION

The  $\mu$ A212AT includes on-chip DTMF generation, using two programmable tone generators. Dialer mode must be selected (TEST = HSK1 = HSK2 = 0) for DTMF dialing. The O/Ā, HS, MOD1 and MOD2 pins are used to select the required digit according to the encoding scheme shown in Table II, and the tones are turned on and off by the logic level on  $\overline{\text{TXSO}}$ . The generated tones meet the applicable CCITT and EIA requirement for tone dialing. DTMF output levels are 0.9 Vrms (low group) and 1.1 Vrms (high group).

#### RECEIVER

The received signal from the line-connection circuitry passes through a lowpass filter which performs anti-aliasing and compromise amplitude and delay equalization of the incoming signal. Depending upon mode selection (originate/answer) the following mixer either passes or down converts the signal to the 1200 Hz bandpass filter. In analog loopback mode, the receiver originate and answer mode assignments are inverted, which forces the receiver to operate in the transmitter frequency band. The 1200 Hz bandpass filter passes the desired received signal while attenuating the adjacent transmitted signal component reflected from the line (talker echo). The chosen passband shape converts the spectrum of the received high-speed signal to 100% raised cosine to minimize intersymbol interference in the recovered data. Following the filter is a soft limiter and a signal energy detector. An external capacitor is used to eliminate offset between the soft limiter output and the following limiter.

The against detector provides a digital indication that energy

derspeed data presented to the transmitting modem passes essentially unchanged through the receive buffer.

Overspeed data, which had stop bits deleted at the transmitter, has those stop bits reinserted by the receive buffer. (Generally, stop bit lengths will be elastic). The receive buffer output is then presented to the receive data pin (RXD) at a nominal intracharacter rate of 1219.05 bps.

# MASTER CLOCK/OSCILLATOR/DIVIDER CHAIN

The µA212AT may be controlled by either a quartz crystal operating in parallel mode or by an external signal source at 3.6864 MHz. The crystal should be connected between XTL1 and XTL2 pins, with a mica or high-Q ceramic 30 pF capacitor from each pin to digital ground (See Figure 1). An external circuit may be driven from XTL2. In this case, AC coupling to a high impedance load should be used. Note that total capacitance to ground from XTL2, including such an external circuit, should be 30 pF. Crystal requirements;  $R_{\mbox{\scriptsize S}} <$  150  $\!\Omega,\, C_{\mbox{\scriptsize L}} =$  18 pF, parallel mode, tolerance (accuracy, temperature, aging) less than ±75 ppm. An external TTL drive may be applied to the XTL2 pin, with XTL1 grounded. Internal divider chains provide the timing signals required for modulation, demodulation, filtering, buffering, encoding/decoding, energy detection and remote digital loopback. Timing for line connect and disconnect sequences (handshaking) derives from the host controller, ensuring maximum applications flexibility.

# **Control Considerations**

The host controller, whether a dedicated microcontroller or a diagital interface, controls the  $\mu$ A212AT as well as the line

# 5

### **Control Considerations** (Continued)

Answer Tone In this mode, 2225 Hz answer tone is

transmitted provided TXSQ is inactive high (= 1). Receive data rate is selected as normal with the HS pin. This permits the data rate of the originating modem to be determined while answer tone is

continuously transmitted.

Force Continuous Mark Disconnects TXD pin from the transmitter and forces the signal internally to a mark (logic 1).

nark (logic 1)

Force Continuous Space Disconnects TXD pin from the transmitter and forces the signal internally to a space (logic 0).

Analog Loop Receiver is for

Receiver is forced to the transmitter channel. With modem on-hook (disconnected from line) signal from TXO is reflected through hybrid to RXIN.

Local Digital Loop Forces synchronous mode, and internally loops received data to transmitter and SCR to SCT. Transmitted data (TXD) and clock (ETC) are ignored. SCR and SCT are provided. RXD is forced to 1.

Remote Digital Loop Initiating modem: If RDL is initiated (TEST = 0, HSK1 = 1, HSK2 = 0), TXD is isolated, RXD is clamped to a 1 and unscrambled mark is transmitted.

When high speed scrambled dotting pattern is detected, scrambled mark is transmitted. Upon receipt of scrambled mark from responding modem, RLST is set to 0.

Responding modem: Upon receipt of unscrambled mark when in data mode (TEST = HSK1 = HSK2 = 1), RLST is set to 0. Upon detecting this the controller responds by setting TEST and HSK2 to 0, and the  $\mu$ A212AT sets synchronous mode, isolates TXD, clamps RXD to 1, and transmits a 1200 bps scrambled dotting pattern. Upon receipt of a scrambled mark signal, the  $\mu$ A212AT internally loops received data and clock to the transmitter and resets (See Table III).

Dialer Mode

The  $\mu$ A212AT provides DTMF tone generation and energy indication at EDET pin to identify call progress tones, i.e. dial, busy and ringback. The DTMF digit is selected by the levels on O/Ā, HS, MOD1 and MOD2 according to Table II. Tone generation is turned on and off by the level on TXSQ. 1 = on, 0 = off.

| TABLE I. Operating and Test Modes |          |      |              |      |      |      |      |                                    |     |  |

|-----------------------------------|----------|------|--------------|------|------|------|------|------------------------------------|-----|--|

| DOT                               | HS       | SYNC | MOD1         | MOD2 | TEST | HSK1 | HSK2 | Description                        | SCT |  |

| 0                                 | _        | х    | Х            | х    | 1    | х    | х    | Dotting Pattern (155 or 1200 bps)  | INT |  |

| 1                                 | <b> </b> |      | _            |      | 1    | 0    | 0    | Answer Tone                        | *   |  |

| 1                                 |          | _    |              | _    | 1    | 0    | 1    | Force Continuous Mark              | ٠   |  |

| 1                                 | _        |      | _            | _    | 1    | 1    | 0    | Force Continuous Space             | •   |  |

| 1                                 | 1        | 1    | 0            | 0    | 1    | 1    | 1    | ASYNC, 8-Bit                       | INT |  |

| 1                                 | 1        | 1    | 0            | 1    | 1    | 1 1  | 1    | ASYNC, 9-Bit                       | INT |  |

| 1                                 | 1        | 1    | 1            | 1    | 1    | 1    | 1    | ASYNC, 10-Bit                      | INT |  |

| 1                                 | 1        | _ 1  | 1            | 0    | 1    | 1    | 1    | ASYNC, 11-Bit                      | INT |  |

| 1                                 | 1        | 0    | 1            | 1    | 1    | 1    | 1    | SYNC, Internal                     | INT |  |

| 1                                 | 1        | 0    | 1            | 0    | 1    | 1    | 1    | SYNC, Slave                        | SCR |  |

| 1                                 | 1        | 0    | 0            | 1    | 1    | 1    | 1    | SYNC, External                     | ETC |  |

| _                                 | _        | _    | <del>-</del> | _    | 0    | 0    | 1    | Analog Loop                        | *   |  |

| 1                                 | _        | Х    | Х            | х    | 0    | 1    | 1    | Local Digital Loop                 | SCR |  |

| 1                                 | 1        |      | _            | _    | 0    | 1    | 0    | Remote Digital Loop Initiate       | *   |  |

| 1                                 | 1        | X    | х            | ×    | 0    | 1    | 0    | Respond to Far End Request for RDL | SCR |  |

| 1                                 | Х        | Х    | Х            | Х    | 0    | 0    | 0    | Dialer Mode (See Table II)         | •   |  |

| 1                                 | 0        | X    | х            | ×    | _    | _    | _    | Low-Speed Mode                     | INT |  |

### Key:

SCT-TX Buffer and PSK Modulator Clock

SCR-Receive Clock

ETC-External Clock Input

INT-Internal 1200 Hz Clock

X-Don't Care (except avoid SYNC = MOD1 = MOD2 = 0)

——Set as appropriate for desired operating condition.

\*—As set by SYNC, MOD1, MOD2.

TABLE II. DTMF Encoding

| O/A | HS  | MOD1 | MOD2 | DTMF Digit |

|-----|-----|------|------|------------|

| 0   | 0   | 0    | 0    | 0          |

| 0   | 0   | 0    | 1    | 1          |

| 0   | 0   | 1    | 0    | 2          |

| 0   | 0   | 1    | 1    | 3          |

| 0   | 1 1 | 0    | 0    | 4          |

| 0   | 1   | 0    | 1    | 5          |

| 0   | 1   | 1    | 0    | 6          |

| 0   | 1   | 1    | 1    | 7          |

| 1   | 0   | 0    | 0    | 8          |

| 1   | 0   | 0    | 1    | 9          |

| 1   | 0   | 1    | 0    |            |

| 1   | 0   | 1    | 1    | #          |

| 1   | 1   | 0    | 0    | Α          |

| 1   | 1   | 0    | 1    | В          |

| 1   | 1   | 1    | 0    | С          |

| 1   | 1   | 1    | 1    | D          |

Note: TEST, HSK1 and HSK2 must be = 0 for DTMF to operate. (See Table I.)

TL/H/9430-3 FIGURE 2. Bit Error Rate vs Signal-to-Noise Ratio

$\ensuremath{\text{\textbf{Note:}}}$  BER measured in synchronous mode, using an AEA S3A channel simulator.

<u>5\_</u>

| Modem Action                                                                                   | Controller Action | TEST | HSK1 | HSK2 | RLST |  |

|------------------------------------------------------------------------------------------------|-------------------|------|------|------|------|--|

| Data Mode                                                                                      |                   | 11   | 1    | 1    | 1    |  |

| Initiate RDL: Disable scrambler Disconnect TXD Force 1 on RXD Transmit unscrambled mark (U.M.) | "INITIATE RDL"    | 0    | 1    | 0    | 1    |  |

| Recognize Dotting for 231–308 ms<br>Enable scrambler<br>Transmit scrambled mark (S.M.)         |                   |      |      |      |      |  |

| Recognize S.M. for 231–308 ms<br>Connect TXD<br>Unclamp RXD<br>"RDL ESTABLISHED"               |                   | 0    | 11   | 0    | 0    |  |

| Response to far end request: U.M. recognized for 154-231 ms "RDL REQUESTED"                    | "RDL RESPONSE OK" | 0    | 1    | 0    | 0    |  |

| Disconnect TXD Force 1 on RXD Force Sync Slave Mode Transmit Dotting                           |                   |      |      |      |      |  |

| S.M. recognized Internally loop Receiver to Transmitter "RDL ESTABLISHED"                      |                   | 0_   | 1    | 0    | 1    |  |

| Terminate RDL: Reset to Data Mode                                                              | TXSQ active 80 ms | 1    | 1    | 1*   | 0    |  |

\*TEST = HSK1 = HSK2 = 1 may be asserted at any time after "RDL ESTABLISHED" and before terminating.

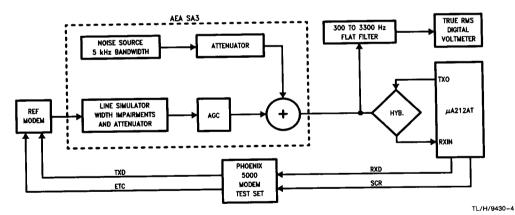

FIGURE 3. 2-Wire Bit Error Test Setup