### Am29540

### Programmable FFT Address Sequencer

### DISTINCTIVE CHARACTERISTICS

- Generates data and coefficient addresses

- Programmable transform length 2 to 65,536 points

- Radix-2 or Radix-4

- In-place or non-in-place transformation

- Decimation in frequency (DIF) or decimation in time (DIT) FFT algorithms supported

- 40-pin DIP package, 5 volt single supply

### GENERAL DESCRIPTION

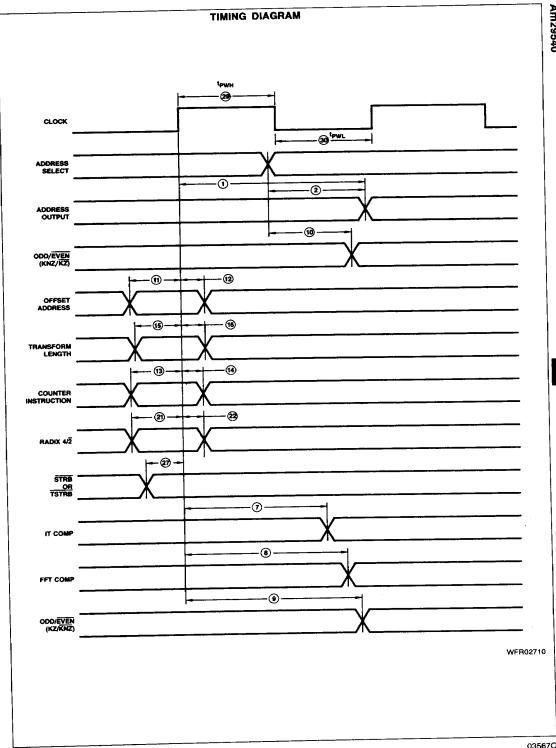

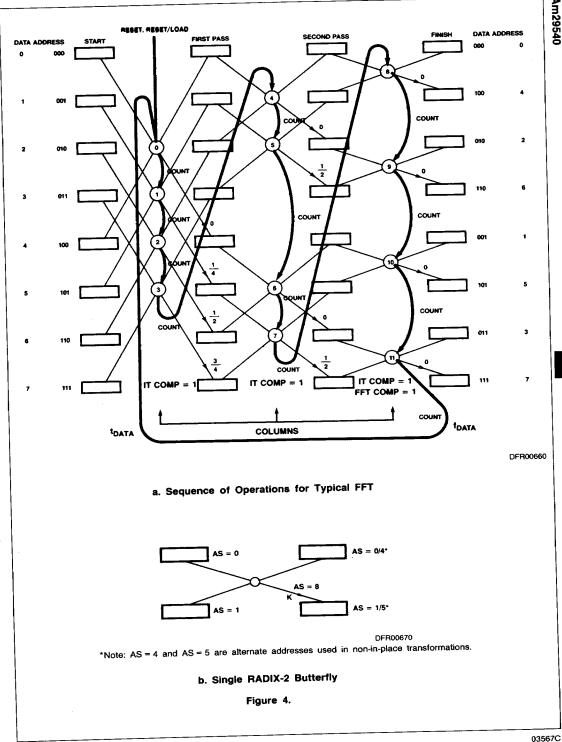

The Am29540 Fast Fourier Transform Address Sequencer generates all the data (RAM) and coefficient (ROM) addresses necessary to perform the repetitive butterfly operations of the FFT. Decimation in time and decimation in frequency algorithms are supported (control DIT/DIF) in radix-2 or radix-4 (RADIX 4/2). A radix-2 real valued input (RVI) transform is also supported. For radix-2 operation the transform length is programmable in powers of 2 from 2 to 65,536 points. In radix-4 the range is 4 to 65,536 in powers of 4.

Address sequences can be selected to be compatible with data which may or may not have been pre-scrambled ('bit-reversed'). If the data has been pre-scrambled the control PSD must be LOW to select the correct sequence. If the data is not pre-scrambled (PSD HIGH) and an in-place transform is performed, the output data will necessarily be in bit-reversed order. If this is not desirable, alternate addresses are available for a non-in-place, non-bit-reversing algorithm.

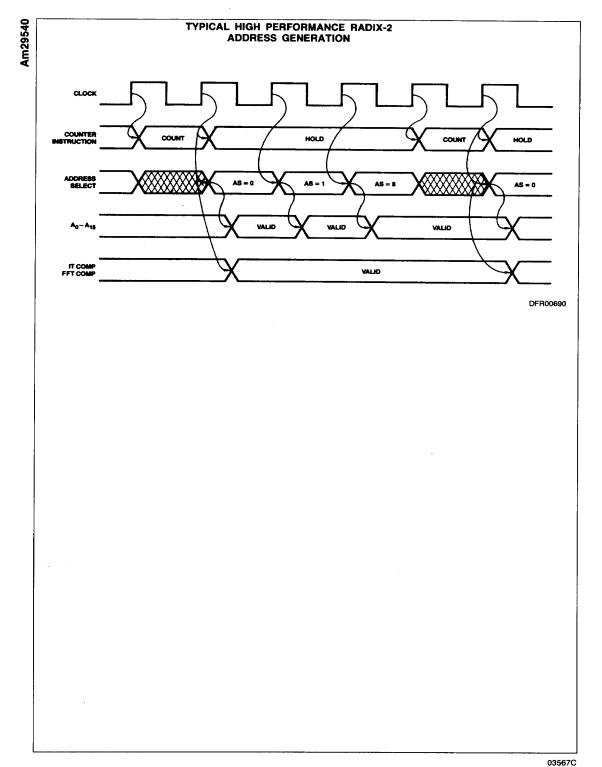

The butterfly counter operates on the positive clock edge and responds to four instructions. COUNT causes the counter to increment to the next butterfly. RESET causes the counter to initialize for the specified transform length. RESET/LOAD causes the counter to initialize and a data address offset to be loaded into the part via the bidirectional 3-state ADDRESS port. This offset is effectively OR-ed onto the higher significant bits of the address which are unused for the selected transform length. A HOLD instruction is also provided. Three status lines are provided. ODD/EVEN (KNZ/KZ) controls the alternation of read and write memories for non-in-place transforms and determines the butterfly structure in the RVI transform. The flag has the function KNZ/KZ when RVI data addresses are selected (AS = 12 to 15). Iteration complete (IT COMP) flags the bottom of a "column" of butterflies and is used in conjunction with block floating point schemes. FFT COMP identifies the last butterfly of the transform.

# BLOCK DIAGRAM TRANSCORM LENGTH TIG\_TL\_2 TESTER OOLATER NOT TOOLET TOOLET ADDRESS SELECT ADDRESS SELECT ADDRESS SELECT ADDRESS SELECT ADDRESS OUTPUT (OFFSET MPVI) BDR02240 FFT Address Sequencer

03567C

### **RELATED PRODUCTS**

|   | Part No.             | Description                                                |

|---|----------------------|------------------------------------------------------------|

| Ī | Am29501              | Multi-port pipelined processor (Byte-slice <sup>TM</sup> ) |

|   | Am29516/17           | 16 x 16 parallel multiplier                                |

| I | Am29520/21           | Multilevel pipeline register                               |

|   | Am29526/<br>27/28/29 | High speed sine/cosine generators                          |

|   | Am29825              | High performance 8-bit register                            |

Byte-Slice is a trademark of Advanced Micro Devices, Inc.

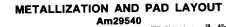

### **CONNECTION DIAGRAM Top View** L-44-1 D-40-1 5 B 2 2 2 2 2 2 2 2 2 2 2 2 2 2 | 158EL | 161R46 | 1740 □ vcc A<sub>12</sub> STAB A13 🗔 DIT/DWF A14 RADIX 4/2 ᅊᄃ □ ггсоми CD004690 CDR04360 Note: Pin 1 is marked for orientation

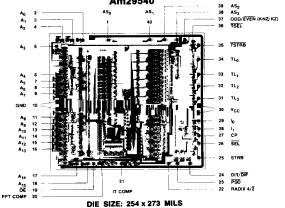

### ORDERING INFORMATION

AMD products are available in several packages and operating ranges. The order number is formed by a combination of the following: Device number, speed option (if applicable), package type, operating range and screening option (if desired).

| Valid Combin | Iations               |

|--------------|-----------------------|

| Am29540 D    | C, DCB, DMB<br>C, LMB |

Valid Combinations

Consult the AMD sales office in your area to determine if a device is currently available in the combination you wish.

### PIN DESCRIPTION

| *Pin No.   | Name                                                                     | 1/0 | Description                                                                                                                                                                                                                                                                                                                         |

|------------|--------------------------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-34      | TL3, TL2<br>TL1, TL0                                                     | 1   | Transform length control determines the number of points to be transformed. (See Figure 1.)                                                                                                                                                                                                                                         |

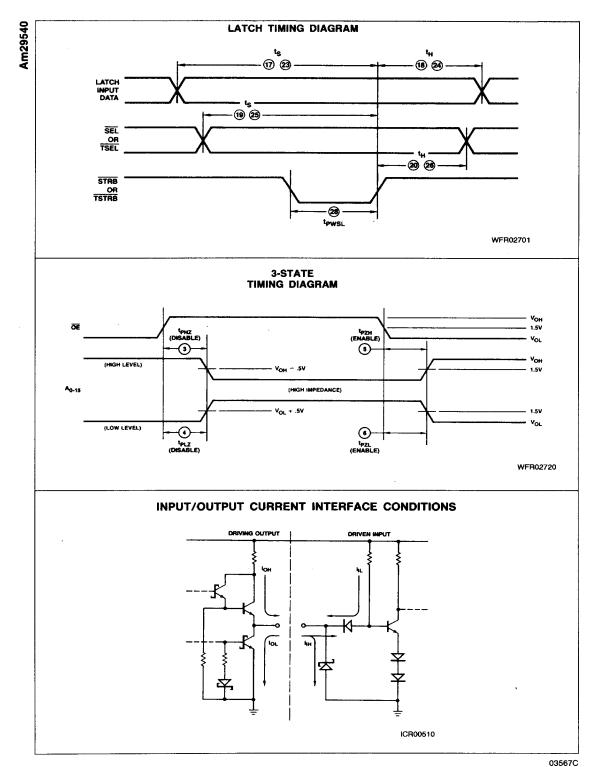

| 36, 35     | TSEL, TSTRB                                                              | 7   | Transform length latch enables. These active LOW inputs are ANDed to control the latch. The latch is transparent when both TSEL and TSTRB are LOW.                                                                                                                                                                                  |

| 29, 28     | lo, 1 <sub>1</sub>                                                       | Ī   | Counter Instruction inputs determine one of four available butterfly counter instructions: Hold, Reset, Reset/Load and Count. (See Figure 2.)                                                                                                                                                                                       |

| 27         | CP                                                                       | ı   | Butterfly counter clock (positive edge active).                                                                                                                                                                                                                                                                                     |

| 22         | Radix 4/2                                                                | 1   | The Radix control determines whether addresses will be generated for Radix-4 (HIGH) for Radix-2 (LOW) transforms.                                                                                                                                                                                                                   |

| 23         | PSD                                                                      | ı   | The Pre-Scrambled Data, PSD, input is used to select an appropriate transform for input data which has previously been digit reversed. Refer to individual transform flow charts for other cases.                                                                                                                                   |

| 24         | DIT/DIF                                                                  | ı   | Control input for selection of the Decimation in Frequency algorithm (LOW) or Decimation In Time algorithm (HIGH).                                                                                                                                                                                                                  |

| 26, 25     | SEL, STAB                                                                | 1   | Transform type (Radix 4/2, PSD, DIF/T) latch enables. These active LOW inputs are ANDed to control the latch. The latch is transparent when both SEL and STRB are LOW.                                                                                                                                                              |

| 1, 38-40   | AS <sub>3</sub> , AS <sub>2</sub> ,<br>AS <sub>1</sub> , AS <sub>0</sub> | 1   | Address Select control determines address selection. (See Figure 3.)                                                                                                                                                                                                                                                                |

| 19         | ō€                                                                       | '   | Three-state output enable. The 3-state output is controlled solely by OE. The output does not automatically become high impedance during the Reset/Load instruction.                                                                                                                                                                |

| 2-9, 11-18 | A <sub>15</sub> -A <sub>0</sub><br>Address Out-<br>put<br>(offset input) | 1/0 | Bidirectional 16-bit port to output selected addresses or to input an address offset.                                                                                                                                                                                                                                               |

| 37         | ODD/EVEN,<br>(KNZ/KZ)                                                    | 0   | For address select 0 to 11 the ODD/EVEN output controls the alternation of separate read and write memories for non-in-place transforms. For Address select 12 to 15 KNZ/KZ = (LOW) indicates that the rotational constant to be used in the RVI transform is W <sup>0</sup> and that an alternative butterfly must be implemented. |

| 20         | FFT COMP                                                                 | 0   | FFT Complete - HIGH identifies the last butterfly (or end) of the transform. (See Figure 4.)                                                                                                                                                                                                                                        |

| 21         | IT COMP                                                                  | 0   | Iteration Complete - HIGH flags the bottom of a 'column' of butterflies. (See Figure 4.)                                                                                                                                                                                                                                            |

\*DIP Configuration

### DETAILED DESCRIPTION

The Am29540 can be pictured as consisting of sixteen 16-bit counters that output on a bidirectional three-state address port,  $A_{15}$ - $A_{0}$ . These sixteen counters generate the data and coefficient addresses required to support the various FFT algorithms.

Decimation-In-Time (DIT) and Decimation-In-Frequency (DIF) algorithms are supported in Radix-2 and Radix-4. Two inputs, DIT/DIF and Radix4/2, control these two parameters without encoding. A third microcode bit, PSD, enables input data to be bit reversed. PSD must be LOW for all transforms with prescrambled (bit reversed) input data. For all in-place transforms with normally-ordered input data. PSD must be HIGH. For all non-in-place DIT transforms, PSD must be LOW, and for all non-in-place DIF transforms, PSD must be HIGH. These three microcode bits can be latched. STRB and SEL are the latch enables. They are ANDed so that the latch is transparent when both are LOW.

The transform length is latched via the TL<sub>3</sub>-TL<sub>0</sub> inputs. TSTRB and TSEL are the latch enables. They are ANDed so that the latch is transparent when both are LOW. For Radix-4 operations, the transform length is programmable in powers of 4, from 4 to 65,536 points. In Radix-2, the range is 2 to 65,536 points in powers of 2. A Radix-2 Real Valued Input (RVI) algorithm is also supported for transform lengths from 2 to 65,536, in powers of 2. Codes to program the transform length are contained in Figure 1.

Two microcode bits,  $l_1-l_0$ , control the operation of the Am29540. The four possible instructions are:

- HOLD. All counters hold their last values. This instruction is used at any time the counter values must remain constant and could be used during initialization of the part.

- RESET. All counters are reset to the start of the transform.

All unused address lines are set to zero. Control bits DIT/ DIF, Radix 4/2 and PSD are unaffected.

- 3. RESET/LOAD. All counters are reset to the start of the transform. All unused address lines are set to the current value of the address port. This allows loading of an offset address via the bidirectional address port. This offset is effectively ORed onto the higher significant bits of the address which are unused for the transform length. Only data address counters are affected. Coefficient address counters are not affected.

- COUNT. All counters are incremented to their next valid address.

Codes for all four instructions are contained in Figure 2.

Four address select controls, AS<sub>3</sub>-AS<sub>0</sub>, choose which of the sixteen counter outputs are available at the address port. Typically, these bits would come from the microcode. Data addresses are right-justified, A<sub>15</sub> being the MSB. Coefficient addresses are left-justified: A<sub>15</sub> is the MSB for Radix-4 operations; A<sub>14</sub> is the MSB for Radix-2 operations. Codes for AS<sub>3</sub>-AS<sub>0</sub> are contained in Figure 3.

Two output flags, ITCOMP and FFTCOMP, indicate counter status. When the bottom of a column of butterflies is reached, Iteration Complete (ITCOMP) goes HIGH. When the last butterfly (or end) of the transform is reached, FFT Complete (FFTCOMP) also goes HIGH. These two flags would typically be condition code inputs to the microprogram sequencer.

A third flag is used to indicate end of column for non-in-place transforms or one of two butterfly types for RVI transforms. For column indication, the flag is called ODD/EVEN and can be used to switch memory banks. The flag will be a HIGH for the last column of butterflies. In the RVI transform the flag is called KNZ/KZ. The equations for the butterfly when the rotational constant is  $\mathbf{W}^0$  are different from when the rotational constant is not  $\mathbf{W}^0$ . When KNZ/KZ is LOW, it indicates that the rotational constant to be used is  $\mathbf{W}^0$  and that the alternative butterfly equations must be executed. Typically there are two microcode segments. The KNZ/KZ flag would be a condition code input to the sequencer to select one of the two segments.

|                 |                 |                 | Tra     | Transform Length                                                                                                                                                                            |                                                                                                                                                                                                                                                     |  |  |

|-----------------|-----------------|-----------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| TL <sub>2</sub> | TL <sub>1</sub> | TL <sub>0</sub> | Radix-2 | Radix-4                                                                                                                                                                                     | RVI                                                                                                                                                                                                                                                 |  |  |

| L               | L               | L               | 2       | 4                                                                                                                                                                                           | 4                                                                                                                                                                                                                                                   |  |  |

| ī               | L               | н               | 4       | 4                                                                                                                                                                                           | 8                                                                                                                                                                                                                                                   |  |  |

| ī               | н               | L               | 8       | 16                                                                                                                                                                                          | 16                                                                                                                                                                                                                                                  |  |  |

| ī               |                 | н               | 16      | 16                                                                                                                                                                                          | 32                                                                                                                                                                                                                                                  |  |  |

| H               | L               | lι              | 32      | 64                                                                                                                                                                                          | 64                                                                                                                                                                                                                                                  |  |  |

| н               | L               | н               | 64      | 64                                                                                                                                                                                          | 128                                                                                                                                                                                                                                                 |  |  |

| 1               | н               | L               | 128     | 256                                                                                                                                                                                         | 256                                                                                                                                                                                                                                                 |  |  |

| 1               | Н               | Н               | 256     | 256                                                                                                                                                                                         | 512                                                                                                                                                                                                                                                 |  |  |

| L               | L               | L               | 512     | 1024                                                                                                                                                                                        | 1024                                                                                                                                                                                                                                                |  |  |

| l ī.            | L               | Н               | 1024    | 1024                                                                                                                                                                                        | 2048                                                                                                                                                                                                                                                |  |  |

| ΙĒ              | н               | L               | 2048    | 4096                                                                                                                                                                                        | 4096                                                                                                                                                                                                                                                |  |  |

| l ī             | lн              | Н               | 4096    | 4096                                                                                                                                                                                        | 8192                                                                                                                                                                                                                                                |  |  |

| lн              | L               | l L             | 8192    | 16384                                                                                                                                                                                       | 16384                                                                                                                                                                                                                                               |  |  |

| 1               | ١ũ              | н               | 16384   | 16384                                                                                                                                                                                       | 32768                                                                                                                                                                                                                                               |  |  |

| H               | H               | lι              | 32768   | 65536                                                                                                                                                                                       | 65536                                                                                                                                                                                                                                               |  |  |

| н               | Н               | Н               | 65536   | 65536                                                                                                                                                                                       | Not Used                                                                                                                                                                                                                                            |  |  |

|                 |                 |                 |         | TL2 TL1 TL0 Radix-2  L L H 4 L H L 8 L H H 16 H L L 32 H L H 64 H H L 128 H H H L 128 H H H L 1256 L L L 512 L L H 1024 L H L 2048 L H H L 2048 L H H H L 3048 L H H H L 3048 H H H L 30768 | TL2 TL1 TL0 Radix-2 Radix-4  L L L L 2 4  L H 4 4  L H 16 16  H L L 32 64  H L H 64 64  H H L 128 256  H H H 15 128 256  L L L 512 1024  L H L 1024 1024  L H L 2048 4096  L H H 4096 4096  H L H 4096 4096  H L H 16384 16384  H H L H 16384 16384 |  |  |

Figure 1. Transform Length Control

| l <sub>1</sub> | l <sub>0</sub> | Counter Function                                                                                                         |

|----------------|----------------|--------------------------------------------------------------------------------------------------------------------------|

| L              | L              | Hold                                                                                                                     |

| L              | н              | Reset. Reset counter to start of transform with unused address outputs set to 0.                                         |

| н              | L              | Reset/Load. Reset counter to start of transform with unused address outputs set to the current value of the address bus. |

| н              | Н              | Count. Increment butterfly counter.                                                                                      |

Figure 2. Counter Instruction Control

| FFT Type                | AS <sub>3</sub> | AS <sub>2</sub> |

|-------------------------|-----------------|-----------------|

| Complex Input           | L<br>X          | X<br>L          |

| Real Valued Input (RVI) | Н               | Н               |

Figure 2a. Offset Address Control

| AS = | AS <sub>3</sub> | AS <sub>2</sub> | AS <sub>1</sub> | AS <sub>0</sub> | Description         | Usage              |

|------|-----------------|-----------------|-----------------|-----------------|---------------------|--------------------|

| 0    |                 | ī               | L               | L               | Data Address 1      | Radix 2/4          |

| 1    | Ē               | Ē               | L               | н               | Data Address 2      | Radix 2/4          |

| 2    | Ĺ               | L               | Н               | L               | Data Address 3      | Radix 4            |

| 3    | Ĺ               | L               | н               | н               | Data Address 4      | Radix 4            |

| 4    |                 | н               | L               | L               | Alt. Data Address 1 | Radix 2/4          |

| 5    | ī               | н               | L               | н               | Alt. Data Address 2 | Radix 2/4          |

| 6    | Ĺ               | н               | н               | L               | Alt. Data Address 3 | Radix 4            |

| 7    | Ĺ               | н               | Н               | Н               | Alt. Data Address 4 | Radix 4            |

| 8    | н               |                 | L               | L               | Const Address 1     | Radix 2/4, Shading |

| 9    | НH              | l ī             | L               | Н               | Const Address 2     | Radix 4            |

| 10   | ÌН              | l L             | Н               | L               | Const Address 3     | Radix 4            |

| 11   | H               | L               | н               | Н               | Const Address 1     | Shading            |

| 12   | н               | H               | L               | L               | RVI Data Address 1  | RVI                |

| 13   | l μ             | H               | l ī             | н               | RVI Data Address 2  | RVI                |

| 14   | НĤ              | Н               | н               | l L             | RVI Data Address 3  | RVI                |

| 15   | H               | н               | Н               | H               | RVI Data Address 4  | RVI                |

Figure 3. Address Select Control

### ABSOLUTE MAXIMUM RATINGS

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

### **OPERATING RANGES**

DC CHARACTERISTICS over operating range unless otherwise specified

| Parameters      | Description                           | Test                                                                          | Min                                                        | Typ<br>(Note 2) | Max | Units |       |

|-----------------|---------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------|-----------------|-----|-------|-------|

|                 |                                       | V <sub>CC</sub> = MIN                                                         | I <sub>OH</sub> = -2.6mA, COM'L                            | 2.4             |     |       | Volts |

| VOH             | Output HIGH Voltage                   | VIN - VIH or VIL                                                              | IOH = - mA, MIL                                            |                 |     |       | Voits |

| VOL             | Output LOW Voltage                    | V <sub>CC</sub> = MIN<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> | I <sub>OL</sub> = 12mA                                     |                 |     | 0.5   | Volts |

| VIH             | Input HIGH Level                      | Guaranteed input logical HIGH voltage for all inputs                          |                                                            | 2.0             |     |       | Volts |

| VIL             | Input LOW Level                       | Guaranteed input logica<br>voltage for all inputs                             | I LOW                                                      |                 |     | 0.8   | Volts |

| VI              | input Clamp Voltage                   | V <sub>CC</sub> = MIN, I <sub>IN</sub> = -18m/                                | 4                                                          |                 |     | -1.5  | Volts |

| hL              | Input LOW Current                     | V <sub>CC</sub> = MAX, V <sub>IN</sub> = 0.4V                                 |                                                            |                 |     | -0.4  | mA    |

| l <sub>IH</sub> | Input HIGH Current                    | $V_{CC} = MAX$ , $V_{IN} = 2.7V$                                              |                                                            |                 |     | 20    | μА    |

| l <sub>l</sub>  | Input HIGH Current                    | V <sub>CC</sub> = MAX, V <sub>IN</sub> = 5.5V                                 | V <sub>CC</sub> = MAX, V <sub>IN</sub> = 5.5V (See Note 5) |                 |     | 100   | μА    |

| lozh            | Off State (High Impedance)            | V <sub>CC</sub> = MAX                                                         | V <sub>IN</sub> = 2.7V                                     |                 |     | 20    | μΑ    |

| lozL            | Output Current                        | VCC - MIAA                                                                    | V <sub>IN</sub> = 0.4V                                     |                 |     | 0.4   | mA    |

| Isc             | Output Short Circuit Current (Note 3) | V <sub>CC</sub> = MAX                                                         |                                                            | -30             |     | -85   | mA    |

|                 |                                       | COM'L and MIL                                                                 | T <sub>A</sub> =25°C                                       |                 | 320 | 450   |       |

|                 | S                                     | COM'L Only                                                                    | $T_A = 0$ to +70°C (Note 6)                                |                 |     | 450   |       |

| lcc             | Power Supply Current                  | V <sub>CC</sub> = MAX                                                         | T <sub>A</sub> = + 70°C (Note 6)                           |                 |     | 400   | mA    |

| -               | (Note 4)                              | MIL Only                                                                      | T <sub>C</sub> = -55 to +125°C                             |                 |     | 470   |       |

|                 |                                       | V <sub>CC</sub> = MAX                                                         | T <sub>C</sub> = + 125°C                                   |                 |     | 350   |       |

Notes: 1. For conditions shown as MIN or MAX, use the appropriate value specified under Operating Ranges for the applicable device type.

2. Typical limits are at V<sub>CC</sub> = 5.0V, 25°C ambient and maximum loading.

3. Not more than one output should be shorted at a time. Duration of the short circuit test should not exceed one second.

4. OE LOW and all inputs LOW.

5. It is limited to 5.5V because A<sub>0</sub> to A<sub>15</sub> inputs also connect to output transistors.

6. Chip Carriers: T<sub>C</sub> = 0 to 85°C.

## SWITCHING CHARACTERISTICS over operating range unless otherwise specified (T<sub>A</sub> = 25°C, V<sub>CC</sub> = 5.0V)

| Paramet       | ere              | Description                                                                               |                            | Test<br>Conditions | Min | Тур | Max                                              | Units |

|---------------|------------------|-------------------------------------------------------------------------------------------|----------------------------|--------------------|-----|-----|--------------------------------------------------|-------|

| 1 tpD         |                  | CP to A <sub>0-15</sub> (AS = 0)                                                          |                            |                    |     | 21  | 30                                               | ns    |

|               |                  | CP to A <sub>0-15</sub> (AS = 1)                                                          |                            |                    |     | 21  | 30                                               | ns    |

|               |                  | CP to A <sub>0-15</sub> (AS = 2)                                                          |                            |                    | 21  | 30  | ns                                               |       |

|               |                  | CP to A <sub>0-15</sub> (AS = 3)                                                          |                            | 7                  |     | 21  | 30                                               | ns    |

|               |                  | CP to A <sub>0-15</sub> (AS = 4)                                                          |                            | 7                  |     | 21  | 30                                               | ns    |

|               | <del> </del>     | CP to A <sub>0-15</sub> (AS = 5)                                                          |                            |                    |     | 21  | 30                                               | ns    |

|               |                  | CP to A <sub>0-15</sub> (AS = 6)                                                          |                            | _                  |     | 21  | 30                                               | ns    |

|               |                  | CP to A <sub>0-15</sub> (AS = 7)                                                          |                            | 1                  |     | 21  | 30                                               | ns    |

| +             |                  | CP to A <sub>0-15</sub> (AS = 8)                                                          |                            | _                  |     | 25  | 32                                               | ns    |

|               |                  | CP to A <sub>0-15</sub> (AS = 9)                                                          |                            | 7                  |     | 25  | 32                                               | ns    |

|               |                  |                                                                                           |                            |                    |     | 30  | 40                                               | ns    |

| +             |                  | CP to A <sub>0-15</sub> (AS = 10)<br>CP to A <sub>0-15</sub> (AS = 11)                    |                            |                    |     | 21  | 40                                               | ns    |

|               |                  |                                                                                           |                            | _                  |     | 21  | 30                                               | ns    |

| -             |                  | CP to A <sub>0-15</sub> (AS = 12)                                                         |                            | _                  |     | 21  | 30                                               | ns    |

| $\overline{}$ |                  | CP to A <sub>0-15</sub> (AS = 13)                                                         |                            |                    |     | 21  | 30                                               | ns    |

| +             |                  | CP to A <sub>0-15</sub> (AS = 14)                                                         |                            |                    |     | 21  | 30                                               | ns    |

| 1 1           | t <sub>PD</sub>  | CP to A <sub>0-15</sub> (AS = 15)                                                         | With A <sub>2</sub> LOW    |                    |     | 30  | 40                                               | ns    |

| 2             | teD              | Address Select to A <sub>0-15</sub>                                                       | With A <sub>2</sub> Active | <del>-</del>       |     | 45  | 60                                               | ns    |

|               | 1                |                                                                                           | 11017/27/00/0              |                    |     | 20  | 30                                               | ns    |

|               |                  | OE to A <sub>0-15</sub> Disable Time                                                      |                            | _                  |     | 20  | 35                                               | ns    |

| -             | t <sub>PLZ</sub> | OE to A <sub>0-15</sub> Disable Time                                                      |                            |                    | 18  | 30  | ns                                               |       |

| -             | tpzH             | OE to A <sub>0-15</sub> Enable Time                                                       | C <sub>L</sub> = 50pF      |                    | 16  | 25  | ns                                               |       |

|               | tpzL             | OE to A <sub>0-15</sub> Enable Time                                                       | See Test                   |                    | 20  | 30  | ns                                               |       |

|               | tPD              | CP to IT COMP                                                                             |                            | Circuits           |     | 20  | 30                                               | ns    |

| 8             | t <sub>PD</sub>  | CP to FFT COMP                                                                            |                            |                    |     | 30  | 40                                               | ns    |

| 9             | tPD              | CP to ODD/EVEN/ (KNZ/KZ) Address Select to ODD/EVEN/ (KNZ                                 | / <del>27</del> )          | $\dashv$           |     | 20  | 30                                               | ns    |

| 10            | tPD              | Address Select to ODD/EVEN/ (KNZ                                                          | tup Time                   | <del>-</del> i     | 10  | 4   |                                                  | ns    |

| 11            | ts               | Offset Address Input A <sub>0-15</sub> to CP Set                                          | ld Time                    |                    | 0   | -1  |                                                  | ns    |

| 12            | tH               | Offset Address input A <sub>0-15</sub> to CP Ho                                           | 2                          | _                  | 20  | 11  | <b></b>                                          | ns    |

| 13            | ts               | Counter Instruction to CP Set-up Time                                                     |                            |                    | 0   | 0   | $\top$                                           | ns    |

| 14            | tн               | Counter Instruction to CP Hold Time<br>Transform Length Select to CP Set-u                | n Time                     |                    | 40  | 25  |                                                  | ns    |

| 15            | ts               | Transform Length Select to CP Set-u                                                       | Timo                       |                    | 0   | 0   |                                                  | ns    |

| 16            | tн               | Transform Length Select to CP Hold Transform Length Select to TSTRB t                     | Set up Time                |                    | 8   | 4   |                                                  | ns    |

| 17            | ts               | Transform Length Select to TSTRB t                                                        | Hold Time                  | _                  | 5   | 3   |                                                  | ns    |

| 18            | tH               | TSEL (HIGH to LOW) to TSTRB 1 S                                                           | et up. Time                |                    | 15  | 10  |                                                  | ns    |

| 19            | ts               |                                                                                           | et-up Time                 |                    | 15  | 10  |                                                  | ns    |

| 20            | чн               | TSEL to TSTRB: Hold Time                                                                  |                            |                    | 25  | 16  |                                                  | ns    |

| 21            | ts               | RADIX 4/2 to CP Set-up Time                                                               |                            | -                  | 0   | 0   |                                                  | ns    |

| 22            | tн               | RADIX 4/2 to CP Hold Time                                                                 | . Satura Time              |                    | 8   | 5   |                                                  | ns    |

| 23            | ts               | RADIX 4/Z, PSD, DIT/DIF to STRB : Set-up Time RADIX 4/Z, PSD, DIT/DIF to STRB : Hold Time |                            | -                  | 0   | 0   |                                                  | ns    |

| 24            | tH               | RADIX 4/2, PSD, DIT/DIF to STRB                                                           | un Time                    | -                  | 15  | 10  |                                                  | ns    |

| 25            | ts               | SEL (HIGH to LOW) to STRB   Set-up Time                                                   |                            | -                  | 15  | 10  | <del>                                     </del> | n     |

| 26            | tH               | SEL Hold Time to STRB + Hold Time                                                         |                            |                    | 45  | 30  | +                                                | n     |

| 27            | ts               | STRB or TSTRB to CP Set-up Time                                                           |                            |                    | 15  | 10  | +                                                | n:    |

| 28            | tpwsL            | Minimum Strobe Pulse Width LOW                                                            |                            |                    | 15  | 10  | +                                                | n     |

| 29            | tpwH             | CP Pulse Width HIGH                                                                       |                            |                    | 15  | 10  | +-                                               | n     |

| 30            | tpwL             | CP Pulse Width LOW                                                                        |                            |                    |     | 1   |                                                  |       |

### $\textbf{SWITCHING} \ \ \textbf{CHARACTERISTICS} \ \ \text{over operating range unless otherwise specified}$

|                   |                 |                                                                |                       | COMM        | ERCIAL                                           | MILITARY |                                                  |      |

|-------------------|-----------------|----------------------------------------------------------------|-----------------------|-------------|--------------------------------------------------|----------|--------------------------------------------------|------|

| Parameters  1 tpp |                 | Description                                                    | Test<br>Conditions    | Min         | Max                                              | Min      | Max                                              | Unit |

| 1                 | tPD             | CP to A <sub>0-15</sub> (AS = 0)                               |                       |             | 35                                               |          | 40                                               | ns   |

| 1                 | tPD             | CP to A <sub>0-15</sub> (AS = 1)                               |                       |             | 35                                               |          | 40                                               | ns   |

| 1                 | tpD             | CP to A <sub>0-15</sub> (AS = 2)                               |                       |             | 35                                               |          | 40                                               | ns   |

| 1                 | tpD             | CP to A <sub>0-15</sub> (AS = 3)                               |                       |             | 35                                               |          | 40                                               | ns   |

| 1                 | tpD             | CP to A <sub>0-15</sub> (AS = 4)                               |                       |             | 35                                               |          | 40                                               | ns   |

| 1                 | tpD             | CP to A <sub>0-15</sub> (AS = 5)                               |                       |             | 35                                               |          | 40                                               | ns   |

| 1                 | t <sub>PD</sub> | CP to A <sub>0-15</sub> (AS = 6)                               |                       |             | 35                                               |          | 40                                               | ns   |

| 1                 | tpD             | CP to A <sub>0-15</sub> (AS = 7)                               |                       |             | 35                                               |          | 40                                               | ns   |

| 1                 | tpD             | CP to A <sub>0-15</sub> (AS = 8)                               |                       |             | 42                                               |          | 50                                               | ns   |

| 1                 |                 | CP to A <sub>0-15</sub> (AS = 9)                               | _                     |             | 42                                               |          | 50                                               | ns   |

| 1                 | tpD             | CP to A <sub>0-15</sub> (AS = 10)                              | _                     |             | 53                                               |          | 60                                               | ns   |

| 1                 | tPD             | CP to A <sub>0-15</sub> (AS = 11)                              | _                     |             | 53                                               |          | 60                                               | ns   |

| 1                 | teD             | CP to A <sub>0-15</sub> (AS = 12)                              |                       |             | 35                                               |          | 40                                               | ns   |

| 1                 | tPD             | CP to A <sub>0-15</sub> (AS = 13)                              | 7                     |             | 35                                               |          | 40                                               | ns   |

| 1                 | tep             | CP to A <sub>0-15</sub> (AS = 14)                              |                       |             | 35                                               |          | 40                                               | ns   |

| 1                 | tPD             | CP to A <sub>0-15</sub> (AS = 15)                              |                       | ļ           | 35                                               |          | 40                                               | ns   |

|                   | 1 70            | With A <sub>2</sub> LOW                                        |                       | <b></b>     | 45                                               |          | 50                                               | ns   |

| 2                 | tpD             | Address Select to A <sub>0-15</sub> With A <sub>2</sub> Active | _                     | <b></b>     | 65                                               |          | 70                                               | ns   |

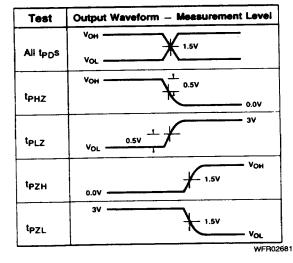

| 3                 | tPHZ            | OE to A <sub>0-15</sub> Disable Time                           | C <sub>L</sub> = 50pF |             | 32                                               | -        | 35                                               | ns   |

| 4                 |                 | OE to A <sub>0-15</sub> Disable Time                           | See Test              | <del></del> | 40                                               |          | 45                                               | ns   |

| 5                 |                 | OE to A <sub>0-15</sub> Enable Time                            | Circuits              |             | 35                                               |          | 40                                               | ns   |

| 6                 | tpzL            | OE to A <sub>0-15</sub> Enable Time                            | -                     |             | 30                                               |          | 35                                               | ns   |

| 7                 | tPD             | CP to IT COMP                                                  | -                     |             | 40                                               |          | 50                                               | ns   |

| 8                 | tPD             | CP to FFT COMP                                                 | -                     | <b></b>     | 40                                               |          | 50                                               | ns   |

| 9                 | ten             | CP to ODD/EVEN/(KNZ/KZ)                                        | =                     |             | 53                                               |          | 60                                               | ns   |

| 10                | ten             | Address Select to ODD/EVEN/(KNZ/KZ)                            | -                     |             | 38                                               |          | 45                                               | ns   |

| 11                | ts              | Offset Address Input A <sub>0-15</sub> to CP Setup Time        | =                     | 11          | <del> </del>                                     | 12       | <del> </del>                                     | ns   |

| 12                | _               | Offset Address Input A <sub>0-15</sub> to CP Hold Time         | $\dashv$              | 1           |                                                  | 2        | 1                                                | ns   |

| 13                | t <sub>H</sub>  | Counter Instruction to CP Setup Time                           | -                     | 22          |                                                  | 25       | t                                                | ns   |

| 14                | ls.             | Counter Instruction to CP Hold Time                            |                       | To          |                                                  | 0        |                                                  | ns   |

| 15                | t <sub>H</sub>  | Transform Length Select to CP Setup Time                       | -                     | 45          | <u> </u>                                         | 50       |                                                  | ns   |

|                   | ts              | Transform Length Select to CP Hold Time                        | _                     | 0           |                                                  | 0        |                                                  | ns   |

| 16<br>17          | t <sub>H</sub>  | Transform Length Select to TSTRB   Setup Time                  | '                     | 9           | <del> </del>                                     | 10       | <del> </del>                                     | ns   |

| 18                | ts              | Transform Length Select to TSTRB † Setup Time                  |                       | 7           |                                                  | 8        | <del> </del>                                     | ns   |

| 19                | t <sub>H</sub>  | TSEL (HIGH to LOW) to TSTRB t Setup Time                       | -                     | 18          | <del>                                     </del> | 20       | <del> </del>                                     | ns   |

|                   | ts              | TSEL toTSTRB : Hold Time                                       |                       | 18          | 1                                                | 20       | <del> </del>                                     | ns   |

| 20                | t <sub>H</sub>  | RADIX 4/2 to CP Setup Time                                     | $\rightarrow$         | 28          |                                                  | 30       | <del>                                     </del> | ns   |

| 21                | ts              | RADIX 4/2 to CP Setup Time                                     | -                     | 0           |                                                  | 0        |                                                  | ns   |

| 22                | tн              | RADIX 4/2 to CP Hold Time                                      | $\dashv$              | 9           | <del>  </del>                                    | 10       |                                                  | n:   |

| 23                | ts              | RADIX 4/2, PSD, DIT/DIF to STRB t Hold Time                    |                       | 1           |                                                  | 2        | <del> </del>                                     |      |

| 24                | tH              | 1                                                              | =                     | 18          | 1                                                | 20       | <b></b>                                          | ns   |

| 25                | ts              | SEL (HIGH to LOW) to STRB t Setup Time                         | _                     | 18          |                                                  | 20       | <del> </del>                                     | ns   |

| 26                | tH              | SEL Hold Time to STRB † Hold Time                              | <b>⊣</b>              |             |                                                  |          |                                                  | -    |

| 27                | ts              | STRB or TSTRB to CP Setup Time                                 | $\dashv$              | 50          | -                                                | 55       | <del> </del>                                     | ns   |

| 28                | tpwsl           | Minimum Strobe Pulse Width LOW                                 |                       | 18          |                                                  | 20       | ļ                                                | ns   |

| 29                | ₹PWH            | CP Pulse Width HIGH                                            | _                     | 18          | -                                                | 20       | ļ                                                | ns   |

| 30                | tpwL            | CP Pulse Width LOW                                             |                       | 18          | 1                                                | 20       | l                                                | ns   |

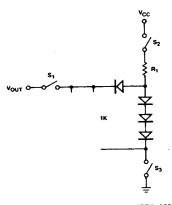

### A. THREE-STATE OUTPUTS

### B. NORMAL OUTPUTS

$v_{cc}$ CL TCR01240

5.0 - VBE - VOL

$$R_2 = \frac{2.4V}{I_{OH}}$$

$$R_1 = \frac{5.0 - V_{BE} - V_{OL}}{\frac{I_{OL} + V_{OL}}{I_{OL}}}$$

Notes: 1.  $C_L = 50$ pF includes scope probe, wiring and stray capacitances without device in test fixture.

SWITCHING TEST CIRCUIT

- 2.  $S_1$ ,  $S_2$ ,  $S_3$  are closed during function tests and all AC tests except output enable tests.

- 3.  $S_1$  and  $S_3$  are closed while  $S_2$  is open for  $t_{PZH}$  test.

- S<sub>1</sub> and S<sub>2</sub> are closed while S<sub>3</sub> is open for tpzL test.

- 4.  $C_L = 5.0 pF$  for output disable tests.

### SWITCHING TEST WAVEFORMS

03567C

7-80

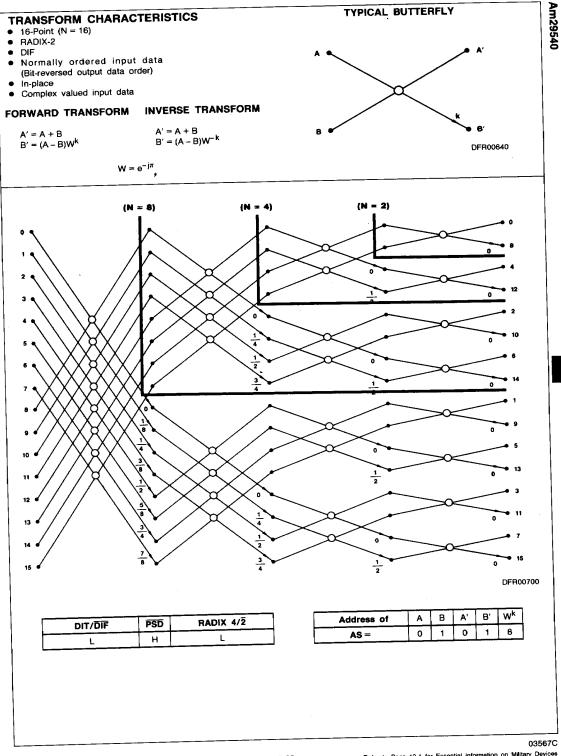

### TYPICAL BUTTERFLY TRANSFORM CHARACTERISTICS 16-Point (N = 16) RADIX-2 DIT Normally ordered output data (Bit-reversed input data order) In-place Complex valued input data INVERSE TRANSFORM FORWARD TRANSFORM $A' = A + BW^{-k}$ $A' = A + BW^k$ $B' = A - BW^{-k}$ DFR00590 $B' = A - BW^k$ $W = e^{-j\pi}$ $\{N=8\}$ (N = 4)(N = 2)12 DFR00470 $\boldsymbol{w^k}$ B Α В A' Address of RADIX 4/2 PSD DIT/DIF 8 AS = 0 0 н

03567C

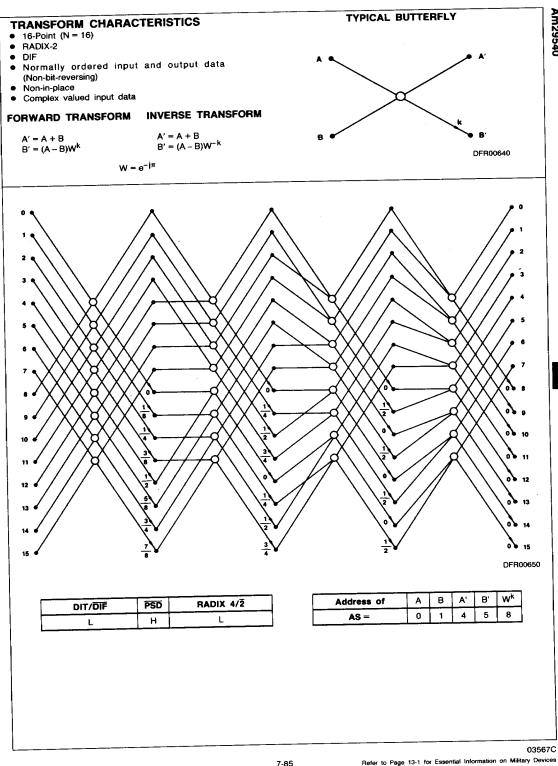

### TYPICAL BUTTERFLY TRANSFORM CHARACTERISTICS 16-Point (N = 16) RADIX-4 DIF Normally ordered input and output data (Non-digit reversing) Non-in-place Complex valued input data INVERSE TRANSFORM FORWARD TRANSFORM DFR00510 A' = A + B + C + DA' = A + B + C + D $B' = (A + jB - C - jD)W^{-k}$ $B' = (A - jB - C + jD)W^{k}$ $C' = (A - B + C - D)W^{2k}$ $C' = (A - B + C - D)W^{-2k}$ $D' = (A + jB - C - jD)W^{3k}$ $D' = (A - jB - C + jD)W^{-3k}$ $W = e^{-j\pi}$ **9** 10 ٥ 12 13 0 15 DFR00580 DIT/DIF **PSD** RADIX 4/2 н L Н w<sup>3k</sup> w<sup>2k</sup> $\mathbf{W}^{\mathbf{k}}$ A' D' B' C' Α В С D Address of 8 9 10 7 0 1 2 3 4 5 6 AS =

03567C

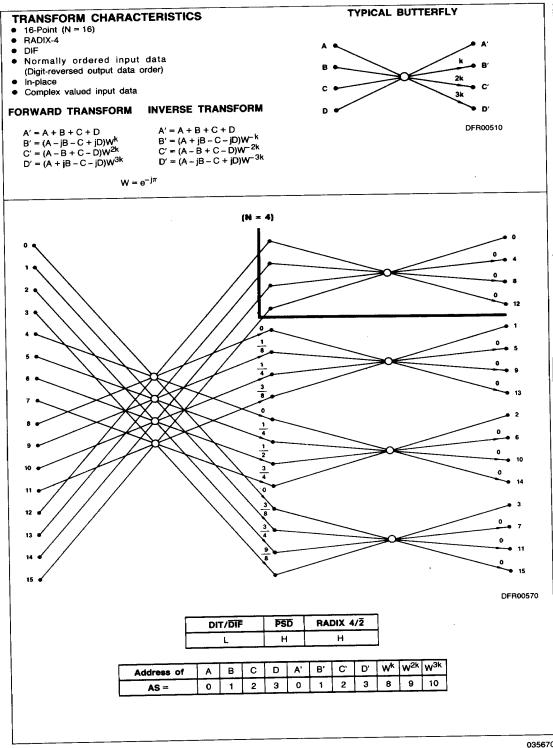

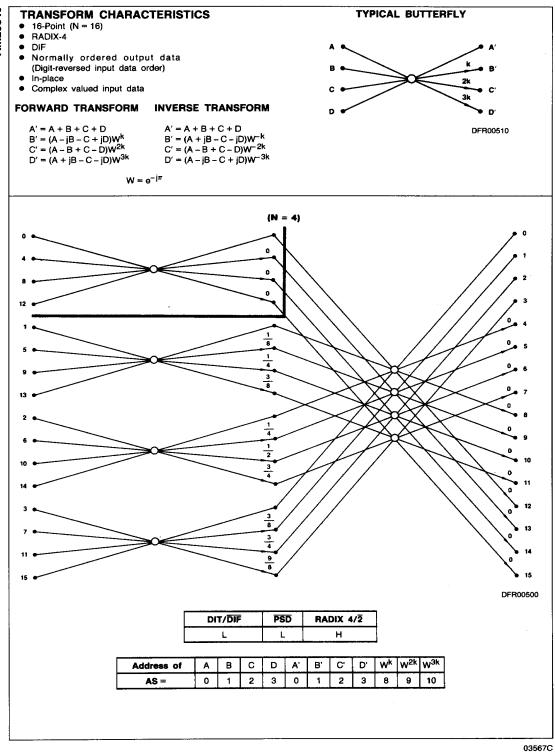

# TRANSFORM CHARACTERISTICS TYPICAL BUTTERFLY • 16-Point (N = 16) • RADIX-4 DIT Normally ordered input data (Digit-reversed output data order) In-place · Complex valued input data DFR00530 FORWARD TRANSFORM **INVERSE TRANSFORM** $\begin{array}{l} A' = A + BW^k + CW^{2k} + DW^{3k} \\ B' = A - |BW^k - CW^{2k} + |DW^{3k}| \\ C' = A - BW^k + CW^{2k} - DW^{3k} \\ D' = A + |BW^k - CW^{2k} - |DW^{3k}| \end{array}$ $\begin{array}{l} A' = A + BW^{-k} + CW^{-2k} + DW^{-3k} \\ B' = A + jBW^{-k} - CW^{-2k} - jDW^{-3k} \\ C' = A - BW^{-k} + CW^{-2k} - DW^{-3k} \\ D' = A - jBW^{-k} - CW^{-2k} + jDW^{-3k} \end{array}$ $W = e^{-j\pi}$ (N = 4)

DIT/DIF PSD RADIX 4/2 H H H

| Address of | Α | В | C | D | A' | B' | Ċ | D' | Wk | W <sup>2k</sup> | W <sub>3k</sub> |

|------------|---|---|---|---|----|----|---|----|----|-----------------|-----------------|

| AS =       | 0 | 1 | 2 | 3 | 0  | 1  | 2 | 3  | 8  | 9               | 10              |

03567C

DFR00540

### TYPICAL BUTTERFLY TRANSFORM CHARACTERISTICS • 16-Point (N = 16) RADIX-4 DIT Normally ordered output data (Digit-reversed input data order) In-place Complex valued input data DFR00530 INVERSE TRANSFORM FORWARD TRANSFORM $A' = A + BW^{k} + CW^{2k} + DW^{3k}$ $B' = A - jBW^{k} - CW^{2k} + jDW^{3k}$ $C' = A - BW^{k} + CW^{2k} - DW^{3k}$ $A' = A + BW^{-k} + CW^{-2k} + DW^{-3k}$ B' = A + jBW<sup>-k</sup> - CW<sup>-2k</sup> - jDW<sup>-3k</sup> C' = A - BW<sup>-k</sup> + CW<sup>-2k</sup> - DW<sup>-3k</sup> $D' = A - jBW^{-k} - CW^{-2k} + jDW^{-3k}$ $D' = A + jBW^k - CW^{2k} - jDW^{3k}$ $W = e^{-j\pi}$ (N = 4)**12 a** 13 **1**5 DFR00550 DIT/DIF **PSD** RADIX 4/2 н Н W<sup>2k</sup> W3k С D B' C, D' Address of 10 0 2 3 8 AS = 2 3 1 0

03567C

7-93

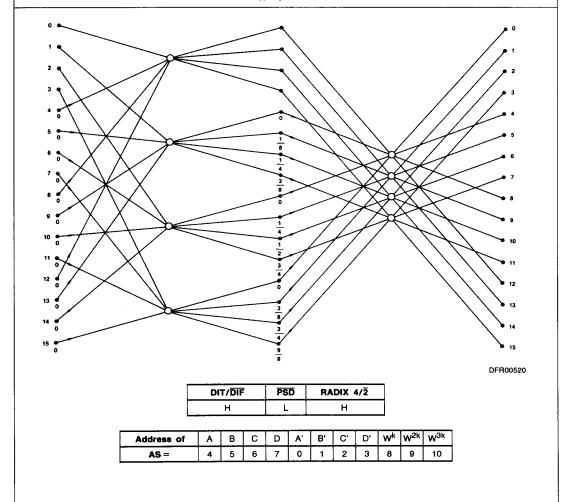

### TRANSFORM CHARACTERISTICS

- 16-Point (N = 16)

- RADIX-4

- DIT

- Normally ordered input and output data (Non-digit reversing)

- Non-in-place

- Complex valued input data

# D'

TYPICAL BUTTERFLY

### FORWARD TRANSFORM

$A' = A + BW^k + CW^{2k} + DW^{3k}$  $B' = A - jBW^k - CW^{2k} + jDW^{3k}$

$C' = A - BW^k + CW^{2k} - DW^{3k}$   $D' = A + jBW^k - CW^{2k} - jDW^{3k}$

### **INVERSE TRANSFORM**

$\begin{array}{l} A' = A + BW^{-k} + CW^{-2k} + DW^{-3k} \\ B' = A + jBW^{-k} - CW^{-2k} - jDW^{-3k} \\ C' = A - BW^{-k} + CW^{-2k} - DW^{-3k} \\ D' = A - jBW^{-k} - CW^{-2k} + jDW^{-3k} \end{array}$

DFR00530

$W = e^{-j\pi}$

7-94

### DIF TRANSFORM CHARACTERISTICS In-place 16-Point (N = 16) Real valued output data RADIX-2 Inverse Transform Normally ordered output data (Unique input data order) TYPICAL BUTTERFLIES $KNZ/\overline{KZ} = HIGH$ $KNZ/\overline{KZ} = LOW$ (k = 0)(k = 0)DFR00610 DFR00600 $A' = \Re e [A + jB + C - jD]$ A' = Re [A + jB + C - jD] $B' = Re [(A + jB - C + jD)W_N^2]$ C' = Im [A + jB + C - jD]B' = Im [A + jB + C - jD] C' = Re [(A + jB - C + jD)WN] $D' = Im [(A + jB - C + jD)W_{1}^{k}]$ $D' = Im [(A + jB - C + jD)W_N^2]$ $W_N = ej^{2\pi/N}$ $W_N = ei^{2\pi/N}$ (N = 4)15 DFR00480 RADIX 4/2 **PSD** DIT/DIF

03567C

Refer to Page 13-1 for Essential Information on Military Devices

12 13 14 15

D A' B' C' D' W

С

14 15

В

12 13

Address of

AS =

7-96

AS =

12 13 14

Refer to Page 13-1 for Essential Information on Military Devices

15 12 13 14 15 8

L

н

н