# 256K (32 x 8) CMOS FLASH MEMORY

ADVANCE DATA

- FLASH ELECTRICAL CHIP ERASE IN 1 SEC-OND RANGE.

- PRESTO F PROGRAMMING TYPICAL BYTE PROGRAM TIME: 100 μs.

- 12 V VPP SUPPLY.

- 100 TO 10.000 ERASE/PROGRAM CYCLES.

- VERY FAST ACCESS TIME: 100 ns.

- LOW POWER CONSUMPTION : Maximum standby current : 100 μA.

- COMMAND REGISTER ARCHITECTURE FOR MICROPROCESSOR / MICROCONTROLLER COMPATIBLE WRITE INTERFACE.

- JEDEC STANDARD BYTE-WIDE EPROM PINOUTS.

### DESCRIPTION

SGS-THOMSON Microelectronics M28F256 FLASH Memory is an Electrically Chip-erasable Reprogrammable non-volatile memory. Higher functionality and flexibility than EPROM come from the ability to be Chip-erased and reprogrammed in a test socket, in a PROM programmer socket, on board, or In-system. The M28F256 is suitable for applications where EEPROM functionality is not suitable or not cost effective, or for replacement of UV EPROM when UV erasure is impractical or time consuming. Pin assignment conforms to JEDEC standards for byte wide EPROMs. The High performance access time allows interface with most microcontrollers and microprocessors.

#### **PIN NAMES**

| A0-A14          | ADDRESS INPUT              |

|-----------------|----------------------------|

| O0-O7           | DATA INPUT/OUTPUT          |

| CE              | CHIP ENABLE                |

| ŌĒ              | OUTPUT ENABLE              |

| WE              | WRITE ENABLE               |

| V <sub>PP</sub> | ERASE/PROGRAM power supply |

| Vcc             | 5V ± 10 % POWER SUPPLY     |

| GND             | GROUND                     |

| NC (1)          | NO INTERNAL CONNECTION     |

(1) Pin may be driven or left floating.

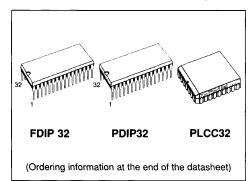

Figure 1: Pin Configuration

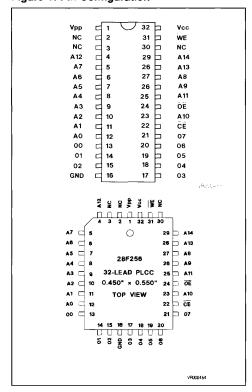

Figure 2: M28F256 Block Diagram

**Table 3: Absolute Maximum Ratings**

| Symbol            | Parameter                                       | Value        | Unit |

|-------------------|-------------------------------------------------|--------------|------|

| Vı                | Input or Output voltages with respect to ground | -0.6 to 7.0  | V    |

| V <sub>PP</sub>   | Supply voltage with respect to ground           | -0.6 to 14   | V    |

| VA9               | Voltage on A9 with respect to ground            | -0.6 to 13.5 | V    |

| Vcc               | Supply voltage with respect to ground           | -0.6 to 7.0  | V    |

| T <sub>bias</sub> | Temperature Range under Bias                    | -10 to 80    | ,c   |

| T <sub>stg</sub>  | Storage temperature range                       | -65 to 125   | °C   |

| TR <sub>op</sub>  | Operating Temperature during Read               | 0 to 70      | °C   |

| TEPop             | Operating Temperature during Erase / Program    | 0 to 70      | °C   |

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 4 : Bus Operation

|                | PINS                                                                          |                                                          | A0                                         | A9                                  | CE                       | ŌĒ                     | WE                     | 00-07                                                   |

|----------------|-------------------------------------------------------------------------------|----------------------------------------------------------|--------------------------------------------|-------------------------------------|--------------------------|------------------------|------------------------|---------------------------------------------------------|

|                | OPERATIONS                                                                    | (1)                                                      | ~                                          | ~                                   | J_                       | OL.                    |                        | 00-07                                                   |

| READ<br>ONLY   | READ OUTPUT DISABLE STANDBY MANUFACTURER SIG- NATURE (2) DEVICE SIGNATURE (2) | VPPL<br>VPPL<br>VPPL<br>VPPL<br>VPPL                     | A0<br>X (7)<br>X<br>VIL<br>V <sub>IH</sub> | A9<br>X<br>X<br>V <sub>SI</sub> (3) | VIL<br>VIL<br>VIH<br>VIL | VIL<br>VIH<br>X<br>VIL | VIH<br>VIH<br>X<br>VIH | DATA OUT TRI STATE TRI STATE DATA = 20  DATA = A1 OR A8 |

| READ/<br>WRITE | READ<br>OUTPUT DISABLE<br>STANDBY (5)<br>WRITE                                | V <sub>PPH</sub><br>V <sub>PPH</sub><br>V <sub>PPH</sub> | A0<br>X<br>X<br>A0                         | A9<br>X<br>X<br>A9                  | VIL<br>VIL<br>VIH<br>VIL | VIL<br>VIH<br>X<br>VIH | VIH<br>VIH<br>X<br>VIL | DATA OUT (4)<br>TRI STATE<br>TRI STATE<br>DATA IN (6)   |

- Notes: (1) VPP Low may be ground, a no connect with a resistor tied to ground, or < 8 volts. VPP High is the programming voltage specified for the device. When VPP = VPPL memory content can be read but not written or erased.

- (2) Manufacturer and Device electronic Signature can be accessed also through Command Register (see table 5) Device code A8 requires  $V_{PPH} = 12V \pm 5\%$ . Device code A1 requires  $V_{PPH} = 12.75V \pm 0.25V$ . All other addresses low.

- (3)  $11.5V < V_{SI} < 13V$ .

- When VPP = VPPH read operation can be array data or Electronic Signature.

- (5) When V<sub>PP</sub> = V<sub>PPH</sub> Standby current is I<sub>CC</sub> + I<sub>PP</sub> (Standby).

- (6) Refer to table 5 for Data In during write.

- (7) X can be VIL or VIH.

#### **DEVICE OPERATION**

#### PRINCIPLE

The added functionality of FLASH as compared EPROM. is Electrical Erasure Reprogramming. In order to manage this new functionality a command register is introduced. Some device functions are addressed via the command register, some not, depending on the VPP pin voltage. When VPP pin is at low voltage (< 8V), the M28F256 is a READ only memory. The command register is disabled. Manipulations of the external memory control pins yield the standard EPROM read, output disable, electronic signature and standby operations. Raising VPP pin to High voltage, enables the command register for READ/WRITE operations. In addition, output disable, standby, signature, ERASE and WRITE operations are allowed. At VPP = VPPH the operating modes are addressed through the use of the command register.

Table 4 summarizes the Bus operations : at VPP=VPPL only Read operations are allowed, at VPP=VPPH Read operations and Erase/Write operations are allowed.

#### OPERATION MODES DESCRIPTION

A- OPERATION MODES WITH VPP AT LOW VOLTAGE (< 8V)

# READ MODE

The M28F256 has two control pins, both of which must be logically active in order to obtain data at the outputs.

Chip Enable (CE) is the power control and should be used for device selection. Output Enable (OE) is the output control and should be used to gate data to the output pins. independent of device selection. Fig 7 illustrates read timing waveforms.

#### STANDBY MODE

The M28F256 has a standby mode which reduces the maximum active current from 30mA to 0.1mA. The device is placed in Standby mode by applying a high signal to the CE input. When in Standby mode the outputs are in a high impedance state, independent of the OE input.

#### **OUTPUT DISABLE**

With OE at High level VIH, output pins are placed in a high impedance state.

# ELECTRONIC SIGNATURE

The Electronic Signature mode allows the reading out of a binary code from the device that will identify its manufacturer and type. This mode is intended for use by programming equipment

automatically match the device to be programmed or erased with its corresponding programming or erasing algorithm. This mode is activated by applying high voltage on address line A9 (11.5V - 13V) and by applying V<sub>IL</sub> to CE and OE. Two identifier bytes may then be sequenced from the outputs by toggling address line A0 from VIL to VIH. All other address lines must be held at VIL during Electronic Signature mode.

Byte 0 (A0=V<sub>IL</sub>) represents the manufacturer

code and byte 1 (A0=V<sub>IH</sub>) represents the device identifier code. For the SGS-THOMSON Microelectronics M28F256, these two identifiers are given here below and can be read on outputs O0 to O7.

# WRITE MODE

When V<sub>PP</sub> is at low voltage, memory contents can not be written or erased. Write/Erased operations can only be accomplished via the command register when VPPH is applied on VPP pin.

#### **ELECTRONIC SIGNATURE**

| IDENTIFIER          |                                    |    |    |    | PI | NS |    |    |        |          |

|---------------------|------------------------------------|----|----|----|----|----|----|----|--------|----------|

| IDENTIFICATION INC. | A0                                 | 07 | O6 | O5 | 04 | О3 | 02 | 01 | 00     | HEX      |

| MANUFACTURER CODE   | VIL                                | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0      | 20       |

| DEVICE IDENTIFIER   | V <sub>IH</sub><br>V <sub>IH</sub> | 1  | 0  | 1  | 0  | 0  | 0  | 0  | 1<br>0 | A1<br>A8 |

Notes: (1) A9 = 12.0V  $\pm$  0.5V;  $\overline{CE} \approx \overline{OE} = V_{IL}$ ;  $V_{PP} = V_{PPL}$ ; A1 to A8=  $V_{IL}$ ; A10 to A14 =  $V_{IL}$

(2) Device code is either A8 if device requires  $V_{PP} = 12V \pm 5\%$  or A1 if device requires  $V_{PP} = 12.75V \pm 0.25V$ .

Table 5 : COMMAND DEFINITIONS

|                                  | BUS             | FIR       | ST BUS CYCL    | SECOND BUS CYCLE |                                    |    |     |  |  |

|----------------------------------|-----------------|-----------|----------------|------------------|------------------------------------|----|-----|--|--|

| COMMAND                          | CYCLES<br>REQ'D | Operation | (1) Address (2 | ) Data (3)       | Operation (1) Address (2) Data (3) |    |     |  |  |

| Read Memory                      | 1               | Write     | Х              | 00H              |                                    |    |     |  |  |

| Read Electronic<br>Signature (4) | 1               | Write     | х              | 90H              | Read                               | 1A | ID  |  |  |

| Setup<br>Erase/Erase (5)         | 2               | Write     | х              | 20H              | Write                              | ×  | 20H |  |  |

| Erase Verify (5)                 | 2               | Write     | EA             | A0H              | Read                               | Х  | EVD |  |  |

| Setup pro-<br>gram/Program (6)   | 2               | Write     | ×              | 40H              | Write                              | PA | PD  |  |  |

| Program verify<br>(6)            | 2               | Write     | Х              | Сон              | Read                               | ×  | PVD |  |  |

| Reset (7)                        | 2               | Write     | Х              | FFH              | Write                              | X  | FFH |  |  |

Notes:

- (1) Bus operations are defined in table 4.

- (2) IA = identifier address; 0000H for manufacturer code and 0001H for device.

- (3) EA = address of memory location to be read during erase verify.

- PA = address of memory location to be programmed.

- (4) ID = data read from location IA during electronic signature; 20H = manuf; A1H or A8H = device. PD = data to be programmed at location PA. EVD = data read during from location EA during erase verify. PVD Data read from location PA during program verify.

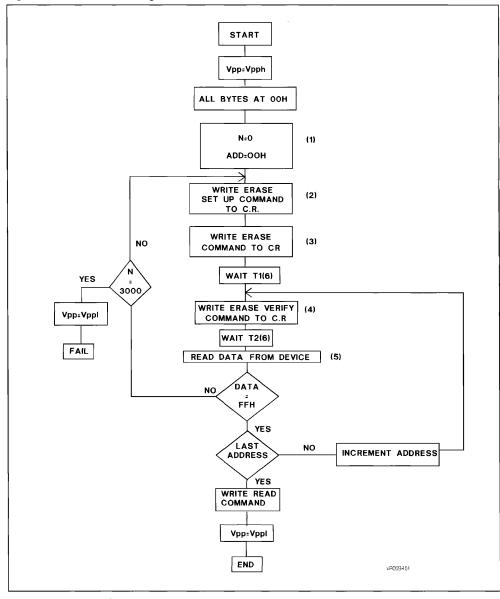

- See fig. 6 for erase algorithm.

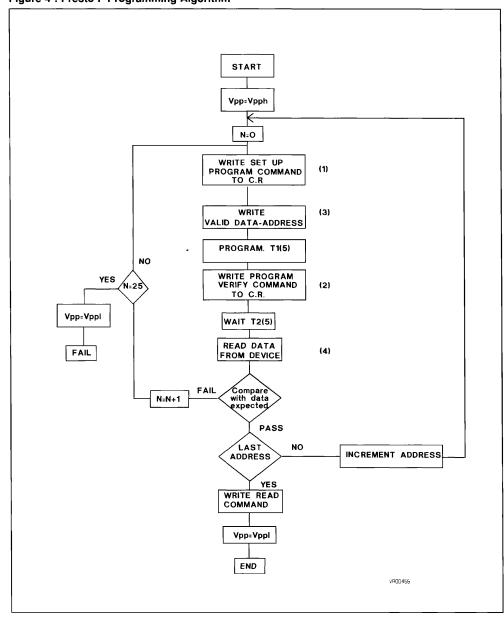

- See fig. 4 for programming algorithm.

- (7) The second bus cycle must be followed by the desired command register write.

# B - OPERATION MODES WITH VPP AT VPPH - COMMAND REGISTER

At VPP = VPPH, Read/Write operations are enabled. Device operations are selected by writing specific data patterns into the command register using standard microprocessor write timings. The register contents are inputs for an internal state machine which controls erase and programming circuitry. Some commands require one write cycle, while others require two. The register is a latch used to store these commands and the data and address needed to execute the command.

(Note that the command register does not occupy an addressable memory location).

With this architecture, the device expects the first write cycle to be a command and does not corrupt data at specified address. The command register is written by bringing WE to VIL, while CE is low. Addresses are latched on the falling edge of WE, while data are latched on the rising edge of WE pulse. Table 5 contains the list of register commands. The three high order register bits R7. R6 and R5 encode the control function. All other register bits R4-R0 must be at zero. Only exception is the reset command, when FFH is written into the command register. Register bits R7-R0 correspond to data inputs D7-D0. Note that when VPP is at low voltage, the contents of the command register default to 00H enabling Read-Only operations. The command register is only alterable when VPP is at high voltage. The system designer may choose to make the VPP switchable or to make the VPP constantly available. In the case of switchable VPP, when VPP is removed, the device defaults to Read Only memory. In the case of constantly available V<sub>PP</sub>, all memory functions performed via the command register.

# READ MODE WITH VPP = VPPH

At VPP = VPPH, memory contents can be addressed via the read command 00H. Read mode is initiated by writing 00H into the command register. The microprocessor read cycles retrieve the array data. The device remains enabled for read operations until the command register contents are altered. The default contents of the command register upon power-up is 00H. This default value ensures that no spurious alteration of memory contents occurs during the VPP power transition. When VPP is "Hardwired", the device powers-up and remains enabled for read operations until the command register contents are changed.

Refer to AC Read characteristics and waveforms for timing parameters (Fig 7,Table 9).

# ELECTRONIC SIGNATURE WITH VPP = VPPH

In order for the M28F256 to be erased and programmed by the local CPU and thus to supplement the traditional PROM programming methodology, the manufacturer and device signature codes can be read via the command register. The operation is initiated by writing 90H to the register. Following the command write, a read cycle from address 0000H returns the manufacturer code of 20H. A read cycle from address 0001H returns the device code of A1 or A8. To terminate the operation, it is necessary to write another valid command into the register.

# SET UP ERASE/ERASE MODE

Before erasure it is necessary to program all bytes to the same level (data 00H). Setup erase is a command-only operation that prepares the device for electrical erasure of all bytes in the array. The setup erase is performed by writing 20H to the command register. To begin chip erasure, the erase command (20H) must again be written to the register. The erase operation begins on the second command's rising edge of the WE pulse and terminates with the rising edge of the next WE pulse (i.e Erase Verify command). This two-step sequence of setup followed by execution ensures that memory contents are not accidentally erased. Refer to A.C Erase characteristics and waveforms for timing parameters (Fig 6, Fig 5, Table 10).

#### **ERASE VERIFY MODE**

The erase command erases all the bytes of the array in parallel. After each erase operation, all bytes must be verified to see if they are erased. The erase verify operation is initiated by writing A0H to the command register. The address of the byte to be verified must be supplied because the device latches this address on the falling the WE and the actual command on the rising edge. The register write with the erase verify command terminates the erase operation. The device applies an internally generated margin voltage to the addressed byte. Reading FFH from the addressed byte indicates that all the bits of the byte are erased. If the location is erased the erase verify operation is repeated for the next location. The command must be written before each byte verification to latch the byte address. This process continues for each byte of the array until a byte does not return FFH or the last address is accessed.

In the case where the data returned is not FFH, another setup Erase/Erase operation is performed. The verification starts then from the address of the last verified byte. Once the last address is accessed, erasure is complete and the erase verify is terminated by writing a valid command to the command register. See Fig.6, 6bis for Erase algorithm, Fig.5 for waveforms and Table 10 for erase timings.

#### SET UP PROGRAM/PROGRAM

Writing 40H to the command register performs the setup operation. The next WE pulse operation causes a transition to an active programming operation. The device latches address and data on the falling and rising edge of WE pulse respectively. The rising edge of this second WE pulse also begins programming operation. The programming operation is stopped on the next rising edge of WE used to write the program verify command into the command register. See A.C programming characteristics and waveforms for programming timings (Fig 4 ,Table 10).

# PROGRAM VERIFY MODE

Flash memory device programs on a byte by byte basis. After each programming operation, the byte just programmed must be verified. The program verify command (COH) stops programming and sets up verification. The device executes the command on the rising edge of WE. The program verify command prepares the device for verification of the byte last programmed. No new address information is latched. The device applies an internally generated margin voltage to the byte. After a 6μs delay the data is read at the address programmed and compared to the programmed data. Reading valid data indicates that the byte programmed successfully. See Fig.4 programming algorithm, Fig.3 for waveforms and Table 10 for programming timings.

#### COMMAND REGISTER RESET

This command is used to safely abort erase- and program-command sequences. The reset operation is performed by writing twice the code FFH to the command register. The memory content is not altered. A valid command must be written to place the device in the desired state.

#### STANDBY MODE

If during Erasure, Programming, or Program/Erase verification, the device is deselected, it draws active current until operation is terminated.

# PRESTO F PROGRAMMING ALGORITHM

Programming with PRESTO F consists in applying a sequence of 100 µs program pulses to each byte until a correct verify occurs. programming operations are allowed for each byte. Each programming operation consists in a set-up program command through the command register (code 40H); the programming is then performed. Then a program verify command is written into the command register (code C0H) and read is performed which compares data output with data expected. During Programming and Verify operation a MARGIN MODE circuit is automatically activated in order to quarantee that each cell is programmed with enough margin. Figure 4 illustrates the PRESTO F programming algorithm.

#### PRESTO F ERASE ALGORITHM

Erasing with PRESTO F erase algorithm allows to erase electrically the entire memory in a reliable way. The algorithm starts by first programming all the bytes to 00H in order to erasure. This step is perform an uniform PRESTO F accomplished by using the Programming algorithm. All bytes being in the same state (00H), a set-up erase command is written into the command register (code 20H) followed by the erase command (code 20H). Erase is then performed. Erase verify command is written to the command register (code A0H), and data of the address to be verified is compared to FFH. The erase verify begins at address 0000H and continues until the last address is accessed or until the comparison of data to FFH fails. The address of the last byte verified can be stored and a new erase operation is performed. The erase verify then starts from the stored address location or from address 0000H. Figure 6 illustrates the PRESTO F erase algorithm.

**Table 6: OPERATING CONDITIONS**

| Symbol | Parameters                                                        | Ranges             | Units |

|--------|-------------------------------------------------------------------|--------------------|-------|

| TA     | Operating Temperature READ only operations ERASE/WRITE operations | 0 to 70<br>0 to 70 | °C    |

| Vcc    | Supply Voltage                                                    | 4.5 to 5.5         | ν     |

**Table 7: DC CHARACTERISTICS**

| Symbol            | Parameters                                                      | Lin                  | nits                 | Units | Test Condition                                                                      |  |

|-------------------|-----------------------------------------------------------------|----------------------|----------------------|-------|-------------------------------------------------------------------------------------|--|

| Symbol            | raidilleters                                                    | min                  | max                  | Units | rest Condition                                                                      |  |

| ILI               | Input Leakage current                                           |                      | ±1                   | μA    | V <sub>CC</sub> = V <sub>CC</sub> max Vin = 0 to V <sub>CC</sub>                    |  |

| lLO               | Output Leakage current                                          |                      | ±10                  | μА    | Vcc = Vccmax Vout = 0 to Vcc                                                        |  |

| I <sub>CCS1</sub> | Vcc standby current TTL                                         |                      | 1                    | mA    | V <sub>CC</sub> = V <sub>CC</sub> max $\overline{CE}$ = V <sub>IH</sub>             |  |

| lccs2             | Vcc standby current CMOS                                        |                      | 100                  | μА    | V <sub>CC</sub> = V <sub>CC</sub> max $\overline{CE}$ = V <sub>CC</sub> ±0.2\       |  |

| IPPS              | V <sub>PP</sub> Leakage current                                 |                      | ±10                  | μА    | Vpp = Vppl                                                                          |  |

| lcc1              | V <sub>CC</sub> active read current                             |                      | 30                   | mA    | $V_{CC} = V_{CC} max \overline{CE} = V_{IL}$<br>f = 5 MHz Iout = 0mA                |  |

| I <sub>CC1</sub>  | V <sub>CC</sub> active read current                             |                      | 50                   | mA    | V <sub>CC</sub> = V <sub>CC</sub> max CE = V <sub>IL</sub><br>f = 10 MHz lout = 0mA |  |

| lcc2              | V <sub>CC</sub> programming current                             |                      | 30                   | mA    | Programming in progress                                                             |  |

| Іссз              | V <sub>CC</sub> erase current                                   |                      | 30                   | mA    | Erasure in progress                                                                 |  |

| I <sub>PP2</sub>  | V <sub>PP</sub> programming current                             |                      | 30                   | mA    | V <sub>PP</sub> = V <sub>PPH</sub> programming in progress                          |  |

| IPP3              | V <sub>PP</sub> erase current                                   |                      | 30                   | mA    | V <sub>PP</sub> = V <sub>PPH</sub> erasure in progress                              |  |

| VIL               | Input low voltage                                               | -0.5                 | 0.8                  | V     |                                                                                     |  |

| VIH               | Input high voltage TTL                                          | 2                    | V <sub>CC</sub> +0.5 | V     |                                                                                     |  |

|                   | Input high voltage CMOS                                         | 0.7V <sub>CC</sub>   | V <sub>CC</sub> +0.5 | V     |                                                                                     |  |

| Vol               | Output low voltage                                              |                      | 0.45                 | V     | V <sub>CC</sub> = V <sub>CC</sub> min I <sub>OH</sub> = 2.1 mA                      |  |

| V <sub>OH</sub>   | Output high voltage CMOS                                        | 4.1                  |                      | V     | V <sub>CC</sub> = V <sub>CC</sub> min I <sub>OH</sub> = -100 μA                     |  |

|                   | Output high voltage TTL                                         | V <sub>CC</sub> -0.8 |                      | V     | Vcc = Vccmin I <sub>0</sub> = -2,5 mA                                               |  |

| V <sub>PPH</sub>  | V <sub>PP</sub> during Write/Read operations                    | 11.4<br>12.5         | 12.6<br>13           | V     | Code A1H V <sub>PP</sub> > +12V device<br>Code A8H V <sub>PP</sub> =12.75V Device   |  |

| V <sub>PPL</sub>  | V <sub>PP</sub> during read only operations                     | 0                    | 8                    | V     |                                                                                     |  |

| V <sub>PPDV</sub> | V <sub>PPH</sub> difference between<br>Erase/Program and Verify |                      | 0.2                  | V     | V <sub>PP</sub> = 12V Device                                                        |  |

| Vsi               | A9 electronic signature voltage                                 | 11.5                 | 13                   | V     | A9 = V <sub>SI</sub>                                                                |  |

Note: Operating temperature is for Commercial Range.

#### **DESIGN CONSIDERATIONS**

#### TWO LINE OUTPUT CONTROL

Because Flash memories are usually used in large memory arrays, the M28F256 features a 2 line control function which accommodates the use of multiple memory connections. The two line control function allows:

a)the lowest possible memory power dissipation, b)complete assurance that output bus contention will not occur.

For the most efficient use of these two control lines, CE should be decoded and used as the primary device selecting function, while OE should be made a common connection to all devices in the array and connected to the read line from the system control bus. This ensures that all deselected memory devices are in their low power standby mode.

#### POWER SUPPLY DECOUPLING

The power switching characteristics of the M28F256 require careful decoupling of the devices. Supply current I<sub>CC</sub> has three segments that are of interest to the system designer: the standby current level, the active current level, and the transient current peaks that are produced by the falling and rising edges of CE. The magnitude of this transient current peak is dependent on capacitive and inductive loading of the device, at the output.

The associated transient voltage peaks can be suppressed by complying with the two line output control and by properly selected decoupling capacitors. It is recommended that a 0.1µF ceramic capacitor be used on every device between V<sub>CC</sub> and GND, and V<sub>PP</sub> and GND. This should be a High frequency capacitor of low inherent inductance and should be placed as close to the device as possible. In addition, a 4.7µF bulk electrolytic capacitor should be used between V<sub>CC</sub> and GND for every eight devices. The bulk capacitor should be placed near the power supply connection point. The purpose of the bulk capacitor is to overcome the voltage drop caused by the inductive effect of the printed-circuit-board traces.

#### POWER UP/DOWN SEQUENCING

The M28F256 is designed to offer protection against accidental erasure and programming caused by spurious system level signals that may exist during power transitions. The M28F256 powers up in its read only mode. With its command register two step command sequences are necessary to alter memory contents. While these precautions are sufficient in most its steady-state value before raising  $V_{PP}$  above  $V_{CC}+2V$ . In addition upon power down  $V_{PP}$  should be below  $V_{CC}+2$  V, before lowering  $V_{CC}$ .

In addition, upon powering-down,  $V_{PP}$  should be below  $V_{CC}+2V$  before lowering  $V_{CC}$ .

Table 8 : CAPACITANCE TA = 25°C, f = 1 MHz

| Symbol          | Parameter          | Test condition        | Max | Unit |

|-----------------|--------------------|-----------------------|-----|------|

| C <sub>IN</sub> | Input capacitance  | V <sub>IN</sub> = 0V  | 6   | pF   |

| Соит            | Output capacitance | V <sub>OUT</sub> ≈ 0V | 12  | pF   |

Note: (1) this parameter is only sampled and not 100% tested.

# **AC TEST CONDITIONS**

Input Rise and Fall Times (10 % to 90 %) 10 ns

Input pulse Levels V<sub>OH</sub> and V<sub>OL</sub>

Input timing reference Levels  $V_{IL}$  and  $V_{IH}$

Output timing Reference Levels VIH and VIL

# A.C. TESTING INPUT/OUTPUT WAVEFORM

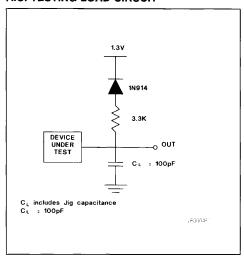

# A.C. TESTING LOAD CIRCUIT

A.C. Testing : Inputs are driven at  $V_{OH}$  for a logic "1" and  $V_{OL}$  for a logic "0". Testing measurements are made at  $V_{IH}$  for a logic "1" and  $V_{IL}$  for a logic "0". Rise/Fall time  $\leq$  10 ns.

Table 9: A.C CHARACTERISTICS Read Only Operations

| Symbol           | Characteristic                                 | M28F256-100 |     | M28F256-120 |     | M28F256-150 |     | M28F256-200 |     | Unit  |

|------------------|------------------------------------------------|-------------|-----|-------------|-----|-------------|-----|-------------|-----|-------|

| Symbol           | Characteristic                                 | Min         | Max | Min         | Max | Min         | Max | Min         | Max | Offic |

| T <sub>ACC</sub> | Address to output delay                        |             | 100 |             | 120 |             | 150 |             | 200 | ns    |

| T <sub>CE</sub>  | CE to output delay                             |             | 100 |             | 120 |             | 150 |             | 200 | ns    |

| ToE              | OE to output delay                             |             | 45  |             | 60  |             | 70  |             | 75  | ns    |

| T <sub>DF</sub>  | OE high to output float                        |             | 30  |             | 30  |             | 35  |             | 45  | ns    |

| Тон              | Output hold from Address, CE, or OE change (1) | 0           |     | 0           |     | 0           |     | 0           |     | ns    |

| T <sub>WR</sub>  | Write recover time be-<br>fore read            | 6           |     | 6           |     | 6           |     | 6           |     | μs    |

| T <sub>CEL</sub> | CE low to output in low Z                      | 0           |     | 0           |     | 0           |     | 0           |     | ns    |

| T <sub>CDF</sub> | CE high to output in high Z                    |             | 40  |             | 40  |             | 55  |             | 60  | ns    |

| T <sub>OEL</sub> | OE low to output in low Z                      | 0           |     | 0           |     | 0           |     | 0           |     | ns    |

<sup>(1)</sup> whichever occurs first.

Table 10 : A.C. CHARACTERISTICS Write/Erase/Program Operations (1)

| Symbol             | Characteristic                         | M28F2 | 56-100 | M28F256-120 |      | M28F256-150 |      | M28F256-200 |      | Unit |

|--------------------|----------------------------------------|-------|--------|-------------|------|-------------|------|-------------|------|------|

| Symbol             | Characteristic                         | Min   | Max    | Min         | Max  | Min         | Max  | Min         | Max  | Oill |

| Twc                | Write cycle time                       | 100   |        | 120         |      | 150         |      | 200         |      | ns   |

| T <sub>AS</sub>    | Address setup time                     | 0     |        | 0           |      | 0           |      | 0           |      | ns   |

| T <sub>AH</sub>    | Address hold time                      | 40    |        | 50          |      | 60          |      | 75          |      | ns   |

| T <sub>DS</sub>    | Data setup time                        | 50    |        | 50          |      | 50          |      | 50          |      | ns   |

| T <sub>DH</sub>    | Data hold time                         | 10    |        | 10          |      | 10          |      | 10          |      | ns   |

| T <sub>WHGL</sub>  | Write recover time before read         | 6     |        | 6           |      | 6           |      | 6           |      | μs   |

| T <sub>GHWL</sub>  | Read recover time before write         | 0     |        | 0           |      | 0           |      | 0           |      | μs   |

| T <sub>CS</sub>    | CE setup time                          | 20    |        | 20          |      | 20          |      | 20          |      | ns   |

| Тсн                | CE hold time                           | 0     |        | 0           |      | 0           |      | 0           |      | ns   |

| T <sub>WP</sub>    | Write pulse width                      | 40    |        | 40          |      | 50          |      | 60          |      | ns   |

| T <sub>WPH</sub>   | Write pulse width high                 | 40    |        | 40          |      | 50          |      | 60          |      | ns   |

| T <sub>WHWH1</sub> | Duration of pro-<br>gramming operation | 95    | 150    | 95          | 150  | 95          | 150  | 95          | 150  | μs   |

| T <sub>WHWH2</sub> | Duration of erase operation            | 9.5   | 10.5   | 9.5         | 10.5 | 9.5         | 10.5 | 9.5         | 10.5 | ms   |

| T <sub>VPEL</sub>  | V <sub>PP</sub> setup to CE low        | 100   |        | 100         |      | 100         |      | 100         |      | ns   |

| T <sub>ELEH</sub>  | Alternate write pulse width            | 40    |        | 40          |      | 50          |      | 60          |      | ns   |

Notes: (1) Refer to read timing table for read timing characteristics during Write/Read operations.

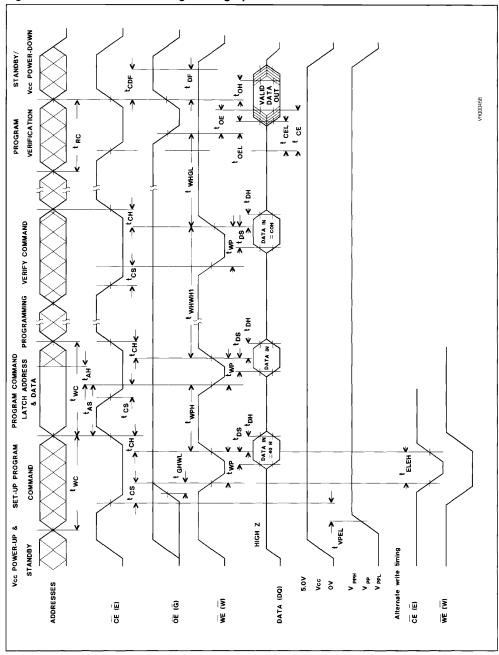

Figure 3: A.C. Waveforms for Programming Operations

Figure 4: Presto F Programming Algorithm

Notes: (1) C.R. = Command Register.

- (2) STOPS program generation program verify command is only performed after byte programming.

- (3) Second bus cycle of the setup Program/Program command (See Table 5 and Fig 4) starts programming operation.

- (4) Second bus cycle of the program verify command (See Table 5 and Fig 4).

- (5)  $T1 = 100\mu s$ ,  $T2 = 6\mu s$

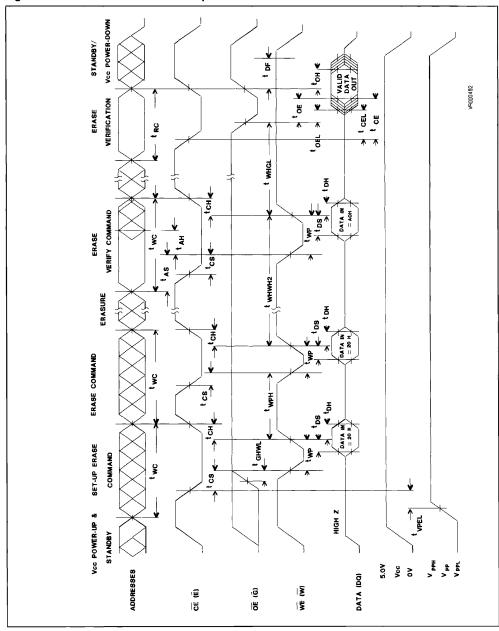

Figure 5 : A.C. Waveforms for Erase Operations

Figure 6: Presto F Erase Algorithm

Notes: (1) N = Pulse Count.

- (2) CR = Command Register.

- (3) Second Bus Cycle of Setup Erase/Erase command (see Table 5 and Fig. 5).

- (4) Address = byte to verify. Erase verify is only performed after chip Erasure.

- (5) Second bus cycle of Erase verify command.

- (6) T1 = 10ms, T2 = 6 $\mu$ s.

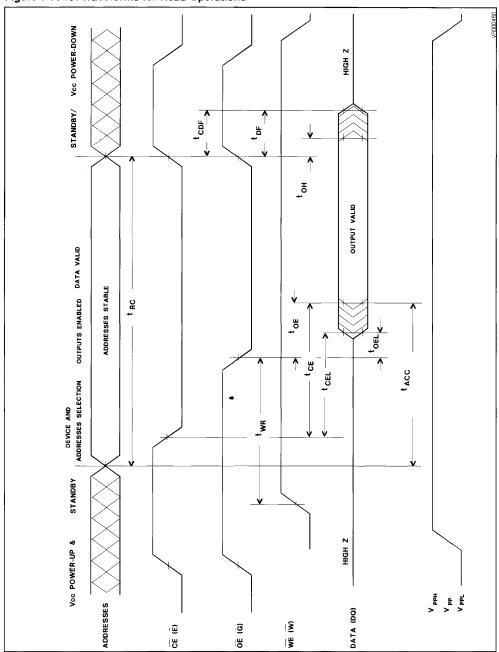

Figure 7 : A.C. Waveforms for Read Operations

# **PACKAGE MECHANICAL DATA**

Figure 8: 32 PIN CERAMIC DUAL IN LINE FREAT SEAL

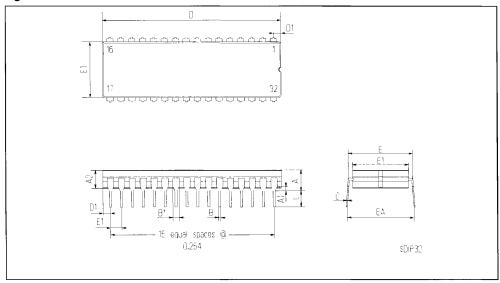

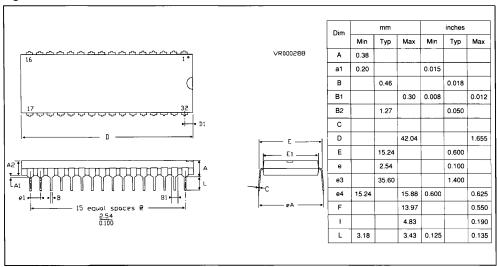

Figure 9: 32 PIN PLASTIC DUAL IN LINE

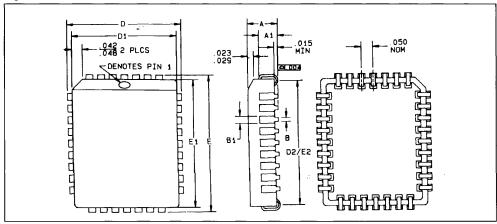

Figure 10: 32 PIN PLCC

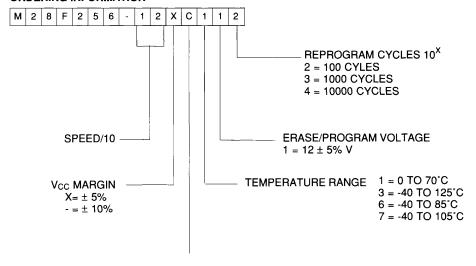

# ORDERING INFORMATION

**PACKAGE**

C = PLCC

B = PLASTIC DIL

F = CERAMIC FRIT SEAL