# 5

# P4C214 ULTRA HIGH-SPEED 16K x 16 LATCHED RAM

### **FEATURES**

- Pin Compatible with the Popular 2x4Kx16 I386 Cache RAM

- Supports Processor Speeds up to 50 MHz

- Easily Configurable

Direct Map 16Kx16

Two-Way Set 2x8Kx16

- On-chip Address Latch

- Separate Lower & Upper Byte Select

- Single 5V ±10% Power Supply

- **■** CMOS for Optimum Speed/Power

- Common Data I/O

- TTL Compatible Inputs & Outputs

- Three-State Outputs

- Package Options: 52-pin PLCC and 52-pin Quad Cerpack

# •

#### DESCRIPTION

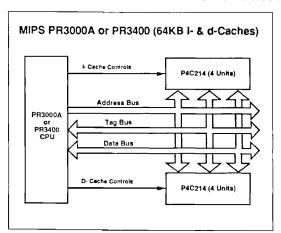

The P4C214 is a 262,144-bit ultra high-speed CMOS cache SCRAM (Static CMOS Random Access Memory) with latched addresses. It is ideally suited for cache RAM applications with the MIPS PR3000A/PR3400, and Intel's 80386 and 80486 processors. It is pin programmable into either a 2x8Kx16 or 16Kx16 configuration.

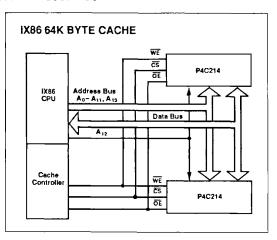

The P4C214 is functionally and pin compatible with the popular 2x4Kx16 cache RAM while providing twice the density, thus allowing a very easy upgrade from 32K byte cache to 64K byte (or larger) cache.

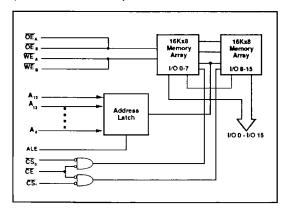

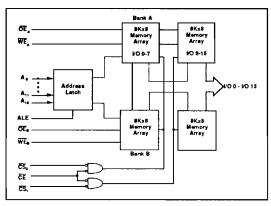

A mode control pin (MODE) controls the configuration of the memory. When this pin is LOW, the SCRAM functions as a direct mapped 16Kx16-bit RAM with A12 having a faster addressing speed. When the MODE pin is HIGH, the SCRAM functions as a two-way associative 2x8Kx16. In this mode, address bit A12 is not used and should be externally wired to ground. In either mode, the new higher-order address bit, A13, allows expanding the cache depth from 4K to 8K or from 8K to 16K in the same 52-pin footprint. Thus, two devices form a 64K byte cache; four devices form a 128 K byte cache, when used with an iX86.

The P4C214 is manufactured using PACE III technology and is supported by a six-inch wafer fabrication production facility.

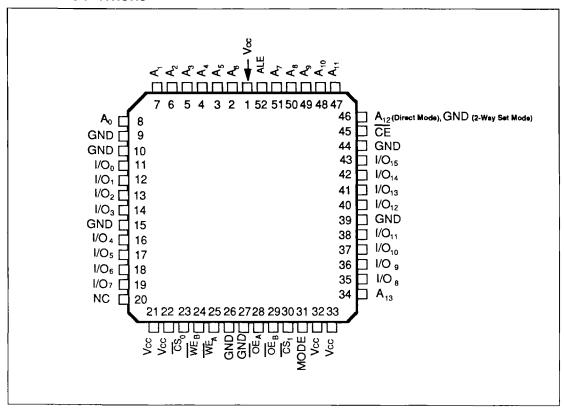

The P4C214 is available in a 52-pin PLCC and also in a 52-pin Quad Cerpack surface-mount package; each provides excellent board-level density.

#### \*

# DIRECT MAP (MODE = L) (For R3000 & iX86)

# TWO-WAY SET (MODE = H) (For iX86)

Means Quality, Service and Speed

# **PIN DESCRIPTIONS**

| Pin Number(s)                                                       | Symbol                                             | Туре              | Description                                                                                                                                                                                 |

|---------------------------------------------------------------------|----------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2, 3, 4, 5, 6, 7, 8, 34,<br>47,48, 49, 50, 51                       | A <sub>0</sub> -A <sub>11</sub><br>A <sub>13</sub> | Input             | Address Inputs: These signals are latched on the negative edge of ALE.                                                                                                                      |

| 46                                                                  | A <sub>12</sub>                                    | Input             | Fast Latched Address Input: This address is latched on the negative edge of ALE. Used in direct mode only.  Must be GND for 2-way mode.                                                     |

| 52                                                                  | ALE                                                | Input             | Address Latch Enable: When ALE is high, the latch is transparent. The negative edge latches the current address inputs (A <sub>b</sub> -A <sub>13</sub> )                                   |

| 45                                                                  | CE                                                 | Input             | Chip Enable: To facilitate depth expansion.                                                                                                                                                 |

| 23, 30                                                              | CS <sub>0</sub> ,CS <sub>1</sub>                   | Input             | Byte Selects: These control signals control the lower and upper byte selection on the A or B side of the array. They also facilitate depth expansion.                                       |

| 28, 29                                                              | ŌĒ₄,ŌĒ <sub>в</sub>                                | Input             | Output Enables: In the Two-Way Set Associative Mode,<br>Active LOW enables cache bank A or B to drive the data bus.<br>In the direct mode, these two pins must be wired together.           |

| 24, 25                                                              | WE <sub>B</sub> ,WE <sub>A</sub>                   | Input             | Write Enables: These active LOW signals enable bank A or B. In the Two-Way Associative Mode, data may be written to bank A or B. In the direct mode, these two pins must be wired together. |

| 11, 12, 13, 14, 16,<br>17, 18, 19, 35, 36<br>37, 38, 40, 41, 42, 43 | I/O <sub>0</sub> - I/O <sub>15</sub>               | 1/0               | I/O: Data inputs and outputs.                                                                                                                                                               |

| 1, 21, 22, 32, 33                                                   | Vcc                                                | Supply<br>Voltage | 5V ±10%                                                                                                                                                                                     |

| 9, 10, 15, 26,<br>27, 39, 44                                        | GND                                                | GND               | Ground                                                                                                                                                                                      |

| 31                                                                  | MODE                                               | Input             | Configuration Control: When signal is LOW, the device function as a direct map 16Kx16. When signal is HIGH, the device functions as a two-way associative 2x8Kx16.                          |

3197 01

#### PIN CONFIGURATIONS

#### CACHE RAM CONFIGURATIONS FOR PR3000A AND i386/i486

# **ABSOLUTE MAXIMUM RATINGS**(1)

| Symbol           | Parameter                                          | Value                           | Unit |

|------------------|----------------------------------------------------|---------------------------------|------|

| V <sub>cc</sub>  | Supply Voltage                                     | -0.5 to +7.0                    | v    |

| V <sub>IN</sub>  | DC Input Voltage                                   | -0.5 to +7.0                    | ٧    |

| V <sub>IO</sub>  | DC Input Voltage<br>Applied to Output<br>in High-Z | -0.5 to<br>V <sub>cc</sub> +0.5 | ٧    |

| P <sub>D</sub>   | Power Dissipation                                  | 1.5                             | W    |

| T <sub>OPR</sub> | Operating<br>Temperature                           | -55 to +125                     | °C   |

| Symbol           | Parameter              | Value       | Unit |

|------------------|------------------------|-------------|------|

| T <sub>stg</sub> | Storage<br>Temperature | -65 to +150 | °C   |

3197 02

# RECOMMENDED OPERATING TEMPERATURE AND SUPPLY VOLTAGE

3197 09

| Grade    | Ambient<br>Temperature | GND | V <sub>cc</sub> |

|----------|------------------------|-----|-----------------|

| Military | -55 to +125°C          | 0V  | 5.0V ± 10%      |

| Grade      | Ambient<br>Temperature | CND |            |

|------------|------------------------|-----|------------|

| Commercial | 0°C to +70°C           | 0V  | 5.0V ± 10% |

3197 03

### DC ELECTRICAL CHARACTERISTICS

Over recommended operating temperature and supply voltage

| Symbol           | Parameter                    | Test Conditions                                          | P4                | Ī                    |      |

|------------------|------------------------------|----------------------------------------------------------|-------------------|----------------------|------|

|                  |                              | rest Conditions                                          | Min               | Max                  | Unit |

| V <sub>IH</sub>  | Input High Voltage           |                                                          | 2.2               | V <sub>cc</sub> +0.5 | V    |

| V <sub>IL</sub>  | Input Low Voltage            |                                                          | -0.5 <sup>2</sup> | 0.8                  | V    |

| l <sub>u</sub>   | Input Leakage Current        | GND < V <sub>IN</sub> < V <sub>CC</sub>                  | -10               | +10                  | μА   |

| I <sub>LO</sub>  | Output Leakage Current       | GND < V <sub>o</sub> < V <sub>cc</sub> , Output Disabled | -10               | +10                  | μA   |

| _l <sub>cc</sub> | VCC Operating Current        | $V_{cc} = Max.$ , $I_{out} = 0$ mA, $f = max$ (Note 4)   |                   | 360                  | mA   |

| V <sub>oL</sub>  | Output Low Voltage           | V <sub>CC</sub> = Min., I <sub>Oi</sub> = 8 mA           |                   | 0.4                  | V    |

| V <sub>OH</sub>  | Output High Voltage          | $V_{cc} = Min., I_{OH} = -4 \text{ mA}$                  | 2.4               |                      | V    |

| I <sub>os</sub>  | Output Short Circuit Current | V <sub>cc</sub> = Max., I <sub>out</sub> = GND           |                   | -350                 | mA   |

# **CAPACITANCES**3

$(V_{CC} = 5.0V, T_A = 25^{\circ}C, f = 1.0MHz)$

| Symbol          | Parameter         | Conditions          | Тур. | Unit |

|-----------------|-------------------|---------------------|------|------|

| C <sub>IN</sub> | Input Capacitance | V <sub>IN</sub> =0V | 5    | рF   |

#### Notes:

1. Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to MAXIMUM rating conditions for extended periods may affect reliability.

| Symbol | Parameter          | Conditions     | Тур. | Unit |

|--------|--------------------|----------------|------|------|

| Соп    | Output Capacitance | $V_{OUT} = 0V$ | 8    | рF   |

3197.05

3197 04

- 2. Transient inputs with  $V_{\rm IL}$  &  $I_{\rm IL}$  not more negative than  $-3.0{\rm V}$  and -100mA, respectively, are permissible for pulse widths up to 20ns

- 3. This parameter is sampled and not 100% tested.

- 4.  $\frac{1}{CE}$  is measured with input levels at 0.0V and 3.0V except  $\overline{OE}_{\text{A}}$  &  $\overline{OE}_{\text{B}} \ge 3.0V$ .

# **AC ELECTRICAL CHARACTERISTICS - READ CYCLE**

(Vcc =  $5V \pm 10\%$ , All Temperature Ranges)

| Sym               | Parameter                     | -13 |     | -13 -17 |     | -20 |     | -:  | 25  | -35 |     | ]     |

|-------------------|-------------------------------|-----|-----|---------|-----|-----|-----|-----|-----|-----|-----|-------|

|                   |                               | Min | Max | Min     | Max | Min | Max | Min | Max | Min | Max | Units |

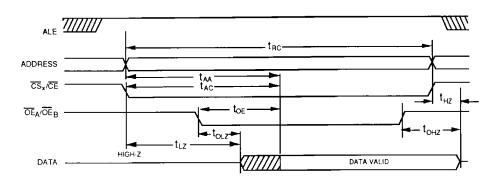

| t <sub>ec</sub>   | Read Cycle Time               | 13  |     | 17      |     | 20  |     | 25  |     | 35  |     | ns    |

| t <sub>M</sub>    | Address Access Time           |     | 13  |         | 17  |     | 20  |     | 25  | 1   | 35  | ns    |

| t <sub>AA12</sub> | Fast Address Access Time      |     | 9   |         | 11  | 1   | 13  |     | 17  |     | 25  | ns    |

| t <sub>AC</sub>   | Chip Select Access Time       |     | 8   |         | 9   |     | 10  |     | 12  |     | 15  | ns    |

| t <sub>o∈</sub>   | Output Enable to Output Valid | 1   | 6   | 1       | 7   |     | 8   |     | 10  |     | 13  | ns    |

| t <sub>oh</sub>   | Output HOLD from address      |     |     | 1       |     |     | Ì   |     |     |     |     |       |

| VIII              | change                        | 2   | l   | 3       |     | 3   | l   | 3   |     | 3   |     | ns    |

| t <sub>ız</sub>   | Chip Enable to low-Z          | 2   |     | 2       |     | 3   |     | 3   |     | 3   |     | ns    |

| toz               | Output Enable to low-Z        | 2   | ŀ   | 2       | Ì   | 2   |     | 2   |     | 2   |     | ns    |

| t <sub>HZ</sub>   | Chip Enable to high-Z         |     | 9   | ļ       | 10  |     | 12  |     | 15  |     | 25  | ns    |

| t <sub>orz</sub>  | Output Enable to high-Z       |     | 5   |         | 6   |     | 8   |     | 10  |     | 14  | ns    |

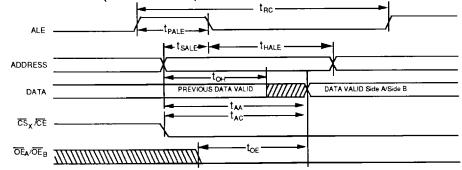

| t <sub>PALE</sub> | ALE pulse width               |     | 6   |         | 6   |     | 6   |     | 8   |     | 10  | ns    |

| t <sub>sale</sub> | Address Setup to ALE Low      |     | 2   |         | 2   | 1   | 2   |     | 3   |     | 6   | ns    |

| t <sub>HALE</sub> | Address Hold from ALE Low     |     | 2   |         | 2   |     | 2   |     | 2   |     | 4   | ns    |

Notes: 1. t<sub>12</sub>, t<sub>12</sub>, t<sub>012</sub>, t<sub>012</sub> are measured ±200mV from Z-level.

2. Worst case for  $t_{\infty}$  is when  $\overline{OE}_{A}$  goes HIGH at the same time that  $\overline{OE}_{B}$  goes LOW, and vice versa. However, such simultaneous switching does not occur in 2-way set associative or in direct mode cache applications.

# **READ CYCLE NO.1 (ALE Controlled)**

### **READ CYCLE NO.2 (Address Controlled)**

# AC ELECTRICAL CHARACTERISTICS - WRITE CYCLE

(VCC= 5V ±10%, All Temperature Ranges)

| Sym               | Parameter                      | -13 |     | -17 |     | -20 |     | -25 |     | -35 |     |       |  |

|-------------------|--------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-------|--|

|                   |                                | Min | Max | Units |  |

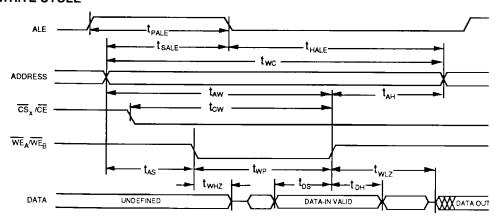

| t <sub>wc</sub>   | Write Cycle Time               | 13  |     | 17  |     | 20  |     | 25  |     | 35  |     | ns    |  |

| t <sub>aw</sub>   | Address Setup to End of Write  | 13  |     | 17  |     | 17  |     | 18  |     | 25  |     | ns    |  |

| t <sub>cw</sub>   | Chip Select to End of Write    | 13  |     | 17  |     | 17  |     | 18  |     | 25  |     | ns    |  |

| t <sub>os</sub>   | Data Setup to End of Write     | 5.5 | ŀ   | 8   |     | 8   |     | 10  |     | 10  |     | ns    |  |

| t <sub>DH</sub>   | Data Hold from End of Write    | 0   | Ì   | 0   |     | 0   |     | 0   |     | 0   |     | ns    |  |

| twp               | Write Enable Pulse Width       | 8   |     | 12  |     | 15  |     | 18  |     | 25  |     | ns    |  |

| tas               | Address Setup to Write Enable  | 0   |     | 0   |     | 0   |     | 0   |     | 0   |     | ns    |  |

| t <sub>ah</sub>   | Address Hold from Write Enable | 0   |     | 0   |     | 0   |     | 0   |     | 0   |     | ns    |  |

| t <sub>w.z</sub>  | Write Enable High to Low-Z     | 2   |     | 2   |     | 2   |     | 3   |     | 3   |     | ns    |  |

| t <sub>wiz</sub>  | Write Enable Low to High-Z     |     | 9   |     | 11  |     | 13  |     | 15  | 1   | 15  | ns    |  |

| t <sub>pale</sub> | ALE Pulse Width                |     | 6   |     | 6   |     | 6   |     | 8   |     | 10  | ns    |  |

Note:  $t_{\text{w.Z}}$ ,  $t_{\text{w.Z}}$  are measured  $\pm 200\text{mV}$  from Z-level.

# **WRITE CYCLE**

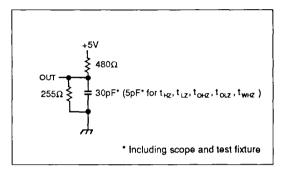

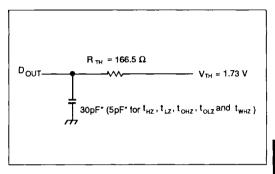

#### **AC TEST CONDITIONS**

| Input Pulse Levels            | GND to 3.0V       |

|-------------------------------|-------------------|

| Input Rise and Fall Times     | 3ns               |

| Input Timing Reference Level  | 1.5V              |

| Output Timing Reference Level | 1.5V              |

| Output Load                   | See Figures 1 & 2 |

319709

Figure 1. Output Load

#### Note:

Because of the ultra-high speed of the P4C214, care must be taken when testing this device; an inadequate setup can cause a normal functioning part to be rejected as faulty. Long high-inductance leads that cause supply bounce must be avoided by bringing the  $V_{cc}$  and ground planes directly up to the contactor fingers. A 0.01  $\mu F$  high frequency capacitor is also required between  $V_{cc}$  and ground. To avoid signal reflections, proper termination must be used; for example, a 50 $\Omega$  test environment should be terminated into a 50 $\Omega$  load with 1.73V (Thevenin Voltage) at the comparator input, and a 116 $\Omega$  resistor must be used in series with  $D_{ccn}$  to match 166 $\Omega$  (Thevenin Resistance).

Figure 2. Thevenin Equivalent

<sup>\*</sup> Including scope and test fixture.

# **TRUTH TABLES**

# TWO-WAY SET, 2X8KX16 (MODE = HIGH)

| Mode                                                  | CE | cs <sub>°</sub> | CS, | OE | ŌĒ, | WE | WE, | 1/0              |

|-------------------------------------------------------|----|-----------------|-----|----|-----|----|-----|------------------|

| Standby                                               | н  | х               | Х   | х  | Х   | х  | х   | High Z           |

|                                                       | L  | Н               | Н   | X  | X   | Х  | X   | High Z           |

| Output Disabled                                       | Х  | Х               | Х   | Н  | Н   | Х  | Х   | High Z           |

|                                                       | X  | Х               | Х   | L  | L   | Х  | X   | High Z           |

| Read I/0, I/0, Bank A                                 | L  | L               | Н   | L  | Н   | Н  | Н   | D <sub>out</sub> |

| Read I/0, I/0, Bank B                                 | L  | L               | Н   | Н  | L   | Н  | Н   | D <sub>out</sub> |

| Read I/0 <sub>8</sub> I/0 <sub>15</sub> Bank A        | L  | Н               | L   | L  | Н   | Н  | Н   | D <sub>out</sub> |

| Read I/0 <sub>8</sub> — I/0 <sub>15</sub> Bank B      | L  | Н               | L   | Н  | L   | н  | н   | D <sub>out</sub> |

| Read I/0 - I/0 Bank A                                 | L  | L               | L   | L  | Н   | Н  | Н   | D <sub>out</sub> |

| Read I/0, I/0 <sub>15</sub> Bank B                    | L  | L               | L   | Н  | L   | Н  | Н   | D <sub>out</sub> |

| Write I/0, I/0, Bank A                                | L  | L               | Н   | Х  | Х   | L  | Н   | D <sub>in</sub>  |

| Write I/0, I/0, Bank B                                | L  | L               | Н   | Х  | Х   | Н  | L   | D                |

| Write I/O <sub>8</sub> — I/O <sub>15</sub> Bank A     | L  | Н               | L   | Х  | X   | L  | Н   | D <sub>in</sub>  |

| Write I/0 <sub>8</sub> — I/0 <sub>15</sub> Bank B     | L  | Н               | L   | Х  | Х   | Н  | L   | D                |

| Write I/0 - I/0 Bank A                                | L  | L               | L   | Х  | X   | L  | Н   | D                |

| Write I/O <sub>0</sub> — I/O <sub>15</sub> Bank B     | L  | ٦               | L   | Х  | Х   | Н  | L   | D <sub>IN</sub>  |

| Write I/0, I/0, Bank A & B                            | L  | ٦               | Н   | Х  | X   | L  | L   | D <sub>IN</sub>  |

| Write I/0 <sub>8</sub> — I/0 <sub>15</sub> Bank A & B | L  | Н               | L   | Х  | X   | L  | L   | D <sub>in</sub>  |

| Write I/0, I/0, Bank A & B                            | L  | L               | ٦   | X  | X   | L  | L   | D <sub>IN</sub>  |

# DIRECT MAP, 16KX16 (MODE = LOW)

| Mode                                       | CE | ¯CS <sub>o</sub> | cs, | OE,/OE | WE,/WE, | 1/0              |

|--------------------------------------------|----|------------------|-----|--------|---------|------------------|

| Standby                                    | Н  | Х                | Х   | Х      | Х       | High Z           |

|                                            | L  | Н                | Н   | Х      | Х       | High Z           |

| Output Disabled                            | X  | Х                | Х   | Н      | Х       | High Z           |

| Read I/0,— I/0,                            | L  | L                | Н   | L      | Н       | D <sub>out</sub> |

| Read I/0 <sub>8</sub> I/0 <sub>15</sub>    | L  | Н                | L   | L      | Н       | D <sub>out</sub> |

| Read I/0 <sub>0</sub> — I/0 <sub>15</sub>  | L  | L                | L   | L      | Н       | D <sub>out</sub> |

| Write I/0,— I/0,                           | L  | L                | Н   | Х      | L       | D <sub>in</sub>  |

| Write I/O <sub>8</sub> — I/O <sub>15</sub> | L  | Н                | L   | Х      | L       | D <sub>IN</sub>  |

| Write I/0 <sub>0</sub> I/0 <sub>15</sub>   | L  | L                | L   | Х      | L       | D <sub>IN</sub>  |

Note: 1.  $\overline{CE}$ , when taken inactive while  $\overline{WE}_A$  or  $\overline{WE}_B$  remain active, allows a chip enable controlled write to be performed.

2. X = H or L

# 5

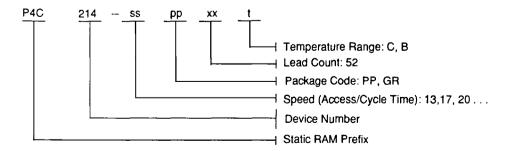

### **PACKAGE SUFFIX**

| Package<br>Suffix | Description                        |  |  |  |  |

|-------------------|------------------------------------|--|--|--|--|

| PP                | Plastic Leaded Chip Carrier (PLCC) |  |  |  |  |

| GR                | Quad Cerpak (J-Bend Leads)         |  |  |  |  |

### **TEMPERATURE RANGE SUFFIX**

| Temperature<br>Range Suffix | Description                                          |

|-----------------------------|------------------------------------------------------|

| С                           | Commercial Temperature Range, 0°C to +70°C.          |

| В                           | -55°C to +125°C with MIL-STD-883D Class B compliance |

9197 11

### **SELECTION GUIDE**

The P4C214 is available in the following temperature, speed and package options.

| Temperature<br>Range   | Package        | 13ns      | 17ns      | 20ns      | 25ns      | 35ns      |

|------------------------|----------------|-----------|-----------|-----------|-----------|-----------|

| Commercial             | PLCC           | -13 PP52C | -17 PP52C | -20 PP52C | -25 PP52C | -35 PP52C |

| Military<br>Processed* | Quad<br>CERPAK | N/A       | N/A       | N/A       | -25 GR52B | -35 GR52B |

Military temperature range with MIL-STD-883 Revision D, Class B processing.

N/A = Not available

31871

The P4C214 supports the high performance processor speeds of the i386 and i486, and the PR3000A/PR3400.

| Processor | Frequency | Access Time | Output Enable | Performance Part Type |

|-----------|-----------|-------------|---------------|-----------------------|

|           | 40 MHz    | 20ns        | 8ns           | P4C214 - 20           |

| i386      | 33 MHz    | 25ns        | 10ns          | P4C214 - 25           |

|           | 25 MHz    | 35ns        | 13ns          | P4C214 - 35           |

| i486      | 50 MHz    | 14ns        | 7ns           | P4C214 - 13           |

|           | 33 MHz    | 19ns        | 8ns           | P4C214 - 17           |

|           | 40 MHz    | 13ns        | 5ns           | P4C214 - 13           |

| R3000     | 33 MHz    | 17ns        | 7ns           | P4C214 - 17           |

|           | 25 MHz    | 23ns        | 9ns           | P4C214 - 20           |

3197 20

#### ORDERING INFORMATION

The following part numbering scheme is used for

1519 09