**DENSE-PAC** MICROSYSTEMS

M-Densus

High Density Memory Device

512 Megabit CMOS DRAM 256 Megabit CMOS DRAM 128 Megabit CMOS DRAM

4Ø VSS

39 DQ8

38 DQ7

37 DQ6

35 VSS

34 CASØ

33 OE

32 N.C.

31 A11 30 A10

29 A9

28 A8

27 A7

26 A6

25 VSS

36 DQ5

**PIN-OUT DIAGRAM**

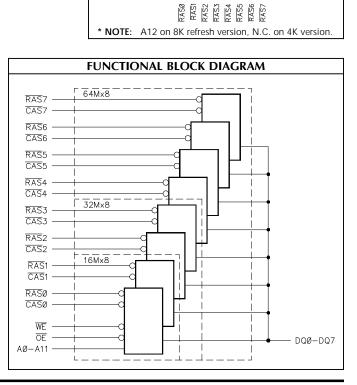

CAS7 CAS6 CAS6 CAS5 CAS3 CAS3 CAS3 CAS2 CAS2 CAS2

$\begin{smallmatrix} 4 & 4 \\ 7 & 4 \\ 6 & 4 \\ 6 & 4 \\ 7 & 4 \\ 6 & 4 \\ 7 & 4 \\ 6 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 4 \\ 7 & 7 \\ 7 & 7 \\ 7 & 7 \\ 7 & 7 \\ 7 & 7 \\ 7 & 7 \\ 7 & 7 \\ 7 & 7 \\ 7 & 7 \\ 7 & 7 \\ 7 & 7 \\ 7 & 7 \\ 7 & 7 \\ 7$

17 19 20 21 22 23 23 24

PIN 1

INDEX

VDD 1

DQ1 2

DQ2 3

DQ3 4

DQ4 5

N.C. 6

VDD 7

WE 8

AØ 1Ø A1 11

A2 12

A3 13

A4 14

A5 15

VDD 16

RASØ 9

$\cap$

## **DESCRIPTION:**

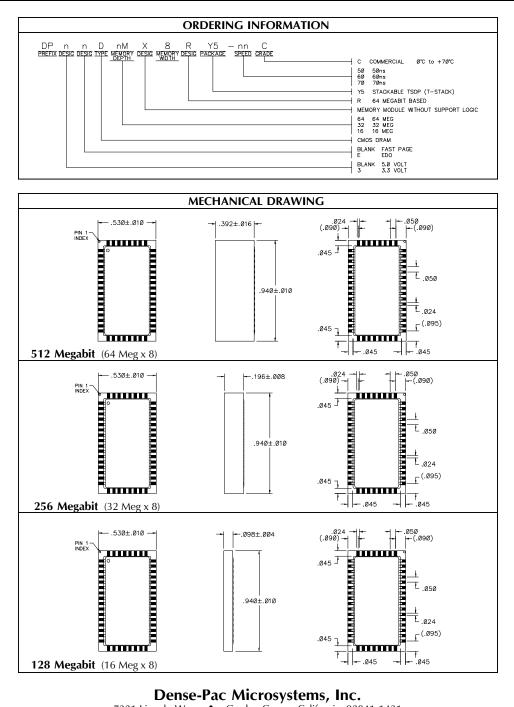

The *M*-*D*ensus series is a family of interchangeable memory modules. The 64 Megabit DRAM is a member of this family which utilizes the new and innovative space saving TSOP technology. The modules are constructed with 8 Meg x 8 DRAM's available in 512, 256 and 128 Megabits.

The 64 Megabit based/*M-Densus* modules have been designed to fit in the same footprint as the 8 Meg x 8 DRAM TSOP monolithic and are backward compatible with the 16 Megabit based family of/*M-Densus* modules. This allows the memory board designer to upgrade the memory in their products without redesigning the memory board, thus saving time and money.

## FEATURES:

- Configurations Available:

- 512 Megabit: 64 Meg x 8

- 256 Megabit: 32 Meg x 8

- 128 Megabit: 16 Meg x 8

- Access Times: 50, 60, 70ns (max.)

- 5.0V or 3.3V Supply

- Common Data Inputs and Outputs

- EDO or Fast Page Mode Capability

- 4096 Cycles / 64 ms

- 3 Variations of Refresh:

- RAS only Refresh

- CAS before RAS Refresh

- Hidden Refresh

- Package: Leadless TSOP Module

| PIN NAMES                           |                                                                     |

|-------------------------------------|---------------------------------------------------------------------|

| A0 - A11                            | Row Address:A0 - A11Column Address:A0 - A11Refresh Address:A0 - A11 |

| DQ0 - DQ7                           | Data In / Data Out                                                  |

| $\overline{CAS}0 - \overline{CAS}7$ | Column Address Strobes                                              |

| $\overline{RAS}0 - \overline{RAS}7$ | Row Address Enables                                                 |

| WE                                  | Data Write Enable                                                   |

| ŌĒ                                  | Data Output Enable                                                  |

| V <sub>DD</sub>                     | Power Supply (+5V/3.3V)                                             |

| Vss                                 | Ground                                                              |

| N.C.                                | No Connect                                                          |

This document contains information on a product that is currently released to production at Dense-Pac Microsystems, Inc. Dense-Pac reserves the right to change products or specifications herein without prior notice.

## 64 Megabit DRAM Based M-Densus

Dense-Pac Microsystems, Inc.

Dense-Pac Microsystems, Inc.

7321 Lincoln Way ◆

Garden Grove , California 92841-1431

(714) 898-0007

(800) 642-4477 (Outside CA)

◆ FAX: (714) 897-1772 ◆ http://www.dense-pac.com

30A179-00 REV. C