## S-8253C/D Series

## BATTERY PROTECTION IC FOR 2-SERIES OR 3-SERIES-CELL PACK

www.sii-ic.com

© Seiko Instruments Inc., 2008-2010

Rev.2.0\_00

The S-8253C/D Series is a protection ICs for 2-series or 3-series cell lithium-ion rechargeable battery and includes high-accuracy voltage detector and delay circuit.

This IC is suitable for protecting lithium-ion battery packs from overcharge, overdischarge and overcurrent.

### ■ Features

(1) High-accuracy voltage detection for each cell

Overcharge detection voltage n (n = 1 to 3)

Overcharge release voltage n (n = 1 to 3)

Overdischarge detection voltage n (n = 1 to 3)

Overdischarge release voltage n (n = 1 to 3)

Overdischarge release voltage n (n = 1 to 3)

Overdischarge release voltage n (n = 1 to 3)

Overdischarge release voltage n (n = 1 to 3)

Overdischarge release voltage n (n = 1 to 3)

Overdischarge release voltage n (n = 1 to 3)

Overdischarge release voltage n (n = 1 to 3)

Overdischarge release voltage n (n = 1 to 3)

(2) Three-level overcurrent detection (Including load short circuiting detection)

Overcurrent detection voltage 1

0.05 V to 0.30 V (50 mV step)

Accuracy ±25 mV

Overcurrent detection voltage 2

Overcurrent detection voltage 3

U.5 V (Fixed)

1.2 V (Fixed)

- (3) Delay time (Overcharge, Overdischarge, Overcurrent) is available by only using an internal circuit. (External capacitors are unnecessary).

- (4) Charge / discharge operation can be inhibited by the control pin.

- (5) 0 V battery charge function available / unavailable are selectable.

- (6) High-voltage withstand devices Absolute maximum rating 26 V

- (7) Wide range of operating voltage

2 V to 24 V

(8) Wide range of operating temperature

-40°C to +85°C

- (9) Low current consumption

- Operation mode

Power-down mode

28 μA max. (+25°C)

Double 1 μA max. (+25°C)

- (10) Lead-free, Sn100%, halogen-free\*3

- \*1. Overcharge release voltage = Overcharge detection voltage Overcharge hysteresis voltage (Overcharge hysteresis voltage n (n = 1 to 3) can be selected in 0 V, or in 0.1 V to 0.4 V in 50 mV step.)

- \*2. Overdischarge release voltage = Overdischarge detection voltage + Overdischarge hysteresis voltage (Overdischarge hysteresis voltage n (n = 1 to 3) can be selected in 0 V, or in 0.2 V to 0.7 V in 100 mV step.)

- \*3. Refer to "Product Name Structure" for details.

## Applications

- · Lithium-ion rechargeable battery packs

- Lithium polymer rechargeable battery packs

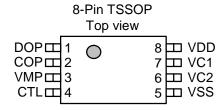

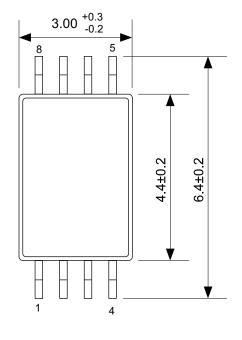

## Package

8-Pin TSSOP

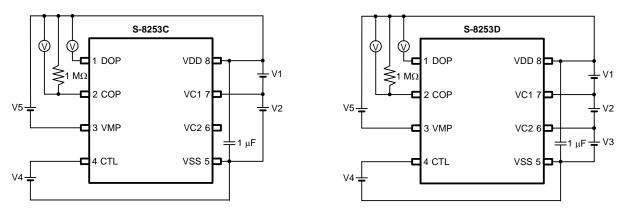

## ■ Block Diagrams

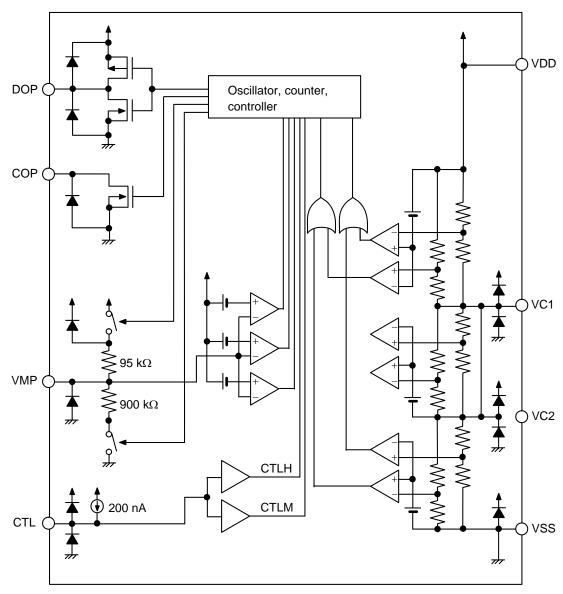

## 1. S-8253C Series

**Remark** All diodes shown in figure are parasitic diodes.

Figure 1

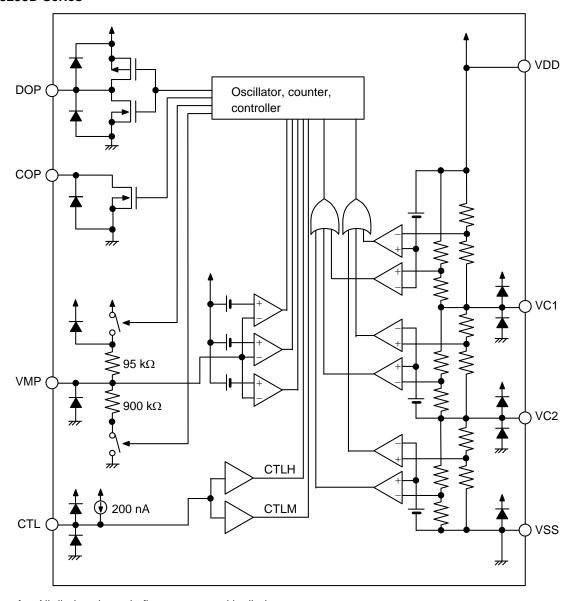

## 2. S-8253D Series

**Remark** All diodes shown in figure are parasitic diodes.

Figure 2

## ■ Product Name Structure

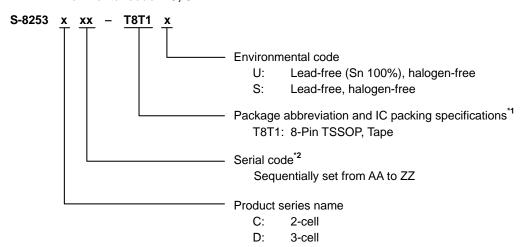

## 1. Product Name

### 1. 1 Environmental code = U, S

- \*1. Refer to the tape specifications.

- \*2. Refer to the "3. Product Name List".

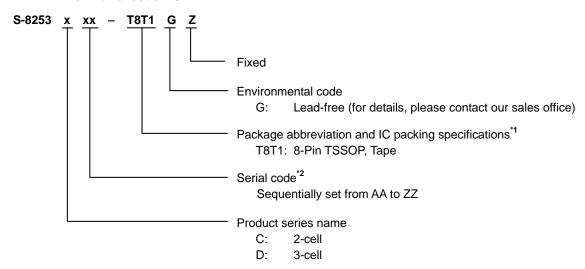

### 1. 2 Environmental code = G

- \*1. Refer to the tape specifications.

- \*2. Refer to the "3. Product Name List".

## 2. Package

|              | Packago Namo              | Drawing Code |              |              |  |  |  |

|--------------|---------------------------|--------------|--------------|--------------|--|--|--|

| Package Name |                           | Package      | Tape         | Reel         |  |  |  |

| 8-Pin TSSOP  | Environmental code = G, S | FT008-A-P-SD | FT008-E-C-SD | FT008-E-R-SD |  |  |  |

|              | Environmental code = U    | FT008-A-P-SD | FT008-E-C-SD | FT008-E-R-S1 |  |  |  |

## 3. Product Name List

Table 1 S-8253C Series (For 2-Serial Cell)

| Model No.        | Overcharge<br>detection voltage<br>[V <sub>CU</sub> ] | Overcharge<br>release voltage<br>[V <sub>CL</sub> ] | Overdischarge<br>detection voltage<br>[V <sub>DL</sub> ] | Overdischarge<br>release voltage<br>[V <sub>DU</sub> ] | Overcurrent detection voltage 1 [V <sub>IOV1</sub> ] | 0 V battery<br>charge function |

|------------------|-------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------|------------------------------------------------------|--------------------------------|

| S-8253CAA-T8T1□□ | 4.350 ±0.025 V                                        | 4.050 ±0.050 V                                      | 2.40 ±0.080 V                                            | 2.70 ±0.100 V                                          | 0.300 ±0.025 V                                       | Available                      |

| S-8253CAD-T8T1□□ | 4.250 ±0.025 V                                        | 4.050 ±0.050 V                                      | 2.40 ±0.080 V                                            | 2.70 ±0.100 V                                          | 0.120 ±0.025 V                                       | Available                      |

| S-8253CAH-T8T1□□ | 4.350 ±0.025 V                                        | 4.150 ±0.050 V                                      | 2.30 ±0.080 V                                            | 2.30 ±0.080 V                                          | 0.090 ±0.025 V                                       | Available                      |

| S-8253CAI-T8T1□□ | 4.250 ±0.025 V                                        | 4.050 ±0.050 V                                      | 2.40 ±0.080 V                                            | 2.70 ±0.100 V                                          | 0.200 ±0.025 V                                       | Available                      |

Table 2 S-8253D Series (For 3-Series Cell)

| Model No.        | Overcharge<br>detection voltage<br>[V <sub>CU</sub> ] | Overcharge<br>release voltage<br>[V <sub>CL</sub> ] | Overdischarge<br>detection voltage<br>[V <sub>DL</sub> ] | Overdischarge<br>release voltage<br>[V <sub>DU</sub> ] | Overcurrent detection voltage 1 [V <sub>IOV1</sub> ] | 0 V battery<br>charge function |

|------------------|-------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------|------------------------------------------------------|--------------------------------|

| S-8253DAA-T8T1□□ | 4.350 ±0.025 V                                        | 4.050 ±0.050 V                                      | 2.40 ±0.080 V                                            | 2.70 ±0.100 V                                          | 0.300 ±0.025 V                                       | Available                      |

| S-8253DAB-T8T1□□ | 4.300 ±0.025 V                                        | 4.050 ±0.050 V                                      | 2.70 ±0.080 V                                            | 3.00 ±0.100 V                                          | 0.200 ±0.025 V                                       | Unavailable                    |

| S-8253DAD-T8T1y  | 4.250 ±0.025 V                                        | 4.050 ±0.050 V                                      | 2.40 ±0.080 V                                            | 2.70 ±0.100 V                                          | 0.120 ±0.025 V                                       | Available                      |

| S-8253DAI-T8T1□□ | 4.350 ±0.025 V                                        | 4.150 ±0.050 V                                      | 2.20 ±0.080 V                                            | 2.40 ±0.100 V                                          | 0.160 ±0.025 V                                       | Available                      |

| S-8253DAK-T8T1y  | 4.350 ±0.025 V                                        | 4.050 ±0.050 V                                      | 2.40 ±0.080 V                                            | 2.70 ±0.100 V                                          | 0.300 ±0.025 V                                       | Available                      |

**Remark 1.** □□: GZ or U y: S or U

2. Please select products of environmental code = U for Sn 100%, halogen-free products.

## ■ Pin Configuration

Figure 3

Table 3 S-8253C Series

| Pin No. | Symbol | Description                                                                                                                                                                           |

|---------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | DOP    | Connection pin for discharge control FET gate (CMOS output)                                                                                                                           |

| 2       | COP    | Connection pin for charge control FET gate (Nch open-drain output)                                                                                                                    |

| 3       | VMP    | Pin for voltage detection between VDD and VMP (Detection pin for overcurrent)                                                                                                         |

| 4       | CTL    | Input pin for charge / discharge control signal, Pin for shortening test time ( L : Normal operation, H : inhibit charge / discharge M (V <sub>DD</sub> × 1 / 2) : shorten test time) |

| 5       | VSS    | Input pin for negative power supply,  Connection pin for negative voltage of battery 2                                                                                                |

| 6       | VC2    | No connection *1                                                                                                                                                                      |

| 7       | VC1    | Connection pin for negative voltage of battery 1, for positive voltage of battery 2                                                                                                   |

| 8       | VDD    | Input pin for positive power supply, Connection pin for positive voltage of battery 1                                                                                                 |

<sup>\*1.</sup> No connection is electrically open. This pin can be connected to VDD or VSS.

**Remark** Refer to the package drawings for the external views.

Table 4 S-8253D Series

| Pin No. | Symbol | Description                                                                                                                                                                            |

|---------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | DOP    | Connection pin for discharge control FET gate (CMOS output)                                                                                                                            |

| 2       | COP    | Connection pin for charge control FET gate (Nch open-drain output)                                                                                                                     |

| 3       | VMP    | Pin for voltage detection between VDD and VMP (Detection pin for overcurrent)                                                                                                          |

| 4       | CTL    | Input pin for charge / discharge control signal, pin for shortening test time ( L : Normal operation, H : inhibit charge / discharge, M (V <sub>DD</sub> × 1 / 2) : shorten test time) |

| 5       | VSS    | Input pin for negative power supply, Connection pin for negative voltage of battery 3                                                                                                  |

| 6       | VC2    | Connection pin for negative voltage of battery 2, for positive voltage of battery 3                                                                                                    |

| 7       | VC1    | Connection pin for negative voltage of battery 1, for positive voltage of battery 2                                                                                                    |

| 8       | VDD    | Input pin for positive power supply, Connection pin for positive voltage of battery 1                                                                                                  |

**Remark** Refer to the package drawings for the external views.

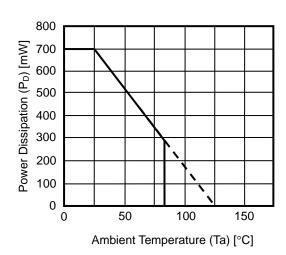

## ■ Absolute Maximum Ratings

Table 5

(Ta = 25°C unless otherwise specified)

| Item                              | Symbol              | Applicable Pins | Absolute Maximum Ratings        | Unit |

|-----------------------------------|---------------------|-----------------|---------------------------------|------|

| Input voltage between VDD and VSS | $V_{DS}$            | _               | $V_{SS}-0.3$ to $V_{SS}+26$     | V    |

| Input pin voltage                 | V <sub>IN</sub>     | VC1, VC2        | $V_{SS}-0.3$ to $V_{DD}+0.3$    | V    |

| VMP pin input voltage             | $V_{VMP}$           | VMP             | $V_{SS} - 0.3$ to $V_{SS} + 26$ | V    |

| DOP pin output voltage            | $V_{DOP}$           | DOP             | $V_{SS}-0.3$ to $V_{DD}+0.3$    | V    |

| COP pin output voltage            | V <sub>COP</sub>    | COP             | $V_{SS}-0.3$ to $V_{VMP}+0.3$   | V    |

| CTL input pin voltage             | V <sub>IN_CTL</sub> | CTL             | $V_{SS}-0.3$ to $V_{DD}+0.3$    | V    |

| Dower dissination                 | D                   |                 | 300 (When not mounted on board) | mW   |

| Power dissipation                 | P <sub>D</sub>      |                 | 700 <sup>*1</sup>               | mW   |

| Operating ambient temperature     | T <sub>opr</sub>    | _               | - 40 to + 85                    | °C   |

| Storage temperature               | T <sub>stg</sub>    | _               | - 40 to + 125                   | °C   |

<sup>\*1.</sup> When mounted on board

[Mounted board]

(1) Board size :  $114.3 \text{ mm} \times 76.2 \text{ mm} \times t1.6 \text{ mm}$ (2) Board name : JEDEC STANDARD51-7

Caution The absolute maximum ratings are rated values exceeding which the product could suffer physical damage. These values must therefore not be exceeded under any conditions.

Figure 4 Power Dissipation of Package (When Mounted on Board)

## ■ Electrical Characteristics

## 1. Characteristics Other Than Detection Delay Time

## Table 6 (1 / 2)

(Ta = 25°C unless otherwise specified)

|                                               |                   |                                                     |                                   |                             | (                 | 20 C un                     |         | Test           |                 |

|-----------------------------------------------|-------------------|-----------------------------------------------------|-----------------------------------|-----------------------------|-------------------|-----------------------------|---------|----------------|-----------------|

| Item                                          | Symbol            | Conditions                                          |                                   | Min.                        | Тур.              | Max.                        | Unit    | condi-<br>tion | Test<br>circuit |

| DETECTION VOLTAGE                             |                   |                                                     |                                   |                             |                   |                             |         |                |                 |

| Overcharge detection voltage n                | $V_{\text{CUn}}$  | 3.90 V to 4.40 V, Adjustal                          | ble                               | V <sub>CUn</sub><br>-0.025  | $V_{\text{CUn}}$  | V <sub>CUn</sub><br>+0.025  | V       | 1              | 1               |

| Oversharge release veltage n                  | V                 | 3.80 V to 4.40 V,                                   | V <sub>CL</sub> ≠ V <sub>CU</sub> | V <sub>CLn</sub><br>-0.05   | $V_{CLn}$         | V <sub>CLn</sub><br>+0.05   | V       | 1              | 1               |

| Overcharge release voltage n                  | V <sub>CLn</sub>  | Adjustable                                          | $V_{CL} = V_{CU}$                 | V <sub>CLn</sub><br>-0.025  | $V_{CLn}$         | V <sub>CLn</sub><br>+0.025  | V       | 1              | 1               |

| Overdischarge detection voltage n             | $V_{DLn}$         | 2.0 V to 3.0 V, Adjustable                          | 2.0 V to 3.0 V, Adjustable        |                             | $V_{DLn}$         | V <sub>DLn</sub><br>+0.080  | V       | 1              | 1               |

| Overdischarge release voltage n               | $V_{DUn}$         | 2.0 V to 3.40 V,<br>Adjustable                      | $V_{DL} \neq V_{DU}$              | V <sub>DUn</sub><br>-0.10   | $V_{DUn}$         | V <sub>DUn</sub><br>+0.10   | V       | 1              | 1               |

|                                               |                   |                                                     | $V_{DL} = V_{DU}$                 | V <sub>DUn</sub><br>-0.08   | $V_{DUn}$         | V <sub>DUn</sub><br>+0.08   | V       | 1              | 1               |

| Overcurrent detection voltage 1               | V <sub>IOV1</sub> | 0.05 V to 0.30 V, Adjustal Based on V <sub>DD</sub> | ble                               | V <sub>IOV1</sub><br>-0.025 | V <sub>IOV1</sub> | V <sub>IOV1</sub><br>+0.025 | V       | 2              | 1               |

| Overcurrent detection voltage 2               | V <sub>IOV2</sub> | Based on V <sub>DD</sub>                            |                                   | 0.40                        | 0.50              | 0.60                        | V       | 2              | 1               |

| Overcurrent detection voltage 3               | $V_{\text{IOV3}}$ | Based on V <sub>DD</sub>                            |                                   | 0.9                         | 1.2               | 1.5                         | V       | 2              | 1               |

| Temperature coefficient 1 *1                  | T <sub>COE1</sub> | $Ta = 0^{\circ}C \text{ to } 50^{\circ}C^{*3}$      |                                   | -1.0                        | 0                 | 1.0                         | mV / °C | _              |                 |

| Temperature coefficient 2 *2                  | T <sub>COE2</sub> | $Ta = 0^{\circ}C \text{ to } 50^{\circ}C^{*3}$      |                                   | -0.5                        | 0                 | 0.5                         | mV / °C |                | _               |

| 0 V BATTERY CHARGE FUNCTION                   |                   |                                                     |                                   |                             |                   |                             |         |                |                 |

| 0 V battery charge starting charger voltage   | $V_{0CHA}$        | 0 V battery charging; ava                           | ilable                            | _                           | 8.0               | 1.5                         | V       | 12             | 5               |

| 0 V battery charge inhibition battery voltage | V <sub>0INH</sub> | 0 V battery charging; unavailable                   |                                   | 0.4                         | 0.7               | 1.1                         | V       | 12             | 5               |

| INTERNAL RESISTANCE                           |                   |                                                     |                                   |                             |                   |                             |         |                |                 |

| Resistance between VMP and VDD                | $R_{\text{VMD}}$  | $V1 = V2 = V3^{4} = 3.5 \text{ V}, \text{ V}$       |                                   | 70                          | 95                | 120                         | kΩ      | 6              | 2               |

| Resistance between VMP and VSS                | $R_{\text{VMS}}$  | $V1 = V2 = V3^{4} = 1.8 \text{ V}, \text{ V}$       | $V_{\text{VMP}} = V_{\text{DD}}$  | 450                         | 900               | 1800                        | kΩ      | 6              | 2               |

## Table 6 (2 / 2)

(Ta = 25°C unless otherwise specified)

| Item                                  | Symbol            | Conditions                                             | Min.                    | Тур. | Max.                    | Unit | Test<br>condi-<br>tion | Test<br>circuit |

|---------------------------------------|-------------------|--------------------------------------------------------|-------------------------|------|-------------------------|------|------------------------|-----------------|

| INPUT VOLTAGE                         |                   |                                                        |                         |      | -                       |      |                        |                 |

| Operating voltage between VDD and VSS | $V_{DSOP}$        | Output voltage of DOP and COP fixed                    | 2                       | _    | 24                      | V    | _                      | _               |

| CTL input voltage "H"                 | V <sub>CTLH</sub> | _                                                      | V <sub>DD</sub><br>-0.5 | _    | _                       | V    | 7                      | 1               |

| CTL input voltage "L"                 | V <sub>CTLL</sub> | _                                                      | _                       | _    | V <sub>SS</sub><br>+0.5 | V    | 7                      | 1               |

| INPUT CURRENT                         |                   |                                                        |                         |      |                         |      |                        |                 |

| Current consumption on operation      | I <sub>OPE</sub>  | $V1 = V2 = V3^{*4} = 3.5 V$                            |                         | 14   | 28                      | μΑ   | 5                      | 2               |

| Current consumption at power down     | I <sub>PDN</sub>  | V1 = V2 = V3*4 = 1.5 V                                 | _                       | _    | 0.1                     | μΑ   | 5                      | 2               |

| VC1 pin current                       | I <sub>VC1</sub>  | $V1 = V2 = V3^{*4} = 3.5 V$                            | -0.3                    | 0    | 0.3                     | μΑ   | 9                      | 3               |

| VC2 pin current                       | I <sub>VC2</sub>  | $V1 = V2 = V3^{*4} = 3.5 V$                            | -0.3                    | 0    | 0.3                     | μΑ   | 9                      | 3               |

| CTL pin current "H"                   | I <sub>CTLH</sub> | $V1 = V2 = V3^{*4} = 3.5 \text{ V}, V_{CTL1} = V_{DD}$ | _                       | _    | 0.1                     | μΑ   | 8                      | 3               |

| CTL pin current "L"                   | I <sub>CTLL</sub> | $V1 = V2 = V3^{*4} = 3.5 \text{ V}, V_{CTL1} = V_{SS}$ | -0.4                    | -0.2 | _                       | μΑ   | 8                      | 3               |

| OUTPUT CURRENT                        |                   |                                                        |                         |      |                         |      |                        |                 |

| COP pin leakage current               | I <sub>COH</sub>  | V <sub>COP</sub> = 24 V                                | _                       | _    | 0.1                     | μΑ   | 10                     | 4               |

| COP pin sink current                  | I <sub>COL</sub>  | $V_{COP} = V_{SS} + 0.5 V$                             | 10                      | _    | _                       | μΑ   | 10                     | 4               |

| DOP pin source current                | I <sub>DOH</sub>  | $V_{DOP} = V_{DD} - 0.5 \text{ V}$                     | 10                      | _    | _                       | μА   | 11                     | 4               |

| DOP pin sink current                  | I <sub>DOL</sub>  | $V_{DOP} = V_{SS} + 0.5 V$                             | 10                      | _    | _                       | μА   | 11                     | 4               |

<sup>\*1.</sup> Voltage temperature coefficient 1 : Overcharge detection voltage

<sup>\*2.</sup> Voltage temperature coefficient 2 : Overcurrent detection voltage 1

<sup>\*3.</sup> Since products are not screened at high and low temperature, the specification for this temperature range is guaranteed by design, not tested in production.

<sup>\*4.</sup> The S-8253C Series does not have V3 because this IC is for 2-series cell battery protection.

## 2. Detection Delay Time

## (1) S-8253CAA, S-8253CAD, S-8253CAI, S-8253DAA, S-8253DAB, S-8253DAD, S-8253DAK

### Table 7

| ltem                               | Symbol            | Condition | Min. | Тур. | Max. | Unit | Test<br>Condition | Test<br>Circuit |  |

|------------------------------------|-------------------|-----------|------|------|------|------|-------------------|-----------------|--|

| DELAY TIME (Ta = 25°C)             |                   |           |      |      |      |      |                   |                 |  |

| Overcharge detection delay time    | t <sub>CU</sub>   | _         | 0.92 | 1.15 | 1.38 | S    | 3                 | 1               |  |

| Overdischarge detection delay time | t <sub>DL</sub>   | _         | 115  | 144  | 173  | ms   | 3                 | 1               |  |

| Overcurrent detection delay time 1 | t <sub>IOV1</sub> | _         | 7.2  | 9    | 10.8 | ms   | 4                 | 1               |  |

| Overcurrent detection delay time 2 | t <sub>IOV2</sub> | _         | 3.6  | 4.5  | 5.4  | ms   | 4                 | 1               |  |

| Overcurrent detection delay time 3 | t <sub>IOV3</sub> | _         | 220  | 300  | 380  | μS   | 4                 | 1               |  |

## (2) S-8253DAI

## Table 8

| ltem                               | Symbol            | Condition | Min. | Тур. | Max. | Unit | Test<br>Condition | Test<br>Circuit |  |

|------------------------------------|-------------------|-----------|------|------|------|------|-------------------|-----------------|--|

| DELAY TIME (Ta = 25°C)             |                   |           |      |      |      |      |                   |                 |  |

| Overcharge detection delay time    | t <sub>CU</sub>   | _         | 0.92 | 1.15 | 1.38 | s    | 3                 | 1               |  |

| Overdischarge detection delay time | t <sub>DL</sub>   | _         | 115  | 144  | 173  | ms   | 3                 | 1               |  |

| Overcurrent detection delay time 1 | t <sub>IOV1</sub> | _         | 3.6  | 4.5  | 5.4  | ms   | 4                 | 1               |  |

| Overcurrent detection delay time 2 | t <sub>IOV2</sub> |           | 0.89 | 1.1  | 1.4  | ms   | 4                 | 1               |  |

| Overcurrent detection delay time 3 | t <sub>IOV3</sub> |           | 220  | 300  | 380  | μS   | 4                 | 1               |  |

## (3) S-8253CAH

## Table 9

| ltem                               | Symbol            | Condition | Min. | Тур. | Max. | Unit | Test<br>Condition | Test<br>Circuit |  |

|------------------------------------|-------------------|-----------|------|------|------|------|-------------------|-----------------|--|

| DELAY TIME (Ta = 25°C)             |                   |           |      |      |      |      |                   |                 |  |

| Overcharge detection delay time    | t <sub>CU</sub>   | _         | 0.92 | 1.15 | 1.38 | S    | 3                 | 1               |  |

| Overdischarge detection delay time | t <sub>DL</sub>   | _         | 115  | 144  | 173  | ms   | 3                 | 1               |  |

| Overcurrent detection delay time 1 | t <sub>IOV1</sub> | _         | 14.5 | 18   | 22   | ms   | 4                 | 1               |  |

| Overcurrent detection delay time 2 | t <sub>IOV2</sub> |           | 3.6  | 4.5  | 5.4  | ms   | 4                 | 1               |  |

| Overcurrent detection delay time 3 | t <sub>IOV3</sub> | _         | 220  | 300  | 380  | μS   | 4                 | 1               |  |

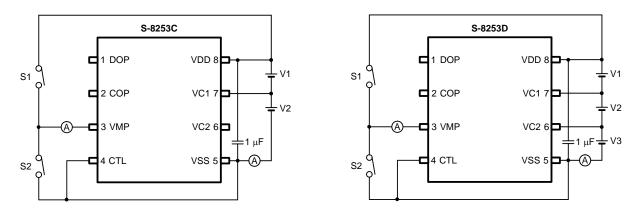

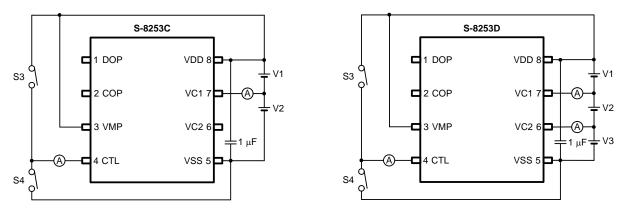

### ■ Test Circuits

## Overcharge Detection Voltage 1, Overcharge Release Voltage 1, Overdischarge Detection Voltage 1, Overdischarge Release Voltage 1 (Test Condition 1, Test Circuit 1)

Confirm that V1 = V2 = 3.5 V (S-8253C Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V4 = 0 V, V5 = 0 V, and the COP and DOP pins are "L" ( $V_{DD} \times 0.1 \text{ V}$  or lower) (this status is referred to as the initial status).

## 1. 1 Overcharge Detection Voltage 1 (V<sub>CU1</sub>), Overcharge Release Voltage 1 (V<sub>CL1</sub>)

Overcharge detection voltage 1 ( $V_{CU1}$ ) is the voltage of V1 when the voltage of the COP pin is "H" ( $V_{DD} \times 0.9 \text{ V}$  or more) after the V1 voltage has been gradually increased starting at the initial status. Overcharge release voltage 1 ( $V_{CL1}$ ) is the voltage of V1 when the voltage at the COP pin is low after the V1 voltage has been gradually decreased.

## 1. 2 Overdischarge Detection Voltage 1 (V<sub>DL1</sub>), Overdischarge Release Voltage 1 (V<sub>DU1</sub>)

Overdischarge detection voltage 1 ( $V_{DL1}$ ) is the voltage of V1 when the voltage of the DOP pin is high after the V1 voltage has been gradually decreased starting at the initial status. Overdischarge release voltage 1 ( $V_{DU1}$ ) is the voltage of V1 when the voltage at the DOP pin is low after the V1 voltage has been gradually increased.

By changing Vn (n = 2: S-8253C Series, n = 2, 3: S-8253D Series) the overcharge detection voltage ( $V_{CLn}$ ), overdischarge detection voltage ( $V_{DLn}$ ), and overdischarge release voltage ( $V_{DLn}$ ) can be measured in the same way as when n = 1.

## 2. Overcurrent Detection Voltage 1, Overcurrent Detection Voltage 2, Overcurrent Detection Voltage 3 (Test Condition 2, Test Circuit 1)

Confirm that V1 = V2 = 3.5 V (S-8253C Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V4 = 0 V, V5 = 0 V, and the COP pin and DOP pin are low (this status is referred to as the initial status).

## 2. 1 Overcurrent Detection Voltage 1 (V<sub>IOV1</sub>)

Overcurrent detection voltage 1 ( $V_{IOV1}$ ) is the voltage of V5 when the voltages of the COP pin and DOP pin are high after the V5 voltage has been gradually increased starting at the initial status.

### 2. 2 Overcurrent Detection Voltage 2 (V<sub>IOV2</sub>)

Overcurrent detection voltage 2 ( $V_{IOV2}$ ) is a voltage at V5 when; by increasing a voltage at V5 instantaneously (within 10  $\mu$ s) from the initial state, the voltages of the COP and DOP pin are set to "H", and its delay time is in the range of minimum to maximum value of overcurrent detection delay time 2 ( $t_{IOV2}$ ).

### 2. 3 Overcurrent Detection Voltage 3 (V<sub>IOV3</sub>)

Overcurrent detection voltage 3 ( $V_{IOV3}$ ) is a voltage at V5 when; by increasing a voltage at V5 instantaneously (within 10  $\mu$ s) from the initial state, the voltages of the COP and DOP pin are set to "H", and its delay time is in the range of minimum to maximum value of overcurrent detection delay time 3 ( $t_{IOV3}$ ).

## 3. Overcharge Detection Delay Time, Overdischarge Detection Delay Time (Test Condition 3, Test Circuit 1)

Confirm that V1 = V2 = 3.5 V (in S-8253C Series), V1 = V2 = V3 = 3.5 V (in S-8253D Series), V4 = 0 V, V5 = 0 V, and the COP pin and DOP pin are low (this status is referred to as the initial status).

## 3. 1 Overcharge Detection Delay Time (t<sub>CU</sub>)

The overcharge detection delay time ( $t_{CU}$ ) is the time it takes for the voltage of the COP pin to change from low to high after the voltage of V1 is instantaneously changed from overcharge detection voltage 1 ( $V_{CU1}$ ) – 0.2 V (within 10  $\mu$ s) starting at the initial status.

### 3. 2 Overdischarge Detection Delay Time (t<sub>DL</sub>)

The overdischarge detection delay time ( $t_{DL}$ ) is the time it takes for the voltage of the DOP pin to change from low to high after the voltage of V1 is instantaneously changed from overdischarge detection voltage 1 ( $V_{DL1}$ ) + 0.2 V to overdischarge detection voltage 1 ( $V_{DL1}$ ) - 0.2 V (within 10  $\mu$ s) starting at the initial status.

## 4. Overcurrent Detection Delay Time 1, Detection Delay Time 2, Detection Delay Time 3 (Test Condition 4, Test Circuit 1)

Confirm that V1 = V2 = 3.5 V (S-8253C Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V4 = 0 V, V5 = 0 V, and the COP pin and DOP pin are low (this status is referred to as the initial status).

#### 4. 1 Overcurrent Detection Delay Time 1 (t<sub>IOV1</sub>)

Overcurrent detection delay time 1 ( $t_{IOV1}$ ) is the time it takes for the voltage of the DOP pin to change from low to high after the voltage of V5 is instantaneously changed to 0.35 V (within 10  $\mu$ s) starting at the initial status.

## 4. 2 Overcurrent Detection Delay Time 2 (t<sub>IOV2</sub>)

Overcurrent detection delay time 2 ( $t_{IOV2}$ ) is the time it takes for the voltage of the DOP pin to change from low to high after the voltage of V5 is instantaneously changed to 0.7 V (within 10  $\mu$ s) starting at the initial status.

### 4. 3 Overcurrent Detection Delay Time 3 (t<sub>IOV3</sub>)

Overcurrent detection delay time 3 ( $t_{IOV3}$ ) is the time it takes for the voltage of the DOP pin to change from low to high after the voltage of V5 is instantaneously changed to 1.6 V (within 10  $\mu$ s) starting at the initial status.

## 5. Consumption on Operation, Power Consumption at Power-down (Test Condition 5, Test Circuit 2)

## 5. 1 Power Consumption on Operation (I<sub>OPE</sub>)

The power consumption during operation ( $I_{OPE}$ ) is the current of the VSS pin ( $I_{SS}$ ) when V1 = V2 = 3.5 V (S-8253C Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), S1 = ON, and S2 = OFF.

#### 5. 2 Power Consumption at Power-down (I<sub>PDN</sub>)

The power consumption at power-down ( $I_{PDN}$ ) is the current of the VSS pin ( $I_{SS}$ ) when V1 = V2 = 1.5 V (S-8253C Series), V1 = V2 = V3 = 1.5 V (S-8253D Series), S1 = OFF, and S2 = ON.

## 6. Resistance between VMP and VDD, Resistance between VMP and VSS (Test Condition 6, Test Circuit 2)

Confirm that V1 = V2 = 3.5 V (S-8253C Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V1 = V2 = V

## 6. 1 Resistance between VMP and VDD (R<sub>VMD</sub>)

The resistance between VMP and VDD ( $R_{VMD}$ ) is determined based on the current of the VMP pin ( $I_{VMD}$ ) after S1 and S2 are switched to OFF and ON, respectively, starting at the initial status.

```

S-8253C Series : R_{VMD} = (V1 + V2) / I_{VMD}

S-8253D Series : R_{VMD} = (V1 + V2 + V3) / I_{VMD}

```

## 6. 2 Resistance between VMP and VSS (R<sub>VMS</sub>)

The resistance between VMP and VSS ( $R_{VMS}$ ) is determined based on the current of the VMP pin ( $I_{VMS}$ ) after V1 = V2 = 1.8 V (S-8253C Series) or V1 = V2 = V3 = 1.8 V (S-8253D Series) are set starting at the initial status.

```

S-8253C Series : R_{VMS} = (V1 + V2) / I_{VMS} S-8253D Series : R_{VMS} = (V1 + V2 + V3) / I_{VMS}

```

## 7. CTL Pin Input Voltage "H"

(Test Condition 7, Test Circuit 1)

Confirm that V1 = V2 = 3.5 V (S-8253C Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V4 = 0 V, V5 = 0 V, and the COP pin and DOP pin are low (this status is referred to as the initial status).

## 7. 1 CTL Pin Input Voltage "H" (V<sub>CTLH</sub>)

The CTL pin input voltage "H" (V<sub>CTLH</sub>) is the voltage of V4 when the voltages of the COP pin and DOP pin are high after the voltage of V4 has been gradually increased starting at the initial status.

## 8. CTL Pin Input Voltage "L"

(Test condition 7, Test circuit 1)

Confirm that V1 = V2 = 3.5 V (S-8253C Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V4 = 0 V, V5 = 0.35 V, and the COP pin and DOP pin are high (this status is referred to as the initial status).

### 8. 1 CTL Pin Input Voltage "L" (V<sub>CTLL</sub>)

The CTL pin input voltage "L" (V<sub>CTLL</sub>) is the voltage of V4 when the voltages of the COP pin and DOP pin are low after the voltage of V4 has been gradually increased starting at the initial status.

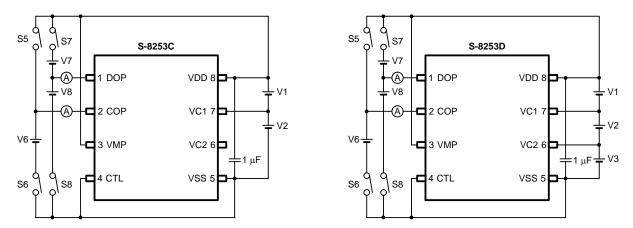

## 9. CTL Pin Current "H", CTL Pin Current "L" (Test Condition 8, Test Circuit 3)

## 9. 1 CTL Pin Current "H" (I<sub>CTLH</sub>), CTL Pin Current "L" (I<sub>CTLL</sub>)

The CTL pin current "H" ( $I_{CTLH}$ ) is the current that flows through the CTL pin when V1 = V2 = 3.5 V (S-8253C Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), and S3 = ON, S4 = OFF. The CTL pin current "L" ( $I_{CTLL}$ ) is the current that flows through the CTL pin when S3 = OFF and S4 = ON after that.

## 10. VC1 Pin Current, VC2 Pin Current (Test Condition 9, Test Circuit 3)

### 10. 1 VC1 Pin Current (I<sub>VC1</sub>), VC2 Pin Current (I<sub>VC2</sub>)

The VC1 pin current ( $I_{VC1}$ ) is the current that flows through the VC1 pin when V1 = V2 = 3.5 V (S-8253C Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), and S3 = OFF, S4 = ON. Similarly, the VC2 pin current ( $I_{VC2}$ ) is the current that flows through the VC2 pin under these conditions (S-8253D Series only).

## 11. COP Pin Leakage Current, COP Pin Sink Current (Test Condition 10, Test Circuit 4)

## 11. 1 COP Pin Leakage Current (I<sub>COH</sub>)

The COP pin leakage current ( $I_{COH}$ ) is the current that flows through the COP pin when V1 = V2 = 12 V (S-8253C Series), V1 = V2 = V3 = 8 V (S-8253D Series), S6 = S7 = S8 = OFF, and S5 = ON.

### 11. 2 COP Pin Sink Current (I<sub>COL</sub>)

The COP pin sink current ( $I_{COL}$ ) is the current that flows through the COP pin when V1 = V2 = 3.5 V (S-8253C Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V6 = 0.5 V, S5 = S7 = S8 = OFF, and S6 = ON.

## 12. DOP Pin Source Current, DOP Pin Sink Current (Test Condition 11, Test Circuit 4)

#### 12. 1 DOP Pin Source Current (IDOH)

The DOP pin source current ( $I_{DOH}$ ) is the current that flows through the DOP pin when V1 = V2 = 1.8 V (S-8253C Series), V1 = V2 = V3 = 1.8 V (S-8253D Series), V7 = 0.5 V, S5 = S6 = S8 = OFF, and S7 = ON.

## 12. 2 DOP Pin Sink Current (IDOL)

The DOP pin sink current ( $I_{DOL}$ ) is the current that flows through the DOP pin when V1 = V2 = 3.5 V (S-8253C Series), V1 = V2 = V3 = 3.5 V (S-8253D Series), V8 = 0.5 V, S5 = S6 = S7 = OFF, and S8 = ON.

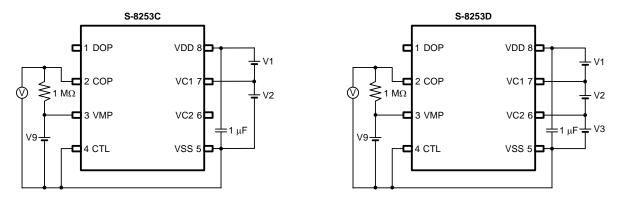

# 13. 0 V Battery Charge Starting Battery Charger Voltage (Product with 0 V Battery Charge Function), 0 V Battery Charge Inhibition Battery Voltage (Product with 0 V Battery Charge Inhibition Function) (Test Condition 12, Test Circuit 5)

## 13. 1 0 V Battery Charge Starting Battery Charger Voltage (V<sub>0CHA</sub>) (Product with 0 V Battery Charge Function)

The COP pin voltage should be lower than  $V_{0CHA}$  max. -1 V when V1 = V2 = 0 V (S-8253C Series), V1 = V2 = V3 = 0 V (S-8253D Series), and V9 =  $V_{VMP} = V_{0CHA}$  max.

## 13. 2 0 V Battery Charge Inhibition Battery Voltage (V<sub>OINH</sub>) (Product with 0 V Battery Charge Inhibition Function)

The COP pin voltage should be higher than  $V_{VMP}-1$  V when  $V1=V2=V_{0INH}$  min. (S-8253C Series),  $V1=V2=V3=V_{0INH}$  min. (S-8253D Series), and  $V9=V_{VMP}=24$  V.

Figure 5 Test Circuit 1

Figure 6 Test Circuit 2

Figure 7 Test Circuit 3

Figure 8 Test Circuit 4

Figure 9 Test Circuit 5

## Operation

**Remark** Refer to "■ Battery Protection IC Connection Example".

#### 1. Normal Status

When all of the battery voltages are in the range from  $V_{DLn}$  to  $V_{CUn}$  and the discharge current is lower than the specified value (the VMP pin voltage is higher than  $V_{DD} - V_{IOV1}$ ), the charging and discharging FETs are turned on. This condition is called the normal status, and in this condition charging and discharging can be carried out freely.

Caution When the battery is connected for the first time, discharging may not be enabled. In this case, short the VMP pin and VDD pin or connect the charger to restore the normal status.

### 2. Overcharge Status

When any one of the battery voltages becomes higher than  $V_{\text{CUn}}$  and the state continues for  $t_{\text{CU}}$  or longer, the COP pin becomes high impedance. Because the COP pin is pulled up to the EB+ pin voltage by an external resistor, the charging FET is turned off to stop charging. This is called the overcharge status. The overcharge status is released when one of the following two conditions holds.

- (1) All battery voltages become V<sub>CLn</sub> or lower.

- (2) All of the battery voltages are V<sub>CUn</sub> or lower, and the VMP pin voltage is V<sub>DD</sub> V<sub>IOV1</sub> or lower (since the discharge current flows through the body diode of the charging FET immediately after discharging is started when the charger is removed and a load is connected, the VMP pin voltage momentarily decreases by approximately 0.6 V from the VDD pin voltage. The IC detects this voltage and releases the overcharging status).

## 3. Overdischarge Status

When any one of the battery voltages becomes lower than  $V_{DLn}$  and the state continues for  $t_{DL}$  or longer, the DOP pin voltage becomes  $V_{DD}$  level, and the discharging FET is turned off to stop discharging. This is called the overdischarging status. After discharging is stopped due to the overdischarge status, the S-8253C/D Series enters the power-down status.

## 4. Power-down Status

When discharging has stopped due to the overdischarge status, the VMP pin is pulled down to the  $V_{SS}$  level by the  $R_{VMS}$  resistor. When the VMP pin voltage is lower than Typ. 0.8 V, the S-8253C/D Series enters the power-down status. In the power-down status, almost all the circuits of the S-8253C/D Series stop and the current consumption is  $I_{PDN}$  or lower. The conditions of each output pin are as follows.

(1) COP pin : High-Z(2) DOP pin : V<sub>DD</sub>

The power-down status is released when the following condition holds.

(1) The VMP pin voltage is Typ. 0.8 V or higher.

The overdischarging status is released when the following two conditions hold.

- (1) All battery voltage is released at  $V_{DUn}$  or higher when the VMP pin voltage is Typ. 0.8 V or higher and the VMP pin voltage is lower than  $V_{DD}$ .

- (2) All battery voltage is released at  $V_{DLn}$  or higher when the VMP pin voltage is Typ. 0.8 V or higher and the VMP pin voltage is  $V_{DD}$  or higher (when a charger is connected and VMP pin voltage is  $V_{DD}$  or higher, overdischarge hysteresis is released and electric discharge control FET is turned on at  $V_{DLn}$ ).

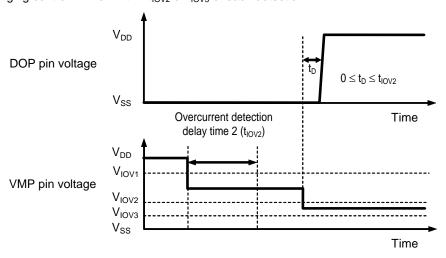

#### 5. Overcurrent Status

The S-8253C/D Series has three overcurrent detection levels ( $V_{IOV1}$ ,  $V_{IOV2}$ , and  $V_{IOV3}$ ) and three overcurrent detection delay times ( $t_{IOV1}$ ,  $t_{IOV2}$ , and  $t_{IOV3}$ ) corresponding to each overcurrent detection level. When the discharging current becomes higher than the specified value (the difference of the voltages of the VMP pin and VDD pin is greater than  $V_{IOV1}$ ) and the state continues for  $t_{IOV1}$  or longer, the S-8253C/D Series enters the overcurrent status, in which the DOP pin voltage becomes  $V_{DD}$  level to turn off the discharging FET to stop discharging, the COP pin becomes high impedance and is pulled up to the EB+ pin voltage to turn off the charging FET to stop charging, and the VMP pin is pulled up to the  $V_{DD}$  voltage by the internal resistor ( $R_{VMD}$ ). Operation of overcurrent detection levels 2, 3 ( $V_{IOV2}$ ,  $V_{IOV3}$ ) and overcurrent detection delay times 2, 3 ( $V_{IOV2}$ ,  $V_{IOV3}$ ) are the same as for  $V_{IOV1}$  and  $V_{IOV1}$ .

The overcurrent status is released when the following condition holds.

(1) The VMP pin voltage is V<sub>DD</sub> – V<sub>IOV1</sub> or higher because a charger is connected or the load is released.

Caution The impedance that enables automatic restoration varies depending on the battery voltage and set value of overcurrent detection voltage 1.

### 6. 0 V Battery Charge Function

Regarding the charging of a self-discharged battery (0 V battery), the S-8253C/D Series has two functions from which one should be selected.

- (1) 0 V battery charging is allowed (0 V battery charging is available.) When the charger voltage is higher than  $V_{0CHA}$ , the 0 V battery can be charged.

- (2) 0 V battery charging is inhibited (0 V battery charging is unavailable.)

When one of the battery voltages is lower than V<sub>0INH</sub>, the 0 V battery cannot be charged.

Caution When the VDD pin voltage is lower than the minimum value of  $V_{DSOP}$ , the operation of the S-8253C/D Series is not guaranteed.

## 7. Delay Circuit

The following detection delay times are determined by dividing a clock of approximately 3.57 kHz by the counter.

(Example) Oscillator clock cycle (T<sub>CLK</sub>): 280 μs

Overcharge detection delay time ( $t_{CU}$ ): 1.15 s Overdischarge detection delay time ( $t_{DL}$ ): 144 ms Overcurrent detection delay time 1 ( $t_{IOV1}$ ): 9 ms Overcurrent detection delay time 2 ( $t_{IOV2}$ ): 4.5 ms

#### Remark

The overcurrent detection delay time 2 ( $t_{IOV2}$ ) and overcurrent detection delay time 3 ( $t_{IOV3}$ ) start when the overcurrent detection voltage 1 ( $V_{IOV1}$ ) is detected. As soon as the overcurrent detection voltage 2 ( $V_{IOV2}$ ) or overcurrent detection voltage 3 ( $V_{IOV3}$ ) is detected over the detection delay time for overcurrent 2 ( $t_{IOV2}$ ) or overcurrent 3 ( $t_{IOV3}$ ) after the detection of overcurrent 1 ( $V_{IOV1}$ ), the S-8253C/D Series turns the discharging control FET off within  $t_{IOV2}$  or  $t_{IOV3}$  of each detection.

Figure 10

#### 8. CTL Pin

The S-8253C/D Series has a control pin for charge / discharge control and reducing test time. The levels, "L", "H", and "M", of the voltage input to the CTL pin determine the status of the S-8253C/D Series: normal operation, charge / discharge inhibition, or test time reduction. The CTL pin takes precedence over the battery protection circuit. During normal use, short the CTL pin and VSS pin.

Table 10 Conditions Set by CTL Pin

| CTL Pin Potential                                                  | Status of IC                        | COP Pin           | DOP Pin           |

|--------------------------------------------------------------------|-------------------------------------|-------------------|-------------------|

| Open                                                               | Charge / discharge inhibited status | High-Z            | $V_{DD}$          |

| High $(V_{CTL} \ge V_{CTLH})$                                      | Charge / discharge inhibited status | High-Z            | $V_{DD}$          |

| Middle (V <sub>CTLL</sub> < V <sub>CTL</sub> < V <sub>CTLH</sub> ) | Status to shorten delay time *1     | (*2)              | ( <sup>*2</sup> ) |

| Low $(V_{CTLL} \ge V_{CTL})$                                       | Normal status                       | ( <sup>*2</sup> ) | ( <sup>*2</sup> ) |

<sup>\*1.</sup> In this status that delay time is shortened, only the overcharge detection delay time is shortened in 1/60 to 1/30.

## Caution 1. If the potential of the CTL pin is middle, overcurrent detection voltage 1 (V<sub>IOV1</sub>) does not operate.

- 2. If you use the middle potential of the CTL pin, contact SII marketing department.

- Please note unexpected behavior might occur when electrical potential difference between the CTL pin ("L" level) and VSS is generated through the external filter (R<sub>VSS</sub> and C<sub>VSS</sub>) as a result of input voltage fluctuations.

<sup>\*2.</sup> The pin status is controlled by the voltage detection circuit.

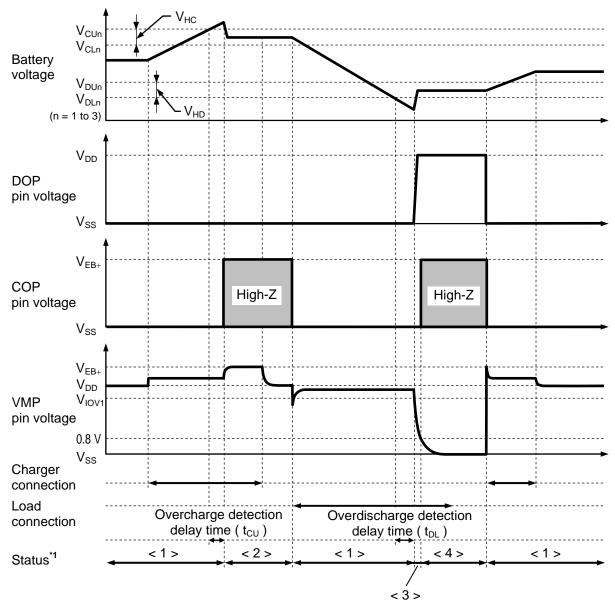

## Timing Chart

## 1. Overcharge Detection and Overdischarge Detection

\*1. < 1 > : Normal status

< 2 > : Overcharge status

< 3 > : Overdischarge status

< 4 > : Power-down status

**Remark** The charger is assumed to charge with a constant current.  $V_{EB+}$  indicates the open voltage of the charger.

Figure 11

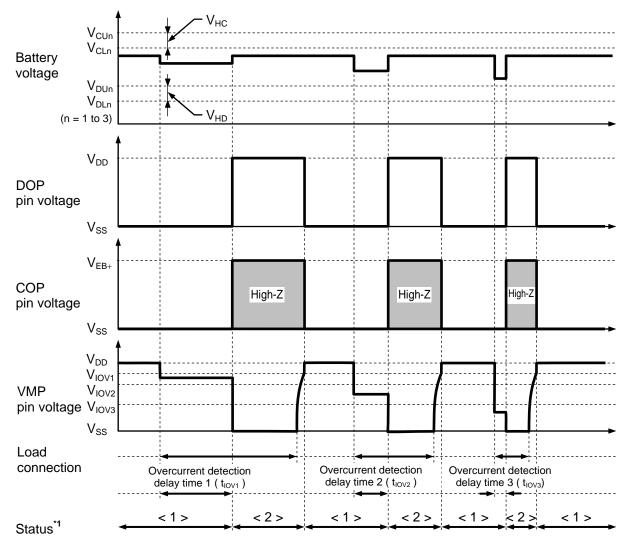

## 2. Overcurrent Detection

\*1. < 1 > : Normal status

< 2 > : Overcurrent status

**Remark** The charger is assumed to charge with a constant current. V<sub>EB+</sub> indicates the open voltage of the charger.

Figure 12

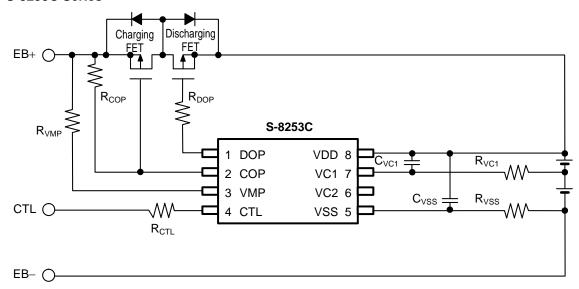

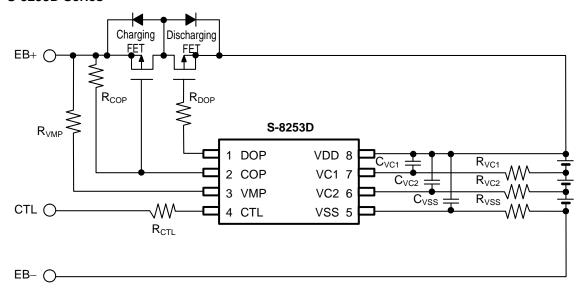

## Battery Protection IC Connection Example

## 1. S-8253C Series

Figure 13

## 2. S-8253D Series

Figure 14

| No. | Symbol           | Тур. | Range                     | Unit      |

|-----|------------------|------|---------------------------|-----------|

| 1   | R <sub>VC1</sub> | 1    | 0.51 to 1*1               | kΩ        |

| 2   | R <sub>VC2</sub> | 1    | 0.51 to 1 <sup>*1</sup>   | kΩ        |

| 3   | R <sub>DOP</sub> | 5.1  | 2 to 10                   | kΩ        |

| 4   | R <sub>COP</sub> | 1    | 0.1 to 1                  | $M\Omega$ |

| 5   | R <sub>VMP</sub> | 5.1  | 1 to 10                   | kΩ        |

| 6   | R <sub>CTL</sub> | 1    | 1 to 100                  | kΩ        |

| 7   | R <sub>VSS</sub> | 51   | 5.1 to 51 <sup>*1</sup>   | Ω         |

| 8   | C <sub>VC1</sub> | 0.1  | 0.1 to 0.47 <sup>*1</sup> | μF        |

| 9   | C <sub>VC2</sub> | 0.1  | 0.1 to 0.47 <sup>*1</sup> | μF        |

| 10  | C <sub>VSS</sub> | 2.2  | 1 to 10 <sup>*1</sup>     | μF        |

**Table 11 Constants for External Components**

## Caution 1. The above constants may be changed without notice.

It has not been confirmed whether the operation is normal or not in circuits other than the above example of connection. In addition, the example of connection shown above and the constant do not guarantee proper operation. Perform thorough evaluation using the actual application to set the constant.

<sup>\*1.</sup> Please set up a filter constant to be  $R_{VSS} \times C_{VSS} \ge 51 \ \mu F \bullet \Omega$  and to be  $R_{VC1} \times C_{VC1} = R_{VC2} \times C_{VC2} = R_{VSS} \times C_{VSS}$ .

## BATTERY PROTECTION IC FOR 2-SERIES OR 3-SERIES-CELL PACK S-8253C/D Series

Rev.2.0\_00

## Precautions

- The application conditions for the input voltage, output voltage, and load current should not exceed the package power dissipation.

- Batteries can be connected in any order, however, there may be cases when discharging cannot be performed when a battery is connected. In this case, short the VMP pin and VDD pin or connect the battery charger to return to the normal mode.

- Do not apply an electrostatic discharge to this IC that exceeds the performance ratings of the built-in electrostatic protection circuit.

- SII claims no responsibility for any disputes arising out of or in connection with any infringement by products including this IC of patents owned by a third party.

## Characteristics (Typical Data)

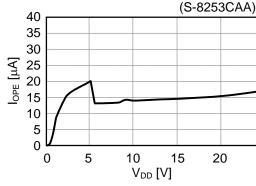

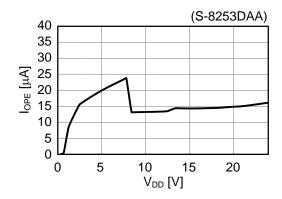

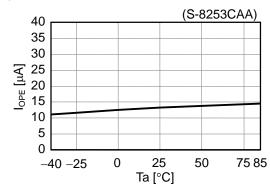

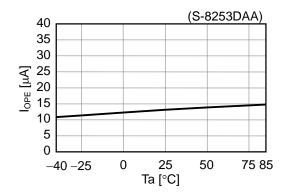

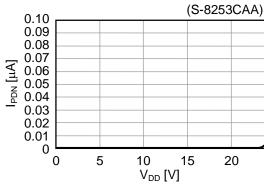

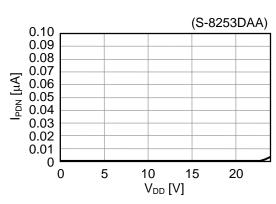

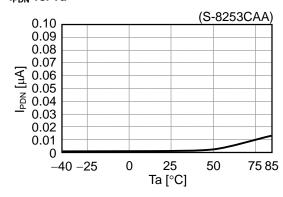

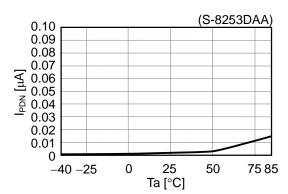

## 1. Current Consumption

## 1. 1 $I_{OPE}$ vs. $V_{DD}$

### 1. 2 I<sub>OPE</sub> vs. Ta

## 1. 3 $I_{PDN}$ vs. $V_{DD}$

## 1.4 I<sub>PDN</sub> vs. Ta

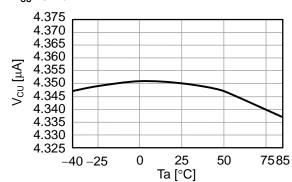

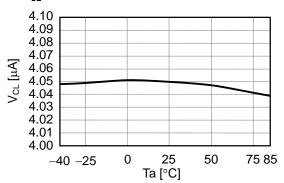

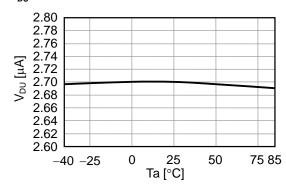

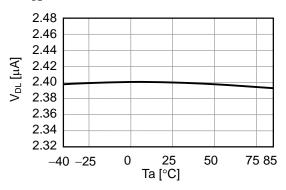

2. Overcharge Detection / Release Voltage, Overdischarge Detection / Release Voltage, Overcurrent Detection Voltage, and Delay Times (S-8253CAA, S-8253DAA)

2. 1 V<sub>CU</sub> vs. Ta

2. 2 V<sub>CL</sub> vs. Ta

2. 3 V<sub>DU</sub> vs. Ta

2. 4  $V_{DL}$  vs. Ta

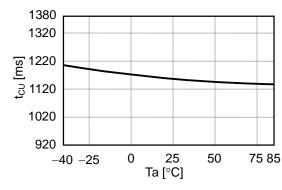

2. 5  $t_{CU}$  vs. Ta

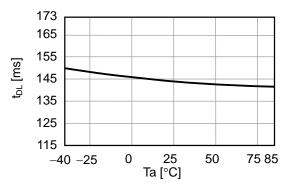

2. 6 t<sub>DL</sub> vs. Ta

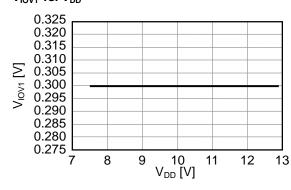

2. 7  $V_{IOV1}$  vs.  $V_{DD}$

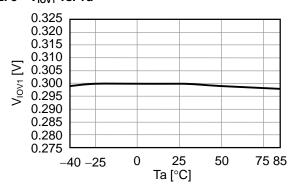

2. 8 V<sub>IOV1</sub> vs. Ta

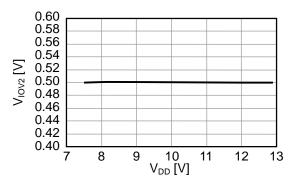

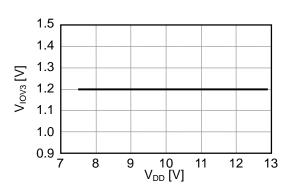

2. 9  $V_{IOV2}$  vs.  $V_{DD}$

2. 10 V<sub>IOV2</sub> vs. Ta

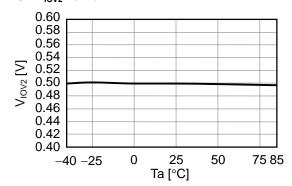

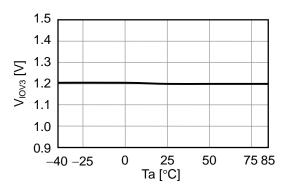

2. 11  $V_{IOV3}$  vs.  $V_{DD}$

2. 12 V<sub>IOV3</sub> vs. Ta

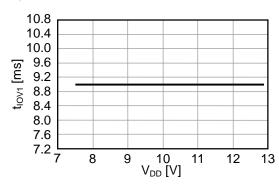

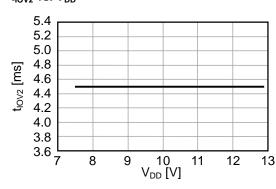

2. 13  $t_{IOV1}$  vs.  $V_{DD}$

$\textbf{2. 14} \quad t_{IOV1} \text{ vs. Ta} \\$

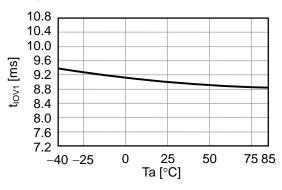

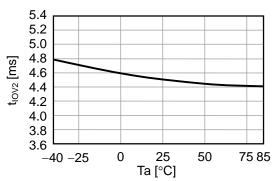

2. 15 t<sub>IOV2</sub> vs. V<sub>DD</sub>

2. 16 t<sub>IOV2</sub> vs. Ta

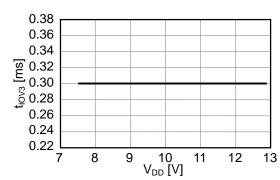

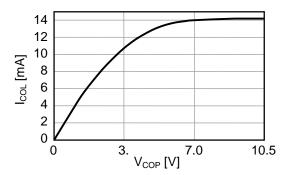

2. 17  $t_{IOV3}$  vs.  $V_{DD}$

2. 18 t<sub>IOV3</sub> vs. Ta

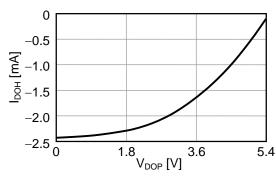

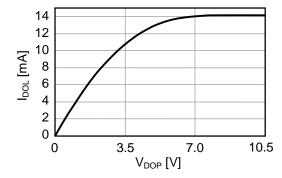

## 3. COP / DOP Pin (S-8253CAA, S-8253DAA)

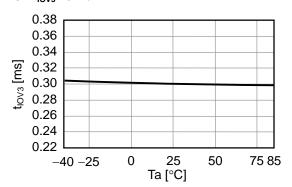

3. 1  $I_{COH}$  vs.  $V_{COP}$

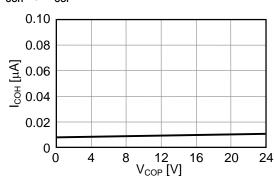

3. 2 I<sub>COL</sub> vs. V<sub>COP</sub>

3. 3 I<sub>DOH</sub> vs. V<sub>DOP</sub>

3. 4  $I_{DOL}$  vs.  $V_{DOP}$

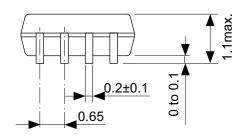

## No. FT008-A-P-SD-1.1

| TSSOP8-E-PKG Dimensions |  |  |  |  |

|-------------------------|--|--|--|--|

| FT008-A-P-SD-1.1        |  |  |  |  |

|                         |  |  |  |  |

| mm                      |  |  |  |  |

|                         |  |  |  |  |

|                         |  |  |  |  |

|                         |  |  |  |  |

| Seiko Instruments Inc.  |  |  |  |  |

|                         |  |  |  |  |

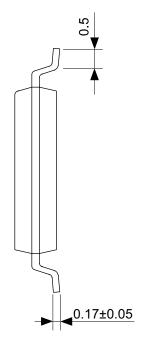

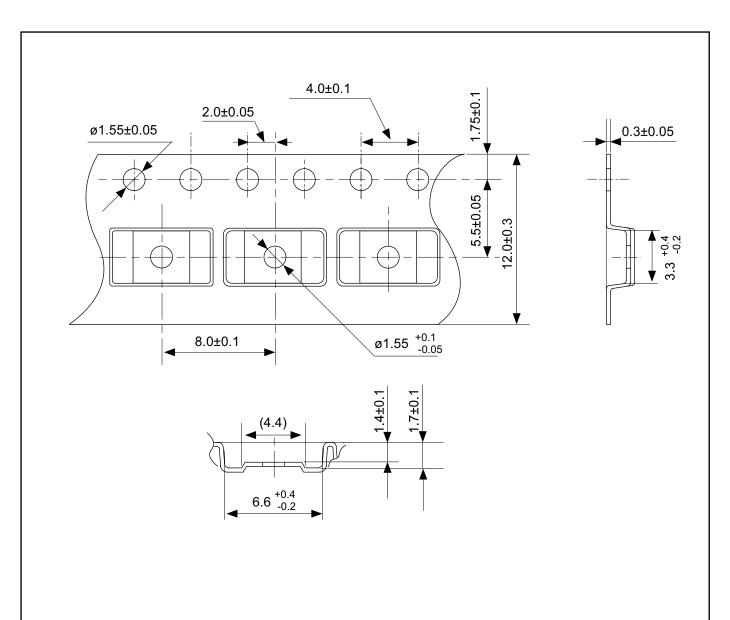

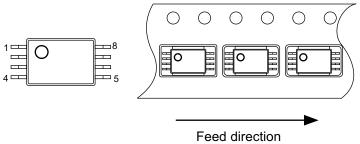

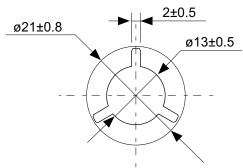

## No. FT008-E-C-SD-1.0

| TITLE                   | TSSOP8-E-Carrier Tape |  |  |  |  |

|-------------------------|-----------------------|--|--|--|--|

| No.                     | FT008-E-C-SD-1.0      |  |  |  |  |

| SCALE                   |                       |  |  |  |  |

| UNIT                    | mm                    |  |  |  |  |

|                         |                       |  |  |  |  |

|                         |                       |  |  |  |  |

|                         |                       |  |  |  |  |

| Cailea Inatouraanta Ina |                       |  |  |  |  |

| Seiko Instruments Inc.  |                       |  |  |  |  |

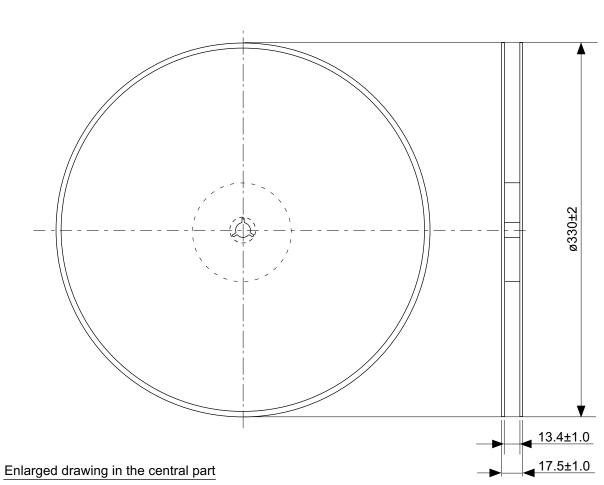

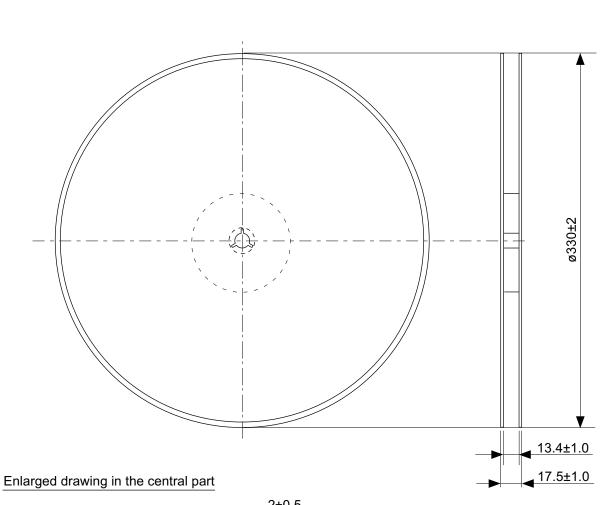

## No. FT008-E-R-SD-1.0

| TITLE                  | TSSOP8-E-Reel    |      |       |  |  |

|------------------------|------------------|------|-------|--|--|

| No.                    | FT008-E-R-SD-1.0 |      |       |  |  |

| SCALE                  |                  | QTY. | 3,000 |  |  |

| UNIT                   | mm               | •    | -     |  |  |

|                        |                  |      |       |  |  |

|                        |                  |      |       |  |  |

|                        |                  |      |       |  |  |

| Seiko Instruments Inc. |                  |      |       |  |  |

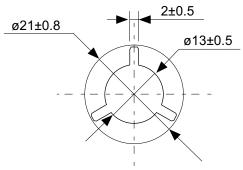

## No. FT008-E-R-S1-1.0

| TITLE                  | TSSOP8-E-Reel    |      |       |  |  |

|------------------------|------------------|------|-------|--|--|

| No.                    | FT008-E-R-S1-1.0 |      |       |  |  |

| SCALE                  |                  | QTY. | 4,000 |  |  |

| UNIT                   | mm               |      |       |  |  |

|                        |                  |      |       |  |  |

|                        |                  |      |       |  |  |

|                        |                  |      |       |  |  |

| Seiko Instruments Inc. |                  |      |       |  |  |

# SII Seiko Instruments Inc. www.sii-ic.com

- The information described herein is subject to change without notice.

- Seiko Instruments Inc. is not responsible for any problems caused by circuits or diagrams described herein

whose related industrial properties, patents, or other rights belong to third parties. The application circuit

examples explain typical applications of the products, and do not guarantee the success of any specific

mass-production design.

- When the products described herein are regulated products subject to the Wassenaar Arrangement or other agreements, they may not be exported without authorization from the appropriate governmental authority.

- Use of the information described herein for other purposes and/or reproduction or copying without the express permission of Seiko Instruments Inc. is strictly prohibited.

- The products described herein cannot be used as part of any device or equipment affecting the human body, such as exercise equipment, medical equipment, security systems, gas equipment, or any apparatus installed in airplanes and other vehicles, without prior written permission of Seiko Instruments Inc.

- Although Seiko Instruments Inc. exerts the greatest possible effort to ensure high quality and reliability, the

failure or malfunction of semiconductor products may occur. The user of these products should therefore

give thorough consideration to safety design, including redundancy, fire-prevention measures, and

malfunction prevention, to prevent any accidents, fires, or community damage that may ensue.