512-Mbit GDDR3 Graphics RAM

**Memory Products**

#### **Edition 2005-08**

Published by Infineon Technologies AG, St.-Martin-Strasse 53, 81669 München, Germany

© Infineon Technologies AG 2005.

All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as a guarantee of characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Under no circumstances may the Infineon Technologies product as referred to in this data sheet be used in

- 1. Any applications that are intended for military usage (including but not limited to weaponry), or

- 2. Any applications, devices or systems which are safety critical or serve the purpose of supporting, maintaining, sustaining or protecting human life (such applications, devices and systems collectively referred to as "Critical Systems"), if

- a) A failure of the Infineon Technologies product can reasonable be expected to directly or indirectly -

- (i) Have a detrimental effect on such Critical Systems in terms of reliability, effectiveness or safety; or

- (ii) Cause the failure of such Critical Systems; or

- b) A failure or malfunction of such Critical Systems can reasonably be expected to directly or indirectly -

- (i) Endanger the health or the life of the user of such Critical Systems or any other person; or

- (ii) Otherwise cause material damages (including but not limited to death, bodily injury or significant damages to property, whether tangible or intangible).

| Revision   | History: Rev. 1.73                           | 2005-08 |

|------------|----------------------------------------------|---------|

| Previous F | Revision: Rev. 1.60                          |         |

| Page       | Subjects (major changes since last revision) |         |

| 75         | figure 61: changed DQ setting                |         |

|            |                                              |         |

|            |                                              |         |

|            |                                              |         |

### **We Listen to Your Comments**

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

## **Table of Contents**

|                 | Overview                                                       |    |

|-----------------|----------------------------------------------------------------|----|

| l.1             | Features                                                       |    |

| 1.2             | Description                                                    | 10 |

| 2               | Pin Configuration                                              | 11 |

| 2.1             | Ball Definition and Description                                | 12 |

| 2.2             | Mirror Function                                                |    |

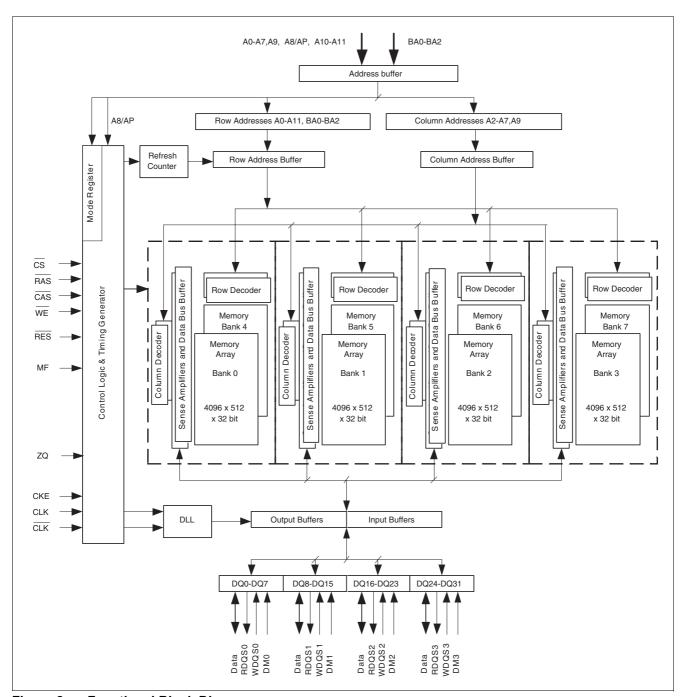

| 2.3             | Functional Block Diagram                                       |    |

| 2.4             | Commands                                                       |    |

| 2.4.1           | Command Table                                                  |    |

| 2.4.2           | Description of Commands                                        | 17 |

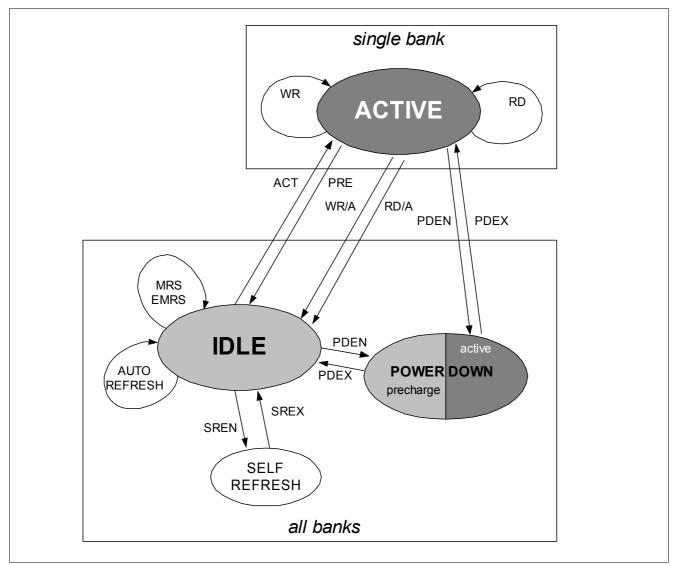

| 2.5             | State Diagram and Truth Tables                                 | 20 |

| 2.5.1           | State Diagram for One Activated Bank                           |    |

| 2.5.2           | Function Truth Table for more than one Activated Bank          | 21 |

| 2.6             | Function Truth Table for CKE                                   | 22 |

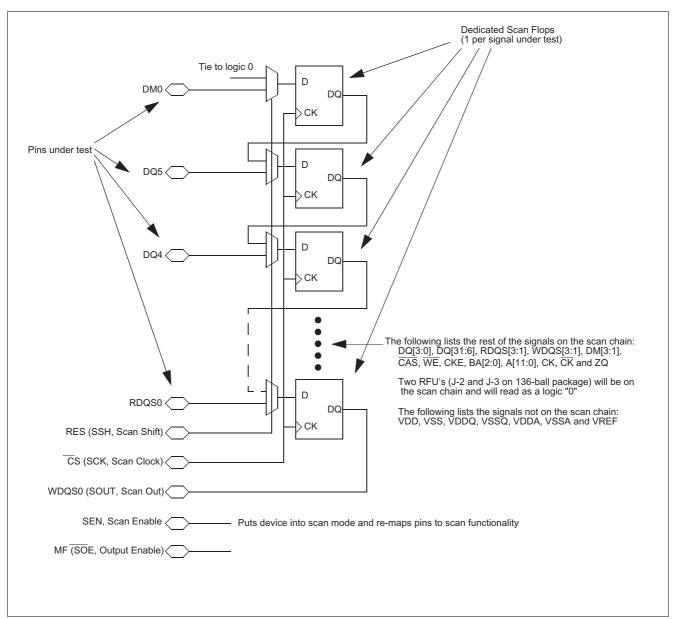

| 2               | Boundary Scan                                                  | 23 |

| <b>,</b><br>3.1 | General Description                                            |    |

| 3.2             | Disabling the scan feature                                     |    |

| 3.3             | Scan Initilization                                             |    |

| 3.3.1           | Scan initilization for Stand-Alone Mode                        |    |

| 3.3.2           | Scan initilization in regular SGRAM operation                  |    |

| 3.3.3           | Scan Exit Sequence                                             |    |

| -               | •                                                              |    |

| <b>.</b>        | Functional Description                                         |    |

| 1.1             | Initialization                                                 |    |

| 1.2             | Programmable impedance output drivers and active terminations  |    |

| 1.2.1           | GDDR3 IO Driver and Termination                                |    |

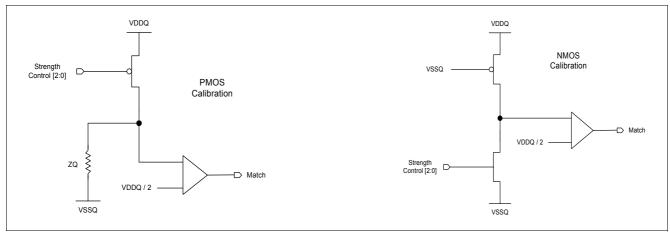

| 1.2.2           | Self Calibration for Driver and Termination                    |    |

| 1.2.3<br>1.2.4  | Dynamic Switching of DQ terminations                           |    |

| +.∠.4<br>1.3    | Output impedance and Termination DC Electrical Characteristics |    |

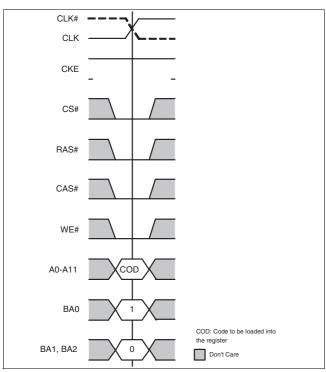

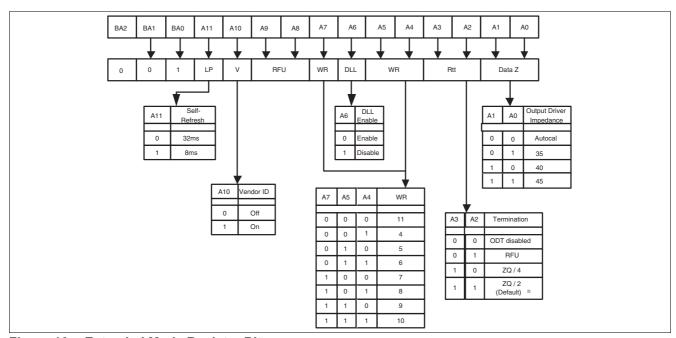

| +.3<br>1.3.1    | Extended Mode Register Set Command (EMRS)                      |    |

| 1.3.1           | WR                                                             |    |

| +.3.2<br>1.3.3  | Termination Rtt                                                |    |

| 1.3.4           | Output Driver Impedance                                        |    |

| 1.3.5           | Low Power                                                      |    |

| 1.3.6           | Vendor Code and Revision Identification                        |    |

| 1.4             | Mode Register Set Command (MRS)                                |    |

| 1.4.1           | Burst length                                                   |    |

| 1.4.2           | Burst type                                                     |    |

| 1.4.3           | CAS Latency                                                    |    |

| 1.4.4           | Write Latency                                                  |    |

| 1.4.5           | Test mode                                                      |    |

| 1.4.6           | DLL Reset                                                      |    |

| 1.5             | Bank / Row Activation (ACT)                                    |    |

| 1.6             | Writes (WR)                                                    |    |

| 1.6.1           | Write - Basic Information                                      |    |

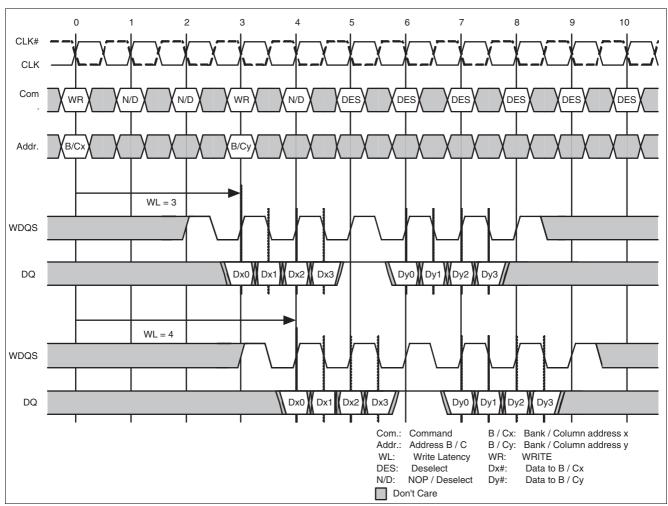

| 1.6.2           | Write - Basic Sequence                                         |    |

| 1.6.3           | Write - Consecutive Bursts                                     |    |

| 1.6.3.1         | Gapless Bursts                                                 |    |

| 1.6.3.2         | Bursts with Gaps                                               |    |

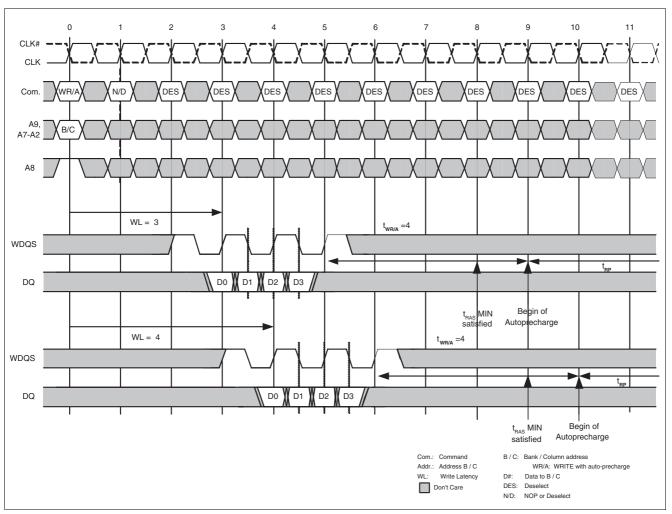

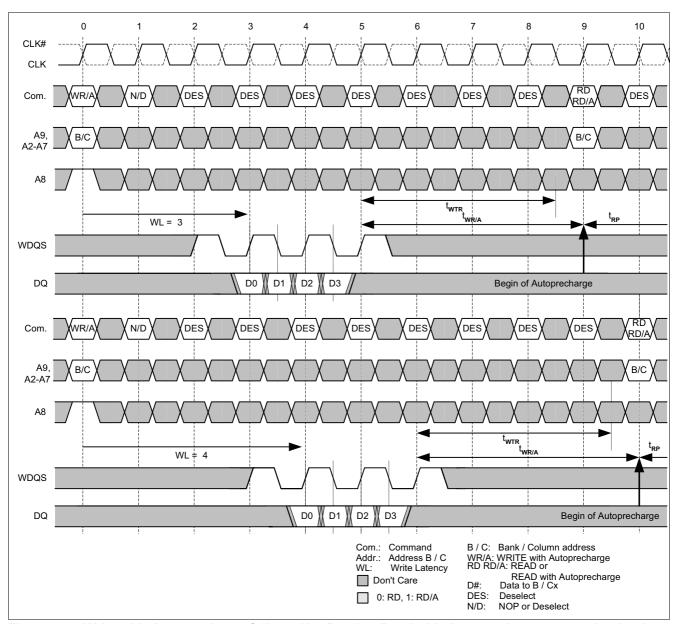

| 1.6.4           | Write with Autoprecharge                                       |    |

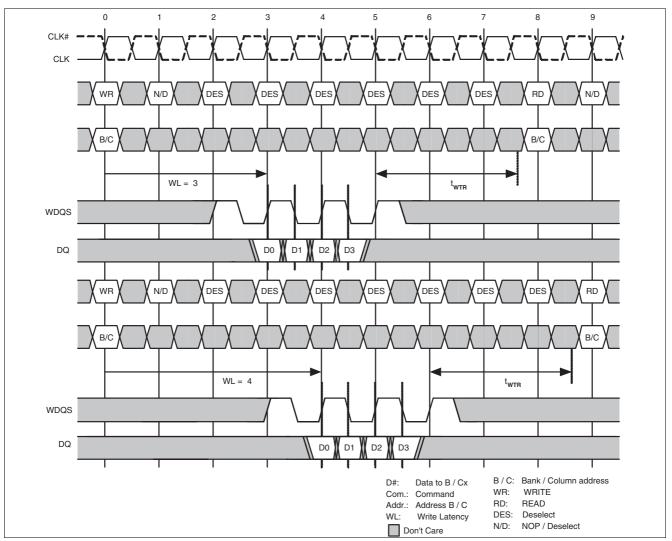

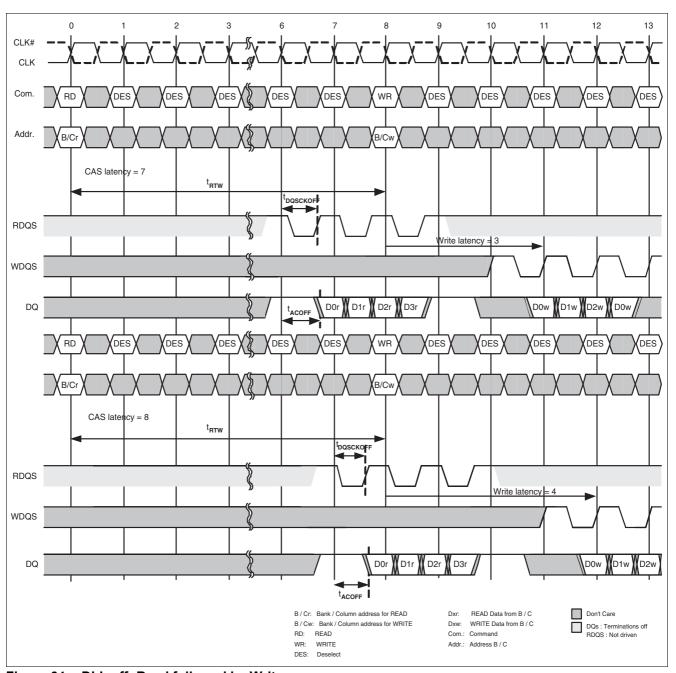

| 1.6.5           | Write followed by Read                                         | 51 |

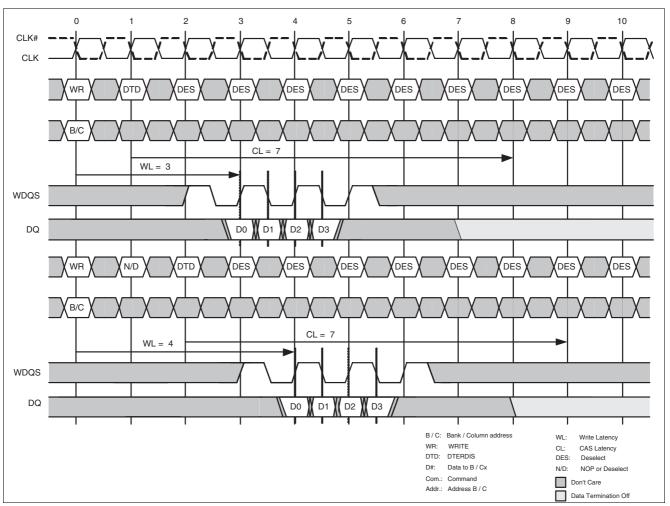

| 1.6.6           | Write followed by DTERDIS                                      |    |

| 4.6.7         | Write with Autoprecharge followed by Read / Read with Autoprecharge |    |

|---------------|---------------------------------------------------------------------|----|

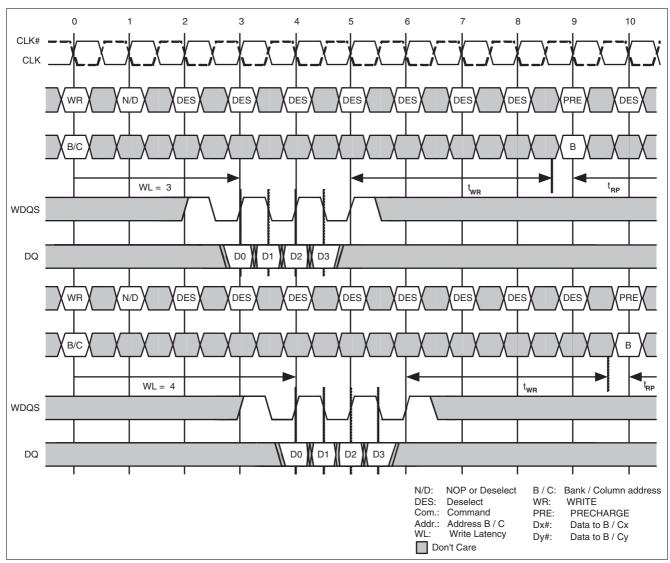

| 4.6.8         | Write followed by Precharge on same bank                            |    |

| 4.7           | Reads (RD)                                                          |    |

| 4.7.1         | Read - Basic Information                                            |    |

| 4.7.2         | Read - Basic Sequence                                               |    |

| 4.7.3         | Consecutive Read Bursts                                             |    |

| 4.7.3.1       | Gapless Bursts                                                      |    |

| 4.7.4         | Bursts with Gaps                                                    |    |

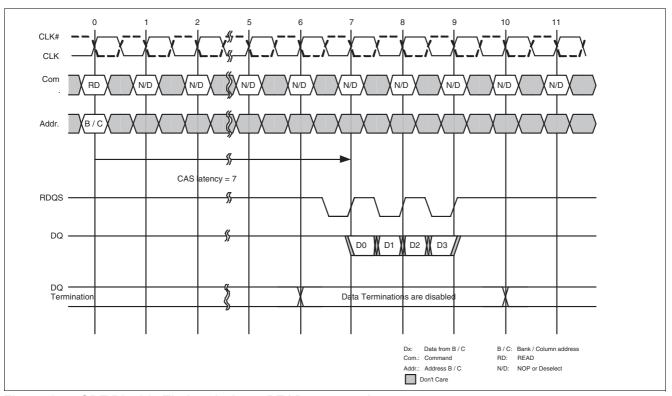

| 4.7.5         | Read followed by DTERDIS                                            |    |

| 4.7.6         | Read with Autoprecharge                                             |    |

| 4.7.7         | Read followed by Write                                              |    |

| 4.7.8         | Read followed by Precharge on the same Bank                         |    |

| 4.8           | Data Termination Disable (DTERDIS)                                  |    |

| 4.8.1         | DTERDIS followed by DTERDIS                                         |    |

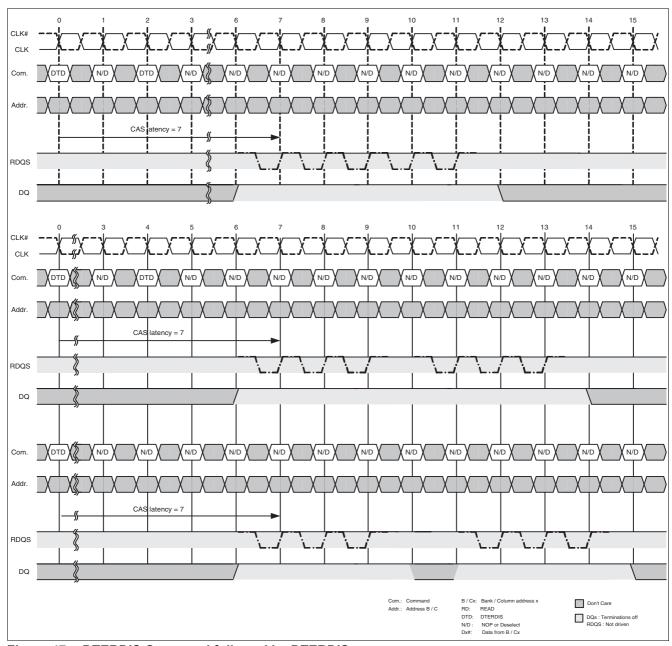

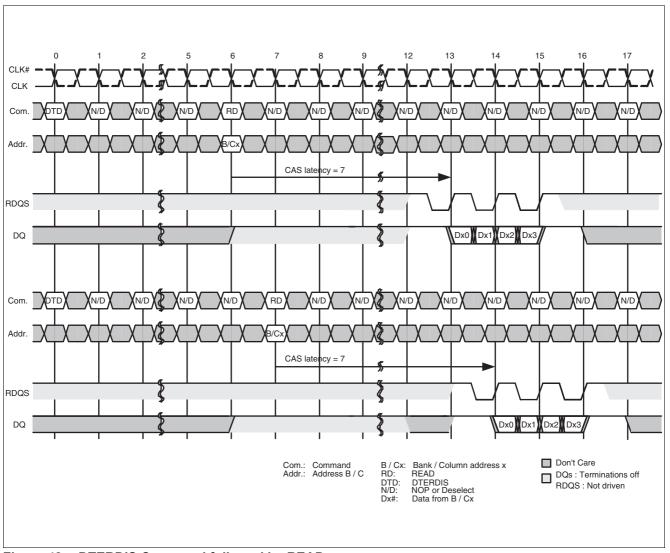

| 4.8.2         | DTERDIS followed by READ                                            |    |

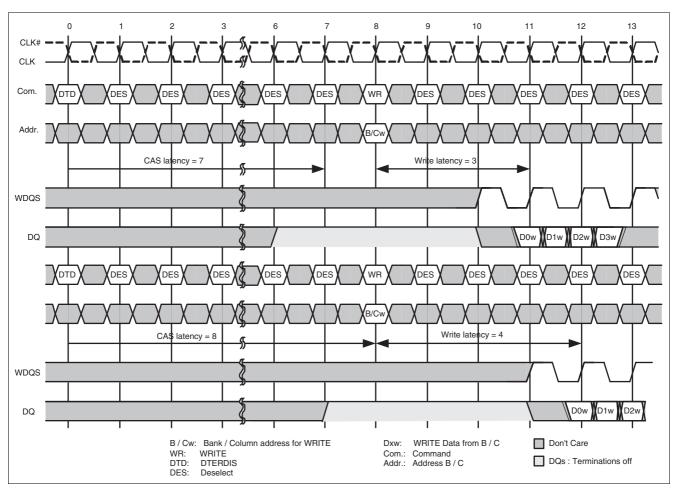

| 4.8.3         | DTERDIS followed by Write                                           |    |

| 4.9           | Precharge (PRE/PREALL)                                              |    |

| 4.10          | Auto Refresh Command (AREF)                                         |    |

| 4.11          | Self-Refresh                                                        |    |

| 4.11.1        | Self-Refresh Entry (SREFEN)                                         |    |

| 4.12          | Self-Refresh Exit (SREFEX)                                          |    |

| 4.13          | Power-Down                                                          |    |

| 4.14          | DLL Off Mode                                                        |    |

| 4.14.1        | Frequency range in DLL off mode                                     |    |

| 4.14.2        | Initialization in DLL off mode                                      |    |

| 4.14.3        | Writes (WR) in DLL off mode                                         |    |

| 4.14.4        | Reads (RD) in DLL off mode                                          |    |

| 4.14.5        | Self Refresh in DLL off mode                                        | 79 |

| 5             | Electrical Characteristics                                          | 80 |

| 5.1           | Absolute Maximum Ratings and Operation Conditions                   |    |

| 5.2           | DC Operation Conditions                                             |    |

| 5.2.1         | Recommended Power & DC Operation Conditions.                        |    |

| 5.2. i<br>5.3 | DC & AC Logic Input Levels                                          |    |

| 5.4           | Differential Clock DC and AC Levels                                 |    |

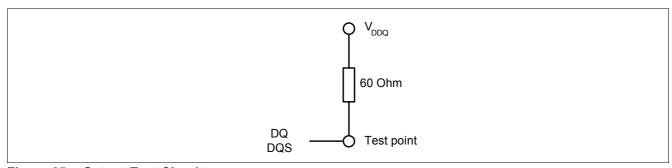

| 5.5           | Output Test Conditions                                              |    |

| 5.6           | Pin Capacitances                                                    |    |

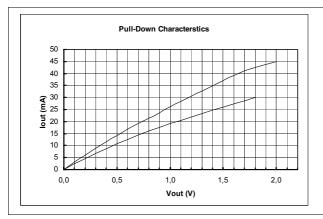

| 5.7           | Driver current characteristics                                      |    |

| 5.7.1         | Driver IV characteristics at 40 Ohms                                |    |

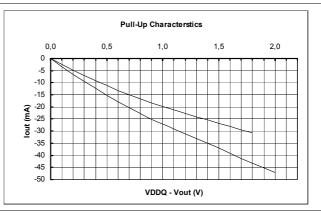

| 5.7.2         | Termination IV Characteristic at 60 Ohms                            |    |

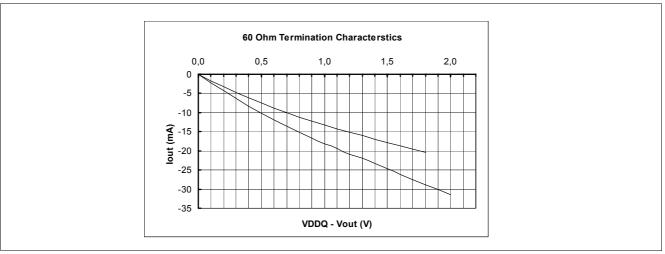

| 5.8           | Termination IV Characteristic at 120 Ohms                           |    |

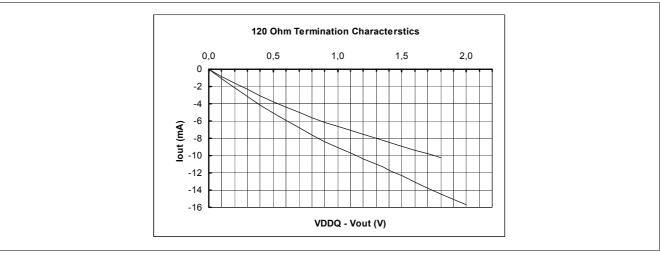

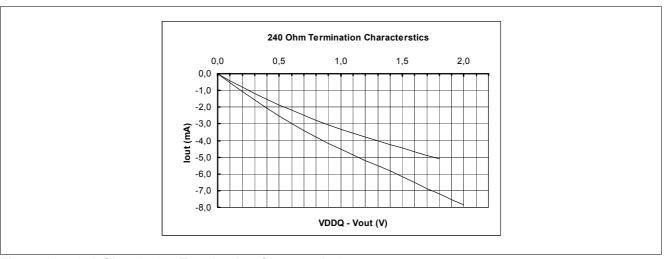

| 5.9           | Termination IV Characteristic at 240 Ohms                           |    |

| 5.10          | Operating Currents                                                  |    |

| 5.10.1        | Operating Current Ratings ( HYB18H512321AF–12/14/16/20 )            |    |

| 5.10.2        | Operating Current Ratings (HYB18H512321AFL14/16/20)                 |    |

| 5.10.2        | Operating Current Measurement Conditions                            |    |

| 5.12          | AC Timings (HYB18H512321AF–12/14/16/20)                             |    |

| 5.12          | AC Timings (HYB18H512321AFL14/16/20)                                |    |

|               |                                                                     |    |

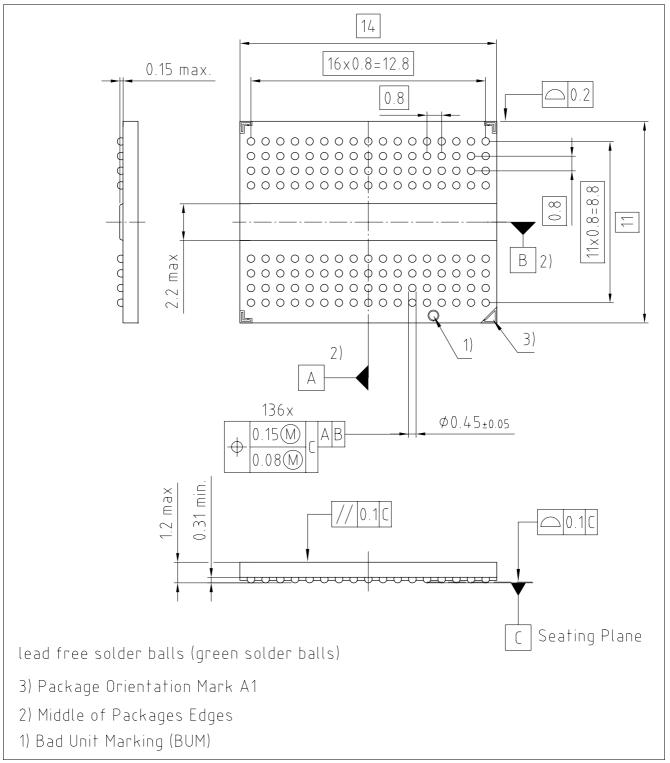

| 6             | Package                                                             |    |

| 6.1           | Package Outline                                                     |    |

| 6.2           | Package Thermal Characteristics                                     | aa |

# List of figures

| Figure 1               | Ballout 512Mbit GDDR3 Graphics RAM [Top View, MF = Low]                              |    |

|------------------------|--------------------------------------------------------------------------------------|----|

| Figure 2               | Functional Block Diagram                                                             |    |

| Figure 3               | State diagram for one bank                                                           | 20 |

| Figure 4               | Internal Block Diagram (Reference only)                                              | 23 |

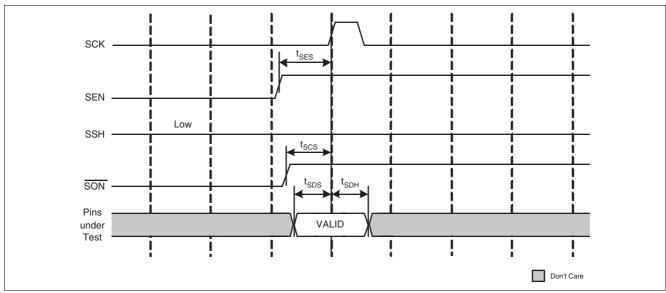

| Figure 5               | Scan Capture Timing                                                                  | 26 |

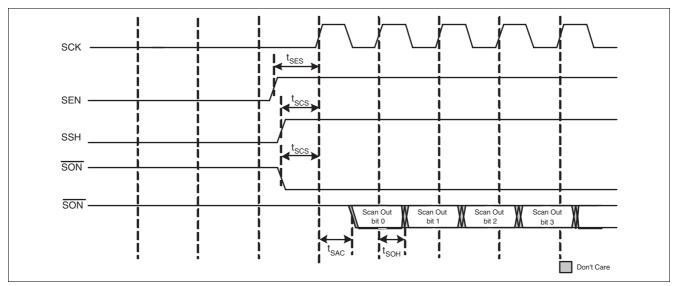

| Figure 6               | Scan Shift Timing                                                                    | 26 |

| Figure 7               | Scan Initialization for Stand-Alone mode                                             |    |

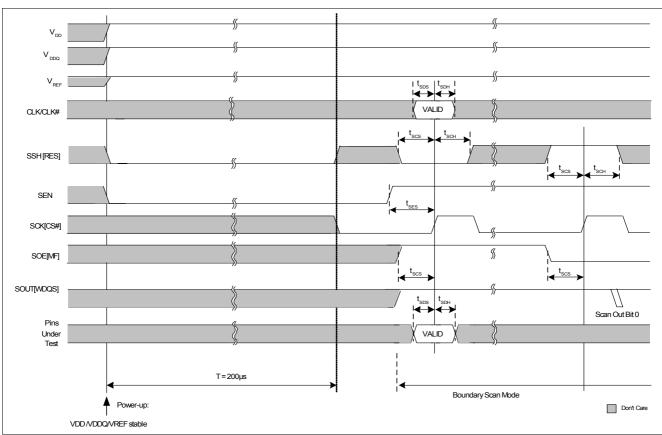

| Figure 8               | Scan Initialization Sequence within regular SGRAM Mode                               |    |

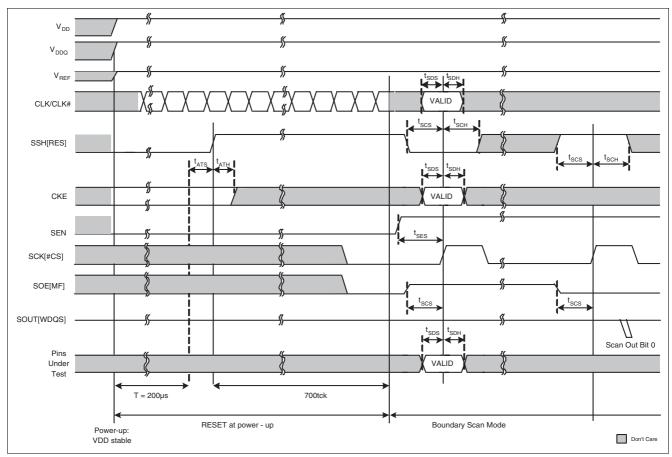

| Figure 9               | Boundary Scan Exit Sequence                                                          |    |

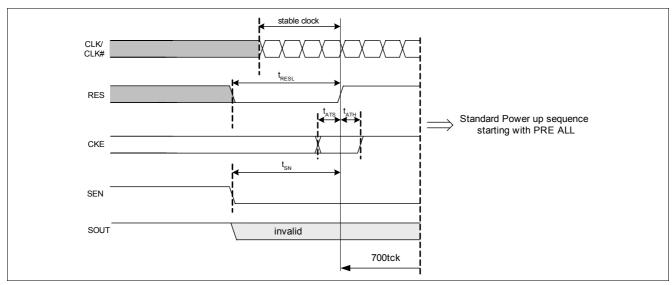

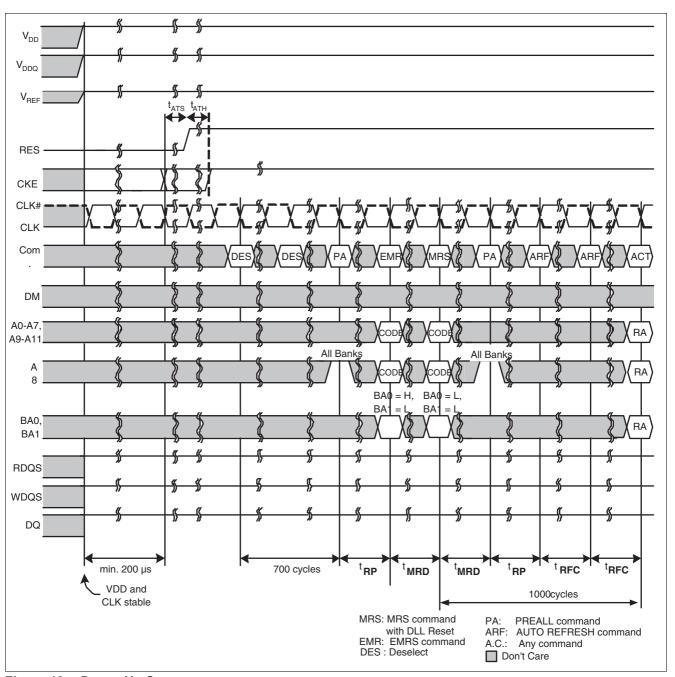

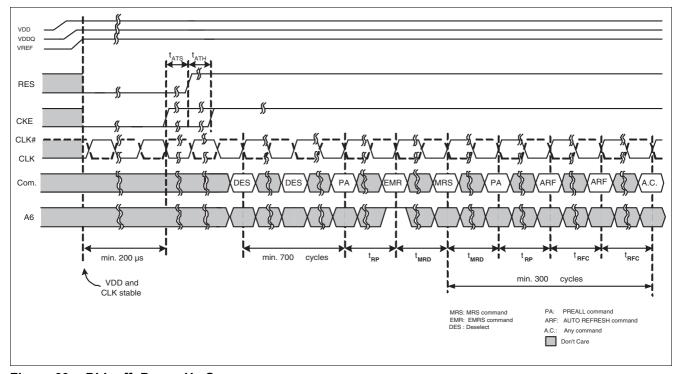

| Figure 10              | Power Up Sequence                                                                    |    |

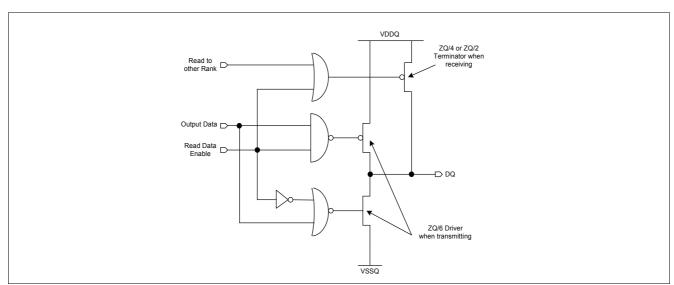

| Figure 11              | Output Driver simplified schematic                                                   |    |

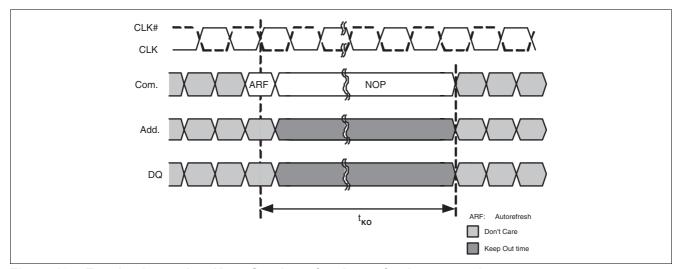

| Figure 12              | Termination update Keep Out time after Autorefresh command                           |    |

| Figure 13              | Self Calibration of PMOS and NMOS Legs                                               |    |

| Figure 14              | ODT Disable Timing during a READ command                                             |    |

| Figure 16              | Extended Mode Register Bitmap                                                        |    |

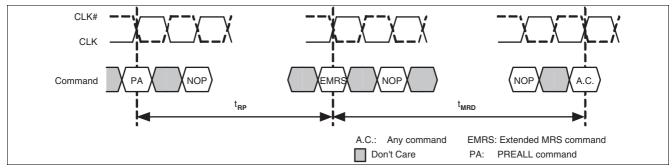

| Figure 17              | Extended Mode Register Set Timing                                                    |    |

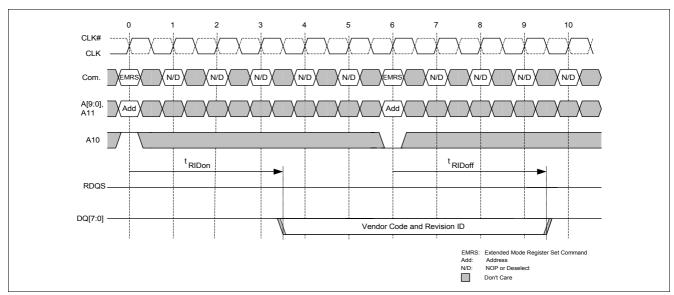

| Figure 17              | Timing of Vendor Code and Revision ID Generation on DQ[7:0]                          |    |

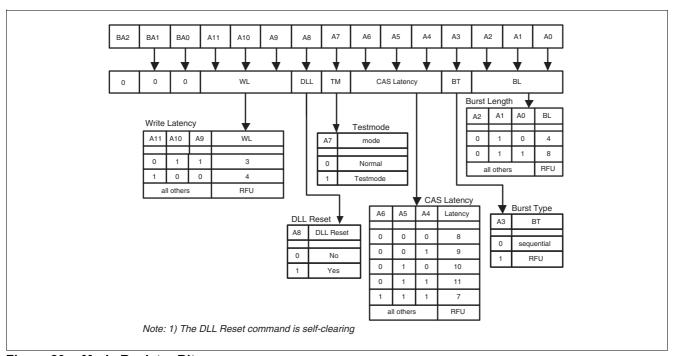

| 0                      | Mode Register Bitmap                                                                 |    |

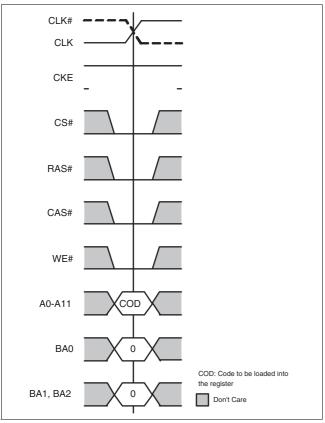

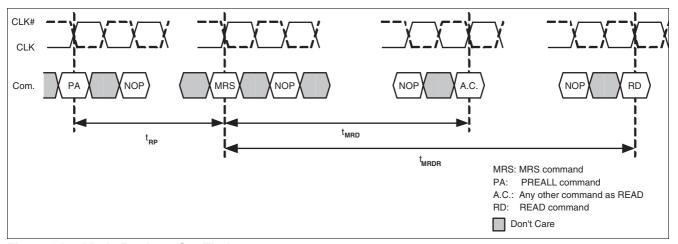

| Figure 20<br>Figure 21 | Mode Register Set Timing                                                             |    |

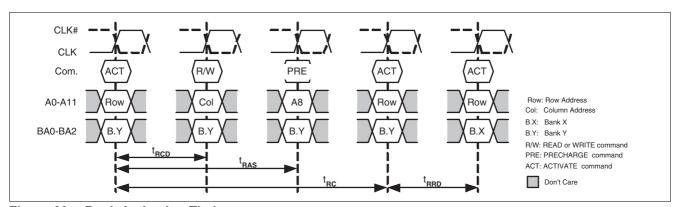

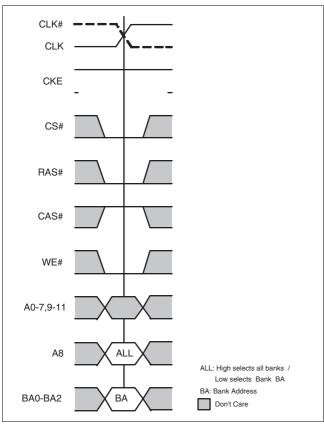

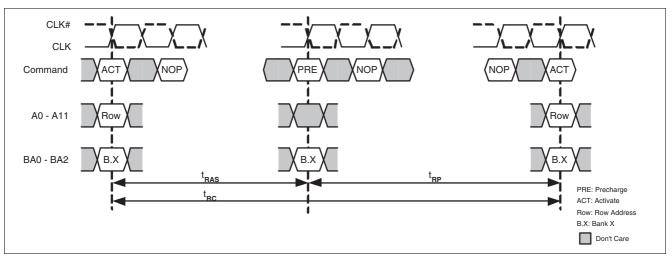

| Figure 23              | Bank Activating Timing                                                               |    |

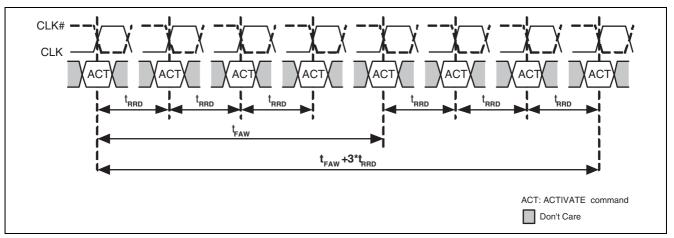

| Figure 24              | Four Window Active $t_{\sf FAW}$                                                     |    |

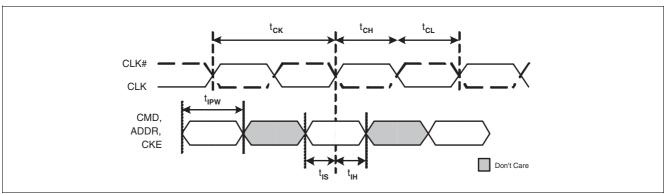

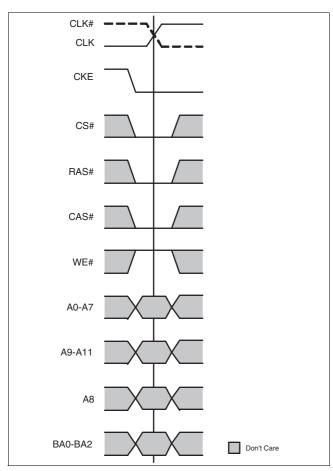

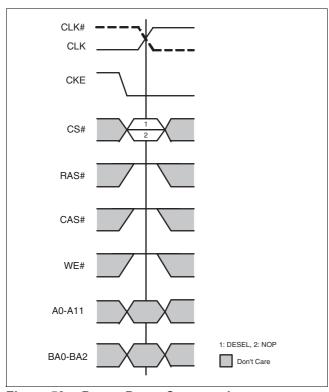

| •                      | Clock, CKE and Command/Address Timings                                               |    |

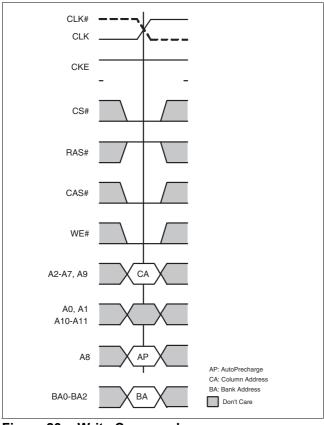

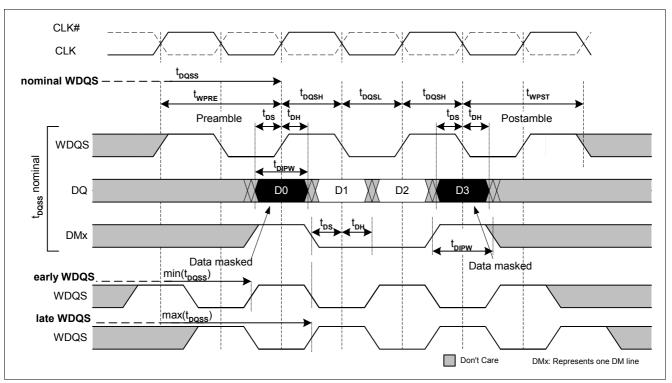

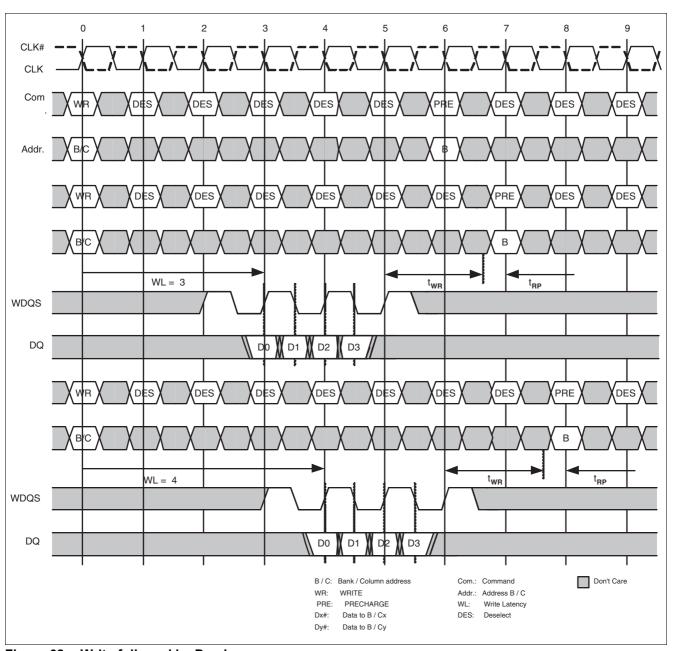

| Figure 25              | Basic Write Burst / DM Timing                                                        |    |

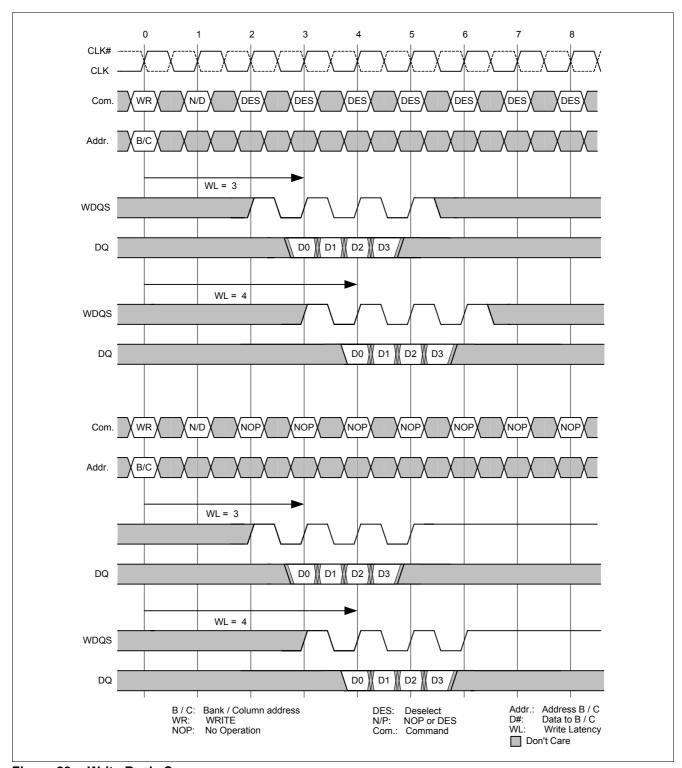

| Figure 27<br>Figure 28 | Write Basic Sequence                                                                 |    |

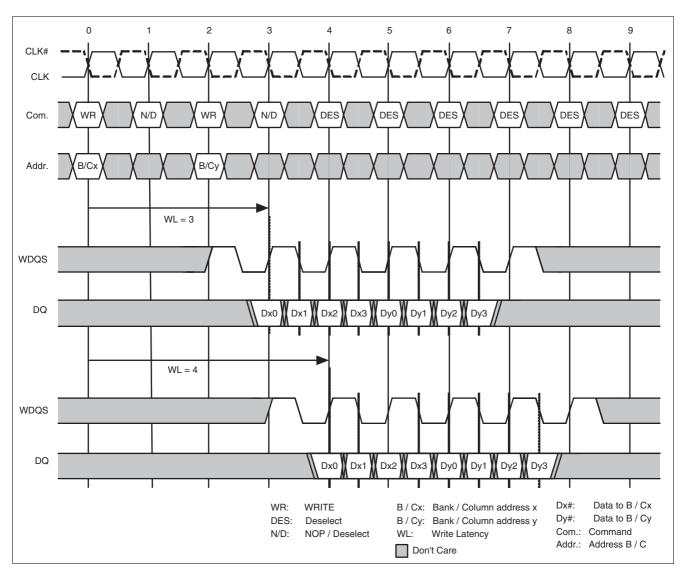

|                        | Gapless Write Bursts                                                                 |    |

| Figure 29              | Consecutive Write Bursts with Gaps                                                   |    |

| Figure 30<br>Figure 31 | Write with Autoprecharge                                                             |    |

| Figure 31              | Write followed by Read                                                               |    |

| Figure 32              | Write Command followed by DTERDIS                                                    |    |

| Figure 34              | Write with Autoprecharge followed by Read or Read with Autoprecharge on another bank |    |

| Figure 35              | Write followed by Precharge on same Bank                                             |    |

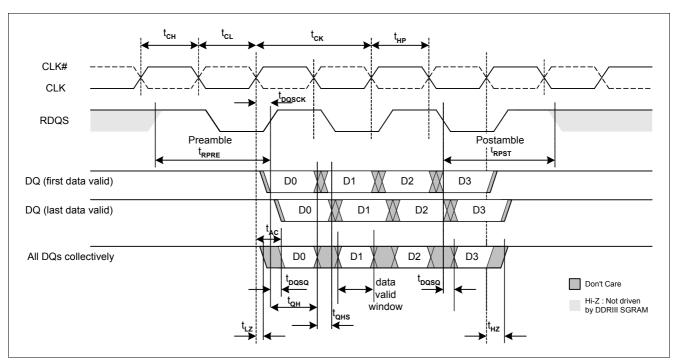

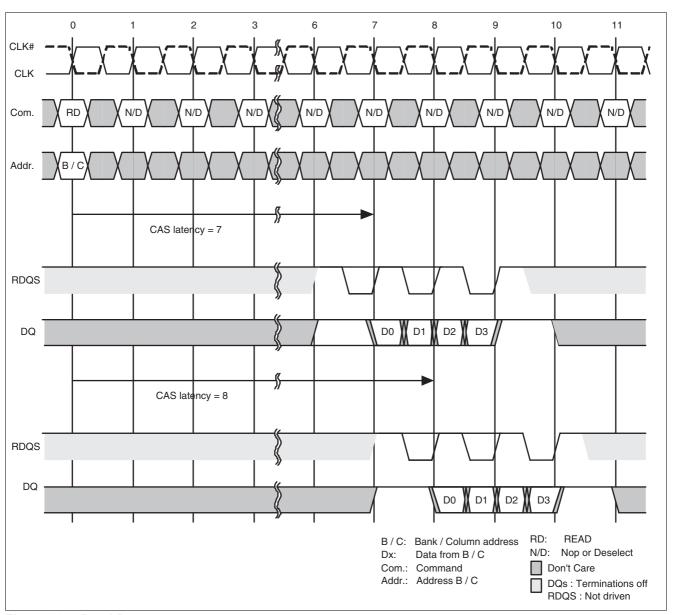

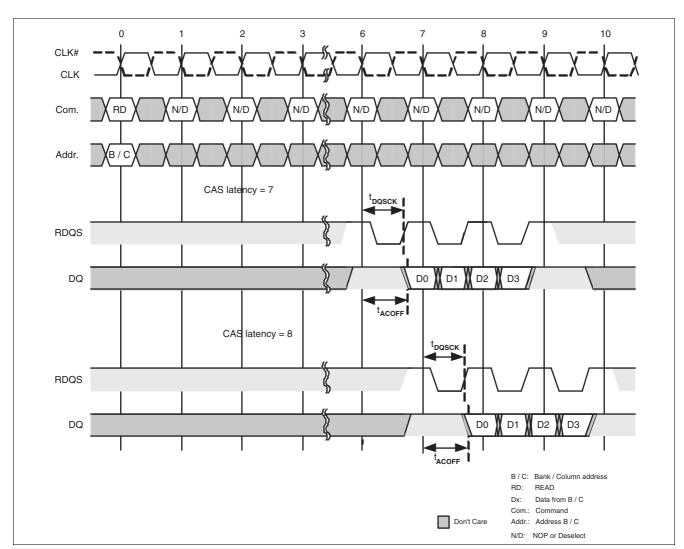

| Figure 37              | Basic Read Burst Timing                                                              | 56 |

| Figure 37              | Read Burst                                                                           |    |

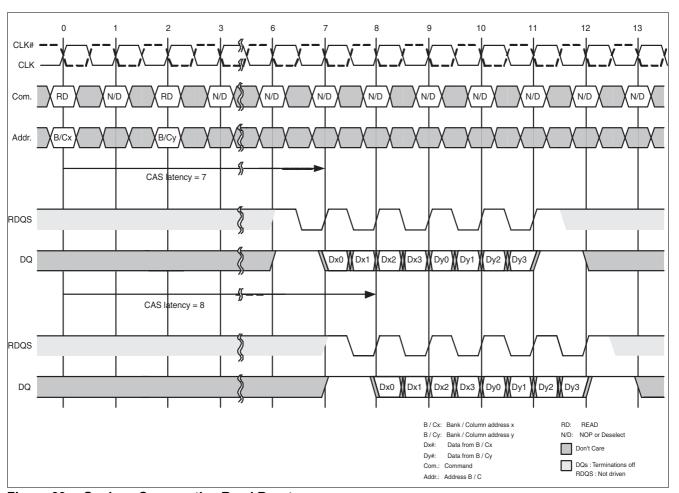

| Figure 39              | Gapless Consecutive Read Bursts                                                      |    |

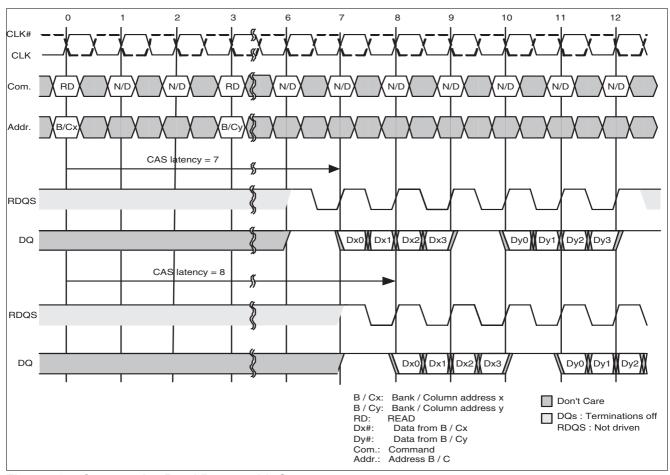

| Figure 40              | Consecutive Read Bursts with Gaps                                                    |    |

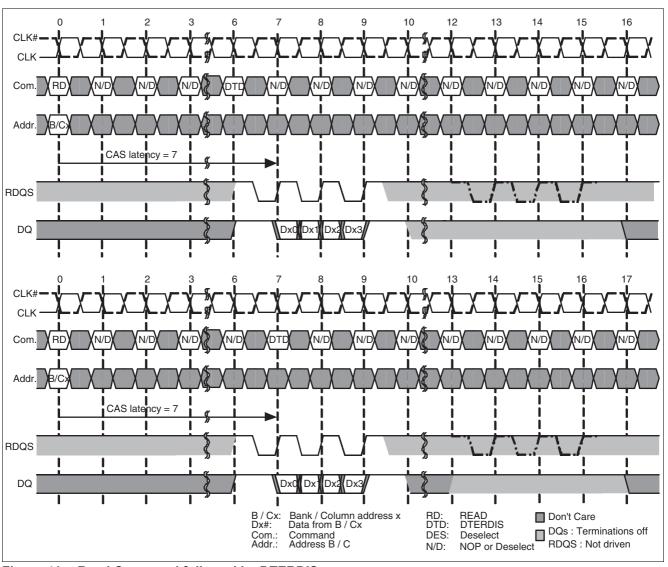

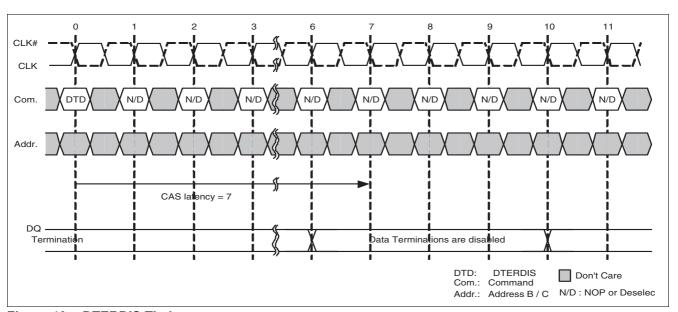

| Figure 40              | Read Command followed by DTERDIS                                                     |    |

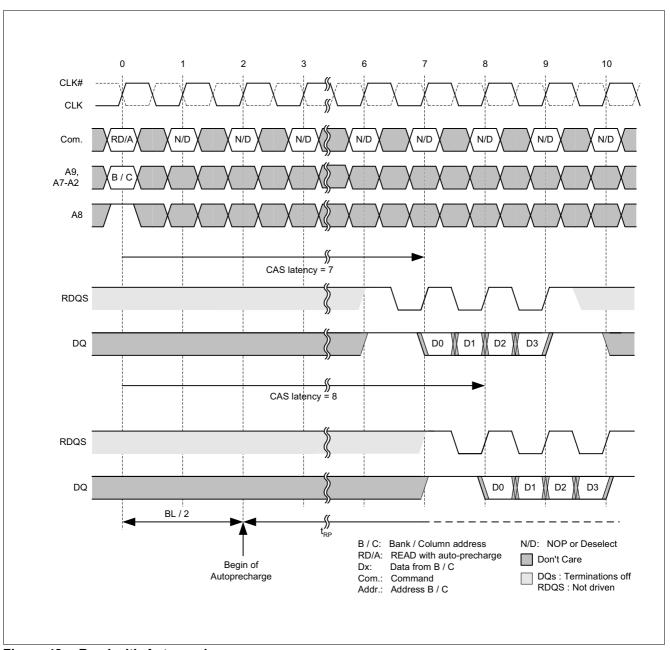

| Figure 41              | Read with Autoprecharge                                                              |    |

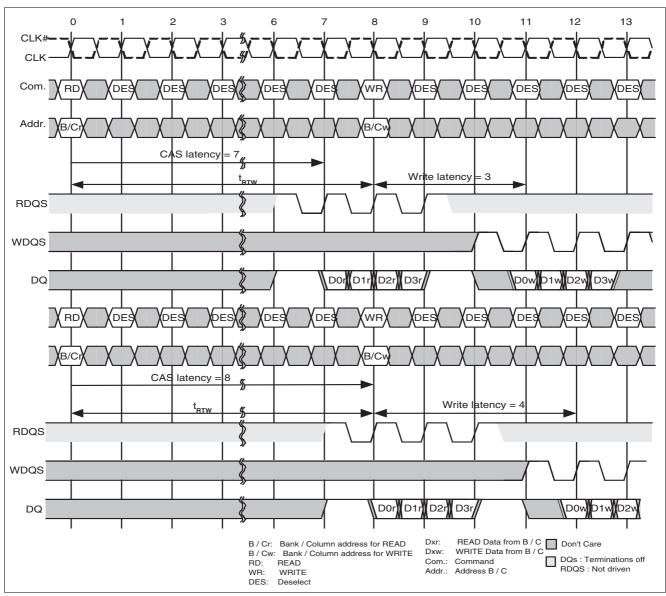

| Figure 42              | Read followed by Write                                                               |    |

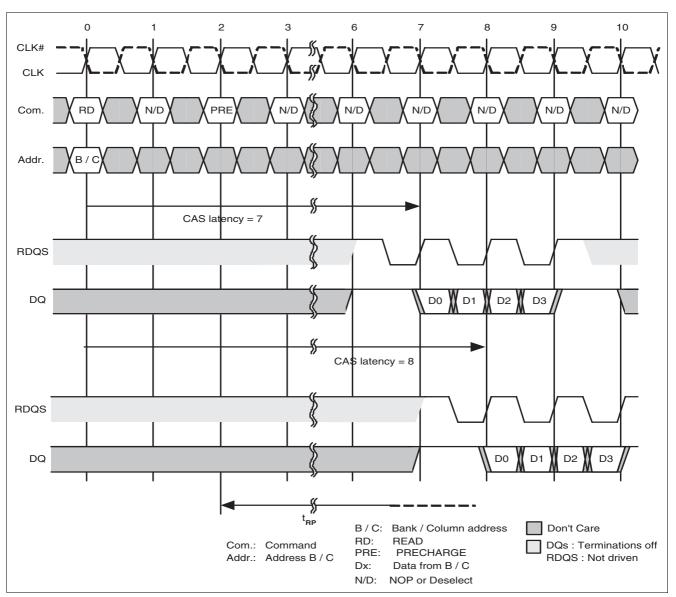

| Figure 43              | Read followed by Precharge on the same bank                                          |    |

| Figure 44<br>Figure 46 |                                                                                      |    |

| Figure 40<br>Figure 47 | DTERDIS Timing                                                                       | 65 |

| Figure 47              | DTERDIS Command followed by BTERDIS                                                  |    |

| Figure 46<br>Figure 49 | DTERDIS Command followed by Write                                                    |    |

|                        |                                                                                      |    |

| Figure 51              | Precharge Timing                                                                     |    |

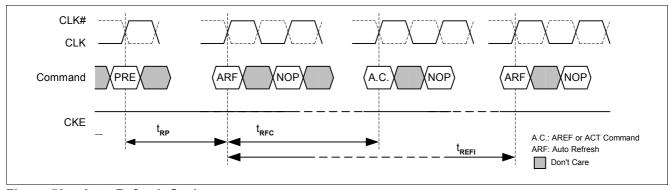

| Figure 53              | Auto Refresh Cycle                                                                   |    |

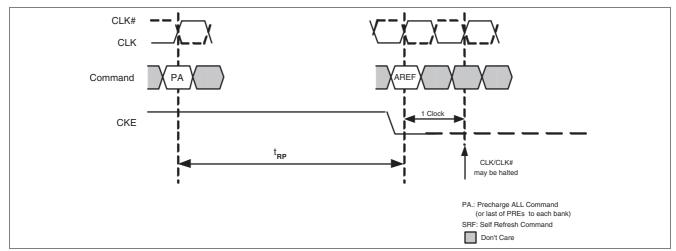

| Figure 54              | Self-Refresh Entry Command                                                           |    |

| Figure 55              | Self Refresh Entry                                                                   |    |

| Figure 57              | Self Refresh Exit                                                                    |    |

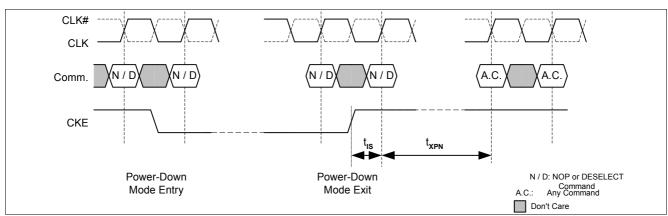

| Figure 59              | Power-Down Mode                                                                      |    |

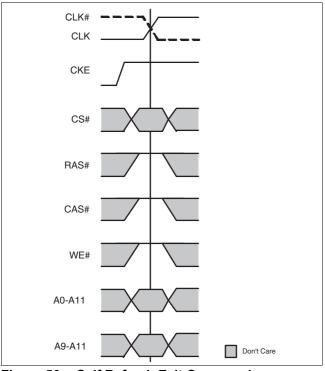

| Figure 60              | DLL off: Power Up Sequence                                                           |    |

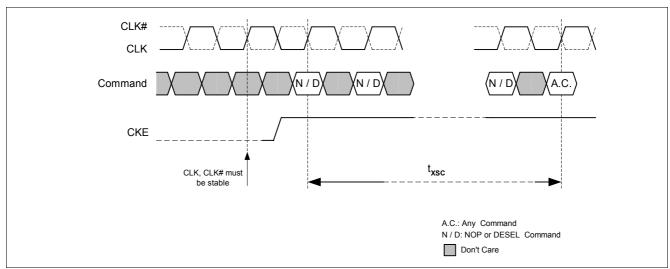

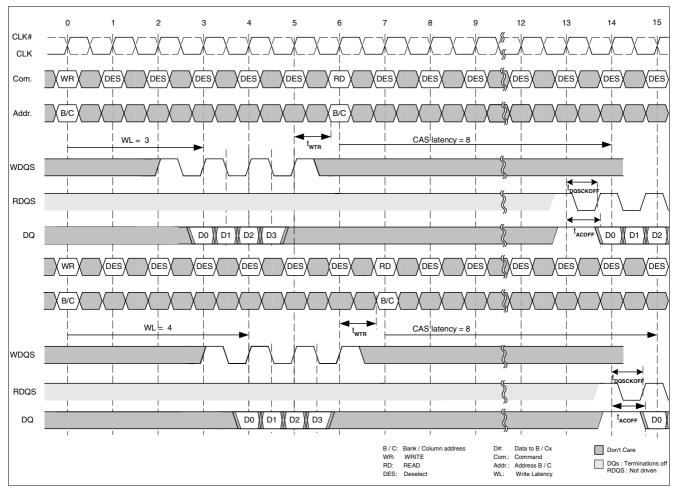

| Figure 61              | DLL off: Write followed by Read                                                      |    |

| Figure 62              | Write followed by Precharge                                                          |    |

| Figure 63              | DLL off: Read Burst                                                                  | 11 |

Data Sheet 6 Rev. 1.73, 2005-08

# HYB18H512321AF 512-Mbit GDDR3

| Figure 64 | DLL off: Read followed by Write                     | 78 |

|-----------|-----------------------------------------------------|----|

|           | Output Test Circuit                                 |    |

| Figure 66 | 40 Ohm Driver Pull-Down and Pull-Up characteristics | 84 |

| Figure 67 | 60 Ohm Active Termination Characteristic            | 85 |

| Figure 68 | 120 Ohm Active Termination Characteristics          | 86 |

| Figure 69 | 240 Ohm Active Termination Characteristic           | 87 |

| Figure 70 | PG-TFBGA 136 package (11mm x 14mm)                  | 98 |

Data Sheet 7 Rev. 1.73, 2005-08

## **List of Tables**

| Table 1  | Ordering Information                                                                       | 10 |

|----------|--------------------------------------------------------------------------------------------|----|

| Table 2  | Ball Description                                                                           | 12 |

| Table 3  | Ball Assignment with Mirror                                                                | 13 |

| Table 4  | Command Overview                                                                           | 16 |

| Table 5  | Description of Commands                                                                    | 17 |

| Table 6  | Minimum delay from RD/A and WR/A to any other command (to another bank) with concurrent    |    |

|          | Autoprecharge 19                                                                           |    |

| Table 7  | Function Truth Table I                                                                     | 21 |

| Table 8  | Function Truth Table II (CKE Table)                                                        |    |

| Table 9  | Boundary Scan Exit) Order                                                                  |    |

| Table 10 | Scan Pin Description                                                                       |    |

| Table 11 | Scan DC Electrical Characteristics and Operating Conditions                                |    |

| Table 12 | Scan AC Electrical Characteristics                                                         |    |

| Table 13 | Scan AC Electrical Parameters                                                              | 30 |

| Table 14 | Range of external resistance ZQ                                                            | 33 |

| Table 15 | Termination Types and Activation                                                           | 33 |

| Table 16 | Number of Legs used for Terminator and Driver Self Calibration                             | 35 |

| Table 17 | DC Electrical Characteristics                                                              | 36 |

| Table 18 | Revision ID and Vendor Code                                                                | 39 |

| Table 19 | Burst Definition                                                                           | 41 |

| Table 20 | Mapping of WDQS and DM Signals                                                             | 45 |

| Table 21 | BA02, BA1 and BA0 precharge bank selection                                                 | 68 |

| Table 22 | DLL off: General Timing Parameter for –16 and –20 speed sorts                              | 74 |

| Table 23 | General Timing Parameter                                                                   | 75 |

| Table 24 | Read Timing Parameter                                                                      | 77 |

| Table 25 | Self Refresh Exit Timing Parameter                                                         | 79 |

| Table 26 | Absolute Maximum Ratings                                                                   |    |

| Table 27 | Power & DC Operation Conditions.( $0  ^{\circ}\text{C} \le T_c \le 85  ^{\circ}\text{C}$ ) | 81 |

| Table 28 | DC & AC Logic Input Levels ( $0  ^{\circ}\text{C} \le T_{c} \le 85  ^{\circ}\text{C}$ )    | 82 |

| Table 29 | Differential Clock DC and AC Input conditions (0 °C ≤ T <sub>c</sub> ≤ 85 °C)              | 82 |

| Table 30 | Pin Capacitances (VDDQ = 1.8V, TA = 25°C, f= 1MHz)                                         | 83 |

| Table 31 | Programmed Driver IV Characterisitcs at 40 Ohm                                             | 84 |

| Table 32 | Programmed Terminator Characteristics at 60 Ohm                                            | 85 |

| Table 33 | Programmed Terminator Characteristics af 120 Ohm                                           |    |

| Table 34 | Programmed Terminator Characteristic at 240 Ohm                                            |    |

| Table 35 | Operating Current Ratings ( 0 °C $\leq$ T <sub>c</sub> $\leq$ 85 °C)                       | 88 |

| Table 36 | Operating Current Ratings ( $0  ^{\circ}\text{C} \le T_c \le 85  ^{\circ}\text{C}$ )       | 89 |

| Table 37 | Operating Current Measurement Conditions                                                   |    |

| Table 38 | Timing Parameters (HYB18H512321AF–12/14/16/20)                                             |    |

| Table 39 | Timing Parameters (HYB18H512321AFL14/16/20)                                                |    |

| Table 40 | PG-TFBGA 136 Package Thermal Resistances                                                   | 99 |

### 512-Mbit GDDR3 Graphics RAM

HYB18H512321AF HYB18H512321AF-12/14/16/20 HYB18H512321AFL14/16/20

## 1 Overview

#### 1.1 Features

- 2.0 V  $V_{\rm DDQ}$  IO voltage HYB18H512321AF–12/14/16/20

- 2.0 V  $V_{\mathrm{DD}}$  core voltage HYB18H512321AF–12/14/16/20

- 1.8 V  $V_{\rm DDQ}$  IO voltage HYB18H512321AFL14/16/20

- 1.8 V  $V_{\mathrm{DD}}$  core voltage HYB18H512321AFL14/16/20

- Organization: 2048K × 32 × 8 banks

- 4096 rows and 512 columns (128 burst start locations) per bank

- Differential clock inputs (CLK and CLK)

- CAS latencies of 7, 8, 9, 10, 11

- Write latencies of 3, 4

- · Burst sequence with length of 4, 8.

- 4n prefetch

- Short RAS to CAS timing for Writes

- t<sub>RAS</sub> Lockout support

- t<sub>WR</sub> programmable for Writes with Auto-Precharge

- · Data mask for write commands

- Single ended READ strobe (RDQS) per byte. RDQS edge-aligned with READ data

- Single ended WRITE strobe (WDQS) per byte. WDQS center-aligned with WRITE data

- DLL aligns RDQS and DQ transitions with Clock

- Programmable IO interface including on chip termination (ODT)

- · Autoprecharge option with concurrent autoprecharge support

- 8k Refresh (32ms)

- · Autorefresh and Self Refresh

- PG-TFBGA 136 package (11mm × 14mm)

- Calibrated output drive. Active termination support

- RoHS Compliant Product<sup>1)</sup>

<sup>1)</sup>RoHS Compliant Product: Restriction of the use of certain hazardous substances (RoHS) in electrical and electronic equipment as defined in the directive 2002/95/EC issued by the European Parliament and of the Council of 27 January 2003. These substances include mercury, lead, cadmium, hexavalent chromium, polybrominated biphenyls and polybrominated biphenyl ethers.

05122004-B1L1-JEN8

Overview

Table 1 Ordering Information

| Part Number <sup>1)</sup>  | Organisation | Clock (MHz)     | Package      |

|----------------------------|--------------|-----------------|--------------|

| HYB18H512321AF-12/14/16/20 | ×32          | 800/700/600/500 | PG-TFBGA 136 |

| HYB18H512321AFL14/16/20    |              | 700/600/500     |              |

1) HYB: designator for memory components

18H:  $V_{\rm DDQ}$  = 1.8 V 512: 512-Mbit density 32: Organization A: Product revision

F: Lead- and Halogen-Free L: Low power product

# 1.2 Description

The Infineon 512-Mbit GDDR3 Graphics RAM is a high speed memory device, designed for high bandwidth intensive applications like PC graphics systems. The chip's 8 bank architecture is optimized for high speed.

HYB18H512321AF uses a double data rate interface and a 4*n*-prefetch architecture. The GDDR3 interface transfers two 32 bit wide data words per clock cycle to/from the I/O pins. Corresponding to the 4*n*-prefetch a single write or read access consists of a 128 bit wide, one-clock-cycle data transfer at the internal memory core and four corresponding 32 bit wide, one-half-clock-cycle data transfers at the I/O pins.

Single-ended unidirectional Read and Write Data strobes are transmitted simultaneously with Read and Write data respectively in order to capture data properly at the receivers of both the Graphics SDRAM and the controller. Data strobes are organized per byte of the 32 bit wide interface. For read commands the RDQS are edge-aligned with data, and the WDQS are center-aligned with data for write commands.

The HYB18H512321AF operates from a differential clock (CLK and  $\overline{\text{CLK}}$ ). Commands (addresses and control signals) are registered at every positive edge of CLK. Input data is registered on both edges of WDQS, and output data is referenced to both edges of RDQS.

In this document references to 'the positive edge of CLK' imply the crossing of the positive edge of CLK and the negative edge of  $\overline{\text{CLK}}$ . Similarly, the 'negative edge of CLK' refers to the crossing of the negative edge of CLK and the positive edge of  $\overline{\text{CLK}}$ . References to RDQS are to be interpreted as any or all RDQS<3:0>. WDQS, DM and DQ should be interpreted in a similar fashion.

Read and write accesses to the HYB18H512321AF are burst oriented. The burst length is fixed to 4 and 8 and the two least significant bits of the burst address are 'Don't Care' and internally set to LOW. Accesses begin with the registration of an ACTIVATE command, which is then followed by a READ or WRITE command. The address bits registered coincident with the ACTIVATE command are used to select the bank and the row to be accessed. The address bits registered coincident with the READ or WRITE command are used to select the bank and the column location for the burst access. Each of the 8 banks consists of 4096 row locations and 512 column locations. An AUTO PRECHARGE function can be combined with READ and WRITE to provide a self-timed row precharge that is initiated at the end of the burst access. The pipelined, multibank architecture of the HYB18H512321AF allows for concurrent operation, thereby providing high effective bandwidth by hiding row precharge and activation time.

The "On Die Termination" interface (ODT) is optimized for high frequency digital data transfers and is internally controlled. The termination resistor value can be set using an external ZQ resistor or disabled through the Extended Mode Register.

The output driver impedance can be set using the Extended Mode Register. It can either be set to ZQ / 6 (autocalibration) or to 35, 40 or 45 Ohms.

Auto Refresh and Power Down with Self Refresh operations are supported.

A standard JEDEC PG-TFBGA 136 package is used which enables ultra high speed data transfer rates and a simple upgrade path from former DDR Graphics SDRAM products.

# 2 Pin Configuration

| 1                            | 2                           | 3            | 4                            | 5 | 6 | 7 | 8 | 9                            | 10                | 11                                  | 12                                    |

|------------------------------|-----------------------------|--------------|------------------------------|---|---|---|---|------------------------------|-------------------|-------------------------------------|---------------------------------------|

| $V_{\mathrm{DDQ}}$           | $V_{\scriptscriptstyle DD}$ | $V_{ m SS}$  | ZQ                           |   | А |   |   | MF                           | $V_{\mathrm{SS}}$ | $V_{\scriptscriptstyle 	extsf{DD}}$ | $V_{\scriptscriptstyle DDQ}$          |

| $V_{\mathrm{SSQ}}$           | DQ0                         | DQ1          | $V_{\mathtt{SSQ}}$           |   | В |   |   | $V_{ m SSQ}$                 | DQ9               | DQ8                                 | $V_{ m SSQ}$                          |

| $V_{DDQ}$                    | DQ2                         | DQ3          | $V_{\scriptscriptstyle DDQ}$ |   | С |   |   | $V_{DDQ}$                    | DQ11              | DQ10                                | $V_{\scriptscriptstyle DDQ}$          |

| $V_{ m SSQ}$                 | WDQS0                       | RDQS0        | $V_{\mathrm{SSQ}}$           |   | D |   |   | $V_{\mathrm{SSQ}}$           | RDQS1             | WDQS1                               | $V_{ m SSQ}$                          |

| $V_{\mathrm{DDQ}}$           | DQ4                         | DM0          | $V_{\scriptscriptstyle DDQ}$ |   | Е |   |   | $V_{\scriptscriptstyle DDQ}$ | DM1               | DQ12                                | $V_{\scriptscriptstyle \mathrm{DDQ}}$ |

| $V_{\scriptscriptstyle DD}$  | DQ6                         | DQ5          | CAS                          |   | F |   |   | - CS                         | DQ13              | DQ14                                | $V_{\scriptscriptstyle { m DD}}$      |

| $V_{\rm SS}$                 | $V_{\mathrm{SSQ}}$          | DQ7          | BA0                          |   | G |   |   | BA1                          | DQ15              | $V_{\mathrm{SSQ}}$                  | $V_{ m SS}$                           |

| $V_{REF}$                    | A1                          | RAS          | CKE                          |   | Н |   |   | WE                           | BA2               | A5                                  | $V_{REF}$                             |

| $V_{ m SSA}$                 | RFU                         | RFU          | $V_{\scriptscriptstyle DDQ}$ |   | J |   |   | $V_{\scriptscriptstyle DDQ}$ | CK                | СК                                  | $V_{\mathtt{SSA}}$                    |

| $V_{\scriptscriptstyle DDA}$ | A10                         | A2           | A0                           |   | K |   |   | A4                           | A6                | A8/AP                               | $V_{\scriptscriptstyle DDA}$          |

| $V_{\rm SS}$                 | $V_{\mathrm{SSQ}}$          | DQ25         | A11                          |   | L |   |   | A7                           | DQ17              | $V_{\mathrm{SSQ}}$                  | $V_{\mathrm{SS}}$                     |

| $V_{DD}$                     | DQ24                        | DQ27         | А3                           |   | М |   |   | A9                           | DQ19              | DQ16                                | $V_{DD}$                              |

| $V_{\scriptscriptstyle DDQ}$ | DQ26                        | DM3          | $V_{\scriptscriptstyle DDQ}$ |   | N |   |   | $V_{\scriptscriptstyle DDQ}$ | DM2               | DQ18                                | $V_{\scriptscriptstyle DDQ}$          |

| $V_{\mathrm{SSQ}}$           | WDQS3                       | RDQS3        | $V_{\mathtt{SSQ}}$           |   | Р |   |   | $V_{ m SSQ}$                 | RDQS2             | WDQS2                               | $V_{ m SSQ}$                          |

| $V_{DDQ}$                    | DQ28                        | DQ29         | $V_{\scriptscriptstyle DDQ}$ |   | R |   |   | $V_{\scriptscriptstyle DDQ}$ | DQ21              | DQ20                                | $V_{\scriptscriptstyle DDQ}$          |

| $V_{\mathrm{SSQ}}$           | DQ30                        | DQ31         | $V_{ m SSQ}$                 |   | Т |   |   | $V_{ m SSQ}$                 | DQ23              | DQ22                                | $V_{\mathrm{SSQ}}$                    |

| $V_{\mathtt{DDQ}}$           | $V_{DD}$                    | $V_{\rm SS}$ | SEN                          |   | V |   |   | RESET                        | $V_{\rm SS}$      | $V_{\scriptscriptstyle DD}$         | $V_{\scriptscriptstyle DDQ}$          |

Figure 1 Ballout 512Mbit GDDR3 Graphics RAM [Top View, MF = Low ]

# 2.1 Ball Definition and Description

Table 2 Ball Description

| Ball            | Type   | Detailed Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK, CLK        | Input  | Clock: CLK and CLK are differential clock inputs. Address and command inputs are latched on the positive edge of CLK. Graphics SDRAM outputs (RDQS, DQs) are referenced to CLK. CLK and CLK are not internally terminated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CKE             | Input  | Clock Enable: CKE HIGH activates and CKE LOW deactivates the internal clock and input buffers. Taking CKE LOW provides Power Down. If all banks are precharged, this mode is called Precharge Power Down and Self Refresh mode is entered if a Auto Refresh command is issued. If at least one bank is open, Active Power Down mode is entered and no Self Refresh is allowed. All input receivers except CLK, CLK and CKE are disabled during Power Down. In Self Refresh mode the clock receivers are disabled too. Self Refresh Exit is performed by setting CKE asynchronously HIGH. Exit of Power Down without Self Refresh is accomplished by setting CKE HIGH with a positive edge of CLK. The value of CKE is latched asynchronously by Reset during Power On to determine the value of the termination resistor of the address and command inputs. CKE is not allowed to go LOW during a RD, a WR or a snoop burst. |

| <u>CS</u>       | Input  | Chip Select: $\overline{CS}$ enables the command decoder when low and disables it when high. When the command decoder is disabled, new commands with the exeption of DTERDIS are ignored, but internal operations continue. $\overline{CS}$ is one of the four command balls.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RAS, CAS,<br>WE | Input  | <b>Command Inputs:</b> Sampled at the positive edge of CLK, $\overline{CAS}$ , $\overline{RAS}$ , and $\overline{WE}$ define (together with $\overline{CS}$ ) the command to be executed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DQ<0:31>        | I/O    | <b>Data Input/Output:</b> The DQ signals form the 32 bit data bus. During READs the balls are outputs and during WRITEs they are inputs. Data is transferred at both edges of RDQS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DM<0:3>         | Input  | Input Data Mask: The DM signals are input mask signals for WRITE data. Data is masked when DM is sampled HIGH with the WRITE data. DM is sampled on both edges of WDQS. DM0 is for DQ<0:7>, DM1 is for DQ<8:15>, DM2 is for DQ<16:23> and DM3 is for DQ<24:31>. Although DM balls are input-only, their loading is designed to match the DQ and WDQS balls.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RDQS<0:3>       | Output | <b>Read Data Strobes:</b> RDQSx are unidirectional strobe signals. During READs the RDQSx are transmitted by the Graphics SDRAM and edge-aligned with data. RDQS have preamble and postamble requirements. RDQS0 is for DQ<0:7>, RDQS1 for DQ<8:15>, RDQS2 for DQ<16:23> and RDQS3 for DQ<24:31>.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| WDQS<0:3>       | Input  | <b>Write Data Strobes:</b> WDQS are unidirectional strobe signals. During WRITEs the WDQS are generated by the controller and center aligned with data. WDQS have preamble and postamble requirements. WDQS0 is for DQ<0:7>, WDQS1 for DQ<8:15>, WDQS2 for DQ<16:23> and WDQS3 for DQ<24:31>.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| BA<0:2>         | Input  | <b>Bank Address Inputs:</b> BA select to which internal bank an ACTIVATE, READ, WRITE or PRECHARGE command is being applied. BA are also used to distinguish between the MODE REGISTER SET and EXTENDED MODE REGISTER SET commands.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

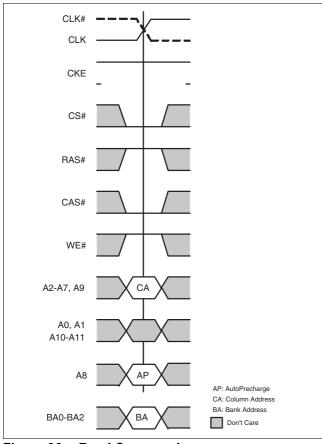

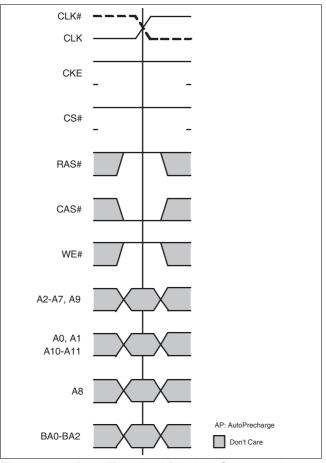

| A<0:11>         | Input  | Address Inputs: During ACTIVATE, A0-A11 defines the row address. For READ/WRITE, A2-A7 and A9 defines the column address, and A8 defines the auto precharge bit. If A8 is HIGH, the accessed bank is precharged after execution of the column access. If A8 is LOW, AUTO PRECHARGE is disabled and the bank remains active. Sampled with PRECHARGE, A8 determines whether one bank is precharged (selected by BA<0:2>, A8 LOW) or all 8 banks are precharged (A8 HIGH). During (EXTENDED) MODE REGISTER SET the address inputs define the register settings. A<0:11> are sampled with the positive edge of CLK.                                                                                                                                                                                                                                                                                                              |

Table 2 Ball Description

| Ball                                                                        | Type   | Detailed Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ZQ                                                                          | -      | ODT Impedance Reference: The ZQ ball is used to control the ODT impedance.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| RES                                                                         | Input  | <b>Reset pin:</b> The RES pin is a $V_{\rm DDQ}$ CMOS input. RES is not internally terminated. When RES is at LOW state the chip goes into full reset. The chip stays in full reset until RES goes to HIGH state. The Low to High transition of the RES signal is used to latch the CKE value to set the value of the termination resistors of the address and command inputs. After exiting the full reset a complete initialization is required since the full reset set the internal settings to default. |

| MF                                                                          | Input  | <b>Mirror function pin:</b> The MF pin is a $V_{\rm DDQ}$ CMOS input. This pin must be hardwired on board either to a power or to a ground plane. With MF set to HIGH, the command and address pins are reassigned in order to allow for an easier routing on board for a back to back memory arrangement.                                                                                                                                                                                                   |

| SEN                                                                         | Input  | Enables <b>Boundary Scan</b> Functionality. If Boundary Scan is not used PIN should be constantly connected to GND.                                                                                                                                                                                                                                                                                                                                                                                          |

| $V_{REF}$                                                                   | Supply | Voltage Reference: V <sub>REF</sub> is the reference voltage input.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| $\overline{V_{\text{DD}}, V_{\text{SS}}}, \ V_{\text{DDA}}, V_{\text{SSA}}$ | Supply | <b>Power Supply:</b> Power and Ground for the internal logic. $V_{\rm DD}$ and $V_{\rm DDA}$ must be provided by the same power rail. Shorted in the package.                                                                                                                                                                                                                                                                                                                                                |

| $\overline{V_{\text{DDQ}}},  V_{\text{SSQ}}$                                | Supply | I/O Power Supply: Isolated Power and Ground for the output buffers to provide improved noise immunity.                                                                                                                                                                                                                                                                                                                                                                                                       |

| NC, RFU                                                                     | -      | Please do not connect No Connect and Reserved for Future Use balls.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

#### 2.2 Mirror Function

The GDDR3 Graphics RAM provides a ball mirroring feature that is enabled by applying a logic HIGH on ball MF. This function allows for efficient routing in a clam shell configuration.

Depending of the logic state applied on MF, the command and address signals will be assigned to different balls. The default ball configuration (see **Figure 1**) correponds to MF = LOW.

The DC level (HIGH or LOW) must be applied on the MF pin at power up and is not allowed to change after that.

Table 3 shows the ball assignment as a function of the logic state applied on MF.

Table 3 Ball Assignment with Mirror

| MF Logic State |      | Signal |  |

|----------------|------|--------|--|

| LOW            | HIGH |        |  |

| H3             | H10  | RAS    |  |

| F4             | F9   | CAS    |  |

| H9             | H4   | WE     |  |

| F9             | F4   | CS     |  |

| H4             | H9   | CKE    |  |

| K4             | K9   | A0     |  |

| H2             | H11  | A1     |  |

| K3             | K10  | A2     |  |

| M4             | M9   | A3     |  |

| K9             | K4   | A4     |  |

| H11            | H2   | A5     |  |

| K10            | K3   | A6     |  |

Table 3 Ball Assignment with Mirror (cont'd)

| MF Logic State |      | Signal |  |

|----------------|------|--------|--|

| LOW            | HIGH |        |  |

| L9             | L4   | A7     |  |

| K11            | K2   | A8     |  |

| M9             | M4   | A9     |  |

| K2             | K11  | A10    |  |

| L4             | L9   | A11    |  |

| G4             | G9   | BA0    |  |

| G9             | G4   | BA1    |  |

| H10            | H3   | BA2    |  |

# 2.3 Functional Block Diagram

Figure 2 Functional Block Diagram

#### 2.4 Commands

#### 2.4.1 Command Table

In the following table CKEn refers to the positive edge of CLK corresponding to the clock cycle when the command is given to the Graphics SDRAM. CKEn-1 refers to the previous positive edge of CLK. For all command and address inputs CKEn is implied.

All input states or sequences not shown are illegal or reserved.

Table 4 Command Overview

| Operation                     | Code    | CKE<br>n-1 | CKE<br>n | cs     | RAS    | CAS    | WE     | BA0 | BA1 | BA2 | <b>A8</b>      | A2-7<br>A9-11 | Note |

|-------------------------------|---------|------------|----------|--------|--------|--------|--------|-----|-----|-----|----------------|---------------|------|

| Device Deselect               | DESEL   | Н          | Н        | Н      | L      | Χ      | Х      | Х   |     | Х   | Х              | Х             | 1)   |

|                               |         |            |          |        | Χ      | X      | L      |     |     |     |                |               |      |

|                               |         |            |          |        | Н      | Н      | Н      |     |     |     |                |               |      |

| Data Terminator Disable       | DTERDIS | Н          | Н        | Н      | Н      | L      | Н      | Х   | X   | Х   | Х              | X             | 1)2) |

| No Operation                  | NOP     | Н          | Н        | L      | Н      | Н      | Н      | Χ   | Χ   | Χ   | Х              | Х             |      |

| Mode Register Set             | MRS     | Н          | Н        | L      | L      | L      | L      | 0   | 0   | 0   | OPC            | ODE           |      |

| Extended Mode<br>Register Set | EMRS    | Н          | Н        | L      | L      | L      | L      | 1   | 0   | 0   | OPC            | CODE          |      |

| Bank Activate                 | ACT     | Н          | Н        | L      | L      | Н      | Н      | ВА  | ВА  | ВА  | Row<br>Address |               | 1)3) |

| Read                          | RD      | Н          | Н        | L      | Н      | L      | Н      | ВА  | ВА  | ВА  | L              | Col.          | 1)4) |

| Read w/ Autoprecharge         | RD/A    | Н          | Н        | L      | Н      | L      | Н      | ВА  | ВА  | ВА  | Н              | Col.          | 1)4) |

| Write                         | WR      | Н          | Н        | L      | Н      | L      | L      | ВА  | ВА  | ВА  | L              | Col.          | 1)4) |

| Write w/ Autoprecharge        | WR/A    | Н          | Н        | L      | Н      | L      | L      | ВА  | ВА  | ВА  | Н              | Col.          | 1)4) |

| Precharge                     | PRE     | Н          | Н        | L      | L      | Н      | L      | ВА  | ВА  | ВА  | L              | Х             | 1)   |

| Precharge All                 | PREALL  | Н          | Н        | L      | L      | Н      | L      | Х   | Х   | Χ   | Н              | Х             | 1)   |

| Auto Refresh                  | AREF    | Н          | Н        | L      | L      | L      | Н      | Х   | Х   | Х   | Х              | Х             | 1)5) |

| Power Down Mode<br>Entry      | PWDNEN  | Н          | L        | H<br>L | X<br>H | X<br>H | X<br>H | Х   | X   | X   | Х              | X             | 1)6) |

| Power Down Mode Exit          | PWDNEX  | L          | Н        | X      | X      | X      | X      | Х   | Х   | Х   | Χ              | X             | 1)7) |

| Self Refresh Entry            | SREFEN  | Н          | L        | L      | L      | L      | Н      | Х   | Х   | Х   | Χ              | X             | 1)8) |

| Self Refresh Exit             | SREFEX  | L          | Н        | Χ      | Х      | Х      | Х      | Х   | Х   | Х   | Χ              | X             | 1)9) |

<sup>1)</sup> X represents "Don't Care".

<sup>2)</sup> This command is invoked when a Read is issued on another DRAM rank placed on the same command bus. Cannot be in power-down or self-refresh state. The Read command will cause the data termination to be disabled. Refer to Figure 14 for timing.

<sup>3)</sup> BA0 - BA2 provide bank address, A0 - A11 provide the row address.

<sup>4)</sup> BA0 - BA2 provide bank address, A2- A7, A9 provide the column address, A8/AP controls Auto Precharge.

<sup>5)</sup> Auto Refresh and Self Refresh Entry differ only by the state of CKE.

<sup>6)</sup> PWDNEN is selected by issuing a DESEL or NOP at the first positive CLK edge following the HIGH to LOW transition of CKE.

<sup>7)</sup> First possible valid command after  $t_{XPN}$ . During  $t_{XPN}$  only NOP or DESEL commands are allowed.

<sup>8)</sup> Self Refresh is selected by issuing AREF at the first positive CLK edge following the HIGH to LOW transition of CKE.

First possible valid command after t<sub>XSC</sub>. During t<sub>XSC</sub> only NOP or DESEL commands are allowed.

# 2.4.2 Description of Commands

| Table 5 | <b>Description of Commands</b> |

|---------|--------------------------------|

|---------|--------------------------------|

| Table 5 | Description of Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Command | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| DESEL   | The DESEL function prevents new commands from being executed by the Graphics SDRAM. The Graphics SDRAM is effectively deselected. Operations in progress are not affected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| NOP     | The NOP command is used to perform a no operation to the Graphics SDRAM, which is selected $(\overline{\text{CS}} \text{ is LOW})$ . This prevents unwanted commands from being registered during idle or wait states. Operations already in progress are not affected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| MRS     | The Mode Register is loaded via address inputs A0 - A11. For more details see "Mode Register Set Command (MRS)" on Page 40 . The MRS command can only be issued when all banks are idle and no bursts are in progress. A subsequent executable command cannot be issued until $t_{\text{MRD}}$ is met.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| EMRS    | The Extended Mode Register is loaded via address inputs A0 - A11. For more details see section "Extended Mode Register Set Command (EMRS)" on Page 37. The EMRS command can only be issued when all banks are idle and no bursts are in progress. A subsequent executable command cannot be issued until $t_{\rm MRD}$ is met.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

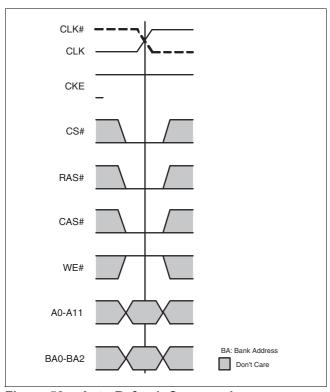

| ACT     | The ACT command is used to open (or activate) a row in a particular bank for a subsequent access. The value on the BA0 - BA2 inputs selects the bank, and the address provided in inputs A0 - A11 selects the row. This row remains active (or open) for accesses until a precharge (PRE, RD/A, or WR/A command) is issued to that bank. A precharge must be issued before opening a different row in the same bank.                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| RD      | The RD command is used to initiate a burst read access to an active row. The value on the BA0 - BA2 inputs selects the bank, and the address provided on inputs A2-A7, A9 selects the column location. The row will remain open for subsequent accesses. For RD commands the value on A8 is set LOW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| RD/A    | The RD/A command is used to initiate a burst read access to an active row. The value on the BA0 - BA2 inputs selects the bank, and the address provided on inputs A2-A7, A9 selects the column location. The value on input A8 is set HIGH. The row being accessed will be precharged at the end of the read burst. The same individual-bank precharge function is performed like it is described for the PRE command. Auto precharge ensures that the precharge is initiated at the earliest valid stage within the burst. The user must not issue a new ACT command to the same bank until the precharge time ( $t_{RP}$ ) is completed. This time is determined as if an explicit PRE command was issued at the earliest possible time as described in section "Reads (RD)" on Page 55. |  |  |  |  |  |  |

| WR      | The WR command is used to initiate a burst write access to an active row. The value on the BA0 - BA2 inputs selects the bank, and the address provided on inputs A2-A7, A9 selects the column location. The row will remain open for subsequent accesses. For WR commands the value on A8 is set LOW.  Input data appearing on the DQs is written to the memory array depending on the value on the DM input appearing coincident with the data. If a given DM signal is registered LOW, the corresponding                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|         | data will be written to the memory; if the DM signal is registered HIGH, the corresponding data inputs will be ignored, and a write will not be executed for that byte / column location.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| Table 5 | Description of Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Command | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| WR/A    | The WR/A command is used to initiate a burst write access to an active row. The value on the BAO BA1 and BA2 inputs selects the bank, and the address provided on inputs A2-A7, A9 selects the column location. The value on input A8 is set HIGH. The row being accessed will be precharged at the end of the write burst. The same individual-bank precharge function is performed which is described for the PRE command. Auto precharge ensures that the precharge is initiated at the earliest valid stage within the burst. The user is not allowed to issue a new ACT to the same bank until the precharge time (t <sub>RP</sub> ) is completed. This time is determined as if an explicit PRE command was issued at the earliest possible time as described in section "Writes (WR)" on Page 45. Input data appearing on the DQs is written to the memory array depending on the DM input logic level appearing coincident with the data. If a given DM signal is registered LOW, the corresponding data will be written to the memory; if the DM signal is registered HIGH, the corresponding data inputs will be ignored, and a write will not be executed to that byte / column location. |  |  |  |  |  |  |

| PRE     | The PRE command is used to deactivate the open row in a particular bank. The bank will be available for a subsequent row access a specified time ( $t_{\rm RP}$ ) after the PRE command is issued. Inputs BA0 - BA2 select the bank to be precharged. A8/AP is set to LOW. Once a bank has been precharged, it is in the idle state and must be activated again prior to any RD or WR commands being issued to that bank. A PRE command will be treated as a NOP if there is no open row in that bank, or if the previously open row is already in the process of precharging.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| PREALL  | The PREALL command is used to deactivate all open rows in the memory device. The banks will be available for a subsequent row access a specified time ( $t_{\rm RP}$ ) after the PREALL command is issued. Once the banks have been precharged, they are in the idle state and must be activated prior to any read or write commands being issued. The PREALL command will be treated as a NOP for those banks where there is no open row, or if a previously open row is already in the process of precharging. PREALL is issued by a PRE command with A8/AP set to HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| AREF    | The AREF is used during normal operation of the GDDR3 Graphics RAM to refresh the memory content. The refresh addressing is generated by the internal refresh controller. This makes the address bits "Don't Care" during an AREF command. The HYB18H512321AF requires AREF cycles at an average periodic interval of $t_{\rm REFI}$ (max). To improve efficiency a maximum number of eight AREF commands can be posted to one memory device (with $t_{\rm RFC}$ from AREF to AREF) as described in section "Auto Refresh Command (AREF)" on Page 70. This means that the maximum absolute interval between any AREF command is 8 x $t_{\rm REFI}$ (max). This maximum absolute interval is to allow the GDDR3 Graphics RAM output drivers and internal terminators to recalibrate, compensating for voltage and temperature changes. All banks must be in the idle state before issuing the AREF command. They will be simultaneously refreshed and return to the idle state after AREF is completed. $t_{\rm RFC}$ is the minimum required time between an AREF command and a following ACT/AREF command.                                                                                          |  |  |  |  |  |  |